EXF

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 3688                                                          |

| Number of Logic Elements/Cells | 33192                                                         |

| Total RAM Bits                 | 663552                                                        |

| Number of I/O                  | 376                                                           |

| Number of Gates                | 1600000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 484-BBGA                                                      |

| Supplier Device Package        | 484-FBGA (23x23)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1600e-4fg484i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Configuration

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

## I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, <u>66 MHz</u>

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

| Package                | VQ1<br>VQG                      |                  | CP <sup>.</sup><br>CPG | 132<br>132       |                    | 144<br>6144      | PQ:<br>PQC         |                  |                    | 256<br>1256      |                    | 320<br>3320       |                    | 400<br>6400        | FG4<br>FGG         |                    |

|------------------------|---------------------------------|------------------|------------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|

| Footprint<br>Size (mm) | 16 x                            | 16               | 8 :                    | x 8              | 22 >               | c 22             | 30.5 >             | c 30.5           | 17 ג               | k 17             | 19 >               | c 19              | 21 >               | k 21               | <b>23</b> :        | x 23               |

| Device                 | User                            | Diff             | User                   | Diff             | User               | Diff             | User               | Diff             | User               | Diff             | User               | Diff              | User               | Diff               | User               | Diff               |

| XC3S100E               | <b>66<sup>(2)</sup></b><br>9(7) | <b>30</b><br>(2) | <b>83</b><br>(11)      | <b>35</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | -                  | -                | -                  | -                | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S250E               | <b>66</b><br>(7)                | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>172</b><br>(40) | <b>68</b><br>(8) | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S500E               | <b>66<sup>(3)</sup></b><br>(7)  | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | -                  | -                | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>190</b><br>(41) | <b>77</b><br>(8) | <b>232</b><br>(56) | <b>92</b><br>(12) | -                  | -                  | -                  | -                  |

| XC3S1200E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | <b>190</b><br>(40) | <b>77</b><br>(8) | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | -                  | -                  |

| XC3S1600E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | -                  | -                | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | <b>376</b><br>(82) | <b>156</b><br>(21) |

## Table 2: Available User I/Os and Differential (Diff) I/O Pairs

#### Notes:

1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

3. The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical and general references to the VQ100 will apply to the XC3S500E.

## Supply Voltages for the IOBs

The IOBs are powered by three supplies:

- 1. The  $V_{CCO}$  supplies, one for each of the FPGA's I/O banks, power the output drivers. The voltage on the  $V_{CCO}$  pins determines the voltage swing of the output signal.

- 2.  $V_{CCINT}$  is the main power supply for the FPGA's internal logic.

- V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also applies to input-only pins and dual-purpose I/O pins that are not actively involved in the currently-selected configuration mode.

All I/O pins have ESD clamp diodes to their respective V<sub>CCO</sub> supply and from GND, as shown in Figure 5. The V<sub>CCINT</sub> (1.2V), V<sub>CCAUX</sub> (2.5V), and V<sub>CCO</sub> supplies can be applied in any order. Before the FPGA can start its configuration process, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> must have reached their respective minimum recommended operating levels indicated in Table 74. At this time, all output drivers are in a high-impedance state. V<sub>CCO</sub> Bank 2, V<sub>CCINT</sub>, and V<sub>CCAUX</sub> serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP input enables pull-up resistors on user-I/O and input-only pins from power-on throughout configuration. A High level on HSWAP disables the pull-up resistors, allowing the I/Os to float. HSWAP contains an internal pull-up resistor and defaults to High if left floating. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a default Low state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of configuration, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. Configuration data is then loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP input) throughout configuration.

At the end of configuration, the GSR net is released, placing the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective SR inputs.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the

beginning of design operation in the User mode. After the GTS net is released, all user I/Os go active while all unused I/Os are pulled down (PULLDOWN). The designer can control how the unused I/Os are terminated after GTS is released by setting the Bitstream Generator (BitGen) option UnusedPin to PULLUP, PULLDOWN, or FLOAT.

One clock cycle later (default), the Global Write Enable (GWE) net is released allowing the RAM and registers to change states. Once in User mode, any pull-up resistors enabled by HSWAP revert to the user settings and HSWAP is available as a general-purpose I/O. For more information on PULLUP and PULLDOWN, see Pull-Up and Pull-Down Resistors.

# Behavior of Unused I/O Pins After Configuration

By default, the Xilinx ISE development software automatically configures all unused I/O pins as input pins with individual internal pull-down resistors to GND.

This default behavior is controlled by the **UnusedPin** bitstream generator (BitGen) option, as described in Table 69.

## JTAG Boundary-Scan Capability

All Spartan-3E IOBs support boundary-scan testing compatible with IEEE 1149.1/1532 standards. During boundary-scan operations such as EXTEST and HIGHZ the pull-down resistor is active. See JTAG Mode for more information on programming via JTAG.

## Wide Multiplexers

For additional information, refer to the "Using Dedicated Multiplexers" chapter in UG331.

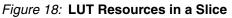

Wide-function multiplexers effectively combine LUTs in order to permit more complex logic operations. Each slice has two of these multiplexers with F5MUX in the bottom portion of the slice and FiMUX in the top portion. The F5MUX multiplexes the two LUTs in a slice. The FiMUX multiplexes two CLB inputs which connect directly to the F5MUX and FiMUX results from the same slice or from other slices. See Figure 19.

Depending on the slice, FiMUX takes on the name F6MUX, F7MUX, or F8MUX. The designation indicates the number of inputs possible without restriction on the function. For example, an F7MUX can generate any function of seven inputs. Figure 20 shows the names of the multiplexers in each position in the Spartan-3E CLB. The figure also includes the direct connections within the CLB, along with the F7MUX connection to the CLB below.

Each mux can create logic functions of more inputs than indicated by its name. The F5MUX, for example, can generate any function of five inputs, with four inputs duplicated to two LUTs and the fifth input controlling the mux. Because each LUT can implement independent 2:1 muxes, the F5MUX can combine them to create a 4:1 mux, which is a six-input function. If the two LUTs have completely independent sets of inputs, some functions of all nine inputs can be implemented. Table 11 shows the connections for each multiplexer and the number of inputs possible for different types of functions.

## Table 14: Carry Logic Functions (Cont'd)

| Function | Description                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY0G     | <ul> <li>Carry generation for top half of slice. Fixed selection of:</li> <li>G1 or G2 inputs to the LUT (both equal 1 when a carry is to be generated)</li> <li>GAND gate for multiplication</li> <li>BY input for carry initialization</li> <li>Fixed 1 or 0 input for use as a simple Boolean function</li> </ul> |

| CYMUXF   | <ul> <li>Carry generation or propagation mux for bottom half of slice. Dynamic selection via CYSELF of:</li> <li>CYINIT carry propagation (CYSELF = 1)</li> <li>CY0F carry generation (CYSELF = 0)</li> </ul>                                                                                                        |

| CYMUXG   | <ul> <li>Carry generation or propagation mux for top half of slice. Dynamic selection via CYSELF of:</li> <li>CYMUXF carry propagation (CYSELG = 1)</li> <li>CY0G carry generation (CYSELG = 0)</li> </ul>                                                                                                           |

| CYSELF   | <ul> <li>Carry generation or propagation select for bottom half of slice. Fixed selection of:</li> <li>F-LUT output (typically XOR result)</li> <li>Fixed 1 to always propagate</li> </ul>                                                                                                                           |

| CYSELG   | <ul> <li>Carry generation or propagation select for top half of slice. Fixed selection of:</li> <li>G-LUT output (typically XOR result)</li> <li>Fixed 1 to always propagate</li> </ul>                                                                                                                              |

| XORF     | <ul> <li>Sum generation for bottom half of slice. Inputs from:</li> <li>F-LUT</li> <li>CYINIT carry signal from previous stage</li> <li>Result is sent to either the combinatorial or registered output for the top of the slice.</li> </ul>                                                                         |

| XORG     | <ul> <li>Sum generation for top half of slice. Inputs from:</li> <li>G-LUT</li> <li>CYMUXF carry signal from previous stage</li> <li>Result is sent to either the combinatorial or registered output for the top of the slice.</li> </ul>                                                                            |

| FAND     | <ul> <li>Multiplier partial product for bottom half of slice. Inputs:</li> <li>F-LUT F1 input</li> <li>F-LUT F2 input</li> <li>Result is sent through CY0F to become the carry generate signal into CYMUXF</li> </ul>                                                                                                |

| GAND     | <ul> <li>Multiplier partial product for top half of slice. Inputs:</li> <li>G-LUT G1 input</li> <li>G-LUT G2 input</li> <li>Result is sent through CY0G to become the carry generate signal into CYMUXG</li> </ul>                                                                                                   |

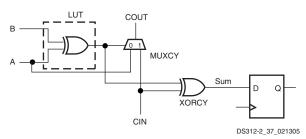

The basic usage of the carry logic is to generate a half-sum in the LUT via an XOR function, which generates or propagates a carry out COUT via the carry mux CYMUXF (or CYMUXG), and then complete the sum with the dedicated XORF (or XORG) gate and the carry input CIN. This structure allows two bits of an arithmetic function in each slice. The CYMUXF (or CYMUXG) can be instantiated using the MUXCY element, and the XORF (or XORG) can be instantiated using the XORCY element.

The FAND (or GAND) gate is used for partial product multiplication and can be instantiated using the MULT\_AND component. Partial products are generated by two-input AND gates and then added. The carry logic is efficient for the adder, but one of the inputs must be outside the LUT as shown in Figure 23.

## Figure 23: Using the MUXCY and XORCY in the Carry Logic

The FAND (or GAND) gate is used to duplicate one of the partial products, while the LUT generates both partial products and the XOR function, as shown in Figure 24.

www.xilinx.com

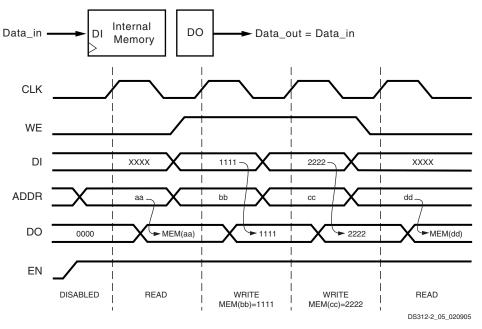

There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a output latch to the DO outputs. The timing for basic data access is shown in the

XILINX.

portions of Figure 33, Figure 34, and Figure 35 during which WE is Low.

Data also can be accessed on the DO outputs when asserting the WE input based on the value of the WRITE\_MODE attribute as described in Table 26.

#### Table 26: WRITE\_MODE Effect on Data Output Latches During Write Operations

| Write Mode                      | Effect on Same Port                                                                                                              | Effect on Opposite Port<br>(dual-port only with same address)   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| WRITE_FIRST<br>Read After Write | Data on DI and DIP inputs is written into specified RAM location and simultaneously appears on DO and DOP outputs.               | Invalidates data on DO and DOP outputs.                         |

| READ_FIRST<br>Read Before Write | Data from specified RAM location appears on DO and DOP outputs.<br>Data on DI and DIP inputs is written into specified location. | Data from specified RAM location appears on DO and DOP outputs. |

| NO_CHANGE<br>No Read on Write   | Data on DO and DOP outputs remains unchanged.<br>Data on DI and DIP inputs is written into specified<br>location.                | Invalidates data on DO and DOP outputs.                         |

Setting the WRITE\_MODE attribute to a value of WRITE\_FIRST, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE\_FIRST timing is shown in the portion of Figure 33 during which WE is High.

Setting the WRITE\_MODE attribute to a value of READ\_FIRST, data already stored in the addressed location passes to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ\_FIRST timing is shown in the portion of Figure 34 during which WE is High.

www.xilinx.com

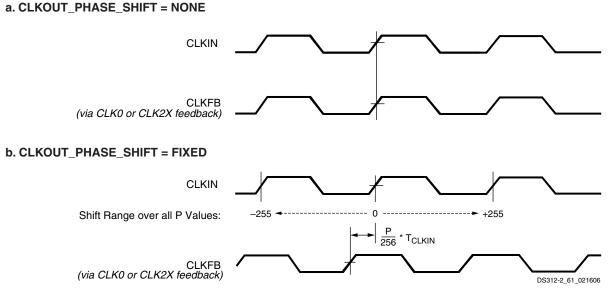

## **FIXED Phase Shift Mode**

The FIXED phase shift mode shifts the DCM outputs by a fixed amount (T<sub>PS</sub>), controlled by the user-specified PHASE\_SHIFT attribute. The PHASE\_SHIFT value (shown as P in Figure 44) must be an integer ranging from –255 to +255. PHASE\_SHIFT specifies a phase shift delay as a fraction of the T<sub>CLKIN</sub>. The phase shift behavior is different between ISE 8.1, Service Pack 3 and prior software versions, as described below.

#### Design Note

Prior to ISE 8.1i, Service Pack 3, the FIXED phase shift feature operated differently than the Spartan-3 DCM design primitive and simulation model. Designs using software prior to ISE 8.1i, Service Pack 3 require recompilation using the latest ISE software release. The following Answer Record contains additional information:

#### http://www.xilinx.com/support/answers/23153.htm.

**FIXED Phase Shift using ISE 8.1i, Service Pack 3 and later:** See Equation 2. The value corresponds to a phase shift range of  $-360^{\circ}$  to  $+360^{\circ}$ , which matches behavior of the Spartan-3 DCM design primitive and simulation model.

$$t_{PS} = \left(\frac{PHASESHIFT}{256}\right) \bullet T_{CLKIN} \qquad Eq 2$$

**FIXED Phase Shift prior to ISE 8.1i, Service Pack 3:** See Equation 3. The value corresponds to a phase shift range of  $-180^{\circ}$  to  $+180^{\circ}$  degrees, which is different from the Spartan-3 DCM design primitive and simulation model. Designs created prior to ISE 8.1i, Service Pack 3 must be recompiled using the most recent ISE development software.

$$t_{PS} = \left(\frac{PHASESHIFT}{512}\right) \bullet T_{CLKIN} \qquad Eq 3$$

When the PHASE\_SHIFT value is zero, CLKFB and CLKIN are in phase, the same as when the PS unit is disabled. When the PHASE\_SHIFT value is positive, the DCM outputs are shifted later in time with respect to CLKIN input. When the attribute value is negative, the DCM outputs are shifted earlier in time with respect to CLKIN.

Figure 44b illustrates the relationship between CLKFB and CLKIN in the Fixed Phase mode. In the Fixed Phase mode, the PSEN, PSCLK, and PSINCDEC inputs are not used and must be tied to GND.

Equation 2 or Equation 3 applies only to FIXED phase shift mode. The VARIABLE phase shift mode operates differently.

Figure 44: NONE and FIXED Phase Shifter Waveforms (ISE 8.1i, Service Pack 3 and later)

## **Direct Connections**

Direct connect lines route signals to neighboring tiles: vertically, horizontally, and diagonally. These lines most often drive a signal from a "source" tile to a double, hex, or long line and conversely from the longer interconnect back to a direct line accessing a "destination" tile.

## Global Controls (STARTUP\_SPARTAN3E)

In addition to the general-purpose interconnect, Spartan-3E FPGAs have two global logic control signals, as described in Table 43. These signals are available to the FPGA application via the STARTUP SPARTAN3E primitive.

| Table 43: Sp | partan-3E Global | Logic Control | Signals |

|--------------|------------------|---------------|---------|

|--------------|------------------|---------------|---------|

| Global Control<br>Input | Description                                                                                                                                                                                                                                        |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GSR                     | <b>Global Set/Reset:</b> When High,<br>asynchronously places all registers and<br>flip-flops in their initial state (see Initialization,<br>page 31). Asserted automatically during the<br>FPGA configuration process (see Start-Up,<br>page 105). |

| GTS                     | <b>Global Three-State:</b> When High, asynchronously forces all I/O pins to a high-impedance state (Hi-Z, three-state).                                                                                                                            |

The Global Set/Reset (GSR) signal replaces the global reset signal included in many ASIC-style designs. Use the GSR control instead of a separate global reset signal in the design to free up CLB inputs, resulting in a smaller, more efficient design. Similarly, the GSR signal is asserted automatically during the FPGA configuration process, guaranteeing that the FPGA starts-up in a known state.

The STARTUP\_SPARTAN3E primitive also includes two other signals used specifically during configuration. The MBT signals are for Dynamically Loading Multiple Configuration Images Using MultiBoot Option, page 91. The CLK input is an alternate clock for configuration Start-Up, page 105.

## **Voltage Compatibility**

The PROM's  $V_{CCINT}$  supply must be either 3.3V for the serial XCFxxS Platform Flash PROMs or 1.8V for the serial/parallel XCFxxP PROMs.

V The FPGA's VCCO\_2 supply input and the Platform Flash PROM's V<sub>CCO</sub> supply input must be the same voltage, ideally +2.5V. Both devices also support 1.8V and 3.3V interfaces but the FPGA's PROG\_B and DONE pins require special attention as they are powered by the FPGA's V<sub>CCAUX</sub> supply, nominally 2.5V. See application note XAPP453: The 3.3V Configuration of Spartan-3 FPGAs for additional information.

## **Supported Platform Flash PROMs**

Table 51 shows the smallest available Platform Flash PROM to program one Spartan-3E FPGA. A multiple-FPGA daisy-chain application requires a <u>Platform Flash PROM</u> large enough to contain the sum of the various FPGA file sizes.

## Table 51: Number of Bits to Program a Spartan-3EFPGA and Smallest Platform Flash PROM

| Spartan-3E<br>FPGA | Number of<br>Configuration Bits | Smallest Available<br>Platform Flash |

|--------------------|---------------------------------|--------------------------------------|

| XC3S100E           | 581,344                         | XCF01S                               |

| XC3S250E           | 1,353,728                       | XCF02S                               |

| XC3S500E           | 2,270,208                       | XCF04S                               |

| XC3S1200E          | 3,841,184                       | XCF04S                               |

| XC3S1600E          | 5,969,696                       | XCF08P<br>or 2 x XCF04S              |

The XC3S1600E requires an 8 Mbit PROM. Two solutions are possible: either a single 8 Mbit XCF08P parallel/serial PROM or two 4 Mbit XCF04S serial PROMs cascaded. The two XCF04S PROMs use a 3.3V V<sub>CCINT</sub> supply while the XCF08P requires a 1.8V V<sub>CCINT</sub> supply. If the board does not already have a 1.8V supply available, the two cascaded XCF04S PROM solution is recommended.

## **CCLK Frequency**

In Master Serial mode, the FPGA's internal oscillator generates the configuration clock frequency. The FPGA provides this clock on its CCLK output pin, driving the PROM's CLK input pin. The FPGA starts configuration at its lowest frequency and increases its frequency for the remainder of the configuration process if so specified in the configuration bitstream. The maximum frequency is specified using the *ConfigRate* bitstream generator option. Table 52 shows the maximum *ConfigRate* settings, approximately equal to MHz, for various Platform Flash devices and I/O voltages. For the serial XCFxxS PROMs, the maximum frequency also depends on the interface voltage.

## *Table 52:* Maximum ConfigRate Settings for Platform Flash

| Platform Flash<br>Part Number | I/O Voltage<br>(VCCO_2, V <sub>CCO</sub> ) | Maximum<br><i>ConfigRate</i><br>Setting |

|-------------------------------|--------------------------------------------|-----------------------------------------|

| XCF01S<br>XCF02S              | 3.3V or 2.5V                               | 25                                      |

| XCF04S                        | 1.8V                                       | 12                                      |

| XCF08P<br>XCF16P<br>XCF32P    | 3.3V, 2.5V, or 1.8V                        | 25                                      |

## **Daisy-Chaining**

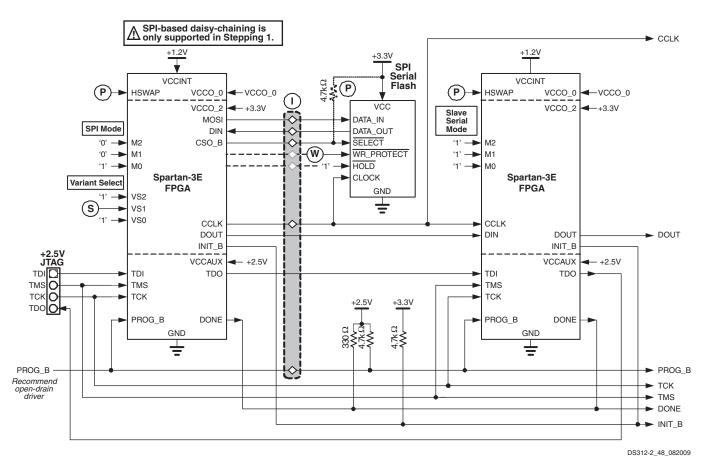

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 57. Daisy-chaining from a single SPI serial Flash PROM is supported in Stepping 1 devices. It is not supported in Stepping 0 devices. Use SPI Flash mode (M[2:0] = <0:0:1>) for the FPGA connected to the Platform Flash PROM and Slave Serial mode (M[2:0] = <1:1:1>) for all other FPGAs in the daisy-chain. After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the SPI Flash PROM, the master device uses its DOUT output pin to supply data to the next device in the daisy-chain, on the falling CCLK edge.

#### Design Note

SPI mode daisy chains are supported only in Stepping 1 silicon versions.

Figure 57: Daisy-Chaining from SPI Flash Mode (Stepping 1)

## **Programming Support**

For successful daisy-chaining, the **DONE\_cycle** configuration option must be set to cycle 5 or sooner. The default cycle is 4. See Table 69 and the Start-Up section for additional information.

U In production applications, the SPI Flash PROM is usually pre-programmed before it is mounted on the printed circuit board. The <u>Xilinx ISE development software</u> produces industry-standard programming files that can be used with third-party gang programmers. Consult your specific SPI Flash vendor for recommended production programming solutions. In-system programming support is available from some third-party PROM programmers using a socket adapter with attached wires. To gain access to the SPI Flash signals, drive the FPGA's PROG\_B input Low with an open-drain driver. This action places all FPGA I/O pins, including those attached to the SPI Flash, in high-impedance (Hi-Z). If the HSWAP input is Low, the I/Os have pull-up resistors to the  $V_{CCO}$  input on their respective I/O bank. The external programming hardware then has direct access to the SPI Flash pins. The programming access points are highlighted in the gray box in Figure 53, Figure 54, and Figure 57.

Beginning with the Xilinx ISE 8.2i software release, the iMPACT programming utility provides direct, in-system prototype programming support for STMicro M25P-series

## **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for Stepping 0 are compatible with Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device.

## **Differences Between Steppings**

Table 71 summarizes the feature and performancedifferences between Stepping 0 devices and Stepping 1devices.

## Table 71: Differences between Spartan-3E Production Stepping Levels

|                                                                                                                     | Stepping 0                                                                                  | Stepping 1                                                |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Production status                                                                                                   | Production from 2005 to 2007                                                                | Production starting<br>March 2006                         |

| Speed grade and operating conditions                                                                                | -4C only                                                                                    | -4C, -4I, -5C                                             |

| JTAG ID code                                                                                                        | Different revision fields. Se                                                               | e Table 67.                                               |

| DCM DLL maximum input frequency                                                                                     | 90 MHz<br>(200 MHz for XC3S1200E)                                                           | 240 MHz (-4 speed grade)<br>275 MHz (-5 speed grade)      |

| DCM DFS output frequency range(s)                                                                                   | Split ranges at 5 – 90 MHz and<br>220 – 307 MHz<br>(single range 5 – 307 MHz for XC3S1200E) | Continuous range:<br>5 – 311 MHz (-4)<br>5 – 333 MHz (-5) |

| Supports multi-FPGA daisy-chain configurations from SPI Flash                                                       | No, single FPGA only                                                                        | Yes                                                       |

| JTAG configuration supported when FPGA in BPI<br>mode with a valid image in the attached parallel NOR<br>Flash PROM | No <sup>(1)</sup>                                                                           | Yes                                                       |

| JTAG EXTEST, INTEST, SAMPLE support                                                                                 | Yes: XC3S100E, XC3S250E, XC3S500E<br>No <sup>(2)</sup> : XC3S1200E, XC3S1600E               | Yes<br>All Devices                                        |

| Power sequencing when using HSWAP Pull-Up                                                                           | Requires V <sub>CCINT</sub> before V <sub>CCAUX</sub>                                       | Any sequence                                              |

| PCI compliance                                                                                                      | No                                                                                          | Yes                                                       |

#### Notes:

1. Workarounds exist. See Stepping 0 Limitations when Reprogramming via JTAG if FPGA Set for BPI Configuration.

2. JTAG BYPASS and JTAG configuration are supported

## **Ordering a Later Stepping**

-5C and -4I devices, and -4C devices (with date codes 0901 (2009) and later) always support the Stepping 1 feature set independent of the stepping code. Optionally, to order only Stepping 1 for the -4C devices, append an "S1" suffix to the standard ordering code, where '1' is the stepping number, as indicated in Table 72.

#### Table 72: Spartan-3E Optional Stepping Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None        | Production |

| 1                  | S1          | Production |

## **Software Version Requirements**

Production Spartan-3E applications must be processed using the Xilinx ISE 8.1i, Service Pack 3 or later development software, using the v1.21 or later speed files. The ISE 8.1i software implements critical bitstream generator updates.

For additional information on Spartan-3E development software and known issues, see the following Answer Record:

Xilinx Answer #22253

<a href="http://www.xilinx.com/support/answers/22253.htm">http://www.xilinx.com/support/answers/22253.htm</a>

# Spartan-3 FPGA Family: DC and Switching Characteristics

DS312 (4.0) October 29, 2012

#### **Product Specification**

## **DC Electrical Characteristics**

In this section, specifications may be designated as Advance, Preliminary, or Production. These terms are defined as follows:

<u>Advance</u>: Initial estimates are based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

**<u>Preliminary</u>:** Based on characterization. Further changes are not expected.

**Production:** These specifications are approved once the silicon has been characterized over numerous production lots. Parameter values are considered stable with no future changes expected.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. **Unless** otherwise noted, the published parameter values apply to all Spartan®-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

## **Absolute Maximum Ratings**

Stresses beyond those listed under Table 73, Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to absolute maximum conditions for extended periods of time adversely affects device reliability.

| Symbol                               | Description                              | Con                          | ditions                 | Min   | Max                                    | Units |

|--------------------------------------|------------------------------------------|------------------------------|-------------------------|-------|----------------------------------------|-------|

| V <sub>CCINT</sub>                   | Internal supply voltage                  |                              |                         | -0.5  | 1.32                                   | V     |

| V <sub>CCAUX</sub>                   | Auxiliary supply voltage                 |                              |                         | -0.5  | 3.00                                   | V     |

| V <sub>CCO</sub>                     | Output driver supply voltage             | It driver supply voltage     |                         |       | 3.75                                   | V     |

| V <sub>REF</sub>                     | Input reference voltage                  |                              |                         | -0.5  | V <sub>CCO</sub> +0.5 <sup>(1)</sup>   | V     |

| V <sub>IN</sub> <sup>(1,2,3,4)</sup> | Voltage applied to all User I/O pins and | Driver in a                  | Commercial              | -0.95 | 4.4                                    | V     |

|                                      | Dual-Purpose pins                        | high-impedance<br>state      | Industrial              | -0.85 | 4.3                                    | V     |

|                                      | Voltage applied to all Dedicated pins    |                              | All temp. ranges        | -0.5  | V <sub>CCAUX</sub> +0.5 <sup>(3)</sup> | V     |

| I <sub>IK</sub>                      | Input clamp current per I/O pin          | $-0.5 V < V_{IN} < (V_{IN})$ | <sub>CCO</sub> + 0.5 V) | -     | ±100                                   | mA    |

| V <sub>ESD</sub>                     | Electrostatic Discharge Voltage          | Human body mod               | lel                     | -     | ±2000                                  | V     |

|                                      |                                          | Charged device n             | nodel                   | -     | ±500                                   | V     |

|                                      |                                          | Machine model                |                         | -     | ±200                                   | V     |

| TJ                                   | Junction temperature                     |                              |                         | -     | 125                                    | °C    |

| T <sub>STG</sub>                     | Storage temperature                      |                              |                         | -65   | 150                                    | °C    |

#### Table 73: Absolute Maximum Ratings

Notes:

- 1. Each of the User I/O and Dual-Purpose pins is associated with one of the four banks'  $V_{CCO}$  rails. Keeping  $V_{IN}$  within 500 mV of the associated  $V_{CCO}$  rails or ground rail ensures that the internal diode junctions do not turn on. Table 77 specifies the  $V_{CCO}$  range used to evaluate the maximum  $V_{IN}$  voltage.

- Input voltages outside the -0.5V to V<sub>CCO</sub> + 0.5V (or V<sub>CCAUX</sub> + 0.5V) voltage range are require the I<sub>IK</sub> input diode clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Prolonged exposure to such current may compromise device reliability. A sustained current of 10 mA will not compromise device reliability. See <u>XAPP459</u>: *Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families* for more details.

- 3. All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> rail do not turn on. Table 77 specifies the V<sub>CCAUX</sub> range used to evaluate the maximum V<sub>IN</sub> voltage. As long as the V<sub>IN</sub> max specification is met, oxide stress is not possible.

- 4. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 5. For soldering guidelines, see <u>UG112</u>: Device Packaging and Thermal Characteristics and <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

www.xilinx.com

## Configurable Logic Block (CLB) Timing

Table 98: CLB (SLICEM) Timing

|                      |                                                                                                                                               |      | Speed | Grade |      |          |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|----------|

| Symbol               | Description                                                                                                                                   |      | -5    | -     | 4    | Units    |

|                      | -                                                                                                                                             |      | Мах   | Min   | Max  |          |

| Clock-to-Output T    | imes                                                                                                                                          |      |       |       |      |          |

| Т <sub>СКО</sub>     | When reading from the FFX (FFY) Flip-Flop, the time<br>from the active transition at the CLK input to data<br>appearing at the XQ (YQ) output | -    | 0.52  | -     | 0.60 | ns       |

| Setup Times          |                                                                                                                                               |      |       | 1     |      |          |

| T <sub>AS</sub>      | Time from the setup of data at the F or G input to the active transition at the CLK input of the CLB                                          | 0.46 | -     | 0.52  | -    | ns       |

| T <sub>DICK</sub>    | Time from the setup of data at the BX or BY input to the active transition at the CLK input of the CLB                                        | 1.58 | -     | 1.81  | -    | ns       |

| Hold Times           |                                                                                                                                               |      |       |       |      |          |

| T <sub>AH</sub>      | Time from the active transition at the CLK input to the point where data is last held at the F or G input                                     | 0    | -     | 0     | -    | ns       |

| Т <sub>СКDI</sub>    | Time from the active transition at the CLK input to the point where data is last held at the BX or BY input                                   | 0    | -     | 0     | -    | ns       |

| Clock Timing         |                                                                                                                                               |      |       | -     |      | <u>.</u> |

| Т <sub>СН</sub>      | The High pulse width of the CLB's CLK signal                                                                                                  | 0.70 | -     | 0.80  | -    | ns       |

| T <sub>CL</sub>      | The Low pulse width of the CLK signal                                                                                                         | 0.70 | -     | 0.80  | -    | ns       |

| F <sub>TOG</sub>     | Toggle frequency (for export control)                                                                                                         | 0    | 657   | 0     | 572  | MHz      |

| Propagation Time     | S                                                                                                                                             |      |       |       |      |          |

| T <sub>ILO</sub>     | The time it takes for data to travel from the CLB's F (G) input to the X (Y) output                                                           | -    | 0.66  | -     | 0.76 | ns       |

| Set/Reset Pulse W    | lidth                                                                                                                                         |      |       |       |      |          |

| T <sub>RPW_CLB</sub> | The minimum allowable pulse width, High or Low, to the CLB's SR input                                                                         | 1.57 | -     | 1.80  | -    | ns       |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77.

## Phase Shifter (PS)

#### Table 108: Recommended Operating Conditions for the PS in Variable Phase Mode

|                                     |                                                       |     | Speed Grade |     |     |     |

|-------------------------------------|-------------------------------------------------------|-----|-------------|-----|-----|-----|

| Symbol                              | Description                                           | -   | -5          |     | -4  |     |

|                                     |                                                       |     | Мах         | Min | Max |     |

| Operating Frequ                     | iency Ranges                                          |     |             |     |     |     |

| PSCLK_FREQ<br>(F <sub>PSCLK</sub> ) | Frequency for the PSCLK input                         | 1   | 167         | 1   | 167 | MHz |

| Input Pulse Req                     | uirements                                             |     | •           | •   | -   |     |

| PSCLK_PULSE                         | PSCLK pulse width as a percentage of the PSCLK period | 40% | 60%         | 40% | 60% | -   |

#### Table 109: Switching Characteristics for the PS in Variable Phase Mode

| Symbol                   | Description                                                                                               | Equa                                   | ation                                           | Units |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------|-------|--|--|--|

| Phase Shifting Range     |                                                                                                           |                                        |                                                 |       |  |  |  |

| MAX_STEPS <sup>(2)</sup> | Maximum allowed number of DCM_DELAY_STEP steps<br>for a given CLKIN clock period, where $T = CLKIN$ clock | CLKIN < 60 MHz                         | ±[INTEGER(10 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |  |  |  |

|                          | period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, double the effective clock period. <sup>(3)</sup>        | CLKIN ≥ 60 MHz                         | ±[INTEGER(15 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |  |  |  |

| FINE_SHIFT_RANGE_MIN     | Minimum guaranteed delay for variable phase shifting                                                      | ±[MAX_STEPS •<br>DCM_DELAY_STEP_MIN]   |                                                 | ns    |  |  |  |

| FINE_SHIFT_RANGE_MAX     | Maximum guaranteed delay for variable phase shifting                                                      | g ±[MAX_STEPS •<br>DCM_DELAY_STEP_MAX] |                                                 | ns    |  |  |  |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 108.

- 2. The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, i.e., the PHASE\_SHIFT attribute is set to 0.

- 3. The DCM\_DELAY\_STEP values are provided at the bottom of Table 105.

## **Miscellaneous DCM Timing**

#### Table 110: Miscellaneous DCM Timing

| Symbol Description                 |                                                                                                                                               | Min | Max | Units           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN <sup>(1)</sup>      | Minimum duration of a RST pulse width                                                                                                         | 3   | -   | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(2)</sup>      | Maximum duration of a RST pulse width                                                                                                         | N/A | N/A | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(3)</sup> | Maximum duration from $V_{\rm CCINT}$ applied to FPGA configuration successfully completed (DONE pin goes High) and clocks applied to DCM DLL | N/A | N/A | minutes         |

#### Notes:

1. This limit only applies to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV). The DCM DFS outputs (CLKFX, CLKFX180) are unaffected.

- 2. This specification is equivalent to the Virtex-4 DCM\_RESET specification. This specification does not apply for Spartan-3E FPGAs.

- 3. This specification is equivalent to the Virtex-4 TCONFIG specification. This specification does not apply for Spartan-3E FPGAs.

## Configuration and JTAG Timing

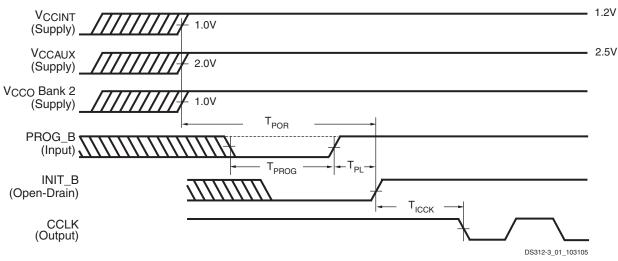

## **General Configuration Power-On/Reconfigure Timing**

#### Notes:

- 1. The  $V_{CCINT}\!,\,V_{CCAUX}\!,$  and  $V_{CCO}$  supplies may be applied in any order.

- 2. The Low-going pulse on PROG\_B is optional after power-on but necessary for reconfiguration without a power cycle.

- 3. The rising edge of INIT\_B samples the voltage levels applied to the mode pins (M0 M2).

#### *Figure 73:* Waveforms for Power-On and the Beginning of Configuration

#### Table 111: Power-On Timing and the Beginning of Configuration

| Ourseland                        | Description                                                                                                                | Device    | All Speed Grades |     | Unite |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----|-------|--|

| Symbol                           | Description                                                                                                                | Device    | Min              | Max | Units |  |

| T <sub>POR</sub> <sup>(2)</sup>  | The time from the application of $V_{CCINT}$ , $V_{CCAUX}$ , and $V_{CCO}$                                                 | XC3S100E  | -                | 5   | ms    |  |

|                                  | Bank 2 supply voltage ramps (whichever occurs last) to the rising transition of the INIT_B pin                             | XC3S250E  | -                | 5   | ms    |  |

|                                  |                                                                                                                            | XC3S500E  | -                | 5   | ms    |  |

|                                  |                                                                                                                            | XC3S1200E | -                | 5   | ms    |  |

|                                  |                                                                                                                            | XC3S1600E | -                | 7   | ms    |  |

| T <sub>PROG</sub>                | The width of the low-going pulse on the PROG_B pin                                                                         | All       | 0.5              | -   | μs    |  |

| T <sub>PL</sub> <sup>(2)</sup>   | The time from the rising edge of the PROG_B pin to the rising transition on the INIT_B pin                                 | XC3S100E  | -                | 0.5 | ms    |  |

|                                  |                                                                                                                            | XC3S250E  | -                | 0.5 | ms    |  |

|                                  |                                                                                                                            | XC3S500E  | -                | 1   | ms    |  |

|                                  |                                                                                                                            | XC3S1200E | -                | 2   | ms    |  |

|                                  |                                                                                                                            | XC3S1600E | -                | 2   | ms    |  |

| T <sub>INIT</sub>                | Minimum Low pulse width on INIT_B output                                                                                   | All       | 250              | -   | ns    |  |

| T <sub>ICCK</sub> <sup>(3)</sup> | The time from the rising edge of the INIT_B pin to the generation of the configuration clock signal at the CCLK output pin | All       | 0.5              | 4.0 | μs    |  |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77. This means power must be applied to all  $V_{CCINT}$ ,  $V_{CCO}$ , and  $V_{CCAUX}$  lines.

- 2. Power-on reset and the clearing of configuration memory occurs during this period.

- 3. This specification applies only to the Master Serial, SPI, BPI-Up, and BPI-Down modes.

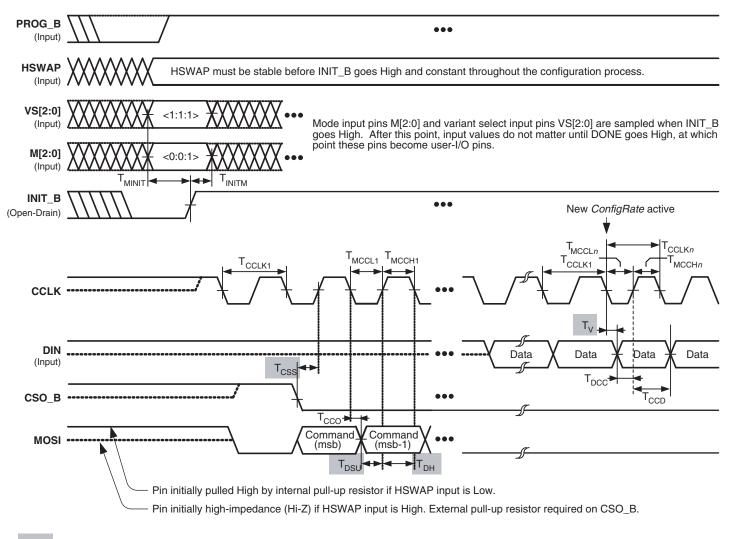

## Serial Peripheral Interface (SPI) Configuration Timing

Shaded values indicate specifications on attached SPI Flash PROM.

ds312-3\_06\_110206

## Figure 76: Waveforms for Serial Peripheral Interface (SPI) Configuration

#### Table 118: Timing for Serial Peripheral Interface (SPI) Configuration Mode

| Symbol             | Description                                                                 | Minimum       | Maximum | Units |

|--------------------|-----------------------------------------------------------------------------|---------------|---------|-------|

| T <sub>CCLK1</sub> | Initial CCLK clock period                                                   | See Table 112 |         |       |

| T <sub>CCLKn</sub> | CCLK clock period after FPGA loads ConfigRate setting                       | See Table 112 |         |       |

| T <sub>MINIT</sub> | Setup time on VS[2:0] and M[2:0] mode pins before the rising edge of INIT_B | 50            | -       | ns    |

| T <sub>INITM</sub> | Hold time on VS[2:0] and M[2:0]mode pins after the rising edge of INIT_B    | 0             | -       | ns    |

| T <sub>CCO</sub>   | MOSI output valid after CCLK edge                                           | See Table 116 |         |       |

| T <sub>DCC</sub>   | Setup time on DIN data input before CCLK edge                               | See Table 116 |         |       |

| T <sub>CCD</sub>   | Hold time on DIN data input after CCLK edge                                 | See Table 116 |         |       |

#### Table 124: Types of Pins on Spartan-3E FPGAs (Cont'd)

| - | Type / Color Description                                                                                                                       |                                                                                                                                                                                                                                                        | Pin Name(s) in Type <sup>(1)</sup> |

|---|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|   | VCCAUX                                                                                                                                         | Dedicated auxiliary power supply pin. The number of VCCAUX pins depends on the package used. All must be connected to +2.5V. See the Powering Spartan-3E FPGAs section in Module 2 for details.                                                        | VCCAUX                             |

|   | VCCINT                                                                                                                                         | Dedicated internal core logic power supply pin. The number of VCCINT pins depends on the package used. All must be connected to +1.2V. See the Powering Spartan-3E FPGAs section in Module 2 for details.                                              | VCCINT                             |

|   | VCCO                                                                                                                                           | Along with all the other VCCO pins in the same bank, this pin supplies power to the output buffers within the I/O bank and sets the input threshold voltage for some I/O standards. See the Powering Spartan-3E FPGAs section in Module 2 for details. | VCCO_#                             |

|   | N.C. This package pin is not connected in this specific device/package combination but may be connected in larger devices in the same package. |                                                                                                                                                                                                                                                        | N.C.                               |

#### Notes:

- 1. # = I/O bank number, an integer between 0 and 3.

- 2. IRDY/TRDY designations are for PCI designs; refer to PCI documentation for details.

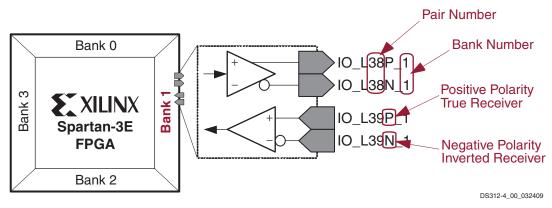

## **Differential Pair Labeling**

I/Os with Lxxy\_# are part of a differential pair. 'L' indicates differential capability. The 'xx' field is a two-digit integer, unique to each bank that identifies a differential pin-pair. The 'y' field is either 'P' for the true signal or 'N' for the inverted signal in the differential pair. The '#' field is the I/O bank number.

The pin name suffix has the following significance. Figure 79 provides a specific example showing a differential input to and a differential output from Bank 1. 'L' indicates that the pin is part of a differential pair.

'xx' is a two-digit integer, unique for each bank, that identifies a differential pin-pair.

'y' is replaced by 'P' for the true signal or 'N' for the inverted. These two pins form one differential pin-pair.

'#' is an integer, 0 through 3, indicating the associated  $\ensuremath{\mathsf{I/O}}$  bank.

Figure 79: Differential Pair Labeling

## Package Overview

Table 125 shows the eight low-cost, space-saving production package styles for the Spartan-3E family. Each package style is available as a standard and an environmentally friendly lead-free (Pb-free) option. The Pb-free packages include an extra 'G' in the package style name. For example, the standard "VQ100" package becomes "VQG100" when ordered as the Pb-free option. The mechanical dimensions of the standard and Pb-free packages are similar, as shown in the mechanical drawings provided in Table 127.

Not all Spartan-3E densities are available in all packages. For a specific package, however, there is a common footprint that supports all the devices available in that package. See the footprint diagrams that follow.

For additional package information, see <u>UG112</u>: *Device Package User Guide*.

| Package        | Leads | Туре                                    | Maximum<br>I/O | Lead<br>Pitch<br>(mm) | Footprint<br>Area (mm) | Height<br>(mm) | Mass <sup>(1)</sup><br>(g) |

|----------------|-------|-----------------------------------------|----------------|-----------------------|------------------------|----------------|----------------------------|

| VQ100 / VQG100 | 100   | Very-thin Quad Flat Pack (VQFP)         | 66             | 0.5                   | 16 x 16                | 1.20           | 0.6                        |

| CP132 / CPG132 | 132   | Chip-Scale Package (CSP)                | 92             | 0.5                   | 8.1 x 8.1              | 1.10           | 0.1                        |

| TQ144 / TQG144 | 144   | Thin Quad Flat Pack (TQFP)              | 108            | 0.5                   | 22 x 22                | 1.60           | 1.4                        |

| PQ208 / PQG208 | 208   | Plastic Quad Flat Pack (PQFP)           | 158            | 0.5                   | 30.6 x 30.6            | 4.10           | 5.3                        |

| FT256 / FTG256 | 256   | Fine-pitch, Thin Ball Grid Array (FBGA) | 190            | 1.0                   | 17 x 17                | 1.55           | 0.9                        |

| FG320 / FGG320 | 320   | Fine-pitch Ball Grid Array (FBGA)       | 250            | 1.0                   | 19 x 19                | 2.00           | 1.4                        |

| FG400 / FGG400 | 400   | Fine-pitch Ball Grid Array (FBGA)       | 304            | 1.0                   | 21 x 21                | 2.43           | 2.2                        |

| FG484 / FGG484 | 484   | Fine-pitch Ball Grid Array (FBGA)       | 376            | 1.0                   | 23 x 23                | 2.60           | 2.2                        |

#### Notes:

1. Package mass is  $\pm 10\%$ .

## Selecting the Right Package Option

Spartan-3E FPGAs are available in both quad-flat pack (QFP) and ball grid array (BGA) packaging options. While QFP packaging offers the lowest absolute cost, the BGA

packages are superior in almost every other aspect, as summarized in Table 126. Consequently, Xilinx recommends using BGA packaging whenever possible.

## Table 126: QFP and BGA Comparison

| Characteristic                              | Quad Flat Pack (QFP) | Ball Grid Array (BGA) |  |

|---------------------------------------------|----------------------|-----------------------|--|

| Maximum User I/O                            | 158                  | 376                   |  |

| Packing Density (Logic/Area)                | Good                 | Better                |  |

| Signal Integrity                            | Fair                 | Better                |  |

| Simultaneous Switching Output (SSO) Support | Fair                 | Better                |  |

| Thermal Dissipation                         | Fair                 | Better                |  |

| Minimum Printed Circuit Board (PCB) Layers  | 4                    | 4-6                   |  |

| Hand Assembly/Rework                        | Possible             | Difficult             |  |

## **Mechanical Drawings**

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

Detailed mechanical drawings for each package type are available from the Xilinx® web site at the specified location in Table 127.

| Package | Package Drawing | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| CP132   | Package Drawing | PK147_CP132  |

| CPG132  |                 | PK101_CPG132 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  |                 | PK123_PQG208 |

| FT256   | Package Drawing | PK158_FT256  |

| FTG256  |                 | PK115_FTG256 |

| FG320   | Package Drawing | PK152_FG320  |

| FGG320  |                 | PK106_FGG320 |

| FG400   | Package Drawing | PK182_FG400  |

| FGG400  |                 | PK108_FGG400 |

| FG484   | Package Drawing | PK183_FG484  |

| FGG484  |                 | PK110_FGG484 |

## Package Pins by Type

Each package has three separate voltage supply inputs—VCCINT, VCCAUX, and VCCO—and a common ground return, GND. The numbers of pins dedicated to these functions vary by package, as shown in Table 128.

| Package | VCCINT | VCCAUX | VCCO | GND |  |

|---------|--------|--------|------|-----|--|

| VQ100   | 4      | 4      | 8    | 12  |  |

| CP132   | 6      | 4      | 8    | 16  |  |

| TQ144   | 4      | 4      | 9    | 13  |  |

| PQ208   | 4      | 8      | 12   | 20  |  |

| FT256   | 8      | 8      | 16   | 28  |  |

| FG320   | 8      | 8      | 20   | 28  |  |

| FG400   | 16     | 8      | 24   | 42  |  |

| FG484   | 16     | 10     | 28   | 48  |  |

A majority of package pins are user-defined I/O or input pins. However, the numbers and characteristics of these I/O depend on the device type and the package in which it is available, as shown in Table 129. The table shows the maximum number of single-ended I/O pins available, assuming that all I/O-, INPUT-, DUAL-, VREF-, and CLK-type pins are used as general-purpose I/O. Likewise, the table shows the maximum number of differential pin-pairs available on the package. Finally, the table shows how the total maximum user-I/Os are distributed by pin type, including the number of unconnected—i.e., N.C.—pins on the device.

## Table 137: TQ144 Package Pinout (Cont'd)

| Bank | XC3S100E Pin Name      | XC3S250E Pin Name      | TQ144 Pin | Туре                                 |

|------|------------------------|------------------------|-----------|--------------------------------------|

| 2    | IP                     | IP                     | P38       | INPUT                                |

| 2    | IP                     | IP                     | P41       | INPUT                                |

| 2    | IP                     | IP                     | P69       | INPUT                                |

| 2    | IP_L03N_2/VREF_2       | IP_L03N_2/VREF_2       | P48       | VREF                                 |

| 2    | IP_L03P_2              | IP_L03P_2              | P47       | INPUT                                |

| 2    | IP_L06N_2/M2/GCLK1     | IP_L06N_2/M2/GCLK1     | P57       | DUAL/GCLK                            |

| 2    | IP_L06P_2/RDWR_B/GCLK0 | IP_L06P_2/RDWR_B/GCLK0 | P56       | DUAL/GCLK                            |

| 2    | VCCO_2                 | VCCO_2                 | P42       | VCCO                                 |

| 2    | VCCO_2                 | VCCO_2                 | P49       | VCCO                                 |

| 2    | VCCO_2                 | VCCO_2                 | P64       | VCCO                                 |

| 3    | IP/VREF_3              | IO/VREF_3              | P31       | 100E: VREF(INPUT)<br>250E: VREF(I/O) |

| 3    | IO_L01N_3              | IO_L01N_3              | P3        | I/O                                  |

| 3    | IO_L01P_3              | IO_L01P_3              | P2        | I/O                                  |

| 3    | IO_L02N_3/VREF_3       | IO_L02N_3/VREF_3       | P5        | VREF                                 |

| 3    | IO_L02P_3              | IO_L02P_3              | P4        | I/O                                  |

| 3    | IO_L03N_3              | IO_L03N_3              | P8        | I/O                                  |

| 3    | IO_L03P_3              | IO_L03P_3              | P7        | I/O                                  |

| 3    | IO_L04N_3/LHCLK1       | IO_L04N_3/LHCLK1       | P15       | LHCLK                                |

| 3    | IO_L04P_3/LHCLK0       | IO_L04P_3/LHCLK0       | P14       | LHCLK                                |

| 3    | IO_L05N_3/LHCLK3/IRDY2 | IO_L05N_3/LHCLK3       | P17       | LHCLK                                |

| 3    | IO_L05P_3/LHCLK2       | IO_L05P_3/LHCLK2       | P16       | LHCLK                                |

| 3    | IO_L06N_3/LHCLK5       | IO_L06N_3/LHCLK5       | P21       | LHCLK                                |

| 3    | IO_L06P_3/LHCLK4/TRDY2 | IO_L06P_3/LHCLK4       | P20       | LHCLK                                |

| 3    | IO_L07N_3/LHCLK7       | IO_L07N_3/LHCLK7       | P23       | LHCLK                                |

| 3    | IO_L07P_3/LHCLK6       | IO_L07P_3/LHCLK6       | P22       | LHCLK                                |

| 3    | IO_L08N_3              | IO_L08N_3              | P26       | I/O                                  |

| 3    | IO_L08P_3              | IO_L08P_3              | P25       | I/O                                  |

| 3    | IO_L09N_3              | IO_L09N_3              | P33       | I/O                                  |

| 3    | IO_L09P_3              | IO_L09P_3              | P32       | I/O                                  |

| 3    | IO_L10N_3              | IO_L10N_3              | P35       | I/O                                  |

| 3    | IO_L10P_3              | IO_L10P_3              | P34       | I/O                                  |

| 3    | IP                     | IP                     | P6        | INPUT                                |

| 3    | IO                     | IP                     | P10       | 100E: I/O                            |

|      |                        |                        |           | 250E: INPUT                          |

| 3    | IP                     | IP                     | P18       | INPUT                                |

| 3    | IP                     | IP                     | P24       | INPUT                                |

| 3    | Ю                      | IP                     | P29       | 100E: I/O<br>250E: INPUT             |

| 3    | IP                     | IP                     | P36       | INPUT                                |

| 3    | IP/VREF_3              | IP/VREF_3              | P12       | VREF                                 |

| 3    | VCCO_3                 | VCCO_3                 | P13       | VCCO                                 |

| 3    | VCCO_3                 | VCCO_3                 | P28       | VCCO                                 |

| GND  | GND                    | GND                    | P11       | GND                                  |

| GND  | GND                    | GND                    | P19       | GND                                  |

www.xilinx.com

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре      |

|------|----------------------------------|--------------|-----------|

| 1    | IO_L15N_1/LDC0                   | P151         | DUAL      |

| 1    | IO_L15P_1/HDC                    | P150         | DUAL      |

| 1    | IO_L16N_1/LDC2                   | P153         | DUAL      |

| 1    | IO_L16P_1/LDC1                   | P152         | DUAL      |

| 1    | IP                               | P110         | INPUT     |

| 1    | IP                               | P118         | INPUT     |

| 1    | IP                               | P124         | INPUT     |

| 1    | IP                               | P130         | INPUT     |

| 1    | IP                               | P142         | INPUT     |

| 1    | IP                               | P148         | INPUT     |

| 1    | IP                               | P154         | INPUT     |

| 1    | IP/VREF_1                        | P136         | VREF      |

| 1    | VCCO_1                           | P114         | VCCO      |

| 1    | VCCO_1                           | P125         | VCCO      |

| 1    | VCCO_1                           | P143         | VCCO      |

| 2    | IO/D5                            | P76          | DUAL      |

| 2    | IO/M1                            | P84          | DUAL      |

| 2    | IO/VREF_2                        | P98          | VREF      |

| 2    | IO_L01N_2/INIT_B                 | P56          | DUAL      |

| 2    | IO_L01P_2/CSO_B                  | P55          | DUAL      |

| 2    | IO_L03N_2/MOSI/CSI_B             | P61          | DUAL      |

| 2    | IO_L03P_2/DOUT/BUSY              | P60          | DUAL      |

| 2    | IO_L04N_2                        | P63          | I/O       |

| 2    | IO_L04P_2                        | P62          | I/O       |

| 2    | IO_L05N_2                        | P65          | I/O       |

| 2    | IO_L05P_2                        | P64          | I/O       |

| 2    | IO_L06N_2                        | P69          | I/O       |

| 2    | IO_L06P_2                        | P68          | I/O       |

| 2    | IO_L08N_2/D6/GCLK13              | P75          | DUAL/GCLK |

| 2    | IO_L08P_2/D7/GCLK12              | P74          | DUAL/GCLK |

| 2    | IO_L09N_2/D3/GCLK15              | P78          | DUAL/GCLK |

| 2    | IO_L09P_2/D4/GCLK14              | P77          | DUAL/GCLK |

| 2    | IO_L11N_2/D1/GCLK3               | P83          | DUAL/GCLK |

| 2    | IO_L11P_2/D2/GCLK2               | P82          | DUAL/GCLK |

| 2    | IO_L12N_2/DIN/D0                 | P87          | DUAL      |

| 2    | IO_L12P_2/M0                     | P86          | DUAL      |

| 2    | IO_L13N_2                        | P90          | I/O       |

| 2    | IO_L13P_2                        | P89          | I/O       |

| 2    | IO_L14N_2/A22                    | P94          | DUAL      |

| 2    | IO_L14P_2/A23                    | P93          | DUAL      |

| 2    | IO_L15N_2/A20                    | P97          | DUAL      |

| 2    | IO_L15P_2/A21                    | P96          | DUAL      |

| 2    | IO_L16N_2/VS1/A18                | P100         | DUAL      |

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре      |

|------|----------------------------------|--------------|-----------|

| 2    | IO_L16P_2/VS2/A19                | P99          | DUAL      |

| 2    | IO_L17N_2/CCLK                   | P103         | DUAL      |

| 2    | IO_L17P_2/VS0/A17                | P102         | DUAL      |

| 2    | IP                               | P54          | INPUT     |

| 2    | IP                               | P91          | INPUT     |

| 2    | IP                               | P101         | INPUT     |

| 2    | IP_L02N_2                        | P58          | INPUT     |

| 2    | IP_L02P_2                        | P57          | INPUT     |