#### AMD Xilinx - XC3S250E-4CPG132C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 612                                                           |

| Number of Logic Elements/Cells | 5508                                                          |

| Total RAM Bits                 | 221184                                                        |

| Number of I/O                  | 92                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 132-TFBGA, CSPBGA                                             |

| Supplier Device Package        | 132-CSPBGA (8x8)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s250e-4cpg132c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

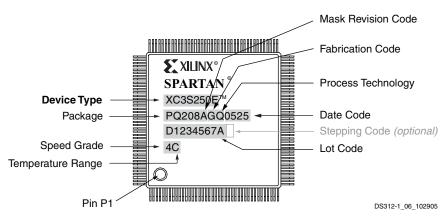

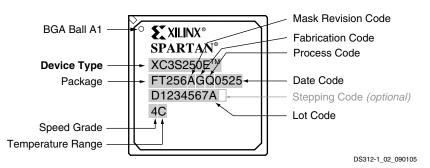

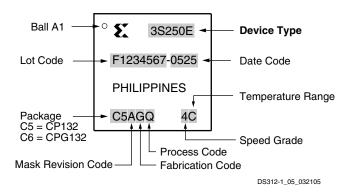

## Package Marking

Figure 2 provides a top marking example for Spartan-3E FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3E FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3E FPGAs in the CP132 and CPG132 packages. On the QFP and BGA packages, the optional numerical Stepping Code follows the Lot Code.

The "5C" and "4I" part combinations can have a dual mark of "5C/4I". Devices with a single mark are only guaranteed for the marked speed grade and temperature range. All "5C" and "4I" part combinations use the Stepping 1 production silicon.

Figure 2: Spartan-3E QFP Package Marking Example

Figure 4: Spartan-3E CP132 and CPG132 Package Marking Example

www.xilinx.com

## Supply Voltages for the IOBs

The IOBs are powered by three supplies:

- 1. The  $V_{CCO}$  supplies, one for each of the FPGA's I/O banks, power the output drivers. The voltage on the  $V_{CCO}$  pins determines the voltage swing of the output signal.

- 2.  $V_{CCINT}$  is the main power supply for the FPGA's internal logic.

- V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

## I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also applies to input-only pins and dual-purpose I/O pins that are not actively involved in the currently-selected configuration mode.

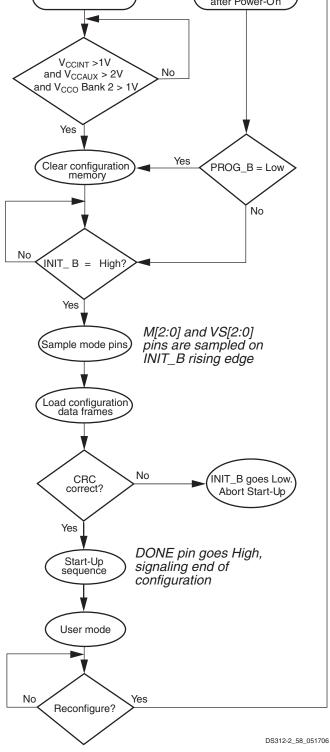

All I/O pins have ESD clamp diodes to their respective V<sub>CCO</sub> supply and from GND, as shown in Figure 5. The V<sub>CCINT</sub> (1.2V), V<sub>CCAUX</sub> (2.5V), and V<sub>CCO</sub> supplies can be applied in any order. Before the FPGA can start its configuration process, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> must have reached their respective minimum recommended operating levels indicated in Table 74. At this time, all output drivers are in a high-impedance state. V<sub>CCO</sub> Bank 2, V<sub>CCINT</sub>, and V<sub>CCAUX</sub> serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP input enables pull-up resistors on user-I/O and input-only pins from power-on throughout configuration. A High level on HSWAP disables the pull-up resistors, allowing the I/Os to float. HSWAP contains an internal pull-up resistor and defaults to High if left floating. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a default Low state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of configuration, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. Configuration data is then loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP input) throughout configuration.

At the end of configuration, the GSR net is released, placing the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective SR inputs.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the

beginning of design operation in the User mode. After the GTS net is released, all user I/Os go active while all unused I/Os are pulled down (PULLDOWN). The designer can control how the unused I/Os are terminated after GTS is released by setting the Bitstream Generator (BitGen) option UnusedPin to PULLUP, PULLDOWN, or FLOAT.

One clock cycle later (default), the Global Write Enable (GWE) net is released allowing the RAM and registers to change states. Once in User mode, any pull-up resistors enabled by HSWAP revert to the user settings and HSWAP is available as a general-purpose I/O. For more information on PULLUP and PULLDOWN, see Pull-Up and Pull-Down Resistors.

# Behavior of Unused I/O Pins After Configuration

By default, the Xilinx ISE development software automatically configures all unused I/O pins as input pins with individual internal pull-down resistors to GND.

This default behavior is controlled by the **UnusedPin** bitstream generator (BitGen) option, as described in Table 69.

## JTAG Boundary-Scan Capability

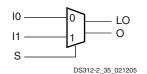

All Spartan-3E IOBs support boundary-scan testing compatible with IEEE 1149.1/1532 standards. During boundary-scan operations such as EXTEST and HIGHZ the pull-down resistor is active. See JTAG Mode for more information on programming via JTAG. The wide multiplexers can be used by the automatic tools or instantiated in a design using a component such as the F5MUX. The symbol, signals, and function are described in Figure 21, Table 12, and Table 13. The description is similar for the F6MUX, F7MUX, and F8MUX. Each has versions with a general output, local output, or both.

Figure 21: F5MUX with Local and General Outputs

#### Table 12: F5MUX Inputs and Outputs

| Signal | Function                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 10     | Input selected when S is Low                                                                                                      |

| 11     | Input selected when S is High                                                                                                     |

| S      | Select input                                                                                                                      |

| LO     | Local Output that connects to the F5 or FX CLB pins,<br>which use local feedback to the FXIN inputs to the<br>FiMUX for cascading |

| 0      | General Output that connects to the general-purpose combinatorial or registered outputs of the CLB                                |

#### Table 13: F5MUX Function

| Inputs |    |    | Outputs |    |  |

|--------|----|----|---------|----|--|

| S      | 10 | l1 | 0       | LO |  |

| 0      | 1  | Х  | 1       | 1  |  |

| 0      | 0  | Х  | 0       | 0  |  |

| 1      | Х  | 1  | 1       | 1  |  |

| 1      | Х  | 0  | 0       | 0  |  |

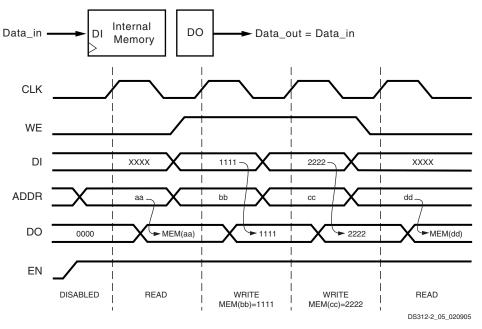

There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a output latch to the DO outputs. The timing for basic data access is shown in the

XILINX.

portions of Figure 33, Figure 34, and Figure 35 during which WE is Low.

Data also can be accessed on the DO outputs when asserting the WE input based on the value of the WRITE\_MODE attribute as described in Table 26.

#### Table 26: WRITE\_MODE Effect on Data Output Latches During Write Operations

| Write Mode                      | Effect on Same Port                                                                                                              | Effect on Opposite Port<br>(dual-port only with same address)   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| WRITE_FIRST<br>Read After Write | Data on DI and DIP inputs is written into specified RAM location and simultaneously appears on DO and DOP outputs.               | Invalidates data on DO and DOP outputs.                         |

| READ_FIRST<br>Read Before Write | Data from specified RAM location appears on DO and DOP outputs.<br>Data on DI and DIP inputs is written into specified location. | Data from specified RAM location appears on DO and DOP outputs. |

| NO_CHANGE<br>No Read on Write   | Data on DO and DOP outputs remains unchanged.<br>Data on DI and DIP inputs is written into specified<br>location.                | Invalidates data on DO and DOP outputs.                         |

Setting the WRITE\_MODE attribute to a value of WRITE\_FIRST, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE\_FIRST timing is shown in the portion of Figure 33 during which WE is High.

Setting the WRITE\_MODE attribute to a value of READ\_FIRST, data already stored in the addressed location passes to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ\_FIRST timing is shown in the portion of Figure 34 during which WE is High.

www.xilinx.com

## **Configuration Bitstream Image Sizes**

A specific Spartan-3E part type always requires a constant number of configuration bits, regardless of design complexity, as shown in Table 45. The configuration file size for a multiple-FPGA daisy-chain design roughly equals the sum of the individual file sizes.

## Table 45: Number of Bits to Program a Spartan-3EFPGA (Uncompressed Bitstreams)

| Spartan-3E FPGA | Number of<br>Configuration Bits |

|-----------------|---------------------------------|

| XC3S100E        | 581,344                         |

| XC3S250E        | 1,353,728                       |

| XC3S500E        | 2,270,208                       |

| XC3S1200E       | 3,841,184                       |

| XC3S1600E       | 5,969,696                       |

## **Pin Behavior During Configuration**

For additional information, refer to the "Configuration Pins and Behavior during Configuration" chapter in <u>UG332</u>.

Table 46 shows how various pins behave during the FPGAconfiguration process. The actual behavior depends on the

#### Table 46: Pin Behavior during Configuration

values applied to the M2, M1, and M0 mode select pins and the HSWAP pin. The mode select pins determine which of the I/O pins are borrowed during configuration and how they function. In JTAG configuration mode, no user-I/O pins are borrowed for configuration.

All user-I/O pins, input-only pins, and dual-purpose pins that are not actively involved in the currently-select configuration mode are high impedance (floating, three-stated, Hi-Z) during the configuration process. These pins are indicated in Table 46 as gray shaded table entries or cells.

The HSWAP input controls whether all user-I/O pins, input-only pins, and dual-purpose pins have a pull-up resistor to the supply rail or not. When HSWAP is Low, each pin has an internal pull-up resistor that is active throughout configuration. After configuration, pull-up and pull-down resistors are available in the FPGA application as described in Pull-Up and Pull-Down Resistors.

The yellow-shaded table entries or cells represent pins where the pull-up resistor is always enabled during configuration, regardless of the HSWAP input. The post-configuration behavior of these pins is defined by Bitstream Generator options as defined in Table 69.

| Pin Name                           | Master Serial | SPI (Serial<br>Flash) | BPI (Parallel<br>NOR Flash) | JTAG   | Slave Parallel | Slave Serial | I/O Bank <sup>(3)</sup> |

|------------------------------------|---------------|-----------------------|-----------------------------|--------|----------------|--------------|-------------------------|

| IO* (user-I/O)<br>IP* (input-only) |               |                       |                             |        |                |              | -                       |

| TDI                                | TDI           | TDI                   | TDI                         | TDI    | TDI            | TDI          | V <sub>CCAUX</sub>      |

| TMS                                | TMS           | TMS                   | TMS                         | TMS    | TMS            | TMS          | V <sub>CCAUX</sub>      |

| ТСК                                | TCK           | ТСК                   | TCK                         | TCK    | TCK            | ТСК          | V <sub>CCAUX</sub>      |

| TDO                                | TDO           | TDO                   | TDO                         | TDO    | TDO            | TDO          | V <sub>CCAUX</sub>      |

| PROG_B                             | PROG_B        | PROG_B                | PROG_B                      | PROG_B | PROG_B         | PROG_B       | V <sub>CCAUX</sub>      |

| DONE                               | DONE          | DONE                  | DONE                        | DONE   | DONE           | DONE         | V <sub>CCAUX</sub>      |

| HSWAP                              | HSWAP         | HSWAP                 | HSWAP                       | HSWAP  | HSWAP          | HSWAP        | 0                       |

| M2                                 | 0             | 0                     | 0                           | 1      | 1              | 1            | 2                       |

| M1                                 | 0             | 0                     | 1                           | 0      | 1              | 1            | 2                       |

| MO                                 | 0             | 1                     | 0 = Up<br>1 = Down          | 1      | 0              | 1            | 2                       |

| CCLK                               | CCLK (I/O)    | CCLK (I/O)            | CCLK (I/O)                  |        | CCLK (I)       | CCLK (I)     | 2                       |

| INIT_B                             | INIT_B        | INIT_B                | INIT_B                      |        | INIT_B         | INIT_B       | 2                       |

| CSO_B                              |               | CSO_B                 | CSO_B                       |        | CSO_B          |              | 2                       |

| DOUT/BUSY                          | DOUT          | DOUT                  | BUSY                        |        | BUSY           | DOUT         | 2                       |

| MOSI/CSI_B                         |               | MOSI                  | CSI_B                       |        | CSI_B          |              | 2                       |

| D7                                 |               |                       | D7                          |        | D7             |              | 2                       |

| D6                                 |               |                       | D6                          |        | D6             |              | 2                       |

| D5                                 |               |                       | D5                          |        | D5             |              | 2                       |

| D4                                 |               |                       | D4                          |        | D4             |              | 2                       |

| D3                                 |               |                       | D3                          |        | D3             |              | 2                       |

| D2                                 |               |                       | D2                          |        | D2             |              | 2                       |

| D1                                 |               |                       | D1                          |        | D1             |              | 2                       |

www.xilinx.com

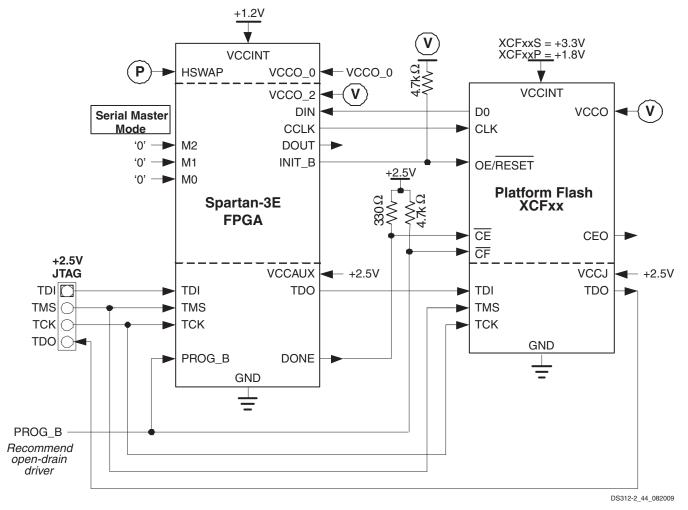

## **Master Serial Mode**

For additional information, refer to the "Master Serial Mode" chapter in  $\underline{\text{UG332}}$ .

In Master Serial mode (M[2:0] = <0:0:0>), the Spartan-3E FPGA configures itself from an attached Xilinx Platform

Flash PROM, as illustrated in Figure 51. The FPGA supplies the CCLK output clock from its internal oscillator to the attached Platform Flash PROM. In response, the Platform Flash PROM supplies bit-serial data to the FPGA's DIN input, and the FPGA accepts this data on each rising CCLK edge.

All mode select pins, M[2:0], must be Low when sampled, when the FPGA's INIT\_B output goes High. After configuration, when the FPGA's DONE output goes High, the mode select pins are available as full-featured user-I/O pins.

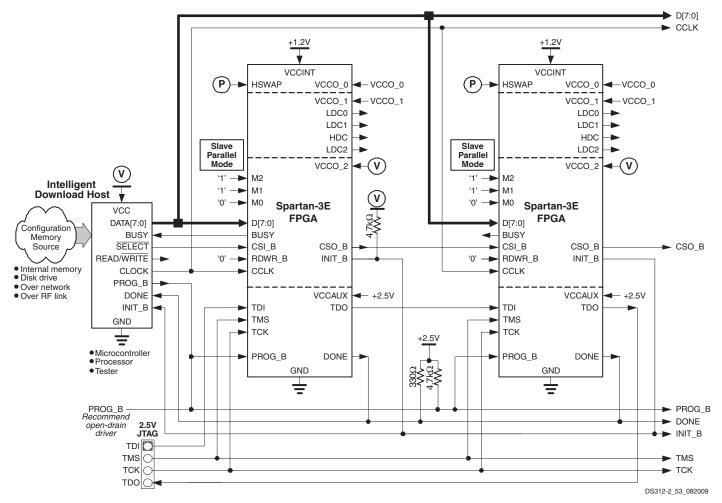

Figure 62: Daisy-Chaining using Slave Parallel Mode

### **Slave Serial Mode**

For additional information, refer to the "Slave Serial Mode" chapter in UG332.

In Slave Serial mode (M[2:0] = <1:1:1>), an external host such as a microprocessor or microcontroller writes serial configuration data into the FPGA, using the synchronous serial interface shown in Figure 63. The serial configuration data is presented on the FPGA's DIN input pin with sufficient setup time before each rising edge of the externally generated CCLK clock input. The intelligent host starts the configuration process by pulsing PROG\_B and monitoring that the INIT\_B pin goes High, indicating that the FPGA is ready to receive its first data. The host then continues supplying data and clock signals until either the DONE pin goes High, indicating a successful configuration, or until the INIT\_B pin goes Low, indicating a configuration error. The configuration process requires more clock cycles than indicated from the configuration file size. Additional clocks are required during the FPGA's start-up sequence, especially if the FPGA is programmed to wait for selected Digital Clock Managers (DCMs) to lock to their respective clock inputs (see Start-Up, page 105).

FPGA passes configuration data via its DOUT output pin to the next FPGA on the falling CCLK edge.

#### Table 66: Slave Serial Mode Connections

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| HSWAP    | Input                           | User I/O Pull-Up Control. When<br>Low during configuration, enables<br>pull-up resistors in all I/O pins to<br>respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-up during configuration<br>1: No pull-ups                                                                                                                                                                                                                                                                                                  | Drive at valid logic level<br>throughout configuration.                                                   | User I/O                                                                                               |

| M[2:0]   | Input                           | Mode Select. Selects the FPGA<br>configuration mode. See Design<br>Considerations for the HSWAP,<br>M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                                                                    | M2 = 1, M1 = 1, M0 = 1 Sampled<br>when INIT_B goes High.                                                  | User I/O                                                                                               |

| DIN      | Input                           | Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Serial data provided by host.<br>FPGA captures data on rising<br>CCLK edge.                               | User I/O                                                                                               |

| CCLK     | Input                           | <b>Configuration Clock</b> . If CCLK<br>PCB trace is long or has multiple<br>connections, terminate this output<br>to maintain signal integrity. See<br>CCLK Design Considerations.                                                                                                                                                                                                                                                                                                                              | External clock.                                                                                           | User I/O                                                                                               |

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active<br>Low. Goes Low at start of<br>configuration during Initialization<br>memory clearing process.<br>Released at end of memory<br>clearing, when mode select pins<br>are sampled. In daisy-chain<br>applications, this signal requires<br>an external 4.7 kΩ pull-up resistor<br>to VCCO_2.                                                                                                                                                                               | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the application, drive INIT_B<br>High.                                          |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                    | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low.<br>When asserted Low for 500 ns or<br>longer, forces the FPGA to restart<br>its configuration process by<br>clearing configuration memory and<br>resetting the DONE and INIT_B<br>pins once PROG_B returns High.<br>Recommend external 4.7 kΩ<br>pull-up resistor to 2.5V. Internal<br>pull-up value may be weaker (see<br>Table 78). If driving externally with<br>a 3.3V output, use an open-drain<br>or open-collector driver or use a<br>current limiting series resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

## **EXILINX**.

## **EXILINX**.

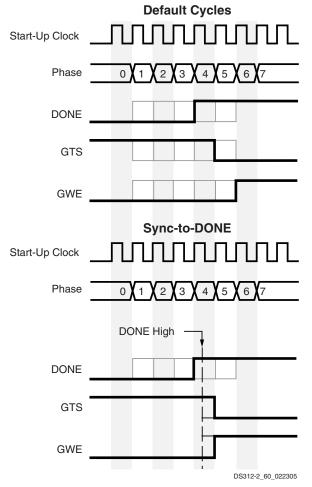

## Start-Up

At the end of configuration, the FPGA automatically pulses the Global Set/Reset (GSR) signal, placing all flip-flops in a known state. After configuration completes, the FPGA switches over to the user application loaded into the FPGA. The sequence and timing of how the FPGA switches over is programmable as is the clock source controlling the sequence.

The default start-up sequence appears in Figure 68, where the Global Three-State signal (GTS) is released one clock cycle after DONE goes High. This sequence allows the DONE signal to enable or disable any external logic used during configuration before the user application in the FPGA starts driving output signals. One clock cycle later, the Global Write Enable (GWE) signal is released. This allows signals to propagate within the FPGA before any clocked storage elements such as flip-flops and block ROM are enabled.

Figure 68: Default Start-Up Sequence

The function of the dual-purpose I/O pins, such as M[2:0], VS[2:0], HSWAP, and A[23:0], also changes when the DONE pin goes High. When DONE is High, these pins

become user I/Os. Like all user-I/O pins, GTS controls when the dual-purpose pins can drive out.

The relative timing of configuration events is programmed via the Bitstream Generator (BitGen) options in the Xilinx development software. For example, the GTS and GWE events can be programmed to wait for all the DONE pins to High on all the devices in a multiple-FPGA daisy-chain, forcing the FPGAs to start synchronously. Similarly, the start-up sequence can be paused at any stage, waiting for selected DCMs to lock to their respective input clock signals. See also Stabilizing DCM Clocks Before User Mode.

By default, the start-up sequence is synchronized to CCLK. Alternatively, the start-up sequence can be synchronized to a user-specified clock from within the FPGA application using the STARTUP\_SPARTAN3E library primitive and by setting the *StartupClk* bitstream generator option. The FPGA application can optionally assert the GSR and GTS signals via the STARTUP\_SPARTAN3E primitive. For JTAG configuration, the start-up sequence can be synchronized to the TCK clock input.

## **Power Supply Specifications**

#### Table 74: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                 | Min | Max | Units |

|---------------------|---------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply | 0.8 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the $V_{CCO}$ Bank 2 supply   | 0.4 | 1.0 | V     |

#### Notes:

To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 75: Supply Voltage Ramp Rate

| Symbol              | Description                                                 | Min | Мах | Units |

|---------------------|-------------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid V <sub>CCINT</sub> supply level | 0.2 | 50  | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid $V_{CCAUX}$ supply level        | 0.2 | 50  | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid $V_{CCO}$ Bank 2 supply level   | 0.2 | 50  | ms    |

#### Notes:

V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 76: Supply Voltage Levels Necessary for Preserving RAM Contents

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

#### Notes:

1. RAM contents include configuration data.

V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

#### Table 94: Output Timing Adjustments for IOB

| LVCMOS25 w    | Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following |       | Adjus<br>Be | l the<br>tment<br>low | Units |

|---------------|---------------------------------------------------------------------------------------------|-------|-------------|-----------------------|-------|

| Signal Standa |                                                                                             |       | Speed       | Grade                 | -     |

|               |                                                                                             | _     | -5          | -4                    |       |

| Single-Ended  | Standards                                                                                   | 5     |             | r                     | 1     |

| LVTTL         | Slow                                                                                        | 2 mA  | 5.20        | 5.41                  | ns    |

|               |                                                                                             | 4 mA  | 2.32        | 2.41                  | ns    |

|               |                                                                                             | 6 mA  | 1.83        | 1.90                  | ns    |

|               |                                                                                             | 8 mA  | 0.64        | 0.67                  | ns    |

|               |                                                                                             | 12 mA | 0.68        | 0.70                  | ns    |

|               |                                                                                             | 16 mA | 0.41        | 0.43                  | ns    |

|               | Fast                                                                                        | 2 mA  | 4.80        | 5.00                  | ns    |

|               |                                                                                             | 4 mA  | 1.88        | 1.96                  | ns    |

|               |                                                                                             | 6 mA  | 1.39        | 1.45                  | ns    |

|               |                                                                                             | 8 mA  | 0.32        | 0.34                  | ns    |

|               |                                                                                             | 12 mA | 0.28        | 0.30                  | ns    |

|               |                                                                                             | 16 mA | 0.28        | 0.30                  | ns    |

| LVCMOS33      | Slow                                                                                        | 2 mA  | 5.08        | 5.29                  | ns    |

|               |                                                                                             | 4 mA  | 1.82        | 1.89                  | ns    |

|               |                                                                                             | 6 mA  | 1.00        | 1.04                  | ns    |

|               |                                                                                             | 8 mA  | 0.66        | 0.69                  | ns    |

|               |                                                                                             | 12 mA | 0.40        | 0.42                  | ns    |

|               |                                                                                             | 16 mA | 0.41        | 0.43                  | ns    |

|               | Fast                                                                                        | 2 mA  | 4.68        | 4.87                  | ns    |

|               |                                                                                             | 4 mA  | 1.46        | 1.52                  | ns    |

|               |                                                                                             | 6 mA  | 0.38        | 0.39                  | ns    |

|               |                                                                                             | 8 mA  | 0.33        | 0.34                  | ns    |

|               |                                                                                             | 12 mA | 0.28        | 0.30                  | ns    |

|               |                                                                                             | 16 mA | 0.28        | 0.30                  | ns    |

| LVCMOS25      | Slow                                                                                        | 2 mA  | 4.04        | 4.21                  | ns    |

|               |                                                                                             | 4 mA  | 2.17        | 2.26                  | ns    |

|               |                                                                                             | 6 mA  | 1.46        | 1.52                  | ns    |

|               |                                                                                             | 8 mA  | 1.04        | 1.08                  | ns    |

|               |                                                                                             | 12 mA | 0.65        | 0.68                  | ns    |

|               | Fast                                                                                        | 2 mA  | 3.53        | 3.67                  | ns    |

|               |                                                                                             | 4 mA  | 1.65        | 1.72                  | ns    |

|               |                                                                                             | 6 mA  | 0.44        | 0.46                  | ns    |

|               |                                                                                             | 8 mA  | 0.20        | 0.21                  | ns    |

|               |                                                                                             | 12 mA | 0           | 0                     | ns    |

#### Table 94: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following<br>Signal Standard (IOSTANDARD) |        |      | Add the<br>Adjustment<br>Below<br>Speed Grade |       | Units |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------|------|-----------------------------------------------|-------|-------|--|

|                                                                                                                             |        |      | -5                                            | -4    |       |  |

|                                                                                                                             |        |      |                                               |       |       |  |

| LVCMOS18                                                                                                                    | Slow   | 2 mA | 5.03                                          | 5.24  | ns    |  |

|                                                                                                                             |        | 4 mA | 3.08                                          | 3.21  | ns    |  |

|                                                                                                                             |        | 6 mA | 2.39                                          | 2.49  | ns    |  |

|                                                                                                                             |        | 8 mA | 1.83                                          | 1.90  | ns    |  |

|                                                                                                                             | Fast   | 2 mA | 3.98                                          | 4.15  | ns    |  |

|                                                                                                                             |        | 4 mA | 2.04                                          | 2.13  | ns    |  |

|                                                                                                                             |        | 6 mA | 1.09                                          | 1.14  | ns    |  |

|                                                                                                                             |        | 8 mA | 0.72                                          | 0.75  | ns    |  |

| LVCMOS15                                                                                                                    | Slow   | 2 mA | 4.49                                          | 4.68  | ns    |  |

|                                                                                                                             |        | 4 mA | 3.81                                          | 3.97  | ns    |  |

|                                                                                                                             |        | 6 mA | 2.99                                          | 3.11  | ns    |  |

|                                                                                                                             | Fast   | 2 mA | 3.25                                          | 3.38  | ns    |  |

|                                                                                                                             |        | 4 mA | 2.59                                          | 2.70  | ns    |  |

|                                                                                                                             |        | 6 mA | 1.47                                          | 1.53  | ns    |  |

| LVCMOS12                                                                                                                    | Slow   | 2 mA | 6.36                                          | 6.63  | ns    |  |

|                                                                                                                             | Fast   | 2 mA | 4.26                                          | 4.44  | ns    |  |

| HSTL_I_18                                                                                                                   |        |      | 0.33                                          | 0.34  | ns    |  |

| HSTL_III_18                                                                                                                 |        |      | 0.53                                          | 0.55  | ns    |  |

| PCI33_3                                                                                                                     |        |      | 0.44                                          | 0.46  | ns    |  |

| PCI66_3                                                                                                                     |        |      | 0.44                                          | 0.46  | ns    |  |

| SSTL18_I                                                                                                                    |        |      | 0.24                                          | 0.25  | ns    |  |

| SSTL2_I                                                                                                                     |        |      | -0.20                                         | -0.20 | ns    |  |

| Differential Sta                                                                                                            | ndards |      | 1                                             |       |       |  |

| LVDS_25                                                                                                                     |        |      | -0.55                                         | -0.55 | ns    |  |

| BLVDS_25                                                                                                                    |        |      | 0.04                                          | 0.04  | ns    |  |

| MINI_LVDS_25                                                                                                                |        |      | -0.56                                         | -0.56 | ns    |  |

| LVPECL_25                                                                                                                   |        |      | Input                                         | Only  | ns    |  |

| RSDS_25                                                                                                                     |        |      | -0.48                                         | -0.48 | ns    |  |

| DIFF_HSTL_I_18                                                                                                              |        |      | 0.42                                          | 0.42  | ns    |  |

| DIFF_HSTL_III_18                                                                                                            |        |      | 0.53                                          | 0.55  | ns    |  |

| DIFF_SSTL18_                                                                                                                | I      |      | 0.40                                          | 0.40  | ns    |  |

| DIFF_SSTL2_I                                                                                                                |        |      | 0.44                                          | 0.44  | ns    |  |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77, Table 80, and Table 82.

- 2. These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

#### Table 99: CLB Distributed RAM Switching Characteristics

| Symbol                              | Description                                                                                                                       | -5   |      | -4   |      | Units |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol                              | Description                                                                                                                       | Min  | Max  | Min  | Max  | Units |

| Clock-to-Outpu                      | t Times                                                                                                                           |      |      |      |      |       |

| Т <sub>SHCKO</sub>                  | Time from the active edge at the CLK input to data appearing on the distributed RAM output                                        | -    | 2.05 | -    | 2.35 | ns    |

| Setup Times                         |                                                                                                                                   |      |      |      |      |       |

| T <sub>DS</sub>                     | Setup time of data at the BX or BY input before the active transition at the CLK input of the distributed RAM                     |      |      | 0.46 | -    | ns    |

| T <sub>AS</sub>                     | Setup time of the F/G address inputs before the active transition at the CLK input of the distributed RAM                         | 0.46 | -    | 0.52 | -    | ns    |

| T <sub>WS</sub>                     | Setup time of the write enable input before the active transition at the CLK input of the distributed RAM                         |      | -    | 0.40 | -    | ns    |

| Hold Times                          |                                                                                                                                   |      |      |      |      |       |

| T <sub>DH</sub>                     | Hold time of the BX, BY data inputs after the active transition at the CLK input of the distributed RAM                           | 0.13 | -    | 0.15 | -    | ns    |

| $T_{AH,} T_{WH}$                    | Hold time of the F/G address inputs or the write enable input after the active transition at the CLK input of the distributed RAM |      | -    | 0    | -    | ns    |

| Clock Pulse Wi                      | dth                                                                                                                               |      |      |      |      |       |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                                      | 0.88 | -    | 1.01 | -    | ns    |

#### Table 100: CLB Shift Register Switching Characteristics

| Symbol                              | Description                                                                                                  |      | -5   |      | -4   |       |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|--|

| Symbol                              |                                                                                                              |      | Max  | Min  | Max  | Units |  |

| Clock-to-Output                     | Times                                                                                                        |      |      |      |      |       |  |

| T <sub>REG</sub>                    | Time from the active edge at the CLK input to data appearing on the shift register output                    |      | 3.62 | -    | 4.16 | ns    |  |

| Setup Times                         | Setup Times                                                                                                  |      |      |      |      |       |  |

| T <sub>SRLDS</sub>                  | Setup time of data at the BX or BY input before the active transition at the CLK input of the shift register | 0.41 | -    | 0.46 | -    | ns    |  |

| Hold Times                          |                                                                                                              |      |      |      |      | L     |  |

| T <sub>SRLDH</sub>                  | Hold time of the BX or BY data input after the active transition at the CLK input of the shift register      | 0.14 | -    | 0.16 | -    | ns    |  |

| Clock Pulse Wie                     | dth                                                                                                          |      |      |      |      |       |  |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                 | 0.88 | -    | 1.01 | -    | ns    |  |

## **Clock Buffer/Multiplexer Switching Characteristics**

#### Table 101: Clock Distribution Switching Characteristics

|                                                                                                             |                   | Maximum |      | Units |  |

|-------------------------------------------------------------------------------------------------------------|-------------------|---------|------|-------|--|

| Description                                                                                                 | Symbol            | Speed   |      |       |  |

|                                                                                                             |                   | -5      | -4   | -     |  |

| Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output delay                                       | T <sub>GIO</sub>  | 1.46    | 1.46 | ns    |  |

| Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1 inputs. Same as BUFGCE enable CE-input | T <sub>GSI</sub>  | 0.55    | 0.63 | ns    |  |

| Frequency of signals distributed on global buffers (all sides)                                              | F <sub>BUFG</sub> | 333     | 311  | MHz   |  |

##

#### Table 117: Timing for the Slave Parallel Configuration Mode (Cont'd)

| Symbol             | Description                                         |                                            |                                       | All Spee | All Speed Grades |       |  |  |  |

|--------------------|-----------------------------------------------------|--------------------------------------------|---------------------------------------|----------|------------------|-------|--|--|--|

| Symbol Description |                                                     |                                            |                                       | Min      | Max              | Units |  |  |  |

| Clock Timing       | Clock Timing                                        |                                            |                                       |          |                  |       |  |  |  |

| Т <sub>ССН</sub>   | The High pulse width at the Co                      | The High pulse width at the CCLK input pin |                                       |          | -                | ns    |  |  |  |

| T <sub>CCL</sub>   | The Low pulse width at the CO                       | The Low pulse width at the CCLK input pin  |                                       |          | -                | ns    |  |  |  |

| F <sub>CCPAR</sub> | Frequency of the clock signal at the CCLK input pin | No bitstream compression                   | Not using the BUSY pin <sup>(2)</sup> | 0        | 50               | MHz   |  |  |  |

|                    |                                                     |                                            | Using the BUSY pin                    | 0        | 66               | MHz   |  |  |  |

|                    | V                                                   |                                            | ompression                            | 0        | 20               | MHz   |  |  |  |

Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77.

- 2. In the Slave Parallel mode, it is necessary to use the BUSY pin when the CCLK frequency exceeds this maximum specification.

- 3. Some Xilinx documents refer to Parallel modes as "SelectMAP" modes.

## **Footprint Migration Differences**

Table 136 summarizes any footprint and functionality differences between the XC3S100E, the XC3S250E, and the XC3S500E FPGAs that may affect easy migration between devices in the CP132 package. There are 14 such balls. All other pins not listed in Table 136 unconditionally migrate between Spartan-3E devices available in the CP132 package.

The XC3S100E is duplicated on both the left and right sides of the table to show migrations to and from the XC3S250E and the XC3S500E. The arrows indicate the direction for easy migration. A double-ended arrow ( $\leftarrow \rightarrow$ ) indicates that the two pins have identical functionality. A left-facing arrow ( $\leftarrow$ ) indicates that the pin on the device on the right unconditionally migrates to the pin on the device on the left. It may be possible to migrate the opposite direction depending on the I/O configuration. For example, an I/O pin (Type = I/O) can migrate to an input-only pin (Type = INPUT) if the I/O pin is configured as an input.

The XC3S100E FPGA in the CP132 package has four fewer BPI-mode address lines than the XC3S250E and XC3S500E.

| CP132<br>Ball | Bank  | XC3S100E<br>Type | Migration     | XC3S250E<br>Type | Migration         | XC3S500E<br>Type | Migration | XC3S100E<br>Type |

|---------------|-------|------------------|---------------|------------------|-------------------|------------------|-----------|------------------|

| A12           | 0     | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |

| B4            | 0     | INPUT            | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | INPUT            |

| B11           | 0     | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |

| B12           | 0     | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |

| C4            | 0     | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |

| C11           | 0     | INPUT            | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | INPUT            |

| D1            | 3     | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |

| D2            | 3     | I/O              | $\rightarrow$ | I/O (Diff)       | $\leftrightarrow$ | I/O (Diff)       | ÷         | I/O              |

| K3            | 3     | VREF(INPUT)      | $\rightarrow$ | VREF(I/O)        | $\leftrightarrow$ | VREF(I/O)        | ÷         | VREF(INPUT)      |

| M9            | 2     | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |

| M10           | 2     | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |

| N9            | 2     | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |

| N10           | 2     | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |

| P11           | 2     | VREF(INPUT)      | $\rightarrow$ | VREF(I/O)        | $\leftrightarrow$ | VREF(I/O)        | ÷         | VREF(INPUT)      |

| DIFFERI       | ENCES |                  | 14            |                  | 0                 |                  | 14        |                  |

#### Table 136: CP132 Footprint Migration Differences

Legend:

$\leftrightarrow$  This pin is identical on the device on the left and the right.

This pin can unconditionally migrate from the device on the left to the device on the right. Migration in the other direction may be possible depending on how the pin is configured for the device on the right.

+ This pin can unconditionally migrate from the device on the right to the device on the left. Migration in the other direction may be possible depending on how the pin is configured for the device on the left.

#### Table 137: TQ144 Package Pinout (Cont'd)

| Bank | XC3S100E Pin Name      | XC3S250E Pin Name      | TQ144 Pin | Туре                                 |

|------|------------------------|------------------------|-----------|--------------------------------------|

| 2    | IP                     | IP                     | P38       | INPUT                                |

| 2    | IP                     | IP                     | P41       | INPUT                                |

| 2    | IP                     | IP                     | P69       | INPUT                                |

| 2    | IP_L03N_2/VREF_2       | IP_L03N_2/VREF_2       | P48       | VREF                                 |

| 2    | IP_L03P_2              | IP_L03P_2              | P47       | INPUT                                |

| 2    | IP_L06N_2/M2/GCLK1     | IP_L06N_2/M2/GCLK1     | P57       | DUAL/GCLK                            |

| 2    | IP_L06P_2/RDWR_B/GCLK0 | IP_L06P_2/RDWR_B/GCLK0 | P56       | DUAL/GCLK                            |

| 2    | VCCO_2                 | VCCO_2                 | P42       | VCCO                                 |

| 2    | VCCO_2                 | VCCO_2                 | P49       | VCCO                                 |

| 2    | VCCO_2                 | VCCO_2                 | P64       | VCCO                                 |

| 3    | IP/VREF_3              | IO/VREF_3              | P31       | 100E: VREF(INPUT)<br>250E: VREF(I/O) |

| 3    | IO_L01N_3              | IO_L01N_3              | P3        | I/O                                  |

| 3    | IO_L01P_3              | IO_L01P_3              | P2        | I/O                                  |

| 3    | IO_L02N_3/VREF_3       | IO_L02N_3/VREF_3       | P5        | VREF                                 |

| 3    | IO_L02P_3              | IO_L02P_3              | P4        | I/O                                  |

| 3    | IO_L03N_3              | IO_L03N_3              | P8        | I/O                                  |

| 3    | IO_L03P_3              | IO_L03P_3              | P7        | I/O                                  |

| 3    | IO_L04N_3/LHCLK1       | IO_L04N_3/LHCLK1       | P15       | LHCLK                                |

| 3    | IO_L04P_3/LHCLK0       | IO_L04P_3/LHCLK0       | P14       | LHCLK                                |

| 3    | IO_L05N_3/LHCLK3/IRDY2 | IO_L05N_3/LHCLK3       | P17       | LHCLK                                |

| 3    | IO_L05P_3/LHCLK2       | IO_L05P_3/LHCLK2       | P16       | LHCLK                                |

| 3    | IO_L06N_3/LHCLK5       | IO_L06N_3/LHCLK5       | P21       | LHCLK                                |

| 3    | IO_L06P_3/LHCLK4/TRDY2 | IO_L06P_3/LHCLK4       | P20       | LHCLK                                |

| 3    | IO_L07N_3/LHCLK7       | IO_L07N_3/LHCLK7       | P23       | LHCLK                                |

| 3    | IO_L07P_3/LHCLK6       | IO_L07P_3/LHCLK6       | P22       | LHCLK                                |

| 3    | IO_L08N_3              | IO_L08N_3              | P26       | I/O                                  |

| 3    | IO_L08P_3              | IO_L08P_3              | P25       | I/O                                  |

| 3    | IO_L09N_3              | IO_L09N_3              | P33       | I/O                                  |

| 3    | IO_L09P_3              | IO_L09P_3              | P32       | I/O                                  |

| 3    | IO_L10N_3              | IO_L10N_3              | P35       | I/O                                  |

| 3    | IO_L10P_3              | IO_L10P_3              | P34       | I/O                                  |

| 3    | IP                     | IP                     | P6        | INPUT                                |

| 3    | IO                     | IP                     | P10       | 100E: I/O                            |

|      |                        |                        |           | 250E: INPUT                          |

| 3    | IP                     | IP                     | P18       | INPUT                                |

| 3    | IP                     | IP                     | P24       | INPUT                                |

| 3    | Ю                      | IP                     | P29       | 100E: I/O<br>250E: INPUT             |

| 3    | IP                     | IP                     | P36       | INPUT                                |

| 3    | IP/VREF_3              | IP/VREF_3              | P12       | VREF                                 |

| 3    | VCCO_3                 | VCCO_3                 | P13       | VCCO                                 |

| 3    | VCCO_3                 | VCCO_3                 | P28       | VCCO                                 |

| GND  | GND                    | GND                    | P11       | GND                                  |

| GND  | GND                    | GND                    | P19       | GND                                  |

www.xilinx.com

## PQ208: 208-pin Plastic Quad Flat Package

The 208-pin plastic quad flat package, PQ208, supports two different Spartan-3E FPGAs, including the XC3S250E and the XC3S500E.

Table 141 lists all the PQ208 package pins. They are sorted by bank number and then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at:

http://www.xilinx.com/support/documentation/data\_sheets /s3e\_pin.zip

## **Pinout Table**

| Table 141: PQ208 Package Pinout |                                  |              |      |  |  |  |

|---------------------------------|----------------------------------|--------------|------|--|--|--|

| Bank                            | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре |  |  |  |

| 0                               | Ю                                | P187         | I/O  |  |  |  |

| 0                               | IO/VREF_0                        | P179         | VREF |  |  |  |

| 0                               | IO_L01N_0                        | P161         | I/O  |  |  |  |

| 0                               | IO_L01P_0                        | P160         | I/O  |  |  |  |

| 0                               | IO_L02N_0/VREF_0                 | P163         | VREF |  |  |  |

| 0                               | IO_L02P_0                        | P162         | I/O  |  |  |  |

| 0                               | IO_L03N_0                        | P165         | I/O  |  |  |  |

| 0                               | IO_L03P_0                        | P164         | I/O  |  |  |  |

| 0                               | IO_L04N_0/VREF_0                 | P168         | VREF |  |  |  |

| 0                               | IO_L04P_0                        | P167         | I/O  |  |  |  |

| 0                               | IO_L05N_0                        | P172         | I/O  |  |  |  |

| 0                               | IO_L05P_0                        | P171         | I/O  |  |  |  |

| 0                               | IO_L07N_0/GCLK5                  | P178         | GCLK |  |  |  |

| 0                               | IO_L07P_0/GCLK4                  | P177         | GCLK |  |  |  |

| 0                               | IO_L08N_0/GCLK7                  | P181         | GCLK |  |  |  |

| 0                               | IO_L08P_0/GCLK6                  | P180         | GCLK |  |  |  |

| 0                               | IO_L10N_0/GCLK11                 | P186         | GCLK |  |  |  |

| 0                               | IO_L10P_0/GCLK10                 | P185         | GCLK |  |  |  |

| 0                               | IO_L11N_0                        | P190         | I/O  |  |  |  |

| 0                               | IO_L11P_0                        | P189         | I/O  |  |  |  |

| 0                               | IO_L12N_0/VREF_0                 | P193         | VREF |  |  |  |

| 0                               | IO_L12P_0                        | P192         | I/O  |  |  |  |

| 0                               | IO_L13N_0                        | P197         | I/O  |  |  |  |

| 0                               | IO_L13P_0                        | P196         | I/O  |  |  |  |

| 0                               | IO_L14N_0/VREF_0                 | P200         | VREF |  |  |  |

| 0                               | IO_L14P_0                        | P199         | I/O  |  |  |  |

| 0                               | IO_L15N_0                        | P203         | I/O  |  |  |  |

| Table 141: PQ208 Package Pinout |                                  |              |      |  |  |  |  |  |

|---------------------------------|----------------------------------|--------------|------|--|--|--|--|--|

| Bank                            | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре |  |  |  |  |  |

| 0                               | 10                               | P187         | I/O  |  |  |  |  |  |

| 0                               | IO/VREF_0                        | P179         | VREF |  |  |  |  |  |

| 0                               | IO_L01N_0                        | P161         | I/O  |  |  |  |  |  |

| 0                               | IO_L01P_0                        | P160         | I/O  |  |  |  |  |  |

| 0                               | IO_L02N_0/VREF_0                 | P163         | VREF |  |  |  |  |  |

| 0                               | IO_L02P_0                        | P162         | I/O  |  |  |  |  |  |

| 0                               | IO_L03N_0                        | P165         | I/O  |  |  |  |  |  |

| 0                               | IO_L03P_0                        | P164         | I/O  |  |  |  |  |  |

| 0                               | IO_L04N_0/VREF_0                 | P168         | VREF |  |  |  |  |  |

| 0                               | IO_L04P_0                        | P167         | I/O  |  |  |  |  |  |

| 0                               | IO_L05N_0                        | P172         | I/O  |  |  |  |  |  |

| 0                               | IO_L05P_0                        | P171         | I/O  |  |  |  |  |  |

| 0                               | IO_L07N_0/GCLK5                  | P178         | GCLK |  |  |  |  |  |

| 0                               | IO_L07P_0/GCLK4                  | P177         | GCLK |  |  |  |  |  |

| 0                               | IO_L08N_0/GCLK7                  | P181         | GCLK |  |  |  |  |  |

| 0                               | IO_L08P_0/GCLK6                  | P180         | GCLK |  |  |  |  |  |

| 0                               | IO_L10N_0/GCLK11                 | P186         | GCLK |  |  |  |  |  |

| 0                               | IO_L10P_0/GCLK10                 | P185         | GCLK |  |  |  |  |  |

| 0                               | IO_L11N_0                        | P190         | I/O  |  |  |  |  |  |

| 0                               | IO_L11P_0                        | P189         | I/O  |  |  |  |  |  |

| 0                               | IO_L12N_0/VREF_0                 | P193         | VREF |  |  |  |  |  |

| 0                               | IO_L12P_0                        | P192         | I/O  |  |  |  |  |  |

| 0                               | IO_L13N_0                        | P197         | I/O  |  |  |  |  |  |

| 0                               | IO_L13P_0                        | P196         | I/O  |  |  |  |  |  |

| 0                               | IO_L14N_0/VREF_0                 | P200         | VREF |  |  |  |  |  |

| Table | 141: | PQ208 | Package | Pinout | (Cont'd) |

|-------|------|-------|---------|--------|----------|

|-------|------|-------|---------|--------|----------|

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре       |

|------|----------------------------------|--------------|------------|

| 0    | IO_L15P_0                        | P202         | I/O        |

| 0    | IO_L16N_0/HSWAP                  | P206         | DUAL       |

| 0    | IO_L16P_0                        | P205         | I/O        |

| 0    | IP                               | P159         | INPUT      |

| 0    | IP                               | P169         | INPUT      |

| 0    | IP                               | P194         | INPUT      |

| 0    | IP                               | P204         | INPUT      |

| 0    | IP_L06N_0                        | P175         | INPUT      |

| 0    | IP_L06P_0                        | P174         | INPUT      |

| 0    | IP_L09N_0/GCLK9                  | P184         | GCLK       |

| 0    | IP_L09P_0/GCLK8                  | P183         | GCLK       |

| 0    | VCCO_0                           | P176         | VCCO       |

| 0    | VCCO_0                           | P191         | VCCO       |

| 0    | VCCO_0                           | P201         | VCCO       |

| 1    | IO_L01N_1/A15                    | P107         | DUAL       |

| 1    | IO_L01P_1/A16                    | P106         | DUAL       |

| 1    | IO_L02N_1/A13                    | P109         | DUAL       |

| 1    | IO_L02P_1/A14                    | P108         | DUAL       |

| 1    | IO_L03N_1/VREF_1                 | P113         | VREF       |

| 1    | IO_L03P_1                        | P112         | I/O        |

| 1    | IO_L04N_1                        | P116         | I/O        |

| 1    | IO_L04P_1                        | P115         | I/O        |

| 1    | IO_L05N_1/A11                    | P120         | DUAL       |

| 1    | IO_L05P_1/A12                    | P119         | DUAL       |

| 1    | IO_L06N_1/VREF_1                 | P123         | VREF       |

| 1    | IO_L06P_1                        | P122         | I/O        |

| 1    | IO_L07N_1/A9/RHCLK1              | P127         | RHCLK/DUAL |

| 1    | IO_L07P_1/A10/RHCLK0             | P126         | RHCLK/DUAL |

| 1    | IO_L08N_1/A7/RHCLK3              | P129         | RHCLK/DUAL |

| 1    | IO_L08P_1/A8/RHCLK2              | P128         | RHCLK/DUAL |

| 1    | IO_L09N_1/A5/RHCLK5              | P133         | RHCLK/DUAL |

| 1    | IO_L09P_1/A6/RHCLK4              | P132         | RHCLK/DUAL |

| 1    | IO_L10N_1/A3/RHCLK7              | P135         | RHCLK/DUAL |

| 1    | IO_L10P_1/A4/RHCLK6              | P134         | RHCLK/DUAL |

| 1    | IO_L11N_1/A1                     | P138         | DUAL       |

| 1    | IO_L11P_1/A2                     | P137         | DUAL       |

| 1    | IO_L12N_1/A0                     | P140         | DUAL       |

| 1    | IO_L12P_1                        | P139         | I/O        |

| 1    | IO_L13N_1                        | P145         | I/O        |

| 1    | IO_L13P_1                        | P144         | I/O        |

| 1    | IO_L14N_1                        | P147         | I/O        |

| 1    | IO_L14P_1                        | P146         | I/O        |

### Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name          | XC3S500E Pin Name          | XC3S1200E Pin Name         | FT256<br>Ball | Туре                                    |

|------|----------------------------|----------------------------|----------------------------|---------------|-----------------------------------------|

| 3    | IO_L06P_3                  | IO_L06P_3                  | IO_L06P_3                  | G5            | I/O                                     |

| 3    | IO_L07N_3                  | IO_L07N_3                  | IO_L07N_3                  | G2            | I/O                                     |

| 3    | IO_L07P_3                  | IO_L07P_3                  | IO_L07P_3                  | G3            | I/O                                     |

| 3    | IO_L08N_3/LHCLK1           | IO_L08N_3/LHCLK1           | IO_L08N_3/LHCLK1           | H6            | LHCLK                                   |

| 3    | IO_L08P_3/LHCLK0           | IO_L08P_3/LHCLK0           | IO_L08P_3/LHCLK0           | H5            | LHCLK                                   |

| 3    | IO_L09N_3/LHCLK3/<br>IRDY2 | IO_L09N_3/LHCLK3/<br>IRDY2 | IO_L09N_3/LHCLK3/<br>IRDY2 | H4            | LHCLK                                   |

| 3    | IO_L09P_3/LHCLK2           | IO_L09P_3/LHCLK2           | IO_L09P_3/LHCLK2           | H3            | LHCLK                                   |

| 3    | IO_L10N_3/LHCLK5           | IO_L10N_3/LHCLK5           | IO_L10N_3/LHCLK5           | J3            | LHCLK                                   |

| 3    | IO_L10P_3/LHCLK4/<br>TRDY2 | IO_L10P_3/LHCLK4/<br>TRDY2 | IO_L10P_3/LHCLK4/<br>TRDY2 | J2            | LHCLK                                   |

| 3    | IO_L11N_3/LHCLK7           | IO_L11N_3/LHCLK7           | IO_L11N_3/LHCLK7           | J4            | LHCLK                                   |

| 3    | IO_L11P_3/LHCLK6           | IO_L11P_3/LHCLK6           | IO_L11P_3/LHCLK6           | J5            | LHCLK                                   |

| 3    | IO_L12N_3                  | IO_L12N_3                  | IO_L12N_3                  | K1            | I/O                                     |

| 3    | IO_L12P_3                  | IO_L12P_3                  | IO_L12P_3                  | J1            | I/O                                     |