Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 612                                                           |

| Number of Logic Elements/Cells | 5508                                                          |

| Total RAM Bits                 | 221184                                                        |

| Number of I/O                  | 92                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 132-TFBGA, CSPBGA                                             |

| Supplier Device Package        | 132-CSPBGA (8x8)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s250e-4cpg132i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                |

| 03/21/05 | 1.1     | Added XC3S250E in CP132 package to Table 2. Corrected number of differential I/O pairs for CP132 package. Added package markings for QFP packages (Figure 2) and CP132/CPG132 packages (Figure 4).                                                                                                                                                                                                     |

| 11/23/05 | 2.0     | Added differential HSTL and SSTL I/O standards. Updated Table 2 to indicate number of input-only pins. Added Production Stepping information, including example top marking diagrams.                                                                                                                                                                                                                  |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Added XC3S100E in CP132 package and updated I/O counts for the XC3S1600E in FG320 package (Table 2). Added information about dual markings for –5C and –4I product combinations to Package Marking.                                                                                                                                                         |

| 11/09/06 | 3.4     | Added 66 MHz PCI support and links to the Xilinx PCI LogiCORE data sheet. Indicated that Stepping 1 parts are Production status. Promoted Module 1 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                             |

| 04/18/08 | 3.7     | Added XC3S500E VQG100 package. Added reference to XA Automotive version. Updated links.                                                                                                                                                                                                                                                                                                                |

| 08/26/09 | 3.8     | Added paragraph to Configuration indicating the device supports MultiBoot configuration. Added package sizes to Table 2. Described the speed grade and temperature range guarantee for devices having a single mark in paragraph 3 under Package Marking. Deleted Pb-Free Packaging example under Ordering Information. Revised information under Production Stepping. Revised description of Table 3. |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.  Updated Table 2 footprint size of PQ208.                                                                                                                                                                                                                                                                                 |

### **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### **AUTOMOTIVE APPLICATIONS DISCLAIMER**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

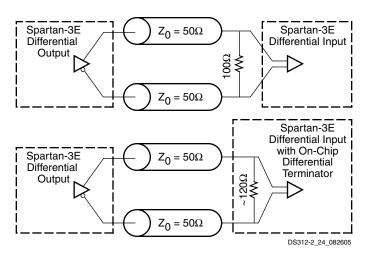

Figure 11: Differential Inputs and Outputs

## **Pull-Up and Pull-Down Resistors**

Pull-up and pull-down resistors inside each IOB optionally force a floating I/O or Input-only pin to a determined state. Pull-up and pull-down resistors are commonly applied to unused I/Os, inputs, and three-state outputs, but can be used on any I/O or Input-only pin. The pull-up resistor connects an IOB to  $V_{CCO}$  through a resistor. The resistance value depends on the  $V_{CCO}$  voltage (see Module 3, DC and Switching Characteristics for the specifications). The pull-down resistor similarly connects an IOB to ground with a resistor. The PULLUP and PULLDOWN attributes and library primitives turn on these optional resistors.

By default, PULLDOWN resistors terminate all unused I/O and Input-only pins. Unused I/O and Input-only pins can alternatively be set to PULLUP or FLOAT. To change the unused I/O Pad setting, set the Bitstream Generator (BitGen) option *UnusedPin* to PULLUP, PULLDOWN, or FLOAT. The *UnusedPin* option is accessed through the Properties for Generate Programming File in ISE. See Bitstream Generator (BitGen) Options.

During configuration a Low logic level on the HSWAP pin activates pull-up resistors on all I/O and Input-only pins not actively used in the selected configuration mode.

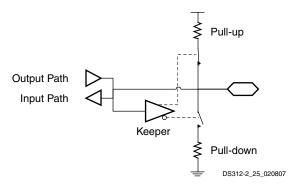

# **Keeper Circuit**

Each I/O has an optional keeper circuit (see Figure 12) that keeps bus lines from floating when not being actively driven. The KEEPER circuit retains the last logic level on a line after all drivers have been turned off. Apply the KEEPER attribute or use the KEEPER library primitive to use the KEEPER circuitry. Pull-up and pull-down resistors override the KEEPER settings.

Figure 12: Keeper Circuit

### **Slew Rate Control and Drive Strength**

Each IOB has a slew-rate control that sets the output switching edge-rate for LVCMOS and LVTTL outputs. The SLEW attribute controls the slew rate and can either be set to SLOW (default) or FAST.

Each LVCMOS and LVTTL output additionally supports up to six different drive current strengths as shown in Table 8. To adjust the drive strength for each output, the DRIVE attribute is set to the desired drive strength: 2, 4, 6, 8, 12, and 16. Unless otherwise specified in the FPGA application, the software default IOSTANDARD is LVCMOS25, SLOW slew rate, and 12 mA output drive.

Table 8: Programmable Output Drive Current

| IOSTANDARD | Output Drive Current (mA) |   |   |   |    |    |  |  |  |

|------------|---------------------------|---|---|---|----|----|--|--|--|

|            | 2                         | 4 | 6 | 8 | 12 | 16 |  |  |  |

| LVTTL      | ~                         | ~ | ~ | ~ | ~  | ~  |  |  |  |

| LVCMOS33   | >                         | ~ | ~ | ~ | ~  | ~  |  |  |  |

| LVCMOS25   | >                         | ~ | ~ | ~ | ~  | -  |  |  |  |

| LVCMOS18   | >                         | ~ | ~ | ~ | -  | -  |  |  |  |

| LVCMOS15   | >                         | ~ | ~ | - | -  | -  |  |  |  |

| LVCMOS12   | >                         | - | - | - | -  | -  |  |  |  |

High output current drive strength and FAST output slew rates generally result in fastest I/O performance. However, these same settings generally also result in transmission line effects on the printed circuit board (PCB) for all but the shortest board traces. Each IOB has independent slew rate and drive strength controls. Use the slowest slew rate and lowest output drive current that meets the performance requirements for the end application.

Likewise, due to lead inductance, a given package supports a limited number of simultaneous switching outputs (SSOs) when using fast, high-drive outputs. Only use fast, high-drive outputs when required by the application.

# **Clocking Infrastructure**

For additional information, refer to the "Using Global Clock Resources" chapter in UG331.

The Spartan-3E clocking infrastructure, shown in Figure 45, provides a series of low-capacitance, low-skew interconnect lines well-suited to carrying high-frequency signals throughout the FPGA. The infrastructure also includes the clock inputs and BUFGMUX clock buffers/multiplexers. The Xilinx Place-and-Route (PAR) software automatically routes high-fanout clock signals using these resources.

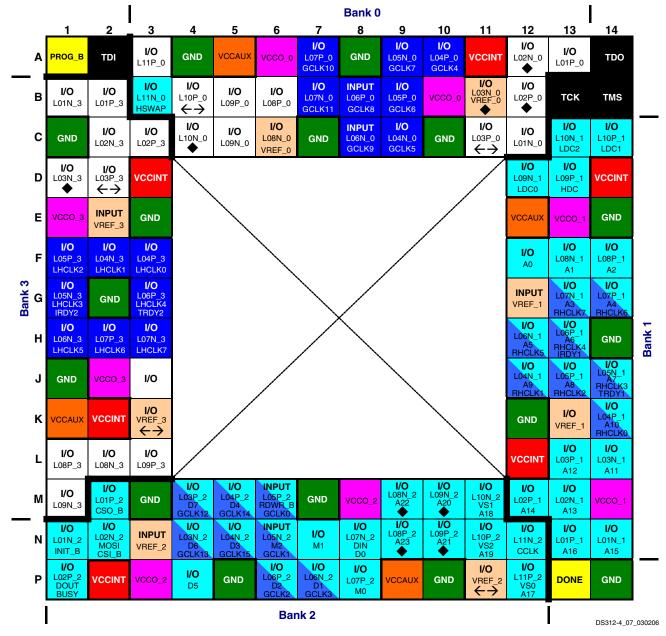

# **Clock Inputs**

Clock pins accept external clock signals and connect directly to DCMs and BUFGMUX elements. Each Spartan-3E FPGA has:

- 16 Global Clock inputs (GCLK0 through GCLK15) located along the top and bottom edges of the FPGA

- 8 Right-Half Clock inputs (RHCLK0 through RHCLK7) located along the right edge

- 8 Left-Half Clock inputs (LHCLK0 through LHCLK7) located along the left edge

Clock inputs optionally connect directly to DCMs using dedicated connections. Table 30, Table 31, and Table 32 show the clock inputs that best feed a specific DCM within a given Spartan-3E part number. Different Spartan-3E FPGA densities have different numbers of DCMs. The XC3S1200E and XC3S1600E are the only two densities with the left- and right-edge DCMs.

Each clock input is also optionally a user-I/O pin and connects to internal interconnect. Some clock pad pins are input-only pins as indicated in Module 4, Pinout Descriptions.

#### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

# **Clock Buffers/Multiplexers**

Clock Buffers/Multiplexers either drive clock input signals directly onto a clock line (BUFG) or optionally provide a multiplexer to switch between two unrelated, possibly asynchronous clock signals (BUFGMUX).

Each BUFGMUX element, shown in Figure 46, is a 2-to-1 multiplexer. The select line, S, chooses which of the two inputs, I0 or I1, drives the BUFGMUX's output signal, O, as described in Table 40. The switching from one clock to the other is glitch-less, and done in such a way that the output High and Low times are never shorter than the shortest

High or Low time of either input clock. The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock (I0 or I1). This setup time is specified as TGSI in Table 101, page 136. Violating this setup time requirement possibly results in an undefined runt pulse output.

Table 40: BUFGMUX Select Mechanism

| S Input | O Output |

|---------|----------|

| 0       | I0 Input |

| 1       | I1 Input |

The BUFG clock buffer primitive drives a single clock signal onto the clock network and is essentially the same element as a BUFGMUX, just without the clock select mechanism. Similarly, the BUFGCE primitive creates an enabled clock buffer using the BUFGMUX select mechanism.

The I0 and I1 inputs to an BUFGMUX element originate from clock input pins, DCMs, or Double-Line interconnect, as shown in Figure 46. As shown in Figure 45, there are 24 BUFGMUX elements distributed around the four edges of the device. Clock signals from the four BUFGMUX elements at the top edge and the four at the bottom edge are truly global and connect to all clocking quadrants. The eight left-edge BUFGMUX elements only connect to the two clock quadrants in the left half of the device. Similarly, the eight right-edge BUFGMUX elements only connect to the right half of the device.

BUFGMUX elements are organized in pairs and share I0 and I1 connections with adjacent BUFGMUX elements from a common clock switch matrix as shown in Figure 46. For example, the input on I0 of one BUFGMUX is also a shared input to I1 of the adjacent BUFGMUX.

The clock switch matrix for the left- and right-edge BUFGMUX elements receive signals from any of the three following sources: an LHCLK or RHCLK pin as appropriate, a Double-Line interconnect, or a DCM in the XC3S1200E and XC3S1600E devices.

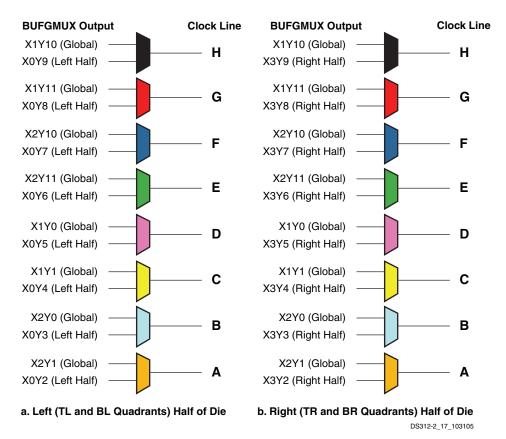

Figure 47: Clock Sources for the Eight Clock Lines within a Clock Quadrant

The outputs of the top or bottom BUFGMUX elements connect to two vertical spines, each comprising four vertical clock lines as shown in Figure 45. At the center of the die, these clock signals connect to the eight-line horizontal clock spine.

Outputs of the left and right BUFGMUX elements are routed onto the left or right horizontal spines, each comprising eight horizontal clock lines.

Each of the eight clock signals in a clock quadrant derives either from a global clock signal or a half clock signal. In other words, there are up to 24 total potential clock inputs to the FPGA, eight of which can connect to clocked elements in a single clock quadrant. Figure 47 shows how the clock lines in each quadrant are selected from associated BUFGMUX sources. For example, if quadrant clock 'A' in the bottom left (BL) quadrant originates from BUFGMUX\_X2Y1, then the clock signal from BUFGMUX\_X0Y2 is unavailable in the bottom left quadrant. However, the top left (TL) quadrant clock 'A' can still solely use the output from either BUFGMUX\_X2Y1 or BUFGMUX\_X0Y2 as the source.

To minimize the dynamic power dissipation of the clock network, the Xilinx development software automatically disables all clock segments not in use.

### **Direct Connections**

Direct connect lines route signals to neighboring tiles: vertically, horizontally, and diagonally. These lines most often drive a signal from a "source" tile to a double, hex, or long line and conversely from the longer interconnect back to a direct line accessing a "destination" tile.

# **Global Controls (STARTUP\_SPARTAN3E)**

In addition to the general-purpose interconnect, Spartan-3E FPGAs have two global logic control signals, as described in Table 43. These signals are available to the FPGA application via the STARTUP SPARTAN3E primitive.

Table 43: Spartan-3E Global Logic Control Signals

| Global Control<br>Input | Description                                                                                                                                                                                                                  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GSR                     | Global Set/Reset: When High, asynchronously places all registers and flip-flops in their initial state (see Initialization, page 31). Asserted automatically during the FPGA configuration process (see Start-Up, page 105). |

| GTS                     | Global Three-State: When High, asynchronously forces all I/O pins to a high-impedance state (Hi-Z, three-state).                                                                                                             |

The Global Set/Reset (GSR) signal replaces the global reset signal included in many ASIC-style designs. Use the GSR control instead of a separate global reset signal in the design to free up CLB inputs, resulting in a smaller, more efficient design. Similarly, the GSR signal is asserted automatically during the FPGA configuration process, guaranteeing that the FPGA starts-up in a known state.

The STARTUP\_SPARTAN3E primitive also includes two other signals used specifically during configuration. The MBT signals are for Dynamically Loading Multiple Configuration Images Using MultiBoot Option, page 91. The CLK input is an alternate clock for configuration Start-Up, page 105.

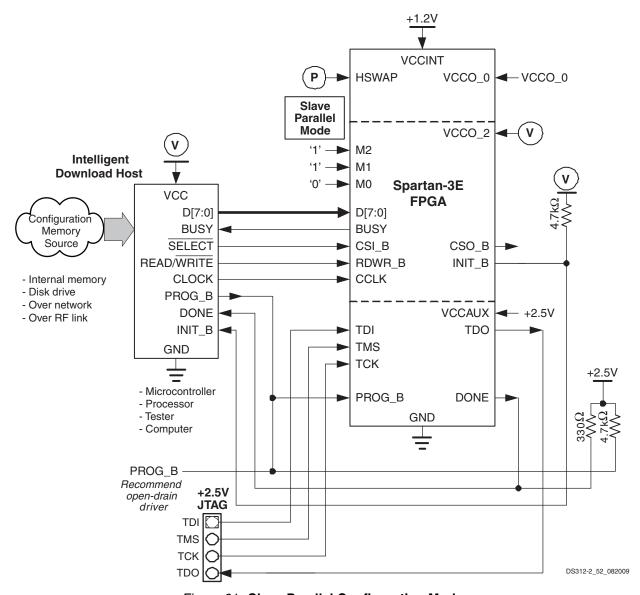

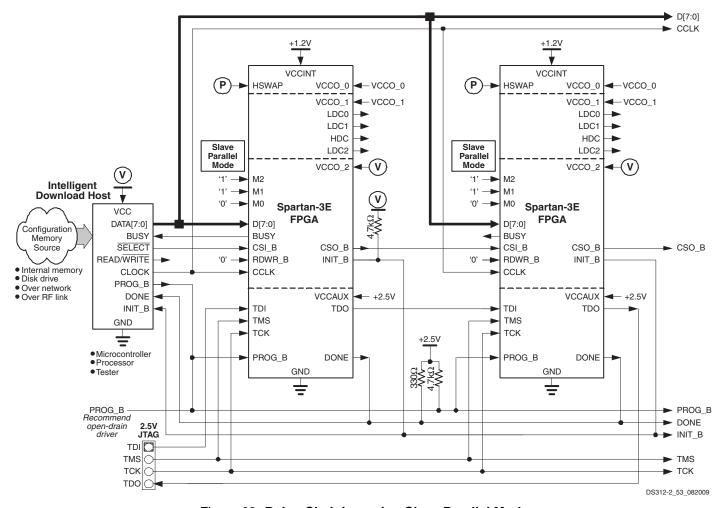

Figure 61: Slave Parallel Configuration Mode

### Slave Parallel Mode

For additional information, refer to the "Slave Parallel (SelectMAP) Mode" chapter in <u>UG332</u>.

In Slave Parallel mode (M[2:0] = <1:1:0>), an external host, such as a microprocessor or microcontroller, writes byte-wide configuration data into the FPGA, using a typical peripheral interface as shown in Figure 61.

The external download host starts the configuration process by pulsing PROG\_B and monitoring that the INIT\_B pin goes High, indicating that the FPGA is ready to receive its first data. The host asserts the active-Low chip-select signal (CSI\_B) and the active-Low Write signal (RDWR\_B). The host then continues supplying data and clock signals until either the FPGA's DONE pin goes High, indicating a successful configuration, or until the FPGA's INIT\_B pin goes Low, indicating a configuration error.

The FPGA captures data on the rising CCLK edge. If the CCLK frequency exceeds 50 MHz, then the host must also monitor the FPGA's BUSY output. If the FPGA asserts BUSY High, the host must hold the data for an additional clock cycle, until BUSY returns Low. If the CCLK frequency is 50 MHz or below, the BUSY pin may be ignored but actively drives during configuration.

The configuration process requires more clock cycles than indicated from the configuration file size. Additional clocks are required during the FPGA's start-up sequence, especially if the FPGA is programmed to wait for selected Digital Clock Managers (DCMs) to lock to their respective clock inputs (see Start-Up, page 105).

If the Slave Parallel interface is only used to configure the FPGA, never to read data back, then the RDWR\_B signal

Figure 62: Daisy-Chaining using Slave Parallel Mode

#### **Slave Serial Mode**

For additional information, refer to the "Slave Serial Mode" chapter in <u>UG332</u>.

In Slave Serial mode (M[2:0] = <1:1:1>), an external host such as a microprocessor or microcontroller writes serial configuration data into the FPGA, using the synchronous serial interface shown in Figure 63. The serial configuration data is presented on the FPGA's DIN input pin with sufficient setup time before each rising edge of the externally generated CCLK clock input.

The intelligent host starts the configuration process by pulsing PROG\_B and monitoring that the INIT\_B pin goes High, indicating that the FPGA is ready to receive its first data. The host then continues supplying data and clock signals until either the DONE pin goes High, indicating a successful configuration, or until the INIT\_B pin goes Low, indicating a configuration error. The configuration process requires more clock cycles than indicated from the configuration file size. Additional clocks are required during the FPGA's start-up sequence, especially if the FPGA is programmed to wait for selected Digital Clock Managers (DCMs) to lock to their respective clock inputs (see Start-Up, page 105).

# **Bitstream Generator (BitGen) Options**

For additional information, refer to the "Configuration Bitstream Generator (BitGen) Settings" chapter in UG332.

Various Spartan-3E FPGA functions are controlled by specific bits in the configuration bitstream image. These

values are specified when creating the bitstream image with the Bitstream Generator (BitGen) software.

Table 69 provides a list of all BitGen options for Spartan-3E FPGAs.

Table 69: Spartan-3E FPGA Bitstream Generator (BitGen) Options

| Option Name Pins/Function Affected |                                                                                                         | Values<br>( <u>default</u> )       | Description                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ConfigRate                         | CCLK,<br>Configuration                                                                                  | <u>1,</u> 3, 6,<br>12, 25, 50      | Sets the approximate frequency, in MHz, of the internal oscillator using for Master Serial, SPI, and BPI configuration modes. The internal oscillator powers up at its lowest frequency, and the new setting is loaded as part of the configuration bitstream. The software default value is 1 (~1.5 MHz) starting with ISE 8.1, Service Pack 1. |

| StartupClk                         | Configuration,<br>Startup                                                                               | <u>Cclk</u>                        | <b>Default.</b> The CCLK signal (internally or externally generated) controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up.                                                                                                                                                             |

|                                    |                                                                                                         | UserClk                            | A clock signal from within the FPGA application controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up. The FPGA application supplies the user clock on the CLK pin on the STARTUP_SPARTAN3E primitive.                                                                                  |

|                                    |                                                                                                         | Jtag                               | The JTAG TCK input controls the startup sequence when the FPGA transitions from the configuration mode to the user mode. See Start-Up.                                                                                                                                                                                                           |

| UnusedPin                          | Unused I/O                                                                                              | Pulldown                           | Default. All unused I/O pins and input-only pins have a pull-down resistor to GND.                                                                                                                                                                                                                                                               |

|                                    | Pins                                                                                                    | Pullup                             | All unused I/O pins and input-only pins have a pull-up resistor to the VCCO_# supply for its associated I/O bank.                                                                                                                                                                                                                                |

|                                    |                                                                                                         | Pullnone                           | All unused I/O pins and input-only pins are left floating (Hi-Z, high-impedance, three-state). Use external pull-up or pull-down resistors or logic to apply a valid signal level.                                                                                                                                                               |

| DONE_cycle                         | DONE pin,<br>Configuration<br>Startup                                                                   | 1, 2, 3, <u>4,</u><br>5, 6         | Selects the Configuration Startup phase that activates the FPGA's DONE pin. See Start-Up.                                                                                                                                                                                                                                                        |

| GWE_cycle                          | All flip-flops,<br>LUT RAMs, and<br>SRL16 shift<br>registers, Block<br>RAM,<br>Configuration<br>Startup | 1, 2, 3, 4,<br>5, <u><b>6</b></u>  | Selects the Configuration Startup phase that asserts the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). It also enables block RAM read and write operations. See Start-Up.                                                                                                                                |

|                                    |                                                                                                         | Done                               | Waits for the DONE pin input to go High before asserting the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). Block RAM read and write operations are enabled at this time.                                                                                                                                 |

|                                    |                                                                                                         | Keep                               | Retains the current GWE_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| GTS_cycle                          | All I/O pins,<br>Configuration                                                                          | 1, 2, 3, 4,<br><u><b>5</b></u> , 6 | Selects the Configuration Startup phase that releases the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point. See Start-Up.                                                                                                                       |

|                                    |                                                                                                         | Done                               | Waits for the DONE pin input to go High before releasing the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point.                                                                                                                                  |

|                                    |                                                                                                         | Keep                               | Retains the current GTS_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| LCK_cycle                          | DCMs,                                                                                                   | NoWait                             | The FPGA does not wait for selected DCMs to lock before completing configuration.                                                                                                                                                                                                                                                                |

|                                    | Configuration<br>Startup                                                                                | 0, 1, 2, 3,<br>4, 5, 6             | If one or more DCMs in the design have the STARTUP_WAIT attribute set to TRUE, the FPGA waits for such DCMs to acquire their respective input clock and assert their LOCKED output. This setting selects the Configuration Startup phase where the FPGA waits for the DCMs to lock.                                                              |

| DonePin                            | DONE pin                                                                                                | <u>Pullup</u>                      | Internally connects a pull-up resistor between DONE pin and $V_{CCAUX}$ . An external 330 $\Omega$ pull-up resistor to $V_{CCAUX}$ is still recommended.                                                                                                                                                                                         |

|                                    |                                                                                                         | Pullnone                           | No internal pull-up resistor on DONE pin. An external 330 $\Omega$ pull-up resistor to $V_{\mbox{\scriptsize CCAUX}}$ is required.                                                                                                                                                                                                               |

# **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for Stepping 0 are compatible with Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device.

# **Differences Between Steppings**

Table 71 summarizes the feature and performance differences between Stepping 0 devices and Stepping 1 devices.

Table 71: Differences between Spartan-3E Production Stepping Levels

|                                                                                                               | Stepping 0                                                                                  | Stepping 1                                                |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| Production status                                                                                             | Production from 2005 to 2007                                                                | Production starting<br>March 2006                         |  |

| Speed grade and operating conditions                                                                          | -4C only                                                                                    | -4C, -4I, -5C                                             |  |

| JTAG ID code                                                                                                  | Different revision fields. See                                                              | e Table 67.                                               |  |

| DCM DLL maximum input frequency                                                                               | 90 MHz<br>(200 MHz for XC3S1200E)                                                           | 240 MHz (-4 speed grade)<br>275 MHz (-5 speed grade)      |  |

| DCM DFS output frequency range(s)                                                                             | Split ranges at 5 – 90 MHz and<br>220 – 307 MHz<br>(single range 5 – 307 MHz for XC3S1200E) | Continuous range:<br>5 – 311 MHz (-4)<br>5 – 333 MHz (-5) |  |

| Supports multi-FPGA daisy-chain configurations from SPI Flash                                                 | No, single FPGA only                                                                        | Yes                                                       |  |

| JTAG configuration supported when FPGA in BPI mode with a valid image in the attached parallel NOR Flash PROM | No <sup>(1)</sup>                                                                           | Yes                                                       |  |

| JTAG EXTEST, INTEST, SAMPLE support                                                                           | Yes: XC3S100E, XC3S250E, XC3S500E<br>No <sup>(2)</sup> : XC3S1200E, XC3S1600E               | Yes<br>All Devices                                        |  |

| Power sequencing when using HSWAP Pull-Up                                                                     | Requires V <sub>CCINT</sub> before V <sub>CCAUX</sub>                                       | Any sequence                                              |  |

| PCI compliance                                                                                                | No                                                                                          | Yes                                                       |  |

#### Notes:

- 1. Workarounds exist. See Stepping 0 Limitations when Reprogramming via JTAG if FPGA Set for BPI Configuration.

- 2. JTAG BYPASS and JTAG configuration are supported

# Ordering a Later Stepping

-5C and -4I devices, and -4C devices (with date codes 0901 (2009) and later) always support the Stepping 1 feature set independent of the stepping code. Optionally, to order only Stepping 1 for the -4C devices, append an "S1" suffix to the standard ordering code, where '1' is the stepping number, as indicated in Table 72.

Table 72: Spartan-3E Optional Stepping Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None        | Production |

| 1                  | S1          | Production |

### **Software Version Requirements**

Production Spartan-3E applications must be processed using the Xilinx ISE 8.1i, Service Pack 3 or later development software, using the v1.21 or later speed files. The ISE 8.1i software implements critical bitstream generator updates.

For additional information on Spartan-3E development software and known issues, see the following Answer Record:

Xilinx Answer #22253 http://www.xilinx.com/support/answers/22253.htm Spartan-3 FPGA Family: DC and Switching Characteristics

# **General Recommended Operating Conditions**

#### Table 77: General Recommended Operating Conditions

| Symbol                           | De                                          |                               | Min        | Nominal | Max                      | Units                  |    |

|----------------------------------|---------------------------------------------|-------------------------------|------------|---------|--------------------------|------------------------|----|

| T <sub>J</sub>                   | Junction temperature                        | Commercial                    | 0          | _       | 85                       | °C                     |    |

|                                  |                                             | Industrial                    | -40        | _       | 100                      | °C                     |    |

| V <sub>CCINT</sub>               | Internal supply voltage                     |                               |            |         | 1.200                    | 1.260                  | V  |

| V <sub>CCO</sub> <sup>(1)</sup>  | Output driver supply voltage                |                               |            | 1.100   | -                        | 3.465                  | V  |

| V <sub>CCAUX</sub>               | Auxiliary supply voltage                    |                               |            | 2.375   | 2.500                    | 2.625                  | V  |

| V <sub>IN</sub> <sup>(2,3)</sup> | Input voltage extremes to avoid             | I/O, Input-only, and          | IP or IO_# | -0.5    | _                        | V <sub>CCO</sub> + 0.5 | V  |

|                                  | turning on I/O protection diodes            | Dual-Purpose pins (4)         | -0.5       | _       | V <sub>CCO</sub> + 0.5   | V                      |    |

|                                  |                                             | Dedicated pins <sup>(6)</sup> | -0.5       | _       | V <sub>CCAUX</sub> + 0.5 | V                      |    |

| T <sub>IN</sub>                  | Input signal transition time <sup>(7)</sup> |                               |            | -       | _                        | 500                    | ns |

#### Notes:

- This V<sub>CCO</sub> range spans the lowest and highest operating voltages for all supported I/O standards. Table 80 lists the recommended V<sub>CCO</sub> range specific to each of the single-ended I/O standards, and Table 82 lists that specific to the differential standards.

- Input voltages outside the recommended range require the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Refer to Table 73.

- See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- Each of the User I/O and Dual-Purpose pins is associated with one of the four banks'  $V_{CCO}$  rails. Meeting the  $V_{IN}$  limit ensures that the internal diode junctions that exist between these pins and their associated  $V_{CCO}$  and GND rails do not turn on. The absolute maximum rating

- For single-ended signals that are placed on a differential-capable I/O,  $V_{IN}$  of -0.2V to -0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*. 5.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- Measured between 10% and 90%  $V_{CCO}$ . Follow <u>Signal Integrity</u> recommendations. 7.

Spartan-3 FPGA Family: DC and Switching Characteristics

#### Table 88: Setup and Hold Times for the IOB Input Path

|                                                                                                                                                                         |                                                                                                            |                                                  | IFD    |            | Speed | Grade |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|------------|-------|-------|-------|

| Symbol                                                                                                                                                                  | Description                                                                                                | Conditions                                       | DELAY_ | Device     | -5    | -4    | Units |

|                                                                                                                                                                         |                                                                                                            |                                                  | VALUE= |            | Min   | Min   |       |

| Setup Tim                                                                                                                                                               | es                                                                                                         |                                                  |        |            |       |       |       |

| T <sub>IOPICK</sub> Time from the setup of data at the Input pin to the active transition at the ICLK input of the Input Flip-Flop (IFF). No Input Delay is programmed. |                                                                                                            | LVCMOS25 <sup>(2)</sup> ,<br>IFD_DELAY_VALUE = 0 | 0      | All        | 1.84  | 2.12  | ns    |

| T <sub>IOPICKD</sub>                                                                                                                                                    | Time from the setup of data at                                                                             | LVCMOS25 <sup>(2)</sup> ,                        | 2      | XC3S100E   | 6.12  | 7.01  | ns    |

|                                                                                                                                                                         | the Input pin to the active transition at the IFF's ICLK input. The Input Delay is programmed.             | IFD_DELAY_VALUE = default software setting       | 3      | All Others | 6.76  | 7.72  |       |

| <b>Hold Time</b>                                                                                                                                                        | s                                                                                                          |                                                  |        |            |       |       | •     |

| Time from the active transition at the IFF's ICLK input to the point where data must be held at the Input pin. No Input Delay is programmed.                            |                                                                                                            | LVCMOS25 <sup>(3)</sup> ,<br>IFD_DELAY_VALUE = 0 | 0      | All        | -0.76 | -0.76 | ns    |

| T <sub>IOICKPD</sub>                                                                                                                                                    | Time from the active transition at                                                                         | LVCMOS25 <sup>(3)</sup> ,                        | 2      | XC3S100E   | -3.93 | -3.93 | ns    |

|                                                                                                                                                                         | the IFF's ICLK input to the point where data must be held at the Input pin. The Input Delay is programmed. | IFD_DELAY_VALUE = default software setting       | 3      | All Others | -3.50 | -3.50 |       |

| Set/Reset                                                                                                                                                               | Pulse Width                                                                                                |                                                  |        |            |       |       |       |

| T <sub>RPW_IOB</sub>                                                                                                                                                    | Minimum pulse width to SR control input on IOB                                                             |                                                  |        | All        | 1.57  | 1.80  | ns    |

#### Notes:

- The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

- This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, add the appropriate Input adjustment from Table 91.

- These hold times require adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. If this is true, subtract the appropriate Input adjustment from Table 91. When the hold time is negative, it is possible to change the data before the clock's active

#### Table 89: Sample Window (Source Synchronous)

| Symbol            | Description                                             | Мах                                                                                                                                                                                                                                                                                                                                   | Units |

|-------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| T <sub>SAMP</sub> | Setup and hold capture window of an IOB input flip-flop | The input capture sample window value is highly specific to a particular application, device, package, I/O standard, I/O placement, DCM usage, and clock buffer. Please consult the appropriate Xilinx application note for application-specific values.  • XAPP485: 1:7 Deserialization in Spartan-3E FPGAs at Speeds Up to 666 Mbps | ps    |

### **Timing Measurement Methodology**

When measuring timing parameters at the programmable I/Os, different signal standards call for different test conditions. Table 95 lists the conditions to use for each standard.

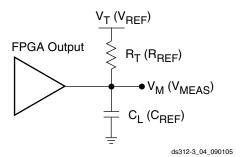

The method for measuring Input timing is as follows: A signal that swings between a Low logic level of  $V_L$  and a High logic level of  $V_H$  is applied to the Input under test. Some standards also require the application of a bias voltage to the  $V_{REF}$  pins of a given bank to properly set the input-switching threshold. The measurement point of the Input signal  $(V_M)$  is commonly located halfway between  $V_L$  and  $V_H.$

The Output test setup is shown in Figure 72. A termination voltage  $V_T$  is applied to the termination resistor  $R_T$ , the other end of which is connected to the Output. For each standard,  $R_T$  and  $V_T$  generally take on the standard values recommended for minimizing signal reflections. If the standard does not ordinarily use terminations (e.g.,

LVCMOS, LVTTL), then  $R_T$  is set to  $1M\Omega$  to indicate an open connection, and  $V_T$  is set to zero. The same measurement point  $(V_M)$  that was used at the Input is also used at the Output.

#### Notes:

The names shown in parentheses are used in the IBIS file.

Figure 72: Output Test Setup

Table 95: Test Methods for Timing Measurement at I/Os

| Signal Standard<br>(IOSTANDARD) |         |                      | Inputs                   |                          | Outputs       |                    | Inputs and<br>Outputs |

|---------------------------------|---------|----------------------|--------------------------|--------------------------|---------------|--------------------|-----------------------|

|                                 |         | V <sub>REF</sub> (V) | V <sub>L</sub> (V)       | V <sub>H</sub> (V)       | $R_T(\Omega)$ | V <sub>T</sub> (V) | V <sub>M</sub> (V)    |

| Single-End                      | ed      |                      |                          |                          |               |                    |                       |

| LVTTL                           |         | -                    | 0                        | 3.3                      | 1M            | 0                  | 1.4                   |

| LVCMOS33                        |         | -                    | 0                        | 3.3                      | 1M            | 0                  | 1.65                  |

| LVCMOS25                        |         | -                    | 0                        | 2.5                      | 1M            | 0                  | 1.25                  |

| LVCMOS18                        |         | -                    | 0                        | 1.8                      | 1M            | 0                  | 0.9                   |

| LVCMOS15                        |         | -                    | 0                        | 1.5                      | 1M            | 0                  | 0.75                  |

| LVCMOS12                        |         | -                    | 0                        | 1.2                      | 1M            | 0                  | 0.6                   |

| PCI33_3                         | Rising  | -                    | Note 3                   | Note 3                   | 25            | 0                  | 0.94                  |

|                                 | Falling |                      |                          |                          | 25            | 3.3                | 2.03                  |

| PCI66_3                         | Rising  | -                    | Note 3                   | Note 3                   | 25            | 0                  | 0.94                  |

|                                 | Falling |                      |                          |                          | 25            | 3.3                | 2.03                  |

| HSTL_I_18                       |         | 0.9                  | V <sub>REF</sub> - 0.5   | V <sub>REF</sub> + 0.5   | 50            | 0.9                | V <sub>REF</sub>      |

| HSTL_III_18                     | 3       | 1.1                  | V <sub>REF</sub> - 0.5   | V <sub>REF</sub> + 0.5   | 50            | 1.8                | V <sub>REF</sub>      |

| SSTL18_I                        |         | 0.9                  | V <sub>REF</sub> - 0.5   | V <sub>REF</sub> + 0.5   | 50            | 0.9                | V <sub>REF</sub>      |

| SSTL2_I                         |         | 1.25                 | V <sub>REF</sub> – 0.75  | V <sub>REF</sub> + 0.75  | 50            | 1.25               | V <sub>REF</sub>      |

| Differential                    |         |                      |                          |                          |               |                    |                       |

| LVDS_25                         |         | -                    | V <sub>ICM</sub> - 0.125 | V <sub>ICM</sub> + 0.125 | 50            | 1.2                | V <sub>ICM</sub>      |

| BLVDS_25                        |         | -                    | V <sub>ICM</sub> - 0.125 | V <sub>ICM</sub> + 0.125 | 1M            | 0                  | V <sub>ICM</sub>      |

| MINI_LVDS_25                    |         | -                    | V <sub>ICM</sub> - 0.125 | V <sub>ICM</sub> + 0.125 | 50            | 1.2                | V <sub>ICM</sub>      |

| LVPECL_25                       |         | -                    | V <sub>ICM</sub> - 0.3   | V <sub>ICM</sub> + 0.3   | 1M            | 0                  | V <sub>ICM</sub>      |

| RSDS_25                         |         | -                    | V <sub>ICM</sub> - 0.1   | V <sub>ICM</sub> + 0.1   | 50            | 1.2                | V <sub>ICM</sub>      |

Spartan-3 FPGA Family: DC and Switching Characteristics

### **Phase Shifter (PS)**

#### Table 108: Recommended Operating Conditions for the PS in Variable Phase Mode

|                                  |                                                       |     | Speed Grade |     |     |       |  |  |

|----------------------------------|-------------------------------------------------------|-----|-------------|-----|-----|-------|--|--|

| Symbol                           | Description                                           | -5  |             | -4  |     | Units |  |  |

|                                  |                                                       |     | Max         | Min | Max |       |  |  |

| Operating Freque                 | Operating Frequency Ranges                            |     |             |     |     |       |  |  |

| PSCLK_FREQ (F <sub>PSCLK</sub> ) | Frequency for the PSCLK input                         | 1   | 167         | 1   | 167 | MHz   |  |  |

| Input Pulse Requirements         |                                                       |     |             |     |     |       |  |  |

| PSCLK_PULSE                      | PSCLK pulse width as a percentage of the PSCLK period | 40% | 60%         | 40% | 60% | -     |  |  |

### Table 109: Switching Characteristics for the PS in Variable Phase Mode

| Symbol                   | Description                                                                                                                                           | Equation                             |                                              | Units |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|-------|--|--|--|--|

| Phase Shifting Range     |                                                                                                                                                       |                                      |                                              |       |  |  |  |  |

| MAX_STEPS <sup>(2)</sup> | Maximum allowed number of DCM_DELAY_STEP steps for a given CLKIN clock period, where T = CLKIN clock period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, |                                      |                                              | steps |  |  |  |  |

|                          | double the effective clock period.(3)                                                                                                                 | CLKIN ≥ 60 MHz                       | ±[INTEGER(15 • (T <sub>CLKIN</sub> − 3 ns))] | steps |  |  |  |  |

| FINE_SHIFT_RANGE_MIN     | Minimum guaranteed delay for variable phase shifting                                                                                                  | ±[MAX_STEPS ●<br>DCM_DELAY_STEP_MIN] |                                              | ns    |  |  |  |  |

| FINE_SHIFT_RANGE_MAX     | Maximum guaranteed delay for variable phase shifting                                                                                                  | ±[MAX_STEPS • DCM_DELAY_STEP_MAX]    |                                              | ns    |  |  |  |  |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 108.

- 2. The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, i.e., the PHASE\_SHIFT attribute is set to 0.

- 3. The DCM DELAY STEP values are provided at the bottom of Table 105.

### **Miscellaneous DCM Timing**

### Table 110: Miscellaneous DCM Timing

| Symbol                             | Description                                                                                                                                      | Min | Max | Units           |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN <sup>(1)</sup>      | Minimum duration of a RST pulse width                                                                                                            | 3   | -   | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(2)</sup>      | Maximum duration of a RST pulse width                                                                                                            | N/A | N/A | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(3)</sup> | Maximum duration from V <sub>CCINT</sub> applied to FPGA configuration successfully completed (DONE pin goes High) and clocks applied to DCM DLL | N/A | N/A | minutes         |

#### Notes:

- This limit only applies to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV).

The DCM DFS outputs (CLKFX, CLKFX180) are unaffected.

- 2. This specification is equivalent to the Virtex-4 DCM\_RESET specification. This specification does not apply for Spartan-3E FPGAs.

- 3. This specification is equivalent to the Virtex-4 TCONFIG specification. This specification does not apply for Spartan-3E FPGAs.

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

Spartan-3 FPGA Family: DC and Switching Characteristics

### Table 117: Timing for the Slave Parallel Configuration Mode (Cont'd)

| Cumbal             | Description                                |                                           | All Spee                              | All Speed Grades |       |     |

|--------------------|--------------------------------------------|-------------------------------------------|---------------------------------------|------------------|-------|-----|

| Symbol             |                                            | Descriptio                                | Min                                   | Max              | Units |     |

| Clock Timing       |                                            |                                           |                                       |                  |       |     |

| T <sub>CCH</sub>   | The High pulse width at the CCLK input pin |                                           |                                       | 5                | -     | ns  |

| T <sub>CCL</sub>   | The Low pulse width at the CO              | The Low pulse width at the CCLK input pin |                                       |                  | -     | ns  |

| F <sub>CCPAR</sub> | Frequency of the clock signal              | No bitstream compression                  | Not using the BUSY pin <sup>(2)</sup> | 0                | 50    | MHz |

|                    | at the CCLK input pin                      |                                           | Using the BUSY pin                    | 0                | 66    | MHz |

|                    |                                            | With bitstream compression                |                                       | 0                | 20    | MHz |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77.

- 2. In the Slave Parallel mode, it is necessary to use the BUSY pin when the CCLK frequency exceeds this maximum specification.

- 3. Some Xilinx documents refer to Parallel modes as "SelectMAP" modes.

### **CP132 Footprint**

Figure 81: CP132 Package Footprint (top view)

Table 137: TQ144 Package Pinout (Cont'd)

| Bank     | XC3S100E Pin Name         | XC3S250E Pin Name    | TQ144 Pin | Туре             |

|----------|---------------------------|----------------------|-----------|------------------|

| 1        | IO_L02P_1/A14             | IO_L02P_1/A14        | P76       | DUAL             |

| 1        | IO_L03N_1/A11             | IO_L03N_1/A11        | P82       | DUAL             |

| 1        | IO_L03P_1/A12             | IO_L03P_1/A12        | P81       | DUAL             |

| 1        | IO_L04N_1/A9/RHCLK1       | IO_L04N_1/A9/RHCLK1  | P86       | RHCLK/DUAL       |

| 1        | IO_L04P_1/A10/RHCLK0      | IO_L04P_1/A10/RHCLK0 | P85       | RHCLK/DUAL       |

| 1        | IO_L05N_1/A7/RHCLK3/TRDY1 | IO_L05N_1/A7/RHCLK3  | P88       | RHCLK/DUAL       |

| 1        | IO_L05P_1/A8/RHCLK2       | IO_L05P_1/A8/RHCLK2  | P87       | RHCLK/DUAL       |

| 1        | IO_L06N_1/A5/RHCLK5       | IO_L06N_1/A5/RHCLK5  | P92       | RHCLK/DUAL       |

| 1        | IO_L06P_1/A6/RHCLK4/IRDY1 | IO_L06P_1/A6/RHCLK4  | P91       | RHCLK/DUAL       |

| 1        | IO_L07N_1/A3/RHCLK7       | IO_L07N_1/A3/RHCLK7  | P94       | RHCLK/DUAL       |

| 1        | IO_L07P_1/A4/RHCLK6       | IO_L07P_1/A4/RHCLK6  | P93       | RHCLK/DUAL       |

| 1        | IO_L08N_1/A1              | IO_L08N_1/A1         | P97       | DUAL             |

| 1        | IO_L08P_1/A2              | IO_L08P_1/A2         | P96       | DUAL             |

| 1        | IO_L09N_1/LDC0            | IO_L09N_1/LDC0       | P104      | DUAL             |

| 1        | IO_L09P_1/HDC             | IO_L09P_1/HDC        | P103      | DUAL             |

| 1        | IO_L10N_1/LDC2            | IO_L10N_1/LDC2       | P106      | DUAL             |

| 1        | IO_L10P_1/LDC1            | IO_L10P_1/LDC1       | P105      | DUAL             |

| 1        | IP                        | IP                   | P78       | INPUT            |

| 1        | IP                        | IP                   | P84       | INPUT            |

| <br>1    | IP                        | IP                   | P89       | INPUT            |

| 1        | IP                        | IP                   | P101      | INPUT            |

| <u> </u> | IP                        | IP                   | P107      | INPUT            |

| 1        | IP/VREF_1                 | IP/VREF_1            | P95       | VREF             |

| 1        | VCCO_1                    | VCCO_1               | P79       | VCCO             |

| 1        | VCCO_1                    | VCCO_1               | P100      | VCCO             |

| 2        | IO/D5                     | IO/D5                | P52       | DUAL             |

| 2        | IO/M1                     | IO/M1                | P60       | DUAL             |

| 2        | IP/VREF_2                 | IO/VREF_2            | P66       | 100E: VREF(INPUT |

|          | _                         |                      |           | 250E: VREF(I/O)  |

| 2        | IO_L01N_2/INIT_B          | IO_L01N_2/INIT_B     | P40       | DUAL             |

| 2        | IO_L01P_2/CSO_B           | IO_L01P_2/CSO_B      | P39       | DUAL             |

| 2        | IO_L02N_2/MOSI/CSI_B      | IO_L02N_2/MOSI/CSI_B | P44       | DUAL             |

| 2        | IO_L02P_2/DOUT/BUSY       | IO_L02P_2/DOUT/BUSY  | P43       | DUAL             |

| 2        | IO_L04N_2/D6/GCLK13       | IO_L04N_2/D6/GCLK13  | P51       | DUAL/GCLK        |

| 2        | IO_L04P_2/D7/GCLK12       | IO_L04P_2/D7/GCLK12  | P50       | DUAL/GCLK        |

| 2        | IO_L05N_2/D3/GCLK15       | IO_L05N_2/D3/GCLK15  | P54       | DUAL/GCLK        |

| 2        | IO_L05P_2/D4/GCLK14       | IO_L05P_2/D4/GCLK14  | P53       | DUAL/GCLK        |

| 2        | IO_L07N_2/D1/GCLK3        | IO L07N 2/D1/GCLK3   | P59       | DUAL/GCLK        |

| 2        | IO_L07P_2/D2/GCLK2        | IO_L07P_2/D2/GCLK2   | P58       | DUAL/GCLK        |

|          | IO_L08N_2/DIN/D0          | IO_L08N_2/DIN/D0     | P63       | DUAL             |

| 2        |                           |                      | P62       | DUAL             |

|          | IO_L08P_2/M0              | IO_L08P_2/M0         | 1 02      |                  |

| 2        |                           |                      |           |                  |

| 2        | IO_L09N_2/VS1/A18         | IO_L09N_2/VS1/A18    | P68       | DUAL             |

| 2        |                           |                      |           |                  |

Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name | XC3S500E Pin Name | XC3S1200E Pin Name | FT256<br>Ball | Туре                                                       |

|------|-------------------|-------------------|--------------------|---------------|------------------------------------------------------------|

| 0    | IO_L12P_0         | IO_L12P_0         | IO_L12P_0          | E8            | I/O                                                        |

| 0    | N.C. (♠)          | IO_L13N_0         | IO_L13N_0          | C7            | <b>250E:</b> N.C. <b>500E:</b> I/O <b>1200E:</b> I/O       |

| 0    | N.C. (♠)          | IO_L13P_0         | IO_L13P_0          | B7            | <b>250E:</b> N.C. <b>500E:</b> I/O <b>1200E:</b> I/O       |

| 0    | IO_L14N_0/VREF_0  | IO_L14N_0/VREF_0  | IO_L14N_0/VREF_0   | D7            | VREF                                                       |

| 0    | IO_L14P_0         | IO_L14P_0         | IO_L14P_0          | E7            | I/O                                                        |

| 0    | IO_L15N_0         | IO_L15N_0         | IO_L15N_0          | D6            | I/O                                                        |

| 0    | IO_L15P_0         | IO_L15P_0         | IO_L15P_0          | C6            | I/O                                                        |

| 0    | IO_L17N_0/VREF_0  | IO_L17N_0/VREF_0  | IO_L17N_0/VREF_0   | A4            | VREF                                                       |

| 0    | IO_L17P_0         | IO_L17P_0         | IO_L17P_0          | A5            | I/O                                                        |

| 0    | IO_L18N_0         | IO_L18N_0         | IO_L18N_0          | C4            | I/O                                                        |

| 0    | IO_L18P_0         | IO_L18P_0         | IO_L18P_0          | C5            | I/O                                                        |

| 0    | IO_L19N_0/HSWAP   | IO_L19N_0/HSWAP   | IO_L19N_0/HSWAP    | B3            | DUAL                                                       |

| 0    | IO_L19P_0         | IO_L19P_0         | IO_L19P_0          | C3            | I/O                                                        |

| 0    | IP                | IP                | IP                 | A3            | INPUT                                                      |

| 0    | IP                | IP                | IP                 | C13           | INPUT                                                      |

| 0    | IP_L02N_0         | IP_L02N_0         | IP_L02N_0          | C12           | INPUT                                                      |

| 0    | IP_L02P_0         | IP_L02P_0         | IP_L02P_0          | D12           | INPUT                                                      |

| 0    | IP_L07N_0         | IP_L07N_0         | IP_L07N_0          | C9            | INPUT                                                      |

| 0    | IP_L07P_0         | IP_L07P_0         | IP_L07P_0          | C10           | INPUT                                                      |

| 0    | IP_L10N_0/GCLK9   | IP_L10N_0/GCLK9   | IP_L10N_0/GCLK9    | B8            | GCLK                                                       |

| 0    | IP_L10P_0/GCLK8   | IP_L10P_0/GCLK8   | IP_L10P_0/GCLK8    | A8            | GCLK                                                       |

| 0    | IP_L16N_0         | IP_L16N_0         | IP_L16N_0          | E6            | INPUT                                                      |

| 0    | IP_L16P_0         | IP_L16P_0         | IP_L16P_0          | D5            | INPUT                                                      |

| 0    | VCCO_0            | VCCO_0            | VCCO_0             | B5            | VCCO                                                       |

| 0    | VCCO_0            | VCCO_0            | VCCO_0             | B12           | VCCO                                                       |

| 0    | VCCO_0            | VCCO_0            | VCCO_0             | F7            | VCCO                                                       |

| 0    | VCCO_0            | VCCO_0            | VCCO_0             | F10           | VCCO                                                       |

| 1    | IO_L01N_1/A15     | IO_L01N_1/A15     | IO_L01N_1/A15      | R15           | DUAL                                                       |

| 1    | IO_L01P_1/A16     | IO_L01P_1/A16     | IO_L01P_1/A16      | R16           | DUAL                                                       |

| 1    | IO_L02N_1/A13     | IO_L02N_1/A13     | IO_L02N_1/A13      | P15           | DUAL                                                       |

| 1    | IO_L02P_1/A14     | IO_L02P_1/A14     | IO_L02P_1/A14      | P16           | DUAL                                                       |

| 1    | N.C. (♠)          | IO_L03N_1/VREF_1  | IO_L03N_1/VREF_1   | N15           | 250E: N.C.<br>500E: VREF<br>1200E: VRE                     |

| 1    | N.C. (♠)          | IO_L03P_1         | IO_L03P_1          | N14           | <b>250E:</b> N.C.<br><b>500E:</b> I/O<br><b>1200E:</b> I/O |

| 1    | IO_L04N_1/VREF_1  | IO_L04N_1/VREF_1  | IO_L04N_1/VREF_1   | M16           | VREF                                                       |

| 1    | IO_L04P_1         | IO_L04P_1         | IO_L04P_1          | N16           | I/O                                                        |

| 1    | N.C. (♠)          | IO_L05N_1         | IO_L05N_1          | L13           | <b>250E:</b> N.C. <b>500E:</b> I/O <b>1200E:</b> I/O       |

### FT256 Footprint

Figure 85: FT256 Package Footprint (top view)

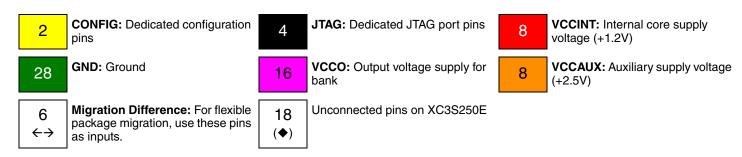

# **Footprint Migration Differences**

Table 151 summarizes any footprint and functionality differences between the XC3S500E, the XC3S1200E, and the XC3S1600E FPGAs that may affect easy migration between devices available in the FG320 package. There are 26 such balls. All other pins not listed in Table 151 unconditionally migrate between Spartan-3E devices available in the FG320 package.

The XC3S500E is duplicated on both the left and right sides of the table to show migrations to and from the XC3S1200E

and the XC3S1600E. The arrows indicate the direction for easy migration. A double-ended arrow  $(\leftarrow \rightarrow)$  indicates that the two pins have identical functionality. A left-facing arrow  $(\leftarrow)$  indicates that the pin on the device on the right unconditionally migrates to the pin on the device on the left. It may be possible to migrate the opposite direction depending on the I/O configuration. For example, an I/O pin (Type = I/O) can migrate to an input-only pin (Type = INPUT) if the I/O pin is configured as an input.

Table 151: FG320 Footprint Migration Differences

| Pin | Bank    | XC3S500E  | Migration     | XC3S1200E   | Migration                | XC3S1600E   | Migration     | XC3S500E  |

|-----|---------|-----------|---------------|-------------|--------------------------|-------------|---------------|-----------|

| A7  | 0       | INPUT     | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | INPUT     |

| A12 | 0       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | N.C.      |

| D4  | 3       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | N.C.      |

| D6  | 0       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | N.C.      |

| D13 | 0       | INPUT     | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | INPUT     |

| E3  | 3       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | +             | N.C.      |

| E4  | 3       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |

| E6  | 0       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |

| E15 | 1       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |

| E16 | 1       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |

| E17 | 1       | I/O       | <b>←</b>      | INPUT       | $\leftarrow \rightarrow$ | INPUT       | $\rightarrow$ | I/O       |

| F4  | 3       | I/O       | <b>←</b>      | INPUT       | $\leftarrow \rightarrow$ | INPUT       | $\rightarrow$ | I/O       |

| N12 | 2       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |

| N14 | 1       | N.C.      | $\rightarrow$ | I/O         | $\leftarrow \rightarrow$ | I/O         | <b>←</b>      | N.C.      |