Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 612                                                           |

| Number of Logic Elements/Cells | 5508                                                          |

| Total RAM Bits                 | 221184                                                        |

| Number of I/O                  | 172                                                           |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 256-LBGA                                                      |

| Supplier Device Package        | 256-FTBGA (17x17)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s250e-4ftg256c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

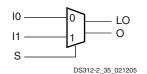

The wide multiplexers can be used by the automatic tools or instantiated in a design using a component such as the F5MUX. The symbol, signals, and function are described in Figure 21, Table 12, and Table 13. The description is similar for the F6MUX, F7MUX, and F8MUX. Each has versions with a general output, local output, or both.

Figure 21: F5MUX with Local and General Outputs

#### Table 12: F5MUX Inputs and Outputs

| Signal | Function                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 10     | Input selected when S is Low                                                                                                      |

| 11     | Input selected when S is High                                                                                                     |

| S      | Select input                                                                                                                      |

| LO     | Local Output that connects to the F5 or FX CLB pins,<br>which use local feedback to the FXIN inputs to the<br>FiMUX for cascading |

| 0      | General Output that connects to the general-purpose combinatorial or registered outputs of the CLB                                |

#### Table 13: F5MUX Function

|   | Inputs |    | Outputs |    |  |

|---|--------|----|---------|----|--|

| S | 10     | l1 | 0       | LO |  |

| 0 | 1      | Х  | 1       | 1  |  |

| 0 | 0      | Х  | 0       | 0  |  |

| 1 | Х      | 1  | 1       | 1  |  |

| 1 | Х      | 0  | 0       | 0  |  |

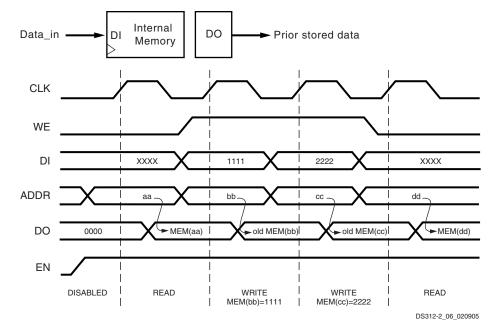

Figure 34: Waveforms of Block RAM Data Operations with READ\_FIRST Selected

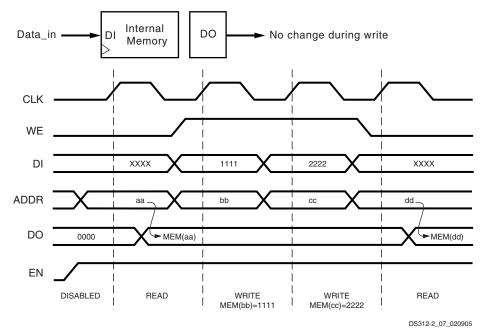

Setting the WRITE\_MODE attribute to a value of NO\_CHANGE, puts the DO outputs in a latched state when asserting WE. Under this condition, the DO outputs retain the data driven just before WE is asserted. NO\_CHANGE timing is shown in the portion of Figure 35 during which WE is High.

BUFGMUX\_X0Y6

| D        | iff. |       | Sin   | gle-Ende | d Pin Nur | nber by F | Package 1 | age Type Left Edge |       |          |                   |              |   |             |

|----------|------|-------|-------|----------|-----------|-----------|-----------|--------------------|-------|----------|-------------------|--------------|---|-------------|

| Cle      | ock  | VQ100 | CP132 | TQ144    | PQ208     | FT256     | FG320     | FG400              | FG484 |          | LHCLK DCM/BUFGMUX |              |   |             |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y5 | → | D           |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y4 | → | С           |

| ir       | Ρ    | P9    | F3    | P14      | P22       | H5        | J5        | K3                 | M5    | <b>→</b> | LHCLK0            |              |   | Se          |

| Pair     | Ν    | P10   | F2    | P15      | P23       | H6        | J4        | K2                 | L5    | →        | LHCLK1            | DCM_X0Y2     |   | Line        |

| <u> </u> | Ρ    | P11   | F1    | P16      | P24       | H3        | J1        | K7                 | L8    | <b>→</b> | LHCLK2            |              |   | Clock Lines |

| Pair     | Ν    | P12   | G1    | P17      | P25       | H4        | J2        | L7                 | M8    | →        | LHCLK3            |              |   | ō           |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y3 | → | В           |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y2 | → | Α           |

|          |      |       |       |          |           |           |           |                    |       |          |                   |              |   |             |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y9 | → | Н           |

|          |      |       |       |          |           |           |           |                    |       |          |                   | BUFGMUX_X0Y8 | → | G           |

| <u> </u> | Ρ    | P15   | G3    | P20      | P28       | J2        | K3        | M1                 | M1    | <b>→</b> | LHCLK4            |              |   | Se          |

| Pair     | Ν    | P16   | H1    | P21      | P29       | J3        | K4        | L1                 | N1    | <b>→</b> | LHCLK5            |              |   | Line        |

| <u>.</u> | Ρ    | P17   | H2    | P22      | P30       | J5        | K6        | M3                 | M3    | →        | LHCLK6            | DCM_X0Y1     |   | Clock Lines |

| Pair     | Ν    | P18   | H3    | P23      | P31       | J4        | K5        | L3                 | M4    | →        | LHCLK7            |              |   | ō           |

|          |      |       |       |          |           | •         |           |                    |       | -        |                   | BUFGMUX_X0Y7 | → | F           |

|          |      |       |       |          |           |           |           |                    |       |          |                   |              | - |             |

#### Table 31: Direct Clock Input and Optional External Feedback to Left-Edge DCMs (XC3S1200E and XC3S1600E)

#### Table 32: Direct Clock Input and Optional External Feedback to Right-Edge DCMs (XC3S1200E and XC3S1600E)

| [                | Right Edg    | е      |   |       | Sing  | gle-Ende | d Pin Nur | nber by F | Package T | уре   |       | Di  | ff.      |

|------------------|--------------|--------|---|-------|-------|----------|-----------|-----------|-----------|-------|-------|-----|----------|

|                  | DCM/BUFGMUX  | RHCLK  |   | VQ100 | CP132 | TQ144    | PQ208     | FT256     | FG320     | FG400 | FG484 | Clo | ock      |

| D 🗲              | BUFGMUX_X3Y5 |        |   |       |       |          |           |           |           |       |       |     |          |

| <mark>C</mark> ← | BUFGMUX_X3Y4 |        |   |       |       |          |           |           |           |       |       |     |          |

| se               |              | RHCLK7 | ÷ | P68   | G13   | P94      | P135      | H11       | J14       | J20   | L19   | Ν   | <b>_</b> |

| Clock Lines      | DCM_X3Y2     | RHCLK6 | ← | P67   | G14   | P93      | P134      | H12       | J15       | K20   | L18   | Ρ   | Pair     |

| ock              | DCW_A312     | RHCLK5 | ← | P66   | H12   | P92      | P133      | H14       | J16       | K14   | L21   | Ν   | L        |

| ō                |              | RHCLK4 | ÷ | P65   | H13   | P91      | P132      | H15       | J17       | K13   | L20   | Р   | Pair     |

| B←               | BUFGMUX_X3Y3 |        |   |       |       |          |           |           |           |       |       |     |          |

| A ←              | BUFGMUX_X3Y2 |        |   |       |       |          |           |           |           |       |       |     |          |

|                  |              |        |   |       |       |          |           |           |           |       |       |     |          |

| H ←              | BUFGMUX_X3Y9 |        |   |       |       |          |           |           |           |       |       |     |          |

| G 🗲              | BUFGMUX_X3Y8 |        |   |       |       |          |           |           |           |       |       |     |          |

| se               |              | RHCLK3 | ← | P63   | J14   | P88      | P129      | J13       | K14       | L14   | M16   | Ν   | ir       |

| Line             | DCM_X3Y1     | RHCLK2 | ← | P62   | J13   | P87      | P128      | J14       | K15       | L15   | M15   | Ρ   | Pair     |

| Clock Lines      |              | RHCLK1 | ← | P61   | J12   | P86      | P127      | J16       | K12       | L16   | M22   | Ν   | ir       |

| ō                |              | RHCLK0 | ← | P60   | K14   | P85      | P126      | K16       | K13       | M16   | N22   | Ρ   | Pair     |

| <b>F</b> ←       | BUFGMUX_X3Y7 |        |   |       |       |          |           |           |           |       |       |     |          |

| E ←              | BUFGMUX_X3Y6 |        |   |       |       |          |           |           |           |       |       |     |          |

Every FPGA input provides a possible DCM clock input, but the path is not temperature and voltage compensated like the GCLKs. Alternatively, clock signals within the FPGA optionally provide a DCM clock input via a Global Clock Multiplexer Buffer (BUFGMUX). The global clock net

connects directly to the CLKIN input. The internal and external connections are shown in Figure 42a and Figure 42c, respectively.

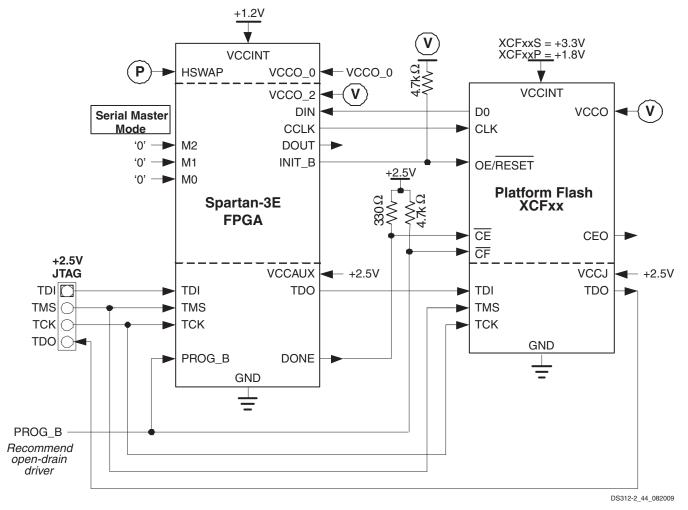

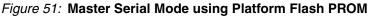

## **Master Serial Mode**

For additional information, refer to the "Master Serial Mode" chapter in  $\underline{\text{UG332}}$ .

In Master Serial mode (M[2:0] = <0:0:0>), the Spartan-3E FPGA configures itself from an attached Xilinx Platform

Flash PROM, as illustrated in Figure 51. The FPGA supplies the CCLK output clock from its internal oscillator to the attached Platform Flash PROM. In response, the Platform Flash PROM supplies bit-serial data to the FPGA's DIN input, and the FPGA accepts this data on each rising CCLK edge.

All mode select pins, M[2:0], must be Low when sampled, when the FPGA's INIT\_B output goes High. After configuration, when the FPGA's DONE output goes High, the mode select pins are available as full-featured user-I/O pins.

##

## SPI Serial Flash Mode

For additional information, refer to the "Master SPI Mode" chapter in UG332.

In SPI Serial Flash mode (M[2:0] = <0:0:1>), the Spartan-3E FPGA configures itself from an attached industry-standard SPI serial Flash PROM, as illustrated in Figure 53 and Figure 54. The FPGA supplies the CCLK output clock from its internal oscillator to the clock input of the attached SPI Flash PROM.

(S) Although SPI is a standard four-wire interface, various available SPI Flash PROMs use different command protocols. The FPGA's variant select pins, VS[2:0], define how the FPGA communicates with the SPI Flash, including which SPI Flash command the FPGA issues to start the read operation and the number of dummy bytes inserted before the FPGA expects to receive valid data from the SPI Flash. Table 53 shows the available SPI Flash PROMs expected to operate with Spartan-3E FPGAs. Other compatible devices might work but have not been tested for suitability with Spartan-3E FPGAs. All other VS[2:0] values are reserved for future use. Consult the data sheet for the desired SPI Flash device to determine its suitability. The basic timing requirements and waveforms are provided in

## Serial Peripheral Interface (SPI) Configuration Timing in Module 3.

Figure 53 shows the general connection diagram for those SPI Flash PROMs that support the 0x03 READ command or the 0x0B FAST READ commands.

Figure 54 shows the connection diagram for Atmel DataFlash serial PROMs, which also use an SPI-based protocol. 'B'-series DataFlash devices are limited to FPGA applications operating over the commercial temperature range. Industrial temperature range applications must use 'C'- or 'D'-series DataFlash devices, which have a shorter DataFlash select setup time, because of the faster FPGA CCLK frequency at cold temperatures.

#### **iMPACT** Dummy VS2 **SPI Read Command** VS1 VS0 **SPI Serial Flash Vendor SPI Flash Family** Programming Bytes Support M25Pxx Yes STMicroelectronics (ST) M25PExx/M45PExx AT45DB 'D'-Series Data Yes Flash Atmel AT26 / AT25(1) Intel **S**33 Spansion (AMD, Fujitsu) S25FLxxxA FAST READ (0x0B) Winbond (NexFlash) NX25 / W25 1 1 1 1 (see Figure 53) Macronix MX25Lxxxx SST25LFxxxA Silicon Storage Technology (SST) SST25VFxxxA Programmable Microelectronics Corp. Pm25LVxxx (PMC) AMIC Technology A25L Eon Silicon Solution, Inc. **EN25** M25Pxx STMicroelectronics (ST) Yes M25PExx/M45PExx Spansion (AMD, Fujitsu) S25FLxxxA Winbond (NexFlash) NX25 / W25 Macronix MX25Lxxxx READ (0x03) 1 0 1 0 (see Figure 53) SST25LFxxxA Silicon Storage Technology SST25VFxxxA (SST) SST25VFxxx Programmable Microelectronics Corp. Pm25LVxxx (PMC) AT45DB DataFlash READ ARRAY (0xE8) (use only 'C' or 'D' 1 1 0 4 **Atmel Corporation** Yes (see Figure 54) Series for Industrial temperature range) Others Reserved

#### Table 53: Variant Select Codes for Various SPI Serial Flash PROMs

Notes:

1. See iMPACT documentation for specific device support.

**WRITER NOTE:** Many of the URLs in this table are obsolete or otherwise broken.

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | During Configuration                               | After Configuration                                                                                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                            | Low indicates that the FPGA is not yet configured. | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA is<br>successfully configured.                                                              |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer,<br>forces the FPGA to restart its<br>configuration process by clearing<br>configuration memory and resetting<br>the DONE and INIT_B pins once<br>PROG_B returns High.<br>Recommend external 4.7 k $\Omega$<br>pull-up resistor to 2.5V. Internal<br>pull-up value may be weaker (see<br>Table 78). If driving externally with a<br>3.3V output, use an open-drain or<br>open-collector driver or use a<br>current limiting series resistor. | Must be High to allow configuration to start.      | Drive PROG_B Low and<br>release to reprogram<br>FPGA. Hold PROG_B to<br>force FPGA I/O pins into<br>Hi-Z, allowing direct<br>programming access to<br>Flash PROM pins. |

#### Table 59: Byte-Wide Peripheral Interface (BPI) Connections (Cont'd)

### **Voltage Compatibility**

V The FPGA's parallel Flash interface signals are within I/O Banks 1 and 2. The majority of parallel Flash PROMs use a single 3.3V supply voltage. Consequently, in most cases, the FPGA's VCCO\_1 and VCCO\_2 supply voltages must also be 3.3V to match the parallel Flash PROM. There are some 1.8V parallel Flash PROMs available and the FPGA interfaces with these devices if the VCCO\_1 and VCCO\_2 supplies are also 1.8V.

## Power-On Precautions if PROM Supply is Last in Sequence

Like SPI Flash PROMs, parallel Flash PROMs typically require some amount of internal initialization time when the supply voltage reaches its minimum value.

The PROM supply voltage also connects to the FPGA's VCCO\_2 supply input. In many systems, the PROM supply feeding the FPGA's VCCO\_2 input is valid before the FPGA's other V<sub>CCINT</sub> and V<sub>CCAUX</sub> supplies, and consequently, there is no issue. However, if the PROM supply is last in the sequence, a potential race occurs between the FPGA and the parallel Flash PROM. See

Power-On Precautions if 3.3V Supply is Last in Sequence for a similar description of the issue for SPI Flash PROMs.

### **Supported Parallel NOR Flash PROM Densities**

Table 60 indicates the smallest usable parallel Flash PROMto program a single Spartan-3E FPGA. Parallel Flashdensity is specified in bits but addressed as bytes. TheFPGA presents up to 24 address lines during configurationbut not all are required for single FPGA applications.Table 60 shows the minimum required number of addresslines between the FPGA and parallel Flash PROM. Theactual number of address line required depends on thedensity of the attached parallel Flash PROM.

A multiple-FPGA daisy-chained application requires a parallel Flash PROM large enough to contain the sum of the FPGA file sizes. An application can also use a larger-density parallel Flash PROM to hold additional data beyond just FPGA configuration data. For example, the parallel Flash PROM can also contain the application code for a MicroBlaze RISC processor core implemented within the Spartan-3E FPGA. After configuration, the MicroBlaze processor can execute directly from external Flash or can copy the code to other, faster system memory before executing the code.

#### Table 60: Number of Bits to Program a Spartan-3E FPGA and Smallest Parallel Flash PROM

| Spartan-3E FPGA | Uncompressed<br>File Sizes (bits) | Smallest Usable<br>Parallel Flash PROM | Minimum Required<br>Address Lines |

|-----------------|-----------------------------------|----------------------------------------|-----------------------------------|

| XC3S100E        | 581,344                           | 1 Mbit                                 | A[16:0]                           |

| XC3S250E        | 1,353,728                         | 2 Mbit                                 | A[17:0]                           |

| XC3S500E        | 2,270,208                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1200E       | 3,841,184                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1600E       | 5,969,696                         | 8 Mbit                                 | A[19:0]                           |

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at the start of<br>configuration during the Initialization<br>memory clearing process. Released<br>at the end of memory clearing, when<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                               | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                       |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                     | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High. Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

#### Table 65: Slave Parallel Mode Connections (Cont'd)

## **Voltage Compatibility**

W Most Slave Parallel interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 1.8V, 2.5V, or 3.3V to match the requirements of the external host, ideally 2.5V. Using 1.8V or 3.3V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain. Use Slave Parallel mode (M[2:0] = <1:1:0>) for all FPGAs in the daisy-chain. The schematic in Figure 62 is optimized for FPGA downloading and does not support the SelectMAP read interface. The FPGA's RDWR\_B pin must be Low during configuration.

After the lead FPGA is filled with its configuration data, the lead FPGA enables the next FPGA in the daisy-chain by asserting is chip-select output, CSO\_B.

## **Bitstream Generator (BitGen) Options**

For additional information, refer to the "Configuration Bitstream Generator (BitGen) Settings" chapter in UG332.

Various Spartan-3E FPGA functions are controlled by specific bits in the configuration bitstream image. These

values are specified when creating the bitstream image with the Bitstream Generator (BitGen) software.

Table 69 provides a list of all BitGen options for Spartan-3EFPGAs.

#### Table 69: Spartan-3E FPGA Bitstream Generator (BitGen) Options

| Option Name | Pins/Function<br>Affected                            | Values<br>( <i>default</i> )   | Description                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ConfigRate  | CCLK,<br>Configuration                               | <u>1</u> , 3, 6,<br>12, 25, 50 | Sets the approximate frequency, in MHz, of the internal oscillator using for Master Serial, SPI, and BPI configuration modes. The internal oscillator powers up at its lowest frequency, and the new setting is loaded as part of the configuration bitstream. The software default value is 1 (~1.5 MHz) starting with ISE 8.1, Service Pack 1. |

| StartupClk  | Configuration,<br>Startup                            | <u>Cclk</u>                    | <b>Default.</b> The CCLK signal (internally or externally generated) controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up.                                                                                                                                                             |

|             |                                                      | UserClk                        | A clock signal from within the FPGA application controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up. The FPGA application supplies the user clock on the CLK pin on the STARTUP_SPARTAN3E primitive.                                                                                  |

|             |                                                      | Jtag                           | The JTAG TCK input controls the startup sequence when the FPGA transitions from the configuration mode to the user mode. See <u>Start-Up</u> .                                                                                                                                                                                                   |

| UnusedPin   | Unused I/O                                           | Pulldown                       | Default. All unused I/O pins and input-only pins have a pull-down resistor to GND.                                                                                                                                                                                                                                                               |

|             | Pins                                                 | Pullup                         | All unused I/O pins and input-only pins have a pull-up resistor to the VCCO_# supply for its associated I/O bank.                                                                                                                                                                                                                                |

|             |                                                      | Pullnone                       | All unused I/O pins and input-only pins are left floating (Hi-Z, high-impedance, three-state). Use external pull-up or pull-down resistors or logic to apply a valid signal level.                                                                                                                                                               |

| DONE_cycle  | DONE pin,<br>Configuration<br>Startup                | 1, 2, 3, <u>4</u> ,<br>5, 6    | Selects the Configuration Startup phase that activates the FPGA's DONE pin. See Start-Up.                                                                                                                                                                                                                                                        |

| GWE_cycle   | All flip-flops,<br>LUT RAMs, and<br>SRL16 shift      | 1, 2, 3, 4,<br>5, <u>6</u>     | Selects the Configuration Startup phase that asserts the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). It also enables block RAM read and write operations. See Start-Up.                                                                                                                                |

|             | registers, Block<br>RAM,<br>Configuration<br>Startup | Done                           | Waits for the DONE pin input to go High before asserting the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). Block RAM read and write operations are enabled at this time.                                                                                                                                 |

|             |                                                      | Keep                           | Retains the current GWE_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| GTS_cycle   | All I/O pins,<br>Configuration                       | 1, 2, 3, 4,<br><u>5</u> , 6    | Selects the Configuration Startup phase that releases the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point. See Start-Up.                                                                                                                       |

|             |                                                      | Done                           | Waits for the DONE pin input to go High before releasing the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point.                                                                                                                                  |

|             |                                                      | Keep                           | Retains the current GTS_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| LCK_cycle   | DCMs,                                                | <u>NoWait</u>                  | The FPGA does not wait for selected DCMs to lock before completing configuration.                                                                                                                                                                                                                                                                |

|             | Configuration<br>Startup                             | 0, 1, 2, 3,<br>4, 5, 6         | If one or more DCMs in the design have the STARTUP_WAIT attribute set to TRUE, the FPGA waits for such DCMs to acquire their respective input clock and assert their LOCKED output. This setting selects the Configuration Startup phase where the FPGA waits for the DCMs to lock.                                                              |

| DonePin     | DONE pin                                             | <u>Pullup</u>                  | Internally connects a pull-up resistor between DONE pin and V <sub>CCAUX</sub> . An external 330 $\Omega$ pull-up resistor to V <sub>CCAUX</sub> is still recommended.                                                                                                                                                                           |

|             |                                                      | Pullnone                       | No internal pull-up resistor on DONE pin. An external 330 $\Omega$ pull-up resistor to $V_{\text{CCAUX}}$ is required.                                                                                                                                                                                                                           |

## **Voltage Regulators**

Various power supply manufacturers offer complete power solutions for Xilinx FPGAs including some with integrated three-rail regulators specifically designed for Spartan-3 and Spartan-3E FPGAs. The Xilinx Power Corner website provides links to vendor solution guides and Xilinx power estimation and analysis tools.

# Power Distribution System (PDS) Design and Decoupling/Bypass Capacitors

Good power distribution system (PDS) design is important for all FPGA designs, but especially so for high performance applications, greater than 100 MHz. Proper design results in better overall performance, lower clock and DCM jitter, and a generally more robust system. Before designing the printed circuit board (PCB) for the FPGA design, please review <u>XAPP623</u>: Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitors.

## **Power-On Behavior**

For additional power-on behavior information, including I/O behavior before and during configuration, refer to the "Sequence of Events" chapter in UG332.

Spartan-3E FPGAs have a built-in Power-On Reset (POR) circuit that monitors the three power rails required to successfully configure the FPGA. At power-up, the POR circuit holds the FPGA in a reset state until the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 2 supplies reach their respective input threshold levels (see Table 74 in Module 3). After all three supplies reach their respective thresholds, the POR reset is released and the FPGA begins its configuration process.

## **Supply Sequencing**

Because the three FPGA supply inputs must be valid to release the POR reset and can be supplied in any order, there are no FPGA-specific voltage sequencing requirements. Applying the FPGA's  $V_{CCAUX}$  supply before the  $V_{CCINT}$  supply uses the least  $I_{CCINT}$  current.

Although the FPGA has no specific voltage sequence requirements, be sure to consider any potential sequencing requirement of the configuration device attached to the FPGA, such as an SPI serial Flash PROM, a parallel NOR Flash PROM, or a microcontroller. For example, Flash PROMs have a minimum time requirement before the PROM can be selected and this must be considered if the 3.3V supply is the last in the sequence. See Power-On Precautions if 3.3V Supply is Last in Sequence for more details.

When all three supplies are valid, the minimum current required to power-on the FPGA equals the worst-case quiescent current, specified in Table 79. Spartan-3E FPGAs

do not require Power-On Surge (POS) current to successfully configure.

## Surplus $I_{CCINT}$ if $V_{CCINT}$ Applied before $V_{CCAUX}$

If the V<sub>CCINT</sub> supply is applied before the V<sub>CCAUX</sub> supply, the FPGA might draw a surplus I<sub>CCINT</sub> current in addition to the I<sub>CCINT</sub> quiescent current levels specified in Table 79, page 118. The momentary additional I<sub>CCINT</sub> surplus current might be a few hundred milliamperes under nominal conditions, significantly less than the instantaneous current consumed by the bypass capacitors at power-on. However, the surplus current immediately disappears when the V<sub>CCAUX</sub> supply is applied, and, in response, the FPGA's I<sub>CCINT</sub> quiescent current demand drops to the levels specified in Table 79. The FPGA does not use or require the surplus current to successfully power-on and configure. If applying V<sub>CCINT</sub> before V<sub>CCAUX</sub>, ensure that the regulator does not have a foldback feature that could inadvertently shut down in the presence of the surplus current.

## **Configuration Data Retention, Brown-Out**

The FPGA's configuration data is stored in robust CMOS configuration latches. The data in these latches is retained even when the voltages drop to the minimum levels necessary to preserve RAM contents, as specified in Table 76.

If, after configuration, the  $V_{CCAUX}$  or  $V_{CCINT}$  supply drops below its data retention voltage, the current device configuration must be cleared using one of the following methods:

- Force the V<sub>CCAUX</sub> or V<sub>CCINT</sub> supply voltage below the minimum Power On Reset (POR) voltage threshold (Table 74).

- Assert PROG\_B Low.

The POR circuit does not monitor the VCCO\_2 supply after configuration. Consequently, dropping the VCCO\_2 voltage does not reset the device by triggering a Power-On Reset (POR) event.

# No Internal Charge Pumps or Free-Running Oscillators

Some system applications are sensitive to sources of analog noise. Spartan-3E FPGA circuitry is fully static and does not employ internal charge pumps.

The CCLK configuration clock is active during the FPGA configuration process. After configuration completes, the CCLK oscillator is automatically disabled unless the Bitstream Generator (BitGen) option *Persist=Yes*.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/16/07 | 3.5     | Added information about new Spartan-3 Generation user guides (Design Documentation Available).<br>Added cross-references to <u>UG331</u> : Spartan-3 Generation FPGA User Guide and to <u>UG332</u> : Spartan-3<br>Generation Configuration User Guide. Added note about possible JTAG configuration issues when the<br>FPGA mode pins are set for Master mode and using software prior to ISE 9.1.01i (JTAG Mode).<br>Removed a few lingering references to "weak" pull-up resistors, including in Figure 12. Removed<br>vestigial references regarding the LDC[2:0] and HDC pins during Slave Parallel Mode configuration.<br>These pins are not used in this configuration mode. |

| 05/29/07 | 3.6     | Added information about HSWAP and PCI differences between steppings to Table 71. Removed<br>"Performance Differences between Global Buffers" to match improved specs in Module 3. Updated<br>PROG_B pulse width descriptions to match specification in Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 04/18/08 | 3.7     | Corrected Figure 6 to show six taps and updated associated text. Added note for recommended pull-up on DONE in Table 55 and elsewhere. Added a caution regarding Persist of pins A20-A23. Updated Stepping description in Table 71 to note that only Stepping 1 is in production today. Updated links.                                                                                                                                                                                                                                                                                                                                                                              |

| 08/26/09 | 3.8     | Added a frequency limitation to Equation 6. Added a new Equation 7 with a frequency limitation. Added a Spread Spectrum, page 56 paragraph. Added Table 42, page 60. Updated a Flash vendor name in Table 61, page 88. Removed the < symbol from the flash read access times in Table 62, page 88. Revised the first paragraph in Configuration Sequence, page 101. Revised the first paragraph in Power-On Behavior, page 110. Revised the second paragraph in Production Stepping, page 111. Revised the first paragraph in Ordering a Later Stepping, page 111.                                                                                                                  |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated the design note section in VARIABLE Phase Shift Mode. Added the VQ100 to the Quadrant Clock Routing section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

## **General Recommended Operating Conditions**

#### Table 77: General Recommended Operating Conditions

| Symbol                           | De                                          | Min                              | Nominal    | Max   | Units |                        |    |

|----------------------------------|---------------------------------------------|----------------------------------|------------|-------|-------|------------------------|----|

| ТJ                               | Junction temperature                        | Commercial                       |            | 0     | -     | 85                     | °C |

|                                  |                                             | Industrial                       |            | -40   | -     | 100                    | °C |

| V <sub>CCINT</sub>               | Internal supply voltage                     | Internal supply voltage          |            |       |       |                        | V  |

| V <sub>CCO</sub> <sup>(1)</sup>  | Output driver supply voltage                |                                  | 1.100      | -     | 3.465 | V                      |    |

| V <sub>CCAUX</sub>               | Auxiliary supply voltage                    |                                  |            | 2.375 | 2.500 | 2.625                  | V  |

| V <sub>IN</sub> <sup>(2,3)</sup> | Input voltage extremes to avoid             | I/O, Input-only, and             | IP or IO_# | -0.5  | -     | V <sub>CCO</sub> + 0.5 | V  |

|                                  | turning on I/O protection diodes            | Dual-Purpose pins (4) IO_Lxxy_#( |            | -0.5  | -     | V <sub>CCO</sub> + 0.5 | V  |

|                                  |                                             | Dedicated pins <sup>(6)</sup>    | -          | -0.5  | _     | $V_{CCAUX} + 0.5$      | V  |

| T <sub>IN</sub>                  | Input signal transition time <sup>(7)</sup> |                                  |            |       | _     | 500                    | ns |

Notes:

- 1. This  $V_{CCO}$  range spans the lowest and highest operating voltages for all supported I/O standards. Table 80 lists the recommended  $V_{CCO}$  range specific to each of the single-ended I/O standards, and Table 82 lists that specific to the differential standards.

- Input voltages outside the recommended range require the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Refer to Table 73.

- 3. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 4. Each of the User I/O and Dual-Purpose pins is associated with one of the four banks' V<sub>CCO</sub> rails. Meeting the V<sub>IN</sub> limit ensures that the internal diode junctions that exist between these pins and their associated V<sub>CCO</sub> and GND rails do not turn on. The absolute maximum rating is provided in Table 73.

- 5. For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- 7. Measured between 10% and 90% V<sub>CCO</sub>. Follow Signal Integrity recommendations.

## **Switching Characteristics**

All Spartan-3E FPGAs ship in two speed grades: -4 and the higher performance -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production, as shown in Table 84. Each category is defined as follows:

<u>Advance</u>: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

**Preliminary**: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

**Production**: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

## **Software Version Requirements**

Production-quality systems must use FPGA designs compiled using a speed file designated as PRODUCTION status. FPGAs designs using a less mature speed file designation should only be used during system prototyping or pre-production qualification. FPGA designs with speed files designated as Advance or Preliminary should not be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the latest Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. **Unless** otherwise noted, the published parameter values apply to all Spartan-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

Sign Up for Alerts on Xilinx.com https://secure.xilinx.com/webreg/register.do

?group=myprofile&languageID=1

Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3E speed files (v1.27), part of the Xilinx Development Software, are the original source for many but not all of the values. The speed grade designations for these files are shown in Table 84. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

| Device    | Advance | Preliminary | Production   |

|-----------|---------|-------------|--------------|

| XC3S100E  |         |             | -MIN, -4, -5 |

| XC3S250E  |         |             | -MIN, -4, -5 |

| XC3S500E  |         |             | -MIN, -4, -5 |

| XC3S1200E |         |             | -MIN, -4, -5 |

| XC3S1600E |         |             | -MIN, -4, -5 |

Table 84: Spartan-3E v1.27 Speed Grade Designations

Table 85 provides the history of the Spartan-3E speed filessince all devices reached Production status.

| Table | 85: | Spartan-3E | Speed File | Version | History |

|-------|-----|------------|------------|---------|---------|

|-------|-----|------------|------------|---------|---------|

| Version | ISE<br>Release | Description                                                                        |

|---------|----------------|------------------------------------------------------------------------------------|

| 1.27    | 9.2.03i        | Added XA Automotive.                                                               |

| 1.26    | 8.2.02i        | Added -0/-MIN speed grade, which includes minimum values.                          |

| 1.25    | 8.2.01i        | Added XA Automotive devices to speed file. Improved model for left and right DCMs. |

| 1.23    | 8.2i           | Updated input setup/hold values based<br>on default IFD_DELAY_VALUE<br>settings.   |

| 1.21    | 8.1.03i        | All Spartan-3E FPGAs and all speed grades elevated to Production status.           |

## Simultaneously Switching Output Guidelines

This section provides guidelines for the recommended maximum allowable number of Simultaneous Switching Outputs (SSOs). These guidelines describe the maximum number of user I/O pins of a given output signal standard that should simultaneously switch in the same direction, while maintaining a safe level of switching noise. Meeting these guidelines for the stated test conditions ensures that the FPGA operates free from the adverse effects of ground and power bounce.

Ground or power bounce occurs when a large number of outputs simultaneously switch in the same direction. The output drive transistors all conduct current to a common voltage rail. Low-to-High transitions conduct to the V<sub>CCO</sub> rail; High-to-Low transitions conduct to the GND rail. The resulting cumulative current transient induces a voltage difference across the inductance that exists between the die pad and the power supply or ground return. The inductance is associated with bonding wires, the package lead frame, and any other signal routing inside the package. Other variables contribute to SSO noise levels, including stray inductance on the PCB as well as capacitive loading at receivers. Any SSO-induced voltage consequently affects internal switching noise margins and ultimately signal quality.

Table 96 and Table 97 provide the essential SSO guidelines. For each device/package combination, Table 96 provides the number of equivalent  $V_{CCO}$ /GND pairs. The

equivalent number of pairs is based on characterization and might not match the physical number of pairs. For each output signal standard and drive strength, Table 97 recommends the maximum number of SSOs, switching in the same direction, allowed per  $V_{CCO}$ /GND pair within an I/O bank. The guidelines in Table 97 are categorized by package style. Multiply the appropriate numbers from Table 96 and Table 97 to calculate the maximum number of SSOs allowed within an I/O bank. Exceeding these SSO guidelines might result in increased power or ground bounce, degraded signal integrity, or increased system jitter.

SSO<sub>MAX</sub>/IO Bank = Table 96 x Table 97

The recommended maximum SSO values assumes that the FPGA is soldered on the printed circuit board and that the board uses sound design practices. The SSO values do not apply for FPGAs mounted in sockets, due to the lead inductance introduced by the socket.

The number of SSOs allowed for quad-flat packages (VQ, TQ, PQ) is lower than for ball grid array packages (FG) due to the larger lead inductance of the quad-flat packages. The results for chip-scale packaging (CP132) are better than quad-flat packaging but not as high as for ball grid array packaging. Ball grid array packages are recommended for applications with a large number of simultaneously switching outputs.

| Device    | Package Style (including Pb-free) |                                 |   |   |   |   |       |       |

|-----------|-----------------------------------|---------------------------------|---|---|---|---|-------|-------|

| Device    | VQ100                             | VQ100 CP132 TQ144 PQ208 FT256 F |   |   |   |   | FG400 | FG484 |

| XC3S100E  | 2                                 | 2                               | 2 | - | - | - | -     | -     |

| XC3S250E  | 2                                 | 2                               | 2 | 3 | 4 | - | -     | -     |

| XC3S500E  | 2                                 | 2                               | - | 3 | 4 | 5 | -     | -     |

| XC3S1200E | -                                 | -                               | - | - | 4 | 5 | 6     | -     |

| XC3S1600E | -                                 | -                               | - | - | - | 5 | 6     | 7     |

Table 96: Equivalent V<sub>CCO</sub>/GND Pairs per Bank

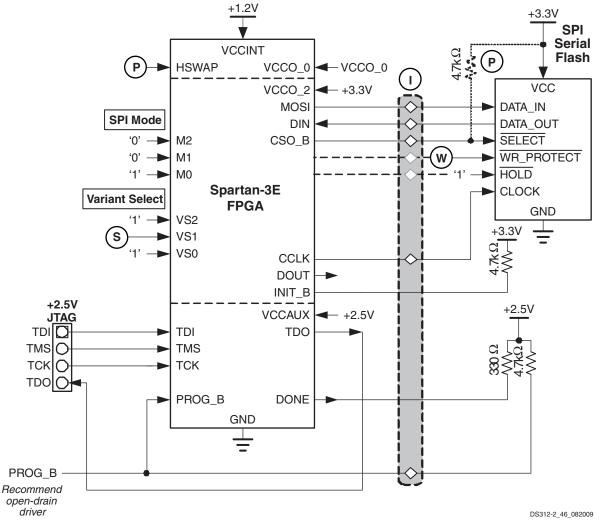

## Configuration and JTAG Timing

## **General Configuration Power-On/Reconfigure Timing**

#### Notes:

- 1. The  $V_{CCINT}\!,\,V_{CCAUX}\!,$  and  $V_{CCO}$  supplies may be applied in any order.

- 2. The Low-going pulse on PROG\_B is optional after power-on but necessary for reconfiguration without a power cycle.

- 3. The rising edge of INIT\_B samples the voltage levels applied to the mode pins (M0 M2).

#### *Figure 73:* Waveforms for Power-On and the Beginning of Configuration

#### Table 111: Power-On Timing and the Beginning of Configuration

| Querra ha a l                    | Description                                                                                                                | Device    | All Speed Grades |     |       |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----|-------|

| Symbol                           | Description                                                                                                                | Device    | Min              | Max | Units |

| T <sub>POR</sub> <sup>(2)</sup>  | The time from the application of $V_{CCINT}$ , $V_{CCAUX}$ , and $V_{CCO}$                                                 | XC3S100E  | -                | 5   | ms    |

|                                  | Bank 2 supply voltage ramps (whichever occurs last) to the rising transition of the INIT_B pin                             | XC3S250E  | -                | 5   | ms    |

|                                  |                                                                                                                            | XC3S500E  | -                | 5   | ms    |

|                                  |                                                                                                                            | XC3S1200E | -                | 5   | ms    |

|                                  |                                                                                                                            | XC3S1600E | -                | 7   | ms    |

| T <sub>PROG</sub>                | The width of the low-going pulse on the PROG_B pin                                                                         | All       | 0.5              | -   | μs    |

| T <sub>PL</sub> <sup>(2)</sup>   | The time from the rising edge of the PROG_B pin to the                                                                     | XC3S100E  | -                | 0.5 | ms    |

|                                  | rising transition on the INIT_B pin                                                                                        | XC3S250E  | -                | 0.5 | ms    |

|                                  |                                                                                                                            | XC3S500E  | -                | 1   | ms    |

|                                  |                                                                                                                            | XC3S1200E | -                | 2   | ms    |

|                                  |                                                                                                                            | XC3S1600E | -                | 2   | ms    |

| T <sub>INIT</sub>                | Minimum Low pulse width on INIT_B output                                                                                   | All       | 250              | -   | ns    |

| T <sub>ICCK</sub> <sup>(3)</sup> | The time from the rising edge of the INIT_B pin to the generation of the configuration clock signal at the CCLK output pin | All       | 0.5              | 4.0 | μs    |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77. This means power must be applied to all  $V_{CCINT}$ ,  $V_{CCO}$ , and  $V_{CCAUX}$  lines.

- 2. Power-on reset and the clearing of configuration memory occurs during this period.

- 3. This specification applies only to the Master Serial, SPI, BPI-Up, and BPI-Down modes.

## Table 133: CP132 Package Pinout (Cont'd)

| Bank | XC3S100E<br>Pin Name   | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                   |

|------|------------------------|----------------------------------|------------|----------------------------------------|

| 2    | N.C. (♠)               | IO_L08P_2/A23                    | N9         | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09N_2/A20                    | M10        | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09P_2/A21                    | N10        | 100E: N.C.<br>Others: DUAL             |

| 2    | IO_L10N_2/VS1/A18      | IO_L10N_2/VS1/A18                | M11        | DUAL                                   |

| 2    | IO_L10P_2/VS2/A19      | IO_L10P_2/VS2/A19                | N11        | DUAL                                   |

| 2    | IO_L11N_2/CCLK         | IO_L11N_2/CCLK                   | N12        | DUAL                                   |

| 2    | IO_L11P_2/VS0/A17      | IO_L11P_2/VS0/A17                | P12        | DUAL                                   |

| 2    | IP/VREF_2              | IP/VREF_2                        | N3         | VREF                                   |

| 2    | IP_L05N_2/M2/GCLK1     | IP_L05N_2/M2/GCLK1               | N6         | DUAL/GCLK                              |

| 2    | IP_L05P_2/RDWR_B/GCLK0 | IP_L05P_2/RDWR_B/GCLK0           | M6         | DUAL/GCLK                              |

| 2    | VCCO_2                 | VCCO_2                           | M8         | VCCO                                   |

| 2    | VCCO_2                 | VCCO_2                           | P3         | VCCO                                   |

| 3    | IO                     | IO                               | J3         | I/O                                    |

| 3    | IP/VREF_3              | IO/VREF_3                        | K3         | 100E: VREF(INPUT)<br>Others: VREF(I/O) |

| 3    | IO_L01N_3              | IO_L01N_3                        | B1         | I/O                                    |

| 3    | IO_L01P_3              | IO_L01P_3                        | B2         | I/O                                    |

| 3    | IO_L02N_3              | IO_L02N_3                        | C2         | I/O                                    |

| 3    | IO_L02P_3              | IO_L02P_3                        | C3         | I/O                                    |

| 3    | N.C. (♠)               | IO_L03N_3                        | D1         | 100E: N.C.<br>Others: I/O              |

| 3    | IO                     | IO_L03P_3                        | D2         | I/O                                    |

| 3    | IO_L04N_3/LHCLK1       | IO_L04N_3/LHCLK1                 | F2         | LHCLK                                  |

| 3    | IO_L04P_3/LHCLK0       | IO_L04P_3/LHCLK0                 | F3         | LHCLK                                  |

| 3    | IO_L05N_3/LHCLK3/IRDY2 | IO_L05N_3/LHCLK3/IRDY2           | G1         | LHCLK                                  |

| 3    | IO_L05P_3/LHCLK2       | IO_L05P_3/LHCLK2                 | F1         | LHCLK                                  |

| 3    | IO_L06N_3/LHCLK5       | IO_L06N_3/LHCLK5                 | H1         | LHCLK                                  |

| 3    | IO_L06P_3/LHCLK4/TRDY2 | IO_L06P_3/LHCLK4/TRDY2           | G3         | LHCLK                                  |

| 3    | IO_L07N_3/LHCLK7       | IO_L07N_3/LHCLK7                 | H3         | LHCLK                                  |

| 3    | IO_L07P_3/LHCLK6       | IO_L07P_3/LHCLK6                 | H2         | LHCLK                                  |

| 3    | IO_L08N_3              | IO_L08N_3                        | L2         | I/O                                    |

| 3    | IO_L08P_3              | IO_L08P_3                        | L1         | I/O                                    |

| 3    | IO_L09N_3              | IO_L09N_3                        | M1         | I/O                                    |

| 3    | IO_L09P_3              | IO_L09P_3                        | L3         | I/O                                    |

| 3    | IP/VREF_3              | IP/VREF_3                        | E2         | VREF                                   |

| 3    | VCCO_3                 | VCCO_3                           | E1         | VCCO                                   |

| 3    | VCCO_3                 | VCCO_3                           | J2         | VCCO                                   |

| GND  | N.C. (GND)             | GND                              | A4         | GND                                    |

| GND  | GND                    | GND                              | A8         | GND                                    |

| GND  | N.C. (GND)             | GND                              | C1         | GND                                    |

| GND  | GND                    | GND                              | C7         | GND                                    |

## FG320: 320-ball Fine-pitch Ball Grid Array

The 320-ball fine-pitch ball grid array package, FG320, supports three different Spartan-3E FPGAs, including the XC3S500E, the XC3S1200E, and the XC3S1600E, as shown in Table 148 and Figure 86.

The FG320 package is an 18 x 18 array of solder balls minus the four center balls.

Table 148 lists all the package pins. They are sorted by bank number and then by pin name of the largest device. Pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

The highlighted rows indicate pinout differences between the XC3S500E, the XC3S1200E, and the XC3S1600E FPGAs. The XC3S500E has 18 unconnected balls, indicated as N.C. (No Connection) in Table 148 and with the black diamond character ( $\blacklozenge$ ) in Table 148 and Figure 86. If the table row is highlighted in tan, then this is an instance where an unconnected pin on the XC3S500E FPGA maps to a VREF pin on the XC3S1200E and XC3S1600E FPGA. If the FPGA application uses an I/O standard that requires a VREF voltage reference, connect the highlighted pin to the VREF voltage supply, even though this does not actually connect to the XC3S500E FPGA. This VREF connection on the board allows future migration to the larger devices without modifying the printed-circuit board.

All other balls have nearly identical functionality on all three devices. Table 147 summarizes the Spartan-3E footprint migration differences for the FG320 package.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx web site at:

http://www.xilinx.com/support/documentation/data\_sheets/s3e\_pin.zip

## Pinout Table

Table 148: FG320 Package Pinout

| Bank | XC3S500E Pin Name | XC3S1200E Pin Name | XC3S1600E Pin Name | FG320<br>Ball | Туре              |

|------|-------------------|--------------------|--------------------|---------------|-------------------|

| 0    | IP                | IO                 | IO                 | A7            | 500E: INPUT       |

|      |                   |                    |                    |               | 1200E: I/O        |

|      |                   |                    |                    |               | <b>1600E:</b> I/O |

| 0    | IO                | IO                 | IO                 | A8            | I/O               |

| 0    | IO                | IO                 | IO                 | A11           | I/O               |

| 0    | N.C. (�)          | IO                 | IO                 | A12           | 500E: N.C.        |

|      |                   |                    |                    |               | 1200E: I/O        |

|      |                   |                    |                    |               | <b>1600E:</b> I/O |

| 0    | IO                | IO                 | IO                 | C4            | I/O               |

| 0    | IP                | IO                 | IO                 | D13           | 500E: INPUT       |

|      |                   |                    |                    |               | 1200E: I/O        |

|      |                   |                    |                    |               | 1600E: I/O        |

| 0    | IO                | IO                 | IO                 | E13           | I/O               |

| 0    | IO                | IO                 | IO                 | G9            | I/O               |

| 0    | IO/VREF_0         | IO/VREF_0          | IO/VREF_0          | B11           | VREF              |

| 0    | IO_L01N_0         | IO_L01N_0          | IO_L01N_0          | A16           | I/O               |

| 0    | IO_L01P_0         | IO_L01P_0          | IO_L01P_0          | B16           | I/O               |

| 0    | IO_L03N_0/VREF_0  | IO_L03N_0/VREF_0   | IO_L03N_0/VREF_0   | C14           | VREF              |

| 0    | IO_L03P_0         | IO_L03P_0          | IO_L03P_0          | D14           | I/O               |

| 0    | IO_L04N_0         | IO_L04N_0          | IO_L04N_0          | A14           | I/O               |

| 0    | IO_L04P_0         | IO_L04P_0          | IO_L04P_0          | B14           | I/O               |

| 0    | IO_L05N_0/VREF_0  | IO_L05N_0/VREF_0   | IO_L05N_0/VREF_0   | B13           | VREF              |

| 0    | IO_L05P_0         | IO_L05P_0          | IO_L05P_0          | A13           | I/O               |

| 0    | IO_L06N_0         | IO_L06N_0          | IO_L06N_0          | E12           | I/O               |

| 0    | IO_L06P_0         | IO_L06P_0          | IO_L06P_0          | F12           | I/O               |

| 0    | IO_L08N_0         | IO_L08N_0          | IO_L08N_0          | F11           | I/O               |

## Table 148: FG320 Package Pinout (Cont'd)

| Bank | XC3S500E Pin Name             | XC3S1200E Pin Name            | XC3S1600E Pin Name            | FG320<br>Ball | Туре                                   |

|------|-------------------------------|-------------------------------|-------------------------------|---------------|----------------------------------------|

| 0    | VCCO_0                        | VCCO_0                        | VCCO_0                        | A9            | VCCO                                   |

| 0    | VCCO_0                        | VCCO_0                        | VCCO_0                        | C6            | VCCO                                   |

| 0    | VCCO_0                        | VCCO_0                        | VCCO_0                        | C13           | VCCO                                   |

| 0    | VCCO_0                        | VCCO_0                        | VCCO_0                        | G8            | VCCO                                   |

| 0    | VCCO_0                        | VCCO_0                        | VCCO_0                        | G11           | VCCO                                   |

| 1    | N.C. (�)                      | IO                            | IO                            | P16           | 500E: N.C.<br>1200E: I/O<br>1600E: I/O |

| 1    | IO_L01N_1/A15                 | IO_L01N_1/A15                 | IO_L01N_1/A15                 | T17           | DUAL                                   |

| 1    | IO_L01P_1/A16                 | IO_L01P_1/A16                 | IO_L01P_1/A16                 | U18           | DUAL                                   |

| 1    | IO_L02N_1/A13                 | IO_L02N_1/A13                 | IO_L02N_1/A13                 | T18           | DUAL                                   |

| 1    | IO_L02P_1/A14                 | IO_L02P_1/A14                 | IO_L02P_1/A14                 | R18           | DUAL                                   |

| 1    | IO_L03N_1/VREF_1              | IO_L03N_1/VREF_1              | IO_L03N_1/VREF_1              | R16           | VREF                                   |

| 1    | IO_L03P_1                     | IO_L03P_1                     | IO_L03P_1                     | R15           | I/O                                    |

| 1    | N.C. (�)                      | IO_L04N_1                     | IO_L04N_1                     | N14           | 500E: N.C.<br>1200E: I/O<br>1600E: I/O |

| 1    | N.C. (�)                      | IO_L04P_1                     | IO_L04P_1                     | N15           | 500E: N.C.<br>1200E: I/O<br>1600E: I/O |

| 1    | IO_L05N_1/VREF_1              | IO_L05N_1/VREF_1              | IO_L05N_1/VREF_1              | M13           | VREF                                   |

| 1    | IO_L05P_1                     | IO_L05P_1                     | IO_L05P_1                     | M14           | I/O                                    |

| 1    | IO_L06N_1                     | IO_L06N_1                     | IO_L06N_1                     | P18           | I/O                                    |

| 1    | IO_L06P_1                     | IO_L06P_1                     | IO_L06P_1                     | P17           | I/O                                    |