# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 612                                                           |

| Number of Logic Elements/Cells | 5508                                                          |

| Total RAM Bits                 | 221184                                                        |

| Number of I/O                  | 66                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 100-TQFP                                                      |

| Supplier Device Package        | 100-VQFP (14x14)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s250e-4vqg100c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan-3E FPGAs provide additional input flexibility by allowing I/O standards to be mixed in different banks. For a particular V<sub>CCO</sub> voltage, Table 6 and Table 7 list all of the

IOSTANDARDs that can be combined and if the IOSTANDARD is supported as an input only or can be used for both inputs and outputs.

#### Table 6: Single-Ended IOSTANDARD Bank Compatibility

|              |                  | v <sub>cco</sub> s | Supply/Comp      | atibility        |                  | Input Rec          | quirements                                         |

|--------------|------------------|--------------------|------------------|------------------|------------------|--------------------|----------------------------------------------------|

| Single-Ended | 1.2V             | 1.5V               | 1.8V             | 2.5V             | 3.3V             | V <sub>REF</sub>   | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) |

| LVTTL        | -                | -                  | -                | -                | Input/<br>Output | N/R <sup>(1)</sup> | N/R                                                |

| LVCMOS33     | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| LVCMOS25     | -                | -                  | -                | Input/<br>Output | Input            | N/R                | N/R                                                |

| LVCMOS18     | -                | -                  | Input/<br>Output | Input            | Input            | N/R                | N/R                                                |

| LVCMOS15     | -                | Input/<br>Output   | Input            | Input            | Input            | N/R                | N/R                                                |

| LVCMOS12     | Input/<br>Output | Input              | Input            | Input            | Input            | N/R                | N/R                                                |

| PCI33_3      | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| PCI66_3      | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| HSTL_I_18    | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| HSTL_III_18  | -                | -                  | Input/<br>Output | Input            | Input            | 1.1                | 1.8                                                |

| SSTL18_I     | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| SSTL2_I      | -                | -                  | -                | Input/<br>Output | Input            | 1.25               | 1.25                                               |

#### Notes:

1. N/R - Not required for input operation.

# **Block RAM Attribute Definitions**

A block RAM has a number of attributes that control its behavior as shown in Table 24.

#### Table 24: Block RAM Attributes

| Function                                                                | Attribute                                           | Possible Values                                                                                       |

|-------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Initial Content for Data Memory, Loaded during Configuration            | INITxx<br>(INIT_00 through INIT3F)                  | Each initialization string defines 32 hex values of the 16384-bit data memory of the block RAM.       |

| Initial Content for Parity Memory, Loaded during Configuration          | INITPxx<br>(INITP_00 through INITP0F)               | Each initialization string defines 32 hex values of the 2048-bit parity data memory of the block RAM. |

| Data Output Latch Initialization                                        | INIT (single-port)<br>INITA, INITB (dual-port)      | Hex value the width of the chosen port.                                                               |

| Data Output Latch Synchronous Set/Reset Value                           | SRVAL (single-port)<br>SRVAL_A, SRVAL_B (dual-port) | Hex value the width of the chosen port.                                                               |

| Data Output Latch Behavior during Write (see Block RAM Data Operations) | WRITE_MODE                                          | WRITE_FIRST, READ_FIRST, NO_CHANGE                                                                    |

# **Block RAM Data Operations**

Writing data to and accessing data from the block RAM are synchronous operations that take place independently on each of the two ports. Table 25 describes the data operations of each port as a result of the block RAM control signals in their default active-High edges. The waveforms for the write operation are shown in the top half of Figure 33, Figure 34, and Figure 35. When the WE and EN signals enable the active edge of CLK, data at the DI input bus is written to the block RAM location addressed by the ADDR lines.

### Table 25: Block RAM Function Table

|     |                                        |       | Input    | t Signals  | 6        |          |           | Output Signals R/       |              | RAM                  | RAM Data             |  |

|-----|----------------------------------------|-------|----------|------------|----------|----------|-----------|-------------------------|--------------|----------------------|----------------------|--|

| GSR | EN                                     | SSR   | WE       | CLK        | ADDR     | DIP      | DI        | DOP                     | DO           | Parity               | Data                 |  |

|     |                                        |       |          |            |          | Immedia  | tely Afte | er Configuration        |              |                      |                      |  |

|     |                                        | Loade | ed Durir | ng Confi   | guration |          |           | Х                       | Х            | INITP_xx             | INIT_xx              |  |

|     |                                        |       |          |            | Global S | et/Reset | Immedi    | ately After Conf        | iguration    |                      |                      |  |

| 1   | Х                                      | Х     | Х        | Х          | Х        | Х        | Х         | INIT                    | INIT         | No Chg               | No Chg               |  |

|     |                                        |       |          |            |          |          | RAM D     | isabled                 |              |                      |                      |  |

| 0   | 0                                      | Х     | Х        | Х          | Х        | Х        | Х         | No Chg                  | No Chg       | No Chg               | No Chg               |  |

|     | Synchronous Set/Reset                  |       |          |            |          |          |           |                         |              |                      |                      |  |

| 0   | 1                                      | 1     | 0        | $\uparrow$ | Х        | Х        | Х         | SRVAL                   | SRVAL        | No Chg               | No Chg               |  |

|     | Synchronous Set/Reset During Write RAM |       |          |            |          |          |           |                         |              |                      |                      |  |

| 0   | 1                                      | 1     | 1        | ↑          | addr     | pdata    | Data      | SRVAL                   | SRVAL        | RAM(addr)<br>← pdata | RAM(addr)<br>← data  |  |

|     |                                        |       |          |            |          | Read R   | AM, no \  | <b>Write Operation</b>  |              |                      |                      |  |

| 0   | 1                                      | 0     | 0        | $\uparrow$ | addr     | Х        | Х         | RAM(pdata)              | RAM(data)    | No Chg               | No Chg               |  |

|     |                                        |       |          |            | Write    | e RAM, S | imultan   | eous Read Oper          | ation        |                      |                      |  |

| 0   | 1                                      | 0     | 1        | $\uparrow$ | addr     | pdata    | Data      |                         | WRITE_MODE : | = WRITE_FIRST        |                      |  |

|     |                                        |       |          |            |          |          |           | pdata                   | data         | RAM(addr)<br>← pdata | RAM(addr)<br>← data  |  |

|     |                                        |       |          |            |          |          |           | WRITE_MODE = READ_FIRST |              |                      |                      |  |

|     |                                        |       |          |            |          |          |           | RAM(data)               | RAM(data)    | RAM(addr)<br>← pdata | RAM(addr)<br>← pdata |  |

|     |                                        |       |          |            |          |          |           |                         | WRITE_MODE   | = NO_CHANGE          |                      |  |

|     |                                        |       |          |            |          |          |           | No Chg                  | No Chg       | RAM(addr)<br>← pdata | RAM(addr)<br>← pdata |  |

cancel out the clock skew. When the DLL phase-aligns the CLK0 signal with the CLKIN signal, it asserts the LOCKED output, indicating a lock on to the CLKIN signal.

#### **DLL Attributes and Related Functions**

The DLL unit has a variety of associated attributes as described in Table 29. Each attribute is described in detail in the sections that follow.

#### Table 29: DLL Attributes

**EXILINX**

| Attribute         | Description                                                                                                           | Values                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| CLK_FEEDBACK      | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                                      | NONE, <u>1X</u> , 2X                                                                                  |

| CLKIN_DIVIDE_BY_2 | Halves the frequency of the CLKIN signal just as it enters the DCM                                                    | <i>FALSE</i> , TRUE                                                                                   |

| CLKDV_DIVIDE      | Selects the constant used to divide the CLKIN input frequency to generate the CLKDV output frequency                  | 1.5, <u>2</u> , 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6.0, 6.5, 7.0, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, and 16 |

| CLKIN_PERIOD      | Additional information that allows the DLL to operate with the most efficient lock time and the best jitter tolerance | Floating-point value representing the CLKIN period in nanoseconds                                     |

#### **DLL Clock Input Connections**

For best results, an external clock source enters the FPGA via a Global Clock Input (GCLK). Each specific DCM has four possible direct, optimal GCLK inputs that feed the DCM's CLKIN input, as shown in Table 30. Table 30 also provides the specific pin numbers by package for each GCLK input. The two additional DCM's on the XC3S1200E and XC3S1600E have similar optimal connections from the left-edge LHCLK and the right-edge RHCLK inputs, as described in Table 31 and Table 32.

The DCM supports differential clock inputs (for example, LVDS, LVPECL\_25) via a pair of GCLK inputs that feed an internal single-ended signal to the DCM's CLKIN input.

#### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes. P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins during configuration or High to disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is

available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

The FPGA's DOUT pin is used in daisy-chain applications, described later. In a single-FPGA application, the FPGA's DOUT pin is not used but is actively driving during the configuration process.

| Pin Name   | FPGA<br>Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | During Configuration                                                                                                                                                                                                                                                                                                              | After Configuration                                                                                       |

|------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| HSWAP<br>P | Input                              | <b>User I/O Pull-Up Control</b> . When Low during configuration, enables pull-up resistors in all I/O pins to respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration<br>1: No pull-ups                                                                                                                                                                                                                                                                   | Drive at valid logic level throughout configuration.                                                                                                                                                                                                                                                                              | User I/O                                                                                                  |

| M[2:0]     | Input                              | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                                      | M2 = 0, M1 = 0, M0 = 0. Sampled<br>when INIT_B goes High.                                                                                                                                                                                                                                                                         | User I/O                                                                                                  |

| DIN        | Input                              | Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receives serial data from PROM's D0 output.                                                                                                                                                                                                                                                                                       | User I/O                                                                                                  |

| CCLK       | Output                             | <b>Configuration Clock</b> . Generated by FPGA internal oscillator. Frequency controlled by <i>ConfigRate</i> bitstream generator option. If CCLK PCB trace is long or has multiple connections, terminate this output to maintain signal integrity. See CCLK Design Considerations.                                                                                                                                                                                              | Drives PROM's CLK clock input.                                                                                                                                                                                                                                                                                                    | User I/O                                                                                                  |

| DOUT       | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Actively drives. Not used in<br>single-FPGA designs. In a<br>daisy-chain configuration, this pin<br>connects to DIN input of the next<br>FPGA in the chain.                                                                                                                                                                       | User I/O                                                                                                  |

| INIT_B     | Open-drain<br>bidirectional<br>I/O | <b>Initialization Indicator</b> . Active Low. Goes<br>Low at start of configuration during<br>Initialization memory clearing process.<br>Released at end of memory clearing, when<br>mode select pins are sampled. Requires<br>external 4.7 k $\Omega$ pull-up resistor to VCCO_2.                                                                                                                                                                                                | Connects to PROM's OE/RESET<br>input. FPGA clears PROM's<br>address counter at start of<br>configuration, enables outputs<br>during configuration. PROM also<br>holds FPGA in Initialization state<br>until PROM reaches Power-On<br>Reset (POR) state. If CRC error<br>detected during configuration,<br>FPGA drives INIT_B Low. | User I/O. If unused in<br>the application, drive<br>INIT_B High.                                          |

| DONE       | Open-drain<br>bidirectional<br>I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                     | Connects to PROM's chip-enable<br>(CE) input. Enables PROM during<br>configuration. Disables PROM<br>after configuration.                                                                                                                                                                                                         | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully<br>configured. |

| PROG_B     | Input                              | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High. Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High during configuration<br>to allow configuration to start.<br>Connects to PROM's CF pin,<br>allowing JTAG PROM<br>programming algorithm to<br>reprogram the FPGA.                                                                                                                                                      | Drive PROG_B Low<br>and release to<br>reprogram FPGA.                                                     |

#### Table 50: Serial Master Mode Connections

**E** XILINX.

SPI serial Flash PROMs and the Atmel AT45DB-series Data Flash PROMs using the <u>Platform Cable USB</u>, <u>Xilinx</u> <u>Parallel IV</u>, or other compatible programming cable.

# Byte-Wide Peripheral Interface (BPI) Parallel Flash Mode

For additional information, refer to the "Master BPI Mode" chapter in UG332.

In Byte-wide Peripheral Interface (BPI) mode (M[2:0] = <0:1:0> or <0:1:1>), a Spartan-3E FPGA configures itself from an industry-standard parallel NOR Flash PROM, as illustrated in Figure 58. The FPGA generates up to a 24-bit address lines to access an attached parallel Flash. Only 20 address lines are generated for Spartan-3E FPGAs in the TQ144 package. Similarly, the XC3S100E FPGA in the CP132 package only has 20 address lines while the XC3S250E and XC3S500E FPGAs in the same package have 24 address lines. When using the VQ100 package, the BPI mode is not available when using parallel NOR Flash, but is supported using parallel Platform Flash (XCFxxP).

The BPI configuration interface is primarily designed for standard parallel NOR Flash PROMs and supports both byte-wide (x8) and byte-wide/halfword (x8/x16) PROMs. The interface functions with halfword-only (x16) PROMs, but the upper byte in a portion of the PROM remains unused. For configuration, the BPI interface does not require any specific Flash PROM features, such as boot block or a specific sector size.

The BPI interface also functions with Xilinx parallel Platform Flash PROMs (XCFxxP), although the FPGA's address lines are left unconnected.

The BPI interface also works equally wells with other asynchronous memories that use a similar SRAM-style interface such as SRAM, NVRAM, EEPROM, EPROM, or masked ROM.

NAND Flash memory is commonly used in memory cards for digital cameras. Spartan-3E FPGAs do not configure directly from NAND Flash memories.

The FPGA's internal oscillator controls the interface timing and the FPGA supplies the clock on the CCLK output pin. However, the CCLK signal is not used in single FPGA applications. Similarly, the FPGA drives three pins Low during configuration (LDC[2:0]) and one pin High during configuration (HDC) to the PROM's control inputs.

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | During Configuration                               | After Configuration                                                                                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                        | Low indicates that the FPGA is not yet configured. | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA is<br>successfully configured.                                                              |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High.<br>Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High to allow configuration to start.      | Drive PROG_B Low and<br>release to reprogram<br>FPGA. Hold PROG_B to<br>force FPGA I/O pins into<br>Hi-Z, allowing direct<br>programming access to<br>Flash PROM pins. |

#### Table 59: Byte-Wide Peripheral Interface (BPI) Connections (Cont'd)

#### **Voltage Compatibility**

V The FPGA's parallel Flash interface signals are within I/O Banks 1 and 2. The majority of parallel Flash PROMs use a single 3.3V supply voltage. Consequently, in most cases, the FPGA's VCCO\_1 and VCCO\_2 supply voltages must also be 3.3V to match the parallel Flash PROM. There are some 1.8V parallel Flash PROMs available and the FPGA interfaces with these devices if the VCCO\_1 and VCCO\_2 supplies are also 1.8V.

# Power-On Precautions if PROM Supply is Last in Sequence

Like SPI Flash PROMs, parallel Flash PROMs typically require some amount of internal initialization time when the supply voltage reaches its minimum value.

The PROM supply voltage also connects to the FPGA's VCCO\_2 supply input. In many systems, the PROM supply feeding the FPGA's VCCO\_2 input is valid before the FPGA's other V<sub>CCINT</sub> and V<sub>CCAUX</sub> supplies, and consequently, there is no issue. However, if the PROM supply is last in the sequence, a potential race occurs between the FPGA and the parallel Flash PROM. See

Power-On Precautions if 3.3V Supply is Last in Sequence for a similar description of the issue for SPI Flash PROMs.

#### **Supported Parallel NOR Flash PROM Densities**

Table 60 indicates the smallest usable parallel Flash PROMto program a single Spartan-3E FPGA. Parallel Flashdensity is specified in bits but addressed as bytes. TheFPGA presents up to 24 address lines during configurationbut not all are required for single FPGA applications.Table 60 shows the minimum required number of addresslines between the FPGA and parallel Flash PROM. Theactual number of address line required depends on thedensity of the attached parallel Flash PROM.

A multiple-FPGA daisy-chained application requires a parallel Flash PROM large enough to contain the sum of the FPGA file sizes. An application can also use a larger-density parallel Flash PROM to hold additional data beyond just FPGA configuration data. For example, the parallel Flash PROM can also contain the application code for a MicroBlaze RISC processor core implemented within the Spartan-3E FPGA. After configuration, the MicroBlaze processor can execute directly from external Flash or can copy the code to other, faster system memory before executing the code.

#### Table 60: Number of Bits to Program a Spartan-3E FPGA and Smallest Parallel Flash PROM

| Spartan-3E FPGA | Uncompressed<br>File Sizes (bits) | Smallest Usable<br>Parallel Flash PROM | Minimum Required<br>Address Lines |

|-----------------|-----------------------------------|----------------------------------------|-----------------------------------|

| XC3S100E        | 581,344                           | 1 Mbit                                 | A[16:0]                           |

| XC3S250E        | 1,353,728                         | 2 Mbit                                 | A[17:0]                           |

| XC3S500E        | 2,270,208                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1200E       | 3,841,184                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1600E       | 5,969,696                         | 8 Mbit                                 | A[19:0]                           |

can also be eliminated from the interface. However, RDWR\_B must remain Low during configuration.

After configuration, all of the interface pins except DONE and PROG\_B are available as user I/Os. Alternatively, the bidirectional SelectMAP configuration interface is available after configuration. To continue using SelectMAP mode, set the **Persist** bitstream generator option to **Yes**. The external host can then read and verify configuration data. The Persist option will maintain A20-A23 as configuration pins although they are not used in SelectMAP mode.

The Slave Parallel mode is also used with BPI mode to create multi-FPGA daisy-chains. The lead FPGA is set for BPI mode configuration; all the downstream daisy-chain FPGAs are set for Slave Parallel configuration, as highlighted in Figure 59.

| Pin Name | Pin Name FPGA Direction Description |                                                                                                                                                                                                        | During Configuration                                                                                                                                                                                            | After Configuration                                                                                                     |

|----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| HSWAP    | Input                               | <b>User I/O Pull-Up Control</b> . When<br>Low during configuration, enables<br>pull-up resistors in all I/O pins to<br>respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration | Drive at valid logic level throughout configuration.                                                                                                                                                            | User I/O                                                                                                                |

|          |                                     | 1: No pull-ups                                                                                                                                                                                         |                                                                                                                                                                                                                 |                                                                                                                         |

| M[2:0]   | Input                               | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                           | M2 = 1, M1 = 1, M0 = 0 Sampled<br>when INIT_B goes High.                                                                                                                                                        | User I/O                                                                                                                |

| D[7:0]   | Input                               | Data Input.                                                                                                                                                                                            | Byte-wide data provided by host.<br>FPGA captures data on rising<br>CCLK edge.                                                                                                                                  | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| BUSY     | Output                              | Busy Indicator.                                                                                                                                                                                        | If CCLK frequency is < 50 MHz,<br>this pin may be ignored. When<br>High, indicates that the FPGA is<br>not ready to receive additional<br>configuration data. Host must hold<br>data an additional clock cycle. | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| CSI_B    | Input                               | Chip Select Input. Active Low.                                                                                                                                                                         | Must be Low throughout configuration.                                                                                                                                                                           | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| RDWR_B   | Input                               | <b>Read/Write Control</b> . Active Low write enable.                                                                                                                                                   | Must be Low throughout configuration.                                                                                                                                                                           | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| CCLK     | Input                               | <b>Configuration Clock</b> . If CCLK PCB trace is long or has multiple connections, terminate this output to maintain signal integrity. See CCLK Design Considerations.                                | External clock.                                                                                                                                                                                                 | User I/O If bitstream option<br><i>Persist=Yes</i> , becomes<br>part of SelectMap parallel<br>peripheral interface.     |

| CSO_B    | Output                              | Chip Select Output. Active Low.                                                                                                                                                                        | Not used in single FPGA<br>applications. In a daisy-chain<br>configuration, this pin connects to<br>the CSI_B pin of the next FPGA in<br>the chain. Actively drives.                                            | User I/O                                                                                                                |

#### Table 65: Slave Parallel Mode Connections

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at the start of<br>configuration during the Initialization<br>memory clearing process. Released<br>at the end of memory clearing, when<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                                                                      | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                       |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                            | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer,<br>forces the FPGA to restart its<br>configuration process by clearing<br>configuration memory and resetting<br>the DONE and INIT_B pins once<br>PROG_B returns High. Recommend<br>external 4.7 k $\Omega$ pull-up resistor to<br>2.5V. Internal pull-up value may be<br>weaker (see Table 78). If driving<br>externally with a 3.3V output, use an<br>open-drain or open-collector driver<br>or use a current limiting series<br>resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

#### Table 65: Slave Parallel Mode Connections (Cont'd)

# **Voltage Compatibility**

W Most Slave Parallel interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 1.8V, 2.5V, or 3.3V to match the requirements of the external host, ideally 2.5V. Using 1.8V or 3.3V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

#### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain. Use Slave Parallel mode (M[2:0] = <1:1:0>) for all FPGAs in the daisy-chain. The schematic in Figure 62 is optimized for FPGA downloading and does not support the SelectMAP read interface. The FPGA's RDWR\_B pin must be Low during configuration.

After the lead FPGA is filled with its configuration data, the lead FPGA enables the next FPGA in the daisy-chain by asserting is chip-select output, CSO\_B.

# **XILINX**.

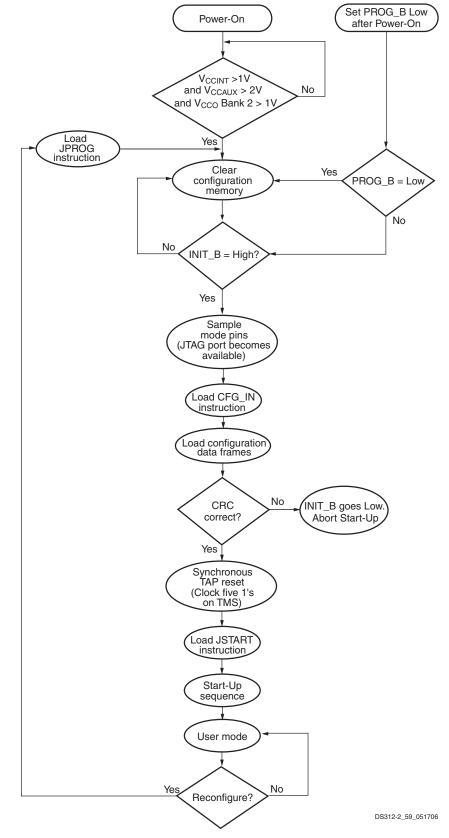

Figure 67: Boundary-Scan Configuration Flow Diagram

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/16/07 | 3.5     | Added information about new Spartan-3 Generation user guides (Design Documentation Available).<br>Added cross-references to <u>UG331</u> : Spartan-3 Generation FPGA User Guide and to <u>UG332</u> : Spartan-3<br>Generation Configuration User Guide. Added note about possible JTAG configuration issues when the<br>FPGA mode pins are set for Master mode and using software prior to ISE 9.1.01i (JTAG Mode).<br>Removed a few lingering references to "weak" pull-up resistors, including in Figure 12. Removed<br>vestigial references regarding the LDC[2:0] and HDC pins during Slave Parallel Mode configuration.<br>These pins are not used in this configuration mode. |

| 05/29/07 | 3.6     | Added information about HSWAP and PCI differences between steppings to Table 71. Removed<br>"Performance Differences between Global Buffers" to match improved specs in Module 3. Updated<br>PROG_B pulse width descriptions to match specification in Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 04/18/08 | 3.7     | Corrected Figure 6 to show six taps and updated associated text. Added note for recommended pull-up on DONE in Table 55 and elsewhere. Added a caution regarding Persist of pins A20-A23. Updated Stepping description in Table 71 to note that only Stepping 1 is in production today. Updated links.                                                                                                                                                                                                                                                                                                                                                                              |

| 08/26/09 | 3.8     | Added a frequency limitation to Equation 6. Added a new Equation 7 with a frequency limitation. Added a Spread Spectrum, page 56 paragraph. Added Table 42, page 60. Updated a Flash vendor name in Table 61, page 88. Removed the < symbol from the flash read access times in Table 62, page 88. Revised the first paragraph in Configuration Sequence, page 101. Revised the first paragraph in Power-On Behavior, page 110. Revised the second paragraph in Production Stepping, page 111. Revised the first paragraph in Ordering a Later Stepping, page 111.                                                                                                                  |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated the design note section in VARIABLE Phase Shift Mode. Added the VQ100 to the Quadrant Clock Routing section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

# **Power Supply Specifications**

#### Table 74: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                 | Min | Max | Units |

|---------------------|---------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply | 0.8 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the $V_{CCO}$ Bank 2 supply   | 0.4 | 1.0 | V     |

#### Notes:

To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 75: Supply Voltage Ramp Rate

| Symbol              | Description                                                 | Min | Мах | Units |

|---------------------|-------------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid V <sub>CCINT</sub> supply level | 0.2 | 50  | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid $V_{CCAUX}$ supply level        | 0.2 | 50  | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid $V_{CCO}$ Bank 2 supply level   | 0.2 | 50  | ms    |

#### Notes:

V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 76: Supply Voltage Levels Necessary for Preserving RAM Contents

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

#### Notes:

1. RAM contents include configuration data.

V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

# Block RAM Timing

# Table 103: Block RAM Timing

| Symbol            | Description                                                                                                                                                            |      | -5   | -    | Units |     |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-----|

|                   |                                                                                                                                                                        | Min  | Max  | Min  | Мах   |     |

| Clock-to-O        | utput Times                                                                                                                                                            |      |      |      |       |     |

| Т <sub>ВСКО</sub> | When reading from block RAM, the delay from the active transition at the CLK input to data appearing at the DOUT output                                                | -    | 2.45 | -    | 2.82  | ns  |

| Setup Time        | es l                                                                                                                                                                   |      |      |      |       | -   |

| T <sub>BACK</sub> | Setup time for the ADDR inputs before the active transition at the CLK input of the block RAM                                                                          | 0.33 | -    | 0.38 | -     | ns  |

| T <sub>BDCK</sub> | Setup time for data at the DIN inputs before the active transition at the CLK input of the block RAM                                                                   |      |      | 0.23 | -     | ns  |

| T <sub>BECK</sub> | Setup time for the EN input before the active transition at the CLK input of the block RAM                                                                             | 0.67 | -    | 0.77 | -     | ns  |

| T <sub>BWCK</sub> | Setup time for the WE input before the active transition at the CLK input of the block RAM                                                                             | 1.09 | -    | 1.26 | -     | ns  |

| Hold Times        | ;<br>;                                                                                                                                                                 |      | 1    |      |       |     |

| T <sub>BCKA</sub> | Hold time on the ADDR inputs after the active transition at the CLK input                                                                                              | 0.12 | -    | 0.14 | -     | ns  |

| T <sub>BCKD</sub> | Hold time on the DIN inputs after the active transition at the CLK input                                                                                               | 0.12 | -    | 0.13 | -     | ns  |

| T <sub>BCKE</sub> | Hold time on the EN input after the active transition at the CLK input                                                                                                 | 0    | -    | 0    | -     | ns  |

| T <sub>BCKW</sub> | Hold time on the WE input after the active transition at the $\ensuremath{CLK}$ input                                                                                  | 0    | -    | 0    | -     | ns  |

| Clock Timi        | ng                                                                                                                                                                     |      |      |      |       | -   |

| T <sub>BPWH</sub> | High pulse width of the CLK signal                                                                                                                                     | 1.39 | -    | 1.59 | -     | ns  |

| T <sub>BPWL</sub> | Low pulse width of the CLK signal                                                                                                                                      | 1.39 | -    | 1.59 | -     | ns  |

| Clock Freq        | uency                                                                                                                                                                  |      |      |      |       |     |

| F <sub>BRAM</sub> | Block RAM clock frequency. RAM read output value written<br>back into RAM, for shift-registers and circular buffers.<br>Write-only or read-only performance is faster. | 0    | 270  | 0    | 230   | MHz |

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/26/09 | 3.8     | Added reference to XAPP459 in Table 73 note 2. Updated BPI timing in Figure 77, Table 119, and Table 120. Removed V <sub>REF</sub> requirements for differential HSTL and differential SSTL in Table 95. Added Spread Spectrum paragraph. Revised hold times for $T_{IOICKPD}$ in Table 88 and setup times for $T_{DICK}$ in Table 98. Added note 4 to Table 106 and note 3 to Table 107, and updated note 6 for Table 107 to add input jitter. |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs. Revised note 2 in Table 73. Revised note 2 and $V_{\rm IN}$ description in Table 77, and added note 5. Added note 3 to Table 78.                                                                                                                                                                                                                                   |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

# Spartan-3 FPGA Family: Pinout Descriptions

DS312 (4.0) October 29, 2012

#### **Product Specification**

# Introduction

This section describes the various pins on a Spartan®-3E FPGA and how they connect within the supported component packages.

# **Pin Types**

Most pins on a Spartan-3E FPGA are general-purpose, user-defined I/O pins. There are, however, up to 11 different functional types of pins on Spartan-3E packages, as outlined in Table 124. In the package footprint drawings that follow, the individual pins are color-coded according to pin type as in the table.

| Type / Color<br>Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin Name(s) in Type <sup>(1)</sup>                                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                  | Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential I/Os.                                                                                                                                                                                                                                                                                                                                                                                                                           | IO<br>IO_Lxxy_#                                                                                                                                                                |

| INPUT                | Unrestricted, general-purpose input-only pin. This pin does not have an output structure, differential termination resistor, or PCI clamp diode.                                                                                                                                                                                                                                                                                                                                                                                  | IP<br>IP_Lxxy_#                                                                                                                                                                |

| DUAL                 | Dual-purpose pin used in some configuration modes during the configuration<br>process and then usually available as a user I/O after configuration. If the pin is not<br>used during configuration, this pin behaves as an I/O-type pin. Some of the<br>dual-purpose pins are also shared with bottom-edge global (GCLK) or right-half<br>(RHCLK) clock inputs. See the Configuration section in Module 2 for additional<br>information on these signals.                                                                         | M[2:0]<br>HSWAP<br>CCLK<br>MOSI/CSI_B<br>D[7:1]<br>D0/DIN<br>CSO_B<br>RDWR_B<br>BUSY/DOUT<br>INIT_B<br>A[23:20]<br>A19/VS2<br>A18/VS1<br>A17/VS0<br>A[16:0]<br>LDC[2:0]<br>HDC |

| VREF                 | Dual-purpose pin that is either a user-I/O pin or Input-only pin, or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected.                                                                                                                                                                                                                                              | IP/VREF_#<br>IP_Lxxy_#/VREF_#<br>IO/VREF_#<br>IO_Lxxy_#/VREF_#                                                                                                                 |

| CLK                  | Either a user-I/O pin or Input-only pin, or an input to a specific clock buffer driver.<br>Every package has 16 global clock inputs that optionally clock the entire device. The<br>RHCLK inputs optionally clock the right-half of the device. The LHCLK inputs<br>optionally clock the left-half of the device. Some of the clock pins are shared with the<br>dual-purpose configuration pins and are considered DUAL-type. See the Clocking<br>Infrastructure section in Module 2 for additional information on these signals. | IO_Lxxy_#/GCLK[15:10, 7:2]<br>IP_Lxxy_#/GCLK[9:8, 1:0]<br>IO_Lxxy_#/LHCLK[7:0]<br>IO_Lxxy_#/RHCLK[7:0]                                                                         |

| CONFIG               | Dedicated configuration pin. Not available as a user-I/O pin. Every package has two dedicated configuration pins. These pins are powered by VCCAUX. See the Configuration section in Module 2 for details.                                                                                                                                                                                                                                                                                                                        | DONE, PROG_B                                                                                                                                                                   |

| JTAG                 | Dedicated JTAG pin. Not available as a user-I/O pin. Every package has four dedicated JTAG pins. These pins are powered by VCCAUX.                                                                                                                                                                                                                                                                                                                                                                                                | TDI, TMS, TCK, TDO                                                                                                                                                             |

| GND                  | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND                                                                                                                                                                            |

#### Table 124: Types of Pins on Spartan-3E FPGAs

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

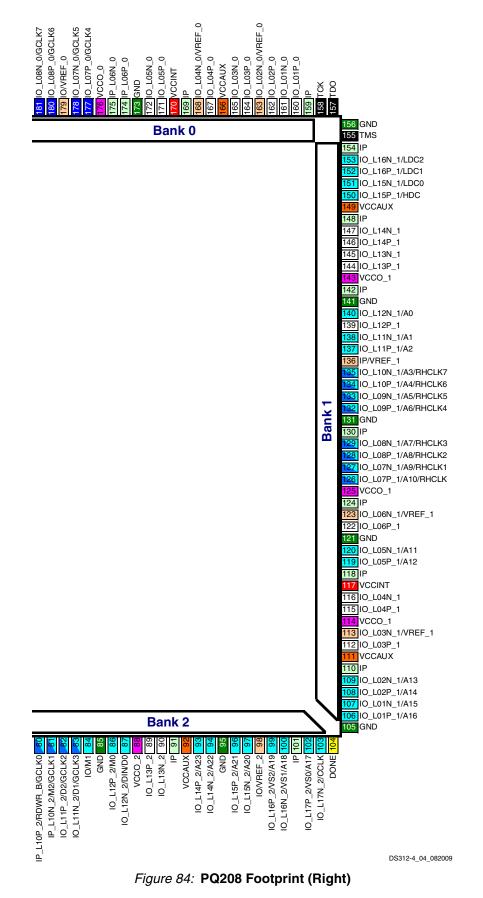

# PQ208 Footprint (Right)

### Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name             | XC3S500E Pin Name             | XC3S1200E Pin Name            | FT256<br>Ball | Туре                                  |

|------|-------------------------------|-------------------------------|-------------------------------|---------------|---------------------------------------|

| 1    | N.C. (�)                      | IO_L05P_1                     | IO_L05P_1                     | L12           | 250E: N.C.<br>500E: I/O<br>1200E: I/O |

| 1    | IO_L06N_1                     | IO_L06N_1                     | IO_L06N_1                     | L15           | I/O                                   |

| 1    | IO_L06P_1                     | IO_L06P_1                     | IO_L06P_1                     | L14           | I/O                                   |

| 1    | IO_L07N_1/A11                 | IO_L07N_1/A11                 | IO_L07N_1/A11                 | K12           | DUAL                                  |

| 1    | IO_L07P_1/A12                 | IO_L07P_1/A12                 | IO_L07P_1/A12                 | K13           | DUAL                                  |

| 1    | IO_L08N_1/VREF_1              | IO_L08N_1/VREF_1              | IO_L08N_1/VREF_1              | K14           | VREF                                  |

| 1    | IO_L08P_1                     | IO_L08P_1                     | IO_L08P_1                     | K15           | I/O                                   |

| 1    | IO_L09N_1/A9/RHCLK1           | IO_L09N_1/A9/RHCLK1           | IO_L09N_1/A9/RHCLK1           | J16           | RHCLK/DUAL                            |

| 1    | IO_L09P_1/A10/RHCLK0          | IO_L09P_1/A10/RHCLK0          | IO_L09P_1/A10/RHCLK0          | K16           | RHCLK/DUAL                            |

| 1    | IO_L10N_1/A7/RHCLK3/<br>TRDY1 | IO_L10N_1/A7/RHCLK3/<br>TRDY1 | IO_L10N_1/A7/RHCLK3/<br>TRDY1 | J13           | RHCLK/DUAL                            |

| 1    | IO_L10P_1/A8/RHCLK2           | IO_L10P_1/A8/RHCLK2           | IO_L10P_1/A8/RHCLK2           | J14           | RHCLK/DUAL                            |

| 1    | IO_L11N_1/A5/RHCLK5           | IO_L11N_1/A5/RHCLK5           | IO_L11N_1/A5/RHCLK5           | H14           | RHCLK/DUAL                            |

| 1    | IO_L11P_1/A6/RHCLK4/<br>IRDY1 | IO_L11P_1/A6/RHCLK4/<br>IRDY1 | IO_L11P_1/A6/RHCLK4/<br>IRDY1 | H15           | RHCLK/DUAL                            |

| 1    | IO_L12N_1/A3/RHCLK7           | IO_L12N_1/A3/RHCLK7           | IO_L12N_1/A3/RHCLK7           | H11           | RHCLK/DUAL                            |

| 1    | IO_L12P_1/A4/RHCLK6           | IO_L12P_1/A4/RHCLK6           | IO_L12P_1/A4/RHCLK6           | H12           | RHCLK/DUAL                            |

| 1    | IO_L13N_1/A1                  | IO_L13N_1/A1 IO_L13N_1/A1     |                               | G16           | DUAL                                  |

| 1    | IO_L13P_1/A2                  | IO_L13P_1/A2                  | IO_L13P_1/A2                  | G15           | DUAL                                  |

| 1    | IO_L14N_1/A0                  | IO_L14N_1/A0                  | IO_L14N_1/A0                  | G14           | DUAL                                  |

| 1    | IO_L14P_1                     | IO_L14P_1                     | IO_L14P_1                     | G13           | I/O                                   |

| 1    | IO_L15N_1                     | IO_L15N_1                     | IO_L15N_1                     | F15           | I/O                                   |

| 1    | IO_L15P_1                     | IO_L15P_1                     | IO_L15P_1                     | F14           | I/O                                   |

| 1    | IO_L16N_1                     | IO_L16N_1                     | IO_L16N_1                     | F12           | I/O                                   |

| 1    | IO_L16P_1                     | IO_L16P_1                     | IO_L16P_1                     | F13           | I/O                                   |

| 1    | N.C. (�)                      | IO_L17N_1                     | IO_L17N_1                     | E16           | 250E: N.C.<br>500E: I/O<br>1200E: I/O |

| 1    | N.C. (�).                     | IO_L17P_1                     | IO_L17P_1                     | E13           | 250E: N.C.<br>500E: I/O<br>1200E: I/O |