Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 612                                                           |

| Number of Logic Elements/Cells | 5508                                                          |

| Total RAM Bits                 | 221184                                                        |

| Number of I/O                  | 172                                                           |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 256-LBGA                                                      |

| Supplier Device Package        | 256-FTBGA (17x17)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s250e-5ftg256c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan-3 FPGA Family: Introduction and Ordering Information

# Configuration

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

# I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, 66 MHz

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

Table 2: Available User I/Os and Differential (Diff) I/O Pairs

| Package                | VQ1<br>VQG                   |                      |                | 132<br>3132          |             | 144<br>3144   |                 | 208<br>3208   | FT2             | 256<br>3256   | _               | 320<br>3320    |                 | 400<br>3400     | FG4<br>FGG      |                 |

|------------------------|------------------------------|----------------------|----------------|----------------------|-------------|---------------|-----------------|---------------|-----------------|---------------|-----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| Footprint<br>Size (mm) | 16 x                         | 16                   | 8              | x 8                  | 22 :        | x 22          | 30.5            | x 30.5        | 17 >            | k 17          | 19 2            | x 19           | 21 2            | c 21            | 23 2            | x 23            |

| Device                 | User                         | Diff                 | User           | Diff                 | User        | Diff          | User            | Diff          | User            | Diff          | User            | Diff           | User            | Diff            | User            | Diff            |

| XC3S100E               | <b>66<sup>(2)</sup></b> 9(7) | <b>30</b> <i>(2)</i> | <b>83</b> (11) | <b>35</b> <i>(2)</i> | 108<br>(28) | <b>40</b> (4) | -               | -             | -               | -             | -               | -              | -               | -               | -               | -               |

| XC3S250E               | <b>66</b> (7)                | <b>30</b> <i>(2)</i> | <b>92</b> (7)  | <b>41</b> <i>(2)</i> | 108<br>(28) | <b>40</b> (4) | <b>158</b> (32) | <b>65</b> (5) | <b>172</b> (40) | <b>68</b> (8) | -               | -              | -               | -               | -               | -               |

| XC3S500E               | <b>66</b> <sup>(3)</sup> (7) | <b>30</b> <i>(2)</i> | <b>92</b> (7)  | <b>41</b> <i>(2)</i> | -           | -             | <b>158</b> (32) | <b>65</b> (5) | <b>190</b> (41) | <b>77</b> (8) | <b>232</b> (56) | <b>92</b> (12) | -               | -               | -               | -               |

| XC3S1200E              | -                            | -                    | -              | -                    | -           | -             | -               | -             | 190<br>(40)     | <b>77</b> (8) | <b>250</b> (56) | <b>99</b> (12) | <b>304</b> (72) | <b>124</b> (20) | -               | -               |

| XC3S1600E              | -                            | -                    | -              | -                    | -           | -             | -               | -             | -               | -             | <b>250</b> (56) | <b>99</b> (12) | <b>304</b> (72) | <b>124</b> (20) | <b>376</b> (82) | <b>156</b> (21) |

#### Notes:

- 1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

- 2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

- 3. The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical and general references to the VQ100 will apply to the XC3S500E.

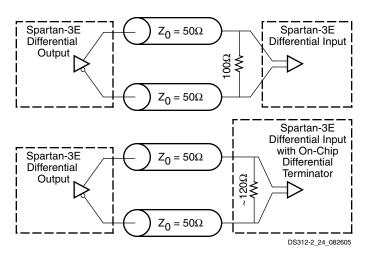

Figure 11: Differential Inputs and Outputs

# **Pull-Up and Pull-Down Resistors**

Pull-up and pull-down resistors inside each IOB optionally force a floating I/O or Input-only pin to a determined state. Pull-up and pull-down resistors are commonly applied to unused I/Os, inputs, and three-state outputs, but can be used on any I/O or Input-only pin. The pull-up resistor connects an IOB to  $V_{CCO}$  through a resistor. The resistance value depends on the  $V_{CCO}$  voltage (see Module 3, DC and Switching Characteristics for the specifications). The pull-down resistor similarly connects an IOB to ground with a resistor. The PULLUP and PULLDOWN attributes and library primitives turn on these optional resistors.

By default, PULLDOWN resistors terminate all unused I/O and Input-only pins. Unused I/O and Input-only pins can alternatively be set to PULLUP or FLOAT. To change the unused I/O Pad setting, set the Bitstream Generator (BitGen) option *UnusedPin* to PULLUP, PULLDOWN, or FLOAT. The *UnusedPin* option is accessed through the Properties for Generate Programming File in ISE. See Bitstream Generator (BitGen) Options.

During configuration a Low logic level on the HSWAP pin activates pull-up resistors on all I/O and Input-only pins not actively used in the selected configuration mode.

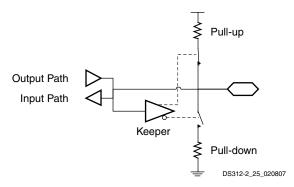

# **Keeper Circuit**

Each I/O has an optional keeper circuit (see Figure 12) that keeps bus lines from floating when not being actively driven. The KEEPER circuit retains the last logic level on a line after all drivers have been turned off. Apply the KEEPER attribute or use the KEEPER library primitive to use the KEEPER circuitry. Pull-up and pull-down resistors override the KEEPER settings.

Figure 12: Keeper Circuit

# **Slew Rate Control and Drive Strength**

Each IOB has a slew-rate control that sets the output switching edge-rate for LVCMOS and LVTTL outputs. The SLEW attribute controls the slew rate and can either be set to SLOW (default) or FAST.

Each LVCMOS and LVTTL output additionally supports up to six different drive current strengths as shown in Table 8. To adjust the drive strength for each output, the DRIVE attribute is set to the desired drive strength: 2, 4, 6, 8, 12, and 16. Unless otherwise specified in the FPGA application, the software default IOSTANDARD is LVCMOS25, SLOW slew rate, and 12 mA output drive.

Table 8: Programmable Output Drive Current

| IOSTANDARD | Output Drive Current (mA) |   |   |   |    |    |  |  |  |  |

|------------|---------------------------|---|---|---|----|----|--|--|--|--|

| IOSTANDARD | 2                         | 4 | 6 | 8 | 12 | 16 |  |  |  |  |

| LVTTL      | ~                         | ~ | ~ | ~ | ~  | ~  |  |  |  |  |

| LVCMOS33   | >                         | ~ | ~ | ~ | ~  | ~  |  |  |  |  |

| LVCMOS25   | >                         | ~ | ~ | ~ | ~  | -  |  |  |  |  |

| LVCMOS18   | >                         | ~ | ~ | ~ | -  | -  |  |  |  |  |

| LVCMOS15   | >                         | ~ | ~ | - | -  | -  |  |  |  |  |

| LVCMOS12   | >                         | - | - | - | -  | -  |  |  |  |  |

High output current drive strength and FAST output slew rates generally result in fastest I/O performance. However, these same settings generally also result in transmission line effects on the printed circuit board (PCB) for all but the shortest board traces. Each IOB has independent slew rate and drive strength controls. Use the slowest slew rate and lowest output drive current that meets the performance requirements for the end application.

Likewise, due to lead inductance, a given package supports a limited number of simultaneous switching outputs (SSOs) when using fast, high-drive outputs. Only use fast, high-drive outputs when required by the application.

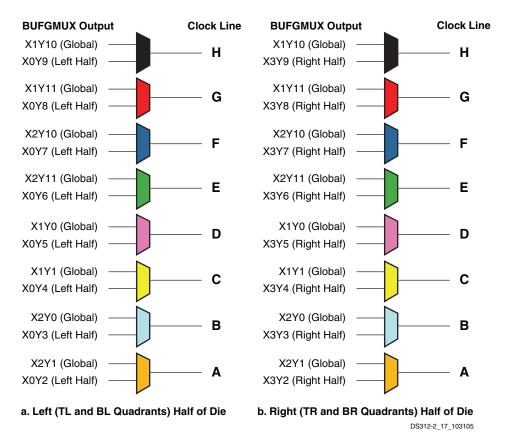

Figure 47: Clock Sources for the Eight Clock Lines within a Clock Quadrant

The outputs of the top or bottom BUFGMUX elements connect to two vertical spines, each comprising four vertical clock lines as shown in Figure 45. At the center of the die, these clock signals connect to the eight-line horizontal clock spine.

Outputs of the left and right BUFGMUX elements are routed onto the left or right horizontal spines, each comprising eight horizontal clock lines.

Each of the eight clock signals in a clock quadrant derives either from a global clock signal or a half clock signal. In other words, there are up to 24 total potential clock inputs to the FPGA, eight of which can connect to clocked elements in a single clock quadrant. Figure 47 shows how the clock lines in each quadrant are selected from associated BUFGMUX sources. For example, if quadrant clock 'A' in the bottom left (BL) quadrant originates from BUFGMUX\_X2Y1, then the clock signal from BUFGMUX\_X0Y2 is unavailable in the bottom left quadrant. However, the top left (TL) quadrant clock 'A' can still solely use the output from either BUFGMUX\_X2Y1 or BUFGMUX\_X0Y2 as the source.

To minimize the dynamic power dissipation of the clock network, the Xilinx development software automatically disables all clock segments not in use.

#### **Compatible Flash Families**

The Spartan-3E BPI configuration interface operates with a wide variety of x8 or x8/x16 parallel NOR Flash devices. Table 61 provides a few Flash memory families that operate with the Spartan-3E BPI interface. Consult the data sheet for the desired parallel NOR Flash to determine its suitability The basic timing requirements and waveforms are provided in Byte Peripheral Interface (BPI) Configuration Timing (Module 3).

Table 61: Compatible Parallel NOR Flash Families

| Flash Vendor    | Flash Memory Family   |  |  |  |

|-----------------|-----------------------|--|--|--|

| Numonyx         | M29W, J3D StrataFlash |  |  |  |

| Atmel           | AT29 / AT49           |  |  |  |

| <u>Spansion</u> | S29                   |  |  |  |

| Macronix        | MX29                  |  |  |  |

# **CCLK Frequency**

In BPI mode, the FPGA's internal oscillator generates the configuration clock frequency that controls all the interface timing. The FPGA starts configuration at its lowest frequency and increases its frequency for the remainder of the configuration process if so specified in the configuration bitstream. The maximum frequency is specified using the *ConfigRate* bitstream generator option.

Table 62: Maximum ConfigRate Settings for Parallel Flash PROMs (Commercial Temperature Range)

| Flash Read Access Time | Maximum <i>ConfigRate</i><br>Setting |

|------------------------|--------------------------------------|

| 250 ns                 | 3                                    |

| 115 ns                 | 6                                    |

| 45 ns                  | 12                                   |

Table 62 shows the maximum *ConfigRate* settings for various typical PROM read access times over the Commercial temperature operating range. See Byte Peripheral Interface (BPI) Configuration Timing (Module 3) and <u>UG332</u> for more detailed information. Despite using slower *ConfigRate* settings, BPI mode is equally fast as the other configuration modes. In BPI mode, data is accessed at the *ConfigRate* frequency and internally serialized with an 8X clock frequency.

## Using the BPI Interface after Configuration

After the FPGA successfully completes configuration, all pins connected to the parallel Flash PROM are available as user I/Os.

If not using the parallel Flash PROM after configuration, drive LDC0 High to disable the PROM's chip-select input. The remainder of the BPI pins then become available to the FPGA application, including all 24 address lines, the eight data lines, and the LDC2, LDC1, and HDC control pins.

Because all the interface pins are user I/Os after configuration, the FPGA application can continue to use the interface pins to communicate with the parallel Flash PROM. Parallel Flash PROMs are available in densities ranging from 1 Mbit up to 128 Mbits and beyond. However, a single Spartan-3E FPGA requires less than 6 Mbits for configuration. If desired, use a larger parallel Flash PROM to contain additional non-volatile application data, such as MicroBlaze processor code, or other user data, such as serial numbers and Ethernet MAC IDs. In such an example, the FPGA configures from parallel Flash PROM. Then using FPGA logic after configuration, a MicroBlaze processor embedded within the FPGA can either execute code directly from parallel Flash PROM or copy the code to external DDR SDRAM and execute from DDR SDRAM. Similarly, the FPGA application can store non-volatile application data within the parallel Flash PROM.

The FPGA configuration data is stored starting at either at location 0 or the top of memory (addresses all ones) or at both locations for MultiBoot mode. Store any additional data beginning in other available parallel Flash PROM sectors. Do not mix configuration data and user data in the same sector.

Similarly, the parallel Flash PROM interface can be expanded to additional parallel peripherals.

The address, data, and LDC1 (OE#) and HDC (WE#) control signals are common to all parallel peripherals. Connect the chip-select input on each additional peripheral to one of the FPGA user I/O pins. If HSWAP = 0 during configuration, the FPGA holds the chip-select line High via an internal pull-up resistor. If HSWAP = 1, connect the select line to +3.3V via an external 4.7 k $\Omega$  pull-up resistor to avoid spurious read or write operations. After configuration, drive the select line Low to select the desired peripheral. Refer to the individual peripheral data sheet for specific interface and communication protocol requirements.

The FPGA optionally supports a 16-bit peripheral interface by driving the LDC2 (BYTE#) control pin High after configuration. See Precautions Using x8/x16 Flash PROMs for additional information.

The FPGA provides up to 24 address lines during configuration, addressing up to 128 Mbits (16 Mbytes). If using a larger parallel PROM, connect the upper address lines to FPGA user I/O. During configuration, the upper address lines will be pulled High if HSWAP = 0. Otherwise, use external pull-up or pull-down resistors on these address lines to define their values during configuration.

# Precautions Using x8/x16 Flash PROMs

D Most low- to mid-density PROMs are byte-wide (x8) only. Many higher-density Flash PROMs support both byte-wide (x8) and halfword-wide (x16) data paths and include a mode input called BYTE# that switches between x8 or x16. During configuration, Spartan-3E FPGAs only

# Stepping 0 Limitations when Reprogramming via JTAG if FPGA Set for BPI Configuration

The FPGA can always be reprogrammed via the JTAG port, regardless of the mode pin (M[2:0]) settings. However, Stepping 0 devices have a minor limitation. If a Stepping 0 FPGA is set to configure in BPI mode and the FPGA is attached to a parallel memory containing a valid FPGA

configuration file, then subsequent reconfigurations using the JTAG port will fail. Potential workarounds include setting the mode pins for JTAG configuration (M[2:0] = <1:0:1>) or offsetting the initial memory location in Flash by 0x2000.

Stepping 1 devices fully support JTAG configuration even when the FPGA mode pins are set for BPI mode.

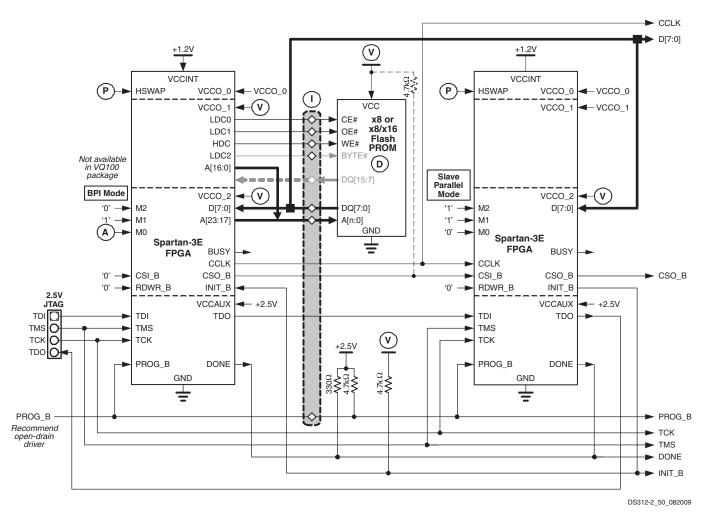

Figure 59: Daisy-Chaining from BPI Flash Mode

#### **In-System Programming Support**

In a production application, the parallel Flash PROM is usually preprogrammed before it is mounted on the printed circuit board. In-system programming support is available from third-party boundary-scan tool vendors and from some third-party PROM programmers using a socket adapter with attached wires. To gain access to the parallel Flash signals, drive the FPGA's PROG\_B input Low with an open-drain driver. This action places all FPGA I/O pins, including those attached to the parallel Flash, in high-impedance (Hi-Z). If the HSWAP input is Low, the I/Os have pull-up resistors to the V<sub>CCO</sub> input on their respective I/O bank. The external programming hardware then has direct access to the parallel Flash pins. The programming access points are

highlighted in the gray boxes in Figure 58 and Figure 59.

The FPGA itself can also be used as a parallel Flash PROM programmer during development and test phases. Initially, an FPGA-based programmer is downloaded into the FPGA via JTAG. Then the FPGA performs the Flash PROM programming algorithms and receives programming data from the host via the FPGA's JTAG interface. See the Embedded System Tools Reference Manual.

# Dynamically Loading Multiple Configuration Images Using MultiBoot Option

For additional information, refer to the "Reconfiguration and MultiBoot" chapter in UG332.

Table 69: Spartan-3E FPGA Bitstream Generator (BitGen) Options (Cont'd)

| Option Name                                                  | Pins/Function<br>Affected         | Values<br>( <u>default</u> ) | Description                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------|-----------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DriveDone                                                    | DONE pin                          | <u>No</u>                    | When configuration completes, the DONE pin stops driving Low and relies on an external 330 $\Omega$ pull-up resistor to V <sub>CCAUX</sub> for a valid logic High.                                                                                                                                    |

|                                                              |                                   | Yes                          | When configuration completes, the DONE pin actively drives High. When using this option, an external pull-up resistor is no longer required. Only one device in an FPGA daisy-chain should use this setting.                                                                                          |

| DonePipe                                                     | onePipe DONE pin                  |                              | The input path from DONE pin input back to the Startup sequencer is not pipelined.                                                                                                                                                                                                                    |

|                                                              |                                   | Yes                          | This option adds a pipeline register stage between the DONE pin input and the Startup sequencer. Used for high-speed daisy-chain configurations when DONE cannot rise in a single CCLK cycle. Releases GWE and GTS signals on the first rising edge of StartupClk after the DONE pin input goes High. |

| ProgPin                                                      | PROG_B pin                        | <u>Pullup</u>                | Internally connects a pull-up resistor or between PROG_B pin and V $_{CCAUX}$ . An external 4.7 k $\Omega$ pull-up resistor to V $_{CCAUX}$ is still recommended since the internal pull-up value may be weaker (see Table 78).                                                                       |

|                                                              |                                   | Pullnone                     | No internal pull-up resistor on PROG_B pin. An external 4.7 k $\Omega$ pull-up resistor to $V_{CCAUX}$ is required.                                                                                                                                                                                   |

| TckPin                                                       | JTAG TCK pin                      | <u>Pullup</u>                | Internally connects a pull-up resistor between JTAG TCK pin and V <sub>CCAUX</sub> .                                                                                                                                                                                                                  |

|                                                              |                                   | Pulldown                     | Internally connects a pull-down resistor between JTAG TCK pin and GND.                                                                                                                                                                                                                                |

|                                                              |                                   | Pullnone                     | No internal pull-up resistor on JTAG TCK pin.                                                                                                                                                                                                                                                         |

| TdiPin JTAG TDI pin                                          |                                   | <u>Pullup</u>                | Internally connects a pull-up resistor between JTAG TDI pin and V <sub>CCAUX</sub> .                                                                                                                                                                                                                  |

|                                                              |                                   | Pulldown                     | Internally connects a pull-down resistor between JTAG TDI pin and GND.                                                                                                                                                                                                                                |

|                                                              |                                   | Pullnone                     | No internal pull-up resistor on JTAG TDI pin.                                                                                                                                                                                                                                                         |

| TdoPin                                                       | Pin JTAG TDO pin                  |                              | Internally connects a pull-up resistor between JTAG TDO pin and V <sub>CCAUX</sub> .                                                                                                                                                                                                                  |

|                                                              |                                   | Pulldown                     | Internally connects a pull-down resistor between JTAG TDO pin and GND.                                                                                                                                                                                                                                |

|                                                              |                                   | Pullnone                     | No internal pull-up resistor on JTAG TDO pin.                                                                                                                                                                                                                                                         |

| TmsPin                                                       | JTAG TMS pin                      | <u>Pullup</u>                | Internally connects a pull-up resistor between JTAG TMS pin and V <sub>CCAUX</sub> .                                                                                                                                                                                                                  |

|                                                              |                                   | Pulldown                     | Internally connects a pull-down resistor between JTAG TMS pin and GND.                                                                                                                                                                                                                                |

|                                                              |                                   | Pullnone                     | No internal pull-up resistor on JTAG TMS pin.                                                                                                                                                                                                                                                         |

| UserID                                                       | JTAG User ID register             | User string                  | The 32-bit JTAG User ID register value is loaded during configuration. The default value is all ones, <code>0xffff_ffffffffffffffffffffffffffffffff</code>                                                                                                                                            |

| Security                                                     | JTAG,<br>SelectMAP,               | <u>None</u>                  | Readback and limited partial reconfiguration are available via the JTAG port or via the SelectMAP interface, if the <i>Persist</i> option is set to <i>Yes</i> .                                                                                                                                      |

|                                                              | Readback, Partial reconfiguration | Level1                       | Readback function is disabled. Limited partial reconfiguration is still available via the JTAG port or via the SelectMAP interface, if the <i>Persist</i> option is set to <i>Yes</i> .                                                                                                               |

|                                                              | J                                 | Level2                       | Readback function is disabled. Limited partial reconfiguration is disabled.                                                                                                                                                                                                                           |

| CRC                                                          | Configuration                     | Enable                       | <b>Default.</b> Enable CRC checking on the FPGA bitstream. If error detected, FPGA asserts INIT_B Low and DONE pin stays Low.                                                                                                                                                                         |

|                                                              |                                   | Disable                      | Turn off CRC checking.                                                                                                                                                                                                                                                                                |

| Persist                                                      | SelectMAP                         | <u>No</u>                    | All BPI and Slave mode configuration pins are available as user-I/O after configuration.                                                                                                                                                                                                              |

| interface pins,<br>BPI mode,<br>Slave mode,<br>Configuration |                                   | Yes                          | This option is required for Readback and partial reconfiguration using the SelectMAP interface. The SelectMAP interface pins (see Slave Parallel Mode) are reserved after configuration and are not available as user-I/O.                                                                            |

# Spartan-3 FPGA Family: DC and Switching Characteristics

DS312 (4.0) October 29, 2012

**Product Specification**

#### **DC Electrical Characteristics**

In this section, specifications may be designated as Advance, Preliminary, or Production. These terms are defined as follows:

<u>Advance</u>: Initial estimates are based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

<u>Preliminary</u>: Based on characterization. Further changes are not expected.

<u>Production</u>: These specifications are approved once the silicon has been characterized over numerous production lots. Parameter values are considered stable with no future changes expected.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the published parameter values apply to all Spartan®-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

# **Absolute Maximum Ratings**

Stresses beyond those listed under Table 73, Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to absolute maximum conditions for extended periods of time adversely affects device reliability.

| Table 73: A | <b>bsolute Maximum</b> | <b>Ratings</b> |

|-------------|------------------------|----------------|

|-------------|------------------------|----------------|

| Symbol                    | Description Conditions                   |                                                                  | Min                     | Max   | Units                                   |    |

|---------------------------|------------------------------------------|------------------------------------------------------------------|-------------------------|-------|-----------------------------------------|----|

| V <sub>CCINT</sub>        | Internal supply voltage                  |                                                                  |                         | -0.5  | 1.32                                    | V  |

| V <sub>CCAUX</sub>        | Auxiliary supply voltage                 | -0.5                                                             | 3.00                    | V     |                                         |    |

| V <sub>CCO</sub>          | Output driver supply voltage             | -0.5                                                             | 3.75                    | V     |                                         |    |

| $V_{REF}$                 | Input reference voltage                  | -0.5                                                             | $V_{CCO} + 0.5^{(1)}$   | V     |                                         |    |

| V <sub>IN</sub> (1,2,3,4) | Voltage applied to all User I/O pins and |                                                                  |                         | -0.95 | 4.4                                     | V  |

|                           | Dual-Purpose pins                        | high-impedance state                                             | Industrial              | -0.85 | 4.3                                     | V  |

|                           | Voltage applied to all Dedicated pins    |                                                                  | All temp. ranges        | -0.5  | V <sub>CCAUX</sub> + 0.5 <sup>(3)</sup> | V  |

| I <sub>IK</sub>           | Input clamp current per I/O pin          | $-0.5 \text{ V} < \text{V}_{\text{IN}} < (\text{V}_{\text{IN}})$ | <sub>CCO</sub> + 0.5 V) | -     | ±100                                    | mA |

| V <sub>ESD</sub>          | Electrostatic Discharge Voltage          | Human body mod                                                   | lel                     | _     | ±2000                                   | V  |

|                           |                                          | Charged device model                                             |                         | _     | ±500                                    | V  |

|                           |                                          | Machine model                                                    |                         |       | ±200                                    | V  |

| T <sub>J</sub>            | Junction temperature                     |                                                                  |                         |       | 125                                     | °C |

| T <sub>STG</sub>          | Storage temperature                      |                                                                  |                         | -65   | 150                                     | °C |

#### Notes:

- Each of the User I/O and Dual-Purpose pins is associated with one of the four banks' V<sub>CCO</sub> rails. Keeping V<sub>IN</sub> within 500 mV of the associated V<sub>CCO</sub> rails or ground rail ensures that the internal diode junctions do not turn on. Table 77 specifies the V<sub>CCO</sub> range used to evaluate the maximum V<sub>IN</sub> voltage.

- Input voltages outside the -0.5V to V<sub>CCO</sub> + 0.5V (or V<sub>CCAUX</sub> + 0.5V) voltage range are require the I<sub>IK</sub> input diode clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Prolonged exposure to such current may compromise device reliability. A sustained current of 10 mA will not compromise device reliability. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families for more details.

- 3. All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> rail do not turn on. Table 77 specifies the V<sub>CCAUX</sub> range used to evaluate the maximum V<sub>IN</sub> voltage. As long as the V<sub>IN</sub> max specification is met, oxide stress is not possible.

- 4. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 5. For soldering guidelines, see <u>UG112</u>: Device Packaging and Thermal Characteristics and <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Spartan-3 FPGA Family: DC and Switching Characteristics

# **Power Supply Specifications**

#### Table 74: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                      | Min | Max | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 0.8 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the V <sub>CCO</sub> Bank 2 supply | 0.4 | 1.0 | V     |

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 75: Supply Voltage Ramp Rate

| Symbol              | Description                                                      | Min | Max | Units |

|---------------------|------------------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid V <sub>CCINT</sub> supply level      | 0.2 | 50  | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid V <sub>CCAUX</sub> supply level      | 0.2 | 50  | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid V <sub>CCO</sub> Bank 2 supply level | 0.2 | 50  | ms    |

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (Platform Flash, SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. In Step 0 devices using the HSWAP internal pull-up, V<sub>CCINT</sub> must be applied before V<sub>CCAUX</sub>.

- 2. To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 76: Supply Voltage Levels Necessary for Preserving RAM Contents

| Symbol             | Description                                          | Min | Units |

|--------------------|------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain RAM data | 1.0 | V     |

| V <sub>DRAUX</sub> | V <sub>CCAUX</sub> level required to retain RAM data | 2.0 | V     |

#### Notes:

RAM contents include configuration data.

# **Switching Characteristics**

All Spartan-3E FPGAs ship in two speed grades: -4 and the higher performance -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production, as shown in Table 84. Each category is defined as follows:

<u>Advance</u>: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

<u>Preliminary</u>: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

<u>Production</u>: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

# **Software Version Requirements**

Production-quality systems must use FPGA designs compiled using a speed file designated as PRODUCTION status. FPGAs designs using a less mature speed file designation should only be used during system prototyping or pre-production qualification. FPGA designs with speed files designated as Advance or Preliminary should not be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the latest Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the published parameter values apply to all Spartan-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

#### Sign Up for Alerts on Xilinx.com

https://secure.xilinx.com/webreg/register.do ?group=myprofile&languageID=1 Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3E speed files (v1.27), part of the Xilinx Development Software, are the original source for many but not all of the values. The speed grade designations for these files are shown in Table 84. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

Table 84: Spartan-3E v1.27 Speed Grade Designations

| Device    | Advance | Preliminary | Production   |

|-----------|---------|-------------|--------------|

| XC3S100E  |         |             | -MIN, -4, -5 |

| XC3S250E  |         |             | -MIN, -4, -5 |

| XC3S500E  |         |             | -MIN, -4, -5 |

| XC3S1200E |         |             | -MIN, -4, -5 |

| XC3S1600E |         |             | -MIN, -4, -5 |

Table 85 provides the history of the Spartan-3E speed files since all devices reached Production status.

Table 85: Spartan-3E Speed File Version History

| Version | ISE<br>Release | Description                                                                        |

|---------|----------------|------------------------------------------------------------------------------------|

| 1.27    | 9.2.03i        | Added XA Automotive.                                                               |

| 1.26    | 8.2.02i        | Added -0/-MIN speed grade, which includes minimum values.                          |

| 1.25    | 8.2.01i        | Added XA Automotive devices to speed file. Improved model for left and right DCMs. |

| 1.23    | 8.2i           | Updated input setup/hold values based on default IFD_DELAY_VALUE settings.         |

| 1.21    | 8.1.03i        | All Spartan-3E FPGAs and all speed grades elevated to Production status.           |

## Table 92: Timing for the IOB Output Path

|                     | Description                                                                                                                             |                                                                    |        | Speed | Grade |       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|-------|-------|-------|

| Symbol              |                                                                                                                                         | Conditions                                                         | Device | -5    | -4    | Units |

|                     |                                                                                                                                         |                                                                    |        | Min   | Min   |       |

| Clock-to-Output     | Times                                                                                                                                   |                                                                    |        |       |       |       |

| T <sub>IOCKP</sub>  | When reading from the Output Flip-Flop (OFF), the time from the active transition at the OCLK input to data appearing at the Output pin | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,<br>Fast slew rate | All    | 2.18  | 2.50  | ns    |

| Propagation Tim     | es                                                                                                                                      |                                                                    |        |       |       | _     |

| T <sub>IOOP</sub>   | The time it takes for data to travel from the IOB's O input to the Output pin                                                           | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,                   | All    | 2.24  | 2.58  | ns    |

| T <sub>IOOLP</sub>  | The time it takes for data to travel from the O input through the OFF latch to the Output pin                                           | Fast slew rate                                                     |        | 2.32  | 2.67  | ns    |

| Set/Reset Times     |                                                                                                                                         |                                                                    |        |       |       | _     |

| T <sub>IOSRP</sub>  | Time from asserting the OFF's SR input to setting/resetting data at the Output pin                                                      | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,                   | All    | 3.27  | 3.76  | ns    |

| T <sub>IOGSRQ</sub> | Time from asserting the Global Set Reset (GSR) input on the STARTUP_SPARTAN3E primitive to setting/resetting data at the Output pin     | Fast slew rate                                                     |        | 8.40  | 9.65  | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

- 2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 94.

- 3. For minimum delays use the values reported by the Timing Analyzer.

# Table 99: CLB Distributed RAM Switching Characteristics

| Symbol                           | Description                                                                                                                       |      | -5   |      | -4   |       |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol                           | Description                                                                                                                       | Min  | Max  | Min  | Max  | Units |

| Clock-to-Output                  | Times                                                                                                                             |      |      |      |      |       |

| T <sub>SHCKO</sub>               | Time from the active edge at the CLK input to data appearing on the distributed RAM output                                        | -    | 2.05 | -    | 2.35 | ns    |

| Setup Times                      |                                                                                                                                   |      |      |      |      |       |

| T <sub>DS</sub>                  | Setup time of data at the BX or BY input before the active transition at the CLK input of the distributed RAM                     | 0.40 | -    | 0.46 | -    | ns    |

| T <sub>AS</sub>                  | Setup time of the F/G address inputs before the active transition at the CLK input of the distributed RAM                         | 0.46 | -    | 0.52 | -    | ns    |

| T <sub>WS</sub>                  | Setup time of the write enable input before the active transition at the CLK input of the distributed RAM                         | 0.34 | -    | 0.40 | -    | ns    |

| Hold Times                       |                                                                                                                                   |      | •    |      |      |       |

| T <sub>DH</sub>                  | Hold time of the BX, BY data inputs after the active transition at the CLK input of the distributed RAM                           | 0.13 | -    | 0.15 | -    | ns    |

| T <sub>AH,</sub> T <sub>WH</sub> | Hold time of the F/G address inputs or the write enable input after the active transition at the CLK input of the distributed RAM | 0    | -    | 0    | -    | ns    |

| Clock Pulse Wid                  | lth                                                                                                                               |      | •    |      |      |       |

| $T_{WPH}, T_{WPL}$               | Minimum High or Low pulse width at CLK input                                                                                      | 0.88 | -    | 1.01 | -    | ns    |

# Table 100: CLB Shift Register Switching Characteristics

| Symbol                              | Description                                                                                                  | -5   |      | -4   |      | Units |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol                              | Description                                                                                                  | Min  | Max  | Min  | Max  | Units |

| Clock-to-Output                     | Times                                                                                                        |      |      |      |      |       |

| T <sub>REG</sub>                    | Time from the active edge at the CLK input to data appearing on the shift register output                    | -    | 3.62 | -    | 4.16 | ns    |

| Setup Times                         |                                                                                                              |      | •    |      |      |       |

| T <sub>SRLDS</sub>                  | Setup time of data at the BX or BY input before the active transition at the CLK input of the shift register | 0.41 | -    | 0.46 | -    | ns    |

| Hold Times                          |                                                                                                              |      |      |      |      |       |

| T <sub>SRLDH</sub>                  | Hold time of the BX or BY data input after the active transition at the CLK input of the shift register      | 0.14 | -    | 0.16 | -    | ns    |

| Clock Pulse Wid                     | Clock Pulse Width                                                                                            |      |      |      |      |       |

| T <sub>WPH</sub> , T <sub>WPL</sub> | Minimum High or Low pulse width at CLK input                                                                 | 0.88 | -    | 1.01 | -    | ns    |

# **Clock Buffer/Multiplexer Switching Characteristics**

# Table 101: Clock Distribution Switching Characteristics

| Description                                                                                                 |                   | Maximum |       |     |

|-------------------------------------------------------------------------------------------------------------|-------------------|---------|-------|-----|

|                                                                                                             |                   | Speed   | Units |     |

|                                                                                                             |                   | -5      | -4    |     |

| Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output delay                                       | T <sub>GIO</sub>  | 1.46    | 1.46  | ns  |

| Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1 inputs. Same as BUFGCE enable CE-input | T <sub>GSI</sub>  | 0.55    | 0.63  | ns  |

| Frequency of signals distributed on global buffers (all sides)                                              | F <sub>BUFG</sub> | 333     | 311   | MHz |

Spartan-3 FPGA Family: DC and Switching Characteristics

# **Configuration Clock (CCLK) Characteristics**

Table 112: Master Mode CCLK Output Period by ConfigRate Option Setting

| Symbol              | Description                                | ConfigRate<br>Setting    | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------|--------------------------|----------------------|---------|---------|-------|

| T <sub>CCLK1</sub>  | CCLK clock period by<br>ConfigRate setting | 1<br>(power-on value and | Commercial           | 570     | 1,250   | ns    |

| 'CCLK1              | Comgnate setting                           | default value)           | Industrial           | 485     | 1,230   | ns    |

| т                   |                                            | 3                        | Commercial           | 285     | 625     | ns    |

| T <sub>CCLK3</sub>  |                                            | 3                        | Industrial           | 242     | 025     | ns    |

| Т                   |                                            | 6                        | Commercial           | 142     | 313     | ns    |

| T <sub>CCLK6</sub>  |                                            |                          | Industrial           | 121     | 313     | ns    |

| Т                   |                                            | 12                       | Commercial           | 71.2    | 157     | ns    |

| T <sub>CCLK12</sub> |                                            | 12                       | Industrial           | 60.6    | 137     | ns    |

| Т                   |                                            | 25                       | Commercial           | 35.5    | 78.2    | ns    |

| T <sub>CCLK25</sub> |                                            | 25                       | Industrial           | 30.3    | 70.2    | ns    |

| T                   |                                            | 50                       | Commercial           | 17.8    | 39.1    | ns    |

| T <sub>CCLK50</sub> |                                            | 30                       | Industrial           | 15.1    | 33.1    | ns    |

#### Notes:

Table 113: Master Mode CCLK Output Frequency by ConfigRate Option Setting

| Symbol              | Description                                                  | ConfigRate<br>Setting    | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------------------------|--------------------------|----------------------|---------|---------|-------|

| F <sub>CCLK1</sub>  | Equivalent CCLK clock frequency by <b>ConfigRate</b> setting | 1<br>(power-on value and | Commercial           | 0.8     | 1.8     | MHz   |

| CCLK1               | by <b>comignate</b> setting                                  | default value)           | Industrial           | 0.0     | 2.1     | MHz   |

| Е                   |                                                              | 3                        | Commercial           | 1.6     | 3.6     | MHz   |

| F <sub>CCLK3</sub>  |                                                              | 3                        | Industrial           | 1.0     | 4.2     | MHz   |

| <b>E</b>            |                                                              | 6                        | Commercial           | 3.2     | 7.1     | MHz   |

| F <sub>CCLK6</sub>  |                                                              | 0                        | Industrial           | 3.2     | 8.3     | MHz   |

| <b>E</b>            |                                                              | 12                       | Commercial           | 6.4     | 14.1    | MHz   |

| F <sub>CCLK12</sub> |                                                              | 12                       | Industrial           | 0.4     | 16.5    | MHz   |

| Е                   |                                                              | 25                       | Commercial           | 12.8    | 28.1    | MHz   |

| F <sub>CCLK25</sub> |                                                              | 25                       | Industrial           | 12.0    | 33.0    | MHz   |

| E                   |                                                              | 50                       | Commercial           | 25.6    | 56.2    | MHz   |

| F <sub>CCLK50</sub> |                                                              | 50                       | Industrial           | 20.0    | 66.0    | MHz   |

#### Table 114: Master Mode CCLK Output Minimum Low and High Time

| Symbol Description  |                          | ConfigRate Setting |     |     |    |      |      | Units |       |

|---------------------|--------------------------|--------------------|-----|-----|----|------|------|-------|-------|

| Symbol              | Symbol Description       |                    | 1   | 3   | 6  | 12   | 25   | 50    | Onits |

| T <sub>MCCL</sub> , | Master mode CCLK minimum | Commercial         | 276 | 138 | 69 | 34.5 | 17.1 | 8.5   | ns    |

| IMCCH               | Low and High time        | Industrial         | 235 | 117 | 58 | 29.3 | 14.5 | 7.3   | ns    |

## Table 115: Slave Mode CCLK Input Low and High Time

| Symbol                                  | Description            | Min | Max | Units |

|-----------------------------------------|------------------------|-----|-----|-------|

| T <sub>SCCL,</sub><br>T <sub>SCCH</sub> | CCLK Low and High time | 5   | ∞   | ns    |

Set the ConfigRate option value when generating a configuration bitstream. See Bitstream Generator (BitGen) Options in Module 2.

# CP132: 132-ball Chip-scale Package

The XC3S100E, XC3S250E and the XC3S500E FPGAs are available in the 132-ball chip-scale package, CP132. The devices share a common footprint for this package as shown in Table 133 and Figure 81.

Table 133 lists all the CP132 package pins. They are sorted by bank number and then by pin name. Pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

Physically, the D14 and K2 balls on the XC3S100E and XC3S250E FPGAs are not connected but should be connected to VCCINT to maintain density migration compatibility.

Similarly, the A4, C1, and P10 balls on the XC3S100E FPGA are not connected but should be connected to GND to maintain density migration compatibility.

The XC3S100E FPGA has four fewer BPI address pins, A[19:0], whereas the XC3S250E and XC3S500E support A[23:0].

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx web site at:

http://www.xilinx.com/support/documentation/data\_sheets/s3e\_pin.zip

#### **Pinout Table**

Table 133: CP132 Package Pinout

| Bank | XC3S100E<br>Pin Name | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                  |

|------|----------------------|----------------------------------|------------|---------------------------------------|

| 0    | IO_L01N_0            | IO_L01N_0                        | C12        | I/O                                   |

| 0    | IO_L01P_0            | IO_L01P_0                        | A13        | I/O                                   |

| 0    | N.C. (♠)             | IO_L02N_0                        | A12        | <b>100E:</b> N.C. <b>Others:</b> I/O  |

| 0    | N.C. (♠)             | IO_L02P_0                        | B12        | <b>100E:</b> N.C. <b>Others:</b> I/O  |

| 0    | N.C. (♠)             | IO_L03N_0/VREF_0                 | B11        | 100E: N.C.<br>Others: VREF (I/O)      |

| 0    | IP                   | IO_L03P_0                        | C11        | <b>100E:</b> INPUT <b>Others:</b> I/O |

| 0    | IO_L04N_0/GCLK5      | IO_L04N_0/GCLK5                  | C9         | GCLK                                  |

| 0    | IO_L04P_0/GCLK4      | IO_L04P_0/GCLK4                  | A10        | GCLK                                  |

| 0    | IO_L05N_0/GCLK7      | IO_L05N_0/GCLK7                  | A9         | GCLK                                  |

| 0    | IO_L05P_0/GCLK6      | IO_L05P_0/GCLK6                  | B9         | GCLK                                  |

| 0    | IO_L07N_0/GCLK11     | IO_L07N_0/GCLK11                 | B7         | GCLK                                  |

| 0    | IO_L07P_0/GCLK10     | IO_L07P_0/GCLK10                 | A7         | GCLK                                  |

| 0    | IO_L08N_0/VREF_0     | IO_L08N_0/VREF_0                 | C6         | VREF                                  |

| 0    | IO_L08P_0            | IO_L08P_0                        | B6         | I/O                                   |

| 0    | IO_L09N_0            | IO_L09N_0                        | C5         | I/O                                   |

| 0    | IO_L09P_0            | IO_L09P_0                        | B5         | I/O                                   |

| 0    | N.C. (♠)             | IO_L10N_0                        | C4         | <b>100E:</b> N.C. <b>Others:</b> I/O  |

| 0    | IP                   | IO_L10P_0                        | B4         | <b>100E:</b> INPUT <b>Others:</b> I/O |

| 0    | IO_L11N_0/HSWAP      | IO_L11N_0/HSWAP                  | B3         | DUAL                                  |

| 0    | IO_L11P_0            | IO_L11P_0                        | A3         | I/O                                   |

| 0    | IP_L06N_0/GCLK9      | IP_L06N_0/GCLK9                  | C8         | GCLK                                  |

| 0    | IP_L06P_0/GCLK8      | IP_L06P_0/GCLK8                  | B8         | GCLK                                  |

| 0    | VCCO_0               | VCCO_0                           | A6         | VCCO                                  |

Table 137: TQ144 Package Pinout (Cont'd)

| Bank | XC3S100E Pin Name      | XC3S250E Pin Name      | TQ144 Pin | Туре                                   |

|------|------------------------|------------------------|-----------|----------------------------------------|

| 2    | IP                     | IP                     | P38       | INPUT                                  |

| 2    | IP                     | IP                     | P41       | INPUT                                  |

| 2    | IP                     | IP                     | P69       | INPUT                                  |

| 2    | IP_L03N_2/VREF_2       | IP_L03N_2/VREF_2       | P48       | VREF                                   |

| 2    | IP_L03P_2              | IP_L03P_2              | P47       | INPUT                                  |

| 2    | IP_L06N_2/M2/GCLK1     | IP_L06N_2/M2/GCLK1     | P57       | DUAL/GCLK                              |

| 2    | IP_L06P_2/RDWR_B/GCLK0 | IP_L06P_2/RDWR_B/GCLK0 | P56       | DUAL/GCLK                              |

| 2    | VCCO_2                 | VCCO_2                 | P42       | VCCO                                   |

| 2    | VCCO_2                 | VCCO_2                 | P49       | VCCO                                   |

| 2    | VCCO_2                 | VCCO_2                 | P64       | VCCO                                   |

| 3    | IP/VREF_3              | IO/VREF_3              | P31       | 100E: VREF(INPUT)<br>250E: VREF(I/O)   |

| 3    | IO_L01N_3              | IO_L01N_3              | P3        | I/O                                    |

| 3    | IO_L01P_3              | IO_L01P_3              | P2        | I/O                                    |

| 3    | IO_L02N_3/VREF_3       | IO_L02N_3/VREF_3       | P5        | VREF                                   |

| 3    | IO_L02P_3              | IO_L02P_3              | P4        | I/O                                    |

| 3    | IO_L03N_3              | IO_L03N_3              | P8        | I/O                                    |

| 3    | IO_L03P_3              | IO_L03P_3              | P7        | I/O                                    |

| 3    | IO_L04N_3/LHCLK1       | IO L04N 3/LHCLK1       | P15       | LHCLK                                  |

| 3    | IO_L04P_3/LHCLK0       | IO_L04P_3/LHCLK0       | P14       | LHCLK                                  |

| 3    | IO_L05N_3/LHCLK3/IRDY2 | IO_L05N_3/LHCLK3       | P17       | LHCLK                                  |

| 3    | IO_L05P_3/LHCLK2       | IO_L05P_3/LHCLK2       | P16       | LHCLK                                  |

| 3    | IO_L06N_3/LHCLK5       | IO_L06N_3/LHCLK5       | P21       | LHCLK                                  |

| 3    | IO_L06P_3/LHCLK4/TRDY2 | IO_L06P_3/LHCLK4       | P20       | LHCLK                                  |

| 3    | IO_L07N_3/LHCLK7       | IO_L07N_3/LHCLK7       | P23       | LHCLK                                  |

| 3    | IO_L07P_3/LHCLK6       | IO_L07P_3/LHCLK6       | P22       | LHCLK                                  |

| 3    | IO_L08N_3              | IO_L08N_3              | P26       | I/O                                    |

| 3    | IO_L08P_3              | IO_L08P_3              | P25       | I/O                                    |

| 3    | IO_L09N_3              | IO_L09N_3              | P33       | I/O                                    |

| 3    | IO_L09P_3              | IO_L09P_3              | P32       | I/O                                    |

| 3    | IO_L10N_3              | IO_L10N_3              | P35       | I/O                                    |

| 3    | IO_L10P_3              | IO_L10P_3              | P34       | I/O                                    |

| 3    | IP                     | IP                     | P6        | INPUT                                  |

| 3    | Ю                      | IP                     | P10       | <b>100E:</b> I/O<br><b>250E:</b> INPUT |

| 3    | IP                     | IP                     | P18       | INPUT                                  |

| 3    | IP                     | IP                     | P24       | INPUT                                  |

| 3    | Ю                      | IP                     | P29       | 100E: I/O<br>250E: INPUT               |

| 3    | IP                     | IP                     | P36       | INPUT                                  |

| 3    | IP/VREF_3              | IP/VREF_3              | P12       | VREF                                   |

| 3    | VCCO_3                 | VCCO_3                 | P13       | VCCO                                   |

| 3    | VCCO_3                 | VCCO_3                 | P28       | VCCO                                   |

| GND  | GND                    | GND                    | P11       | GND                                    |

| GND  | GND                    | GND                    | P19       | GND                                    |

Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| 3      | IO_L14P_3                        | P41          | I/O    |

| 3      | IO_L15N_3                        | P48          | I/O    |

| 3      | IO_L15P_3                        | P47          | I/O    |

| 3      | IO_L16N_3                        | P50          | I/O    |

| 3      | IO_L16P_3                        | P49          | I/O    |

| 3      | IP                               | P6           | INPUT  |

| 3      | IP                               | P14          | INPUT  |

| 3      | IP                               | P26          | INPUT  |

| 3      | IP                               | P32          | INPUT  |

| 3      | IP                               | P43          | INPUT  |

| 3      | IP                               | P51          | INPUT  |

| 3      | IP/VREF_3                        | P20          | VREF   |

| 3      | VCCO_3                           | P21          | VCCO   |

| 3      | VCCO_3                           | P38          | VCCO   |

| 3      | VCCO_3                           | P46          | VCCO   |

| GND    | GND                              | P10          | GND    |

| GND    | GND                              | P17          | GND    |

| GND    | GND                              | P27          | GND    |

| GND    | GND                              | P37          | GND    |

| GND    | GND                              | P52          | GND    |

| GND    | GND                              | P53          | GND    |

| GND    | GND                              | P70          | GND    |

| GND    | GND                              | P79          | GND    |

| GND    | GND                              | P85          | GND    |

| GND    | GND                              | P95          | GND    |

| GND    | GND                              | P105         | GND    |

| GND    | GND                              | P121         | GND    |

| GND    | GND                              | P131         | GND    |

| GND    | GND                              | P141         | GND    |

| GND    | GND                              | P156         | GND    |

| GND    | GND                              | P173         | GND    |

| GND    | GND                              | P182         | GND    |

| GND    | GND                              | P188         | GND    |

| GND    | GND                              | P198         | GND    |

| GND    | GND                              | P208         | GND    |

| VCCAUX | DONE                             | P104         | CONFIG |

| VCCAUX | PROG_B                           | P1           | CONFIG |

| VCCAUX | TCK                              | P158         | JTAG   |

| VCCAUX | TDI                              | P207         | JTAG   |

| VCCAUX | TDO                              | P157         | JTAG   |

| VCCAUX | TMS                              | P155         | JTAG   |

| VCCAUX | VCCAUX                           | P7           | VCCAUX |

| VCCAUX | VCCAUX                           | P44          | VCCAUX |

Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| VCCAUX | VCCAUX                           | P66          | VCCAUX |

| VCCAUX | VCCAUX                           | P92          | VCCAUX |

| VCCAUX | VCCAUX                           | P111         | VCCAUX |

| VCCAUX | VCCAUX                           | P149         | VCCAUX |

| VCCAUX | VCCAUX                           | P166         | VCCAUX |

| VCCAUX | VCCAUX                           | P195         | VCCAUX |

| VCCINT | VCCINT                           | P13          | VCCINT |

| VCCINT | VCCINT                           | P67          | VCCINT |

| VCCINT | VCCINT                           | P117         | VCCINT |

| VCCINT | VCCINT                           | P170         | VCCINT |

Table 148: FG320 Package Pinout (Cont'd)

| Bank | XC3S500E Pin Name | XC3S1200E Pin Name | XC3S1600E Pin Name | FG320<br>Ball | Туре                                      |

|------|-------------------|--------------------|--------------------|---------------|-------------------------------------------|

| 1    | IO_L17N_1         | IO_L17N_1          | IO_L17N_1          | H15           | I/O                                       |

| 1    | IO_L17P_1         | IO_L17P_1          | IO_L17P_1          | H14           | I/O                                       |

| 1    | IO_L18N_1         | IO_L18N_1          | IO_L18N_1          | G16           | I/O                                       |

| 1    | IO_L18P_1         | IO_L18P_1          | IO_L18P_1          | G15           | I/O                                       |

| 1    | IO_L19N_1         | IO_L19N_1          | IO_L19N_1          | F17           | I/O                                       |

| 1    | IO_L19P_1         | IO_L19P_1          | IO_L19P_1          | F18           | I/O                                       |

| 1    | IO_L20N_1         | IO_L20N_1          | IO_L20N_1          | G13           | I/O                                       |