## AMD Xilinx - XC3S500E-4CPG132C Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 1164                                                          |

| Number of Logic Elements/Cells | 10476                                                         |

| Total RAM Bits                 | 368640                                                        |

| Number of I/O                  | 92                                                            |

| Number of Gates                | 500000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 132-TFBGA, CSPBGA                                             |

| Supplier Device Package        | 132-CSPBGA (8x8)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s500e-4cpg132c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Xilinx Alerts**

# Spartan-3 FPGA Family: Functional Description

Create a Xilinx user account and sign up to receive

the associated user guides are updated.

https://secure.xilinx.com/webreg/register.do

Spartan-3E FPGA Starter Kit

various design examples and the user guide.

http://www.xilinx.com/s3estarter

Sign Up for Alerts on Xilinx.com

?group=myprofile&languageID=1

automatic e-mail notification whenever this data sheet or

For specific hardware examples, please see the Spartan-3E

UG230: Spartan-3E FPGA Starter Kit User Guide

FPGA Starter Kit board web page, which has links to

Spartan-3E FPGA Starter Kit Board page

DS312 (4.0) October 29, 2012

### **Product Specification**

## **Design Documentation Available**

The functionality of the Spartan®-3E FPGA family is now described and updated in the following documents. The topics covered in each guide are listed below.

- <u>UG331</u>: Spartan-3 Generation FPGA User Guide

- Clocking Resources

- Digital Clock Managers (DCMs)

- Block RAM

- Configurable Logic Blocks (CLBs)

- Distributed RAM

- SRL16 Shift Registers

- Carry and Arithmetic Logic

- I/O Resources

- Embedded Multiplier Blocks

- Programmable Interconnect

- ISE® Design Tools

- IP Cores

- Embedded Processing and Control Solutions

- Pin Types and Package Overview

- Package Drawings

- Powering FPGAs

- Power Management

- UG332: Spartan-3 Generation Configuration User Guide

- Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

- Detailed Descriptions by Mode

- Master Serial Mode using Xilinx® Platform Flash PROM

- Master SPI Mode using Commodity SPI Serial Flash PROM

- Master BPI Mode using Commodity Parallel NOR Flash PROM

- Slave Parallel (SelectMAP) using a Processor

- Slave Serial using a Processor

- JTAG Mode

- ISE iMPACT Programming Examples

- MultiBoot Reconfiguration

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

## **Double-Data-Rate Transmission**

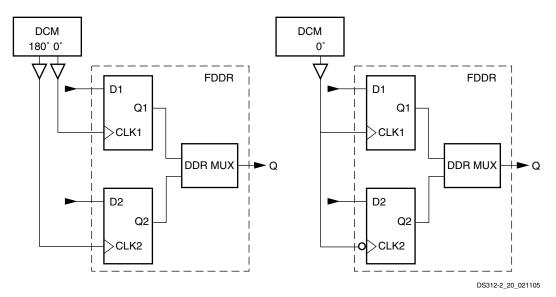

Double-Data-Rate (DDR) transmission describes the technique of synchronizing signals to both the rising and falling edges of the clock signal. Spartan-3E devices use register pairs in all three IOB paths to perform DDR operations.

The pair of storage elements on the IOB's Output path (OFF1 and OFF2), used as registers, combine with a special multiplexer to form a DDR D-type flip-flop (ODDR2). This primitive permits DDR transmission where output data bits are synchronized to both the rising and falling edges of a clock. DDR operation requires two clock signals (usually 50% duty cycle), one the inverted form of the other. These signals trigger the two registers in alternating fashion, as shown in Figure 7. The Digital Clock Manager (DCM) generates the two clock signals by mirroring an incoming signal, and then shifting it 180 degrees. This approach ensures minimal skew between the two signals. Alternatively, the inverter inside the IOB can be used to invert the clock signal, thus only using one clock line and both rising and falling edges of that clock line as the two clocks for the DDR flip-flops.

The storage-element pair on the Three-State path (TFF1 and TFF2) also can be combined with a local multiplexer to form a DDR primitive. This permits synchronizing the output enable to both the rising and falling edges of a clock. This DDR operation is realized in the same way as for the output path.

The storage-element pair on the input path (IFF1 and IFF2) allows an I/O to receive a DDR signal. An incoming DDR clock signal triggers one register, and the inverted clock signal triggers the other register. The registers take turns capturing bits of the incoming DDR data signal. The primitive to allow this functionality is called IDDR2.

Aside from high bandwidth data transfers, DDR outputs also can be used to reproduce, or *mirror*, a clock signal on the output. This approach is used to transmit clock and data signals together (source synchronously). A similar approach is used to reproduce a clock signal at multiple outputs. The advantage for both approaches is that skew across the outputs is minimal.

Figure 7: Two Methods for Clocking the DDR Register

## **Register Cascade Feature**

In the Spartan-3E family, one of the IOBs in a differential pair can cascade its input storage elements with those in the other IOB as part of a differential pair. This is intended to make DDR operation at high speed much simpler to implement. The new DDR connections that are available are shown in Figure 5 (dashed lines), and are only available for routing between IOBs and are not accessible to the FPGA fabric. Note that this feature is only available when using the differential I/O standards LVDS, RSDS, and MINI\_LVDS.

## IDDR2

As a DDR input pair, the master IOB registers incoming data on the rising edge of ICLK1 (= D1) and the rising edge of ICLK2 (= D2), which is typically the same as the falling edge of ICLK1. This data is then transferred into the FPGA fabric. At some point, both signals must be brought into the same clock domain, typically ICLK1. This can be difficult at high frequencies because the available time is only one half of a clock cycle assuming a 50% duty cycle. See Figure 8 for a graphical illustration of this function.

# Supply Voltages for the IOBs

The IOBs are powered by three supplies:

- 1. The  $V_{CCO}$  supplies, one for each of the FPGA's I/O banks, power the output drivers. The voltage on the  $V_{CCO}$  pins determines the voltage swing of the output signal.

- 2.  $V_{CCINT}$  is the main power supply for the FPGA's internal logic.

- V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also applies to input-only pins and dual-purpose I/O pins that are not actively involved in the currently-selected configuration mode.

All I/O pins have ESD clamp diodes to their respective V<sub>CCO</sub> supply and from GND, as shown in Figure 5. The V<sub>CCINT</sub> (1.2V), V<sub>CCAUX</sub> (2.5V), and V<sub>CCO</sub> supplies can be applied in any order. Before the FPGA can start its configuration process, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> must have reached their respective minimum recommended operating levels indicated in Table 74. At this time, all output drivers are in a high-impedance state. V<sub>CCO</sub> Bank 2, V<sub>CCINT</sub>, and V<sub>CCAUX</sub> serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP input enables pull-up resistors on user-I/O and input-only pins from power-on throughout configuration. A High level on HSWAP disables the pull-up resistors, allowing the I/Os to float. HSWAP contains an internal pull-up resistor and defaults to High if left floating. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a default Low state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of configuration, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. Configuration data is then loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP input) throughout configuration.

At the end of configuration, the GSR net is released, placing the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective SR inputs.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the

beginning of design operation in the User mode. After the GTS net is released, all user I/Os go active while all unused I/Os are pulled down (PULLDOWN). The designer can control how the unused I/Os are terminated after GTS is released by setting the Bitstream Generator (BitGen) option UnusedPin to PULLUP, PULLDOWN, or FLOAT.

One clock cycle later (default), the Global Write Enable (GWE) net is released allowing the RAM and registers to change states. Once in User mode, any pull-up resistors enabled by HSWAP revert to the user settings and HSWAP is available as a general-purpose I/O. For more information on PULLUP and PULLDOWN, see Pull-Up and Pull-Down Resistors.

# Behavior of Unused I/O Pins After Configuration

By default, the Xilinx ISE development software automatically configures all unused I/O pins as input pins with individual internal pull-down resistors to GND.

This default behavior is controlled by the **UnusedPin** bitstream generator (BitGen) option, as described in Table 69.

# JTAG Boundary-Scan Capability

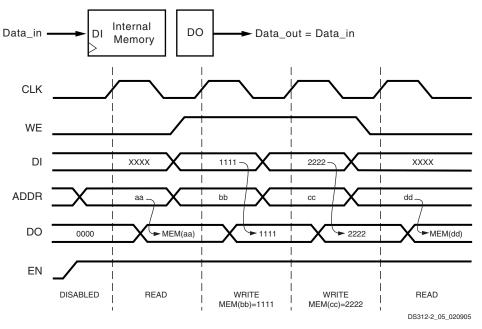

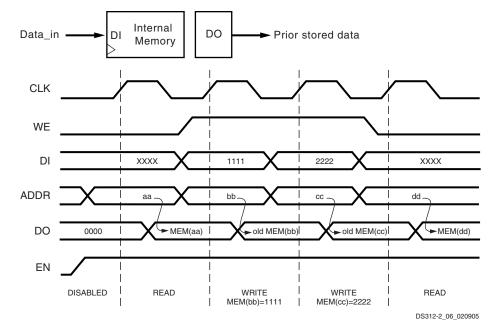

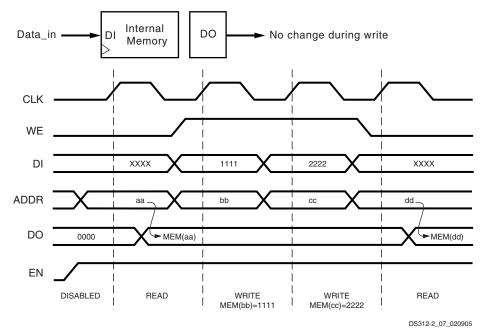

All Spartan-3E IOBs support boundary-scan testing compatible with IEEE 1149.1/1532 standards. During boundary-scan operations such as EXTEST and HIGHZ the pull-down resistor is active. See JTAG Mode for more information on programming via JTAG. There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a output latch to the DO outputs. The timing for basic data access is shown in the

XILINX.

portions of Figure 33, Figure 34, and Figure 35 during which WE is Low.

Data also can be accessed on the DO outputs when asserting the WE input based on the value of the WRITE\_MODE attribute as described in Table 26.

### Table 26: WRITE\_MODE Effect on Data Output Latches During Write Operations

| Write Mode                      | Effect on Same Port                                                                                                              | Effect on Opposite Port<br>(dual-port only with same address)   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| WRITE_FIRST<br>Read After Write | Data on DI and DIP inputs is written into specified RAM location and simultaneously appears on DO and DOP outputs.               | Invalidates data on DO and DOP outputs.                         |

| READ_FIRST<br>Read Before Write | Data from specified RAM location appears on DO and DOP outputs.<br>Data on DI and DIP inputs is written into specified location. | Data from specified RAM location appears on DO and DOP outputs. |

| NO_CHANGE<br>No Read on Write   | Data on DO and DOP outputs remains unchanged.<br>Data on DI and DIP inputs is written into specified<br>location.                | Invalidates data on DO and DOP outputs.                         |

Setting the WRITE\_MODE attribute to a value of WRITE\_FIRST, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE\_FIRST timing is shown in the portion of Figure 33 during which WE is High.

Setting the WRITE\_MODE attribute to a value of READ\_FIRST, data already stored in the addressed location passes to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ\_FIRST timing is shown in the portion of Figure 34 during which WE is High.

Figure 34: Waveforms of Block RAM Data Operations with READ\_FIRST Selected

Setting the WRITE\_MODE attribute to a value of NO\_CHANGE, puts the DO outputs in a latched state when asserting WE. Under this condition, the DO outputs retain the data driven just before WE is asserted. NO\_CHANGE timing is shown in the portion of Figure 35 during which WE is High.

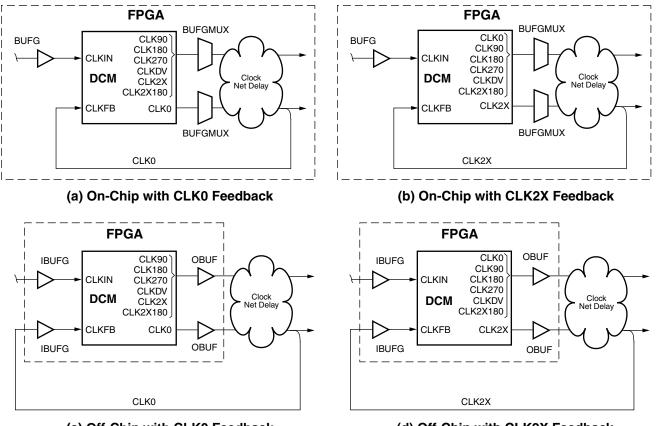

## **DLL Clock Output and Feedback Connections**

As many as four of the nine DCM clock outputs can simultaneously drive four of the BUFGMUX buffers on the same die edge. All DCM clock outputs can simultaneously drive general routing resources, including interconnect leading to OBUF buffers.

The feedback loop is essential for DLL operation. Either the CLK0 or CLK2X outputs feed back to the CLKFB input via a BUFGMUX global buffer to eliminate the clock distribution delay. The specific BUFGMUX buffer used to feed back the CLK0 or CLK2X signal is ideally one of the BUFGMUX buffers associated with a specific DCM, as shown in Table 30, Table 31, and Table 32.

The feedback path also phase-aligns the other seven DLL outputs: CLK0, CLK90, CLK180, CLK270, CLKDV, CLK2X, or CLK2X180. The CLK\_FEEDBACK attribute value must agree with the physical feedback connection. Use "1X" for CLK0 feedback and "2X" for CLK2X feedback. If the DFS unit is used stand-alone, without the DLL, then no feedback is required and set the CLK\_FEEDBACK attribute to "NONE".

Two basic cases determine how to connect the DLL clock outputs and feedback connections: on-chip synchronization and off-chip synchronization, which are illustrated in Figure 42a through Figure 42d.

In the on-chip synchronization case in Figure 42a and Figure 42b, it is possible to connect any of the DLL's seven output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. As shown in Figure 42a, the feedback loop is created by routing CLK0 (or CLK2X) in Figure 42b to a global clock net, which in turn drives the CLKFB input.

In the off-chip synchronization case in Figure 42c and Figure 42d, CLK0 (or CLK2X) plus any of the DLL's other output clock signals exit the FPGA using output buffers (OBUF) to drive an external clock network plus registers on the board. As shown in Figure 42c, the feedback loop is formed by feeding CLK0 (or CLK2X) in Figure 42d back into the FPGA, then to the DCM's CLKFB input via a Global Buffer Input, specified in Table 30.

(d) Off-Chip with CLK2X Feedback

DS099-2\_09\_082104

Figure 42: Input Clock, Output Clock, and Feedback Connections for the DLL

P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins during configuration or High to disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is

available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

The FPGA's DOUT pin is used in daisy-chain applications, described later. In a single-FPGA application, the FPGA's DOUT pin is not used but is actively driving during the configuration process.

| Pin Name   | FPGA<br>Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | During Configuration                                                                                                                                                                                                                                                                                                              | After Configuration                                                                                       |

|------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| HSWAP<br>P | Input                              | <b>User I/O Pull-Up Control</b> . When Low during configuration, enables pull-up resistors in all I/O pins to respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration<br>1: No pull-ups                                                                                                                                                                                                                                                                   | Drive at valid logic level throughout configuration.                                                                                                                                                                                                                                                                              | User I/O                                                                                                  |

| M[2:0]     | Input                              | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                                      | ct. Selects the FPGA configuration     M2 = 0, M1 = 0, M0 = 0. Sampled       Design Considerations for the     when INIT_B goes High.                                                                                                                                                                                             |                                                                                                           |

| DIN        | Input                              | Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receives serial data from PROM's D0 output.                                                                                                                                                                                                                                                                                       | User I/O                                                                                                  |

| CCLK       | Output                             | <b>Configuration Clock</b> . Generated by FPGA internal oscillator. Frequency controlled by <i>ConfigRate</i> bitstream generator option. If CCLK PCB trace is long or has multiple connections, terminate this output to maintain signal integrity. See CCLK Design Considerations.                                                                                                                                                                                              | Drives PROM's CLK clock input.                                                                                                                                                                                                                                                                                                    | User I/O                                                                                                  |

| DOUT       | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Actively drives. Not used in<br>single-FPGA designs. In a<br>daisy-chain configuration, this pin<br>connects to DIN input of the next<br>FPGA in the chain.                                                                                                                                                                       | User I/O                                                                                                  |

| INIT_B     | Open-drain<br>bidirectional<br>I/O | <b>Initialization Indicator</b> . Active Low. Goes<br>Low at start of configuration during<br>Initialization memory clearing process.<br>Released at end of memory clearing, when<br>mode select pins are sampled. Requires<br>external 4.7 k $\Omega$ pull-up resistor to VCCO_2.                                                                                                                                                                                                | Connects to PROM's OE/RESET<br>input. FPGA clears PROM's<br>address counter at start of<br>configuration, enables outputs<br>during configuration. PROM also<br>holds FPGA in Initialization state<br>until PROM reaches Power-On<br>Reset (POR) state. If CRC error<br>detected during configuration,<br>FPGA drives INIT_B Low. | User I/O. If unused in<br>the application, drive<br>INIT_B High.                                          |

| DONE       | Open-drain<br>bidirectional<br>I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                     | Connects to PROM's chip-enable<br>(CE) input. Enables PROM during<br>configuration. Disables PROM<br>after configuration.                                                                                                                                                                                                         | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully<br>configured. |

| PROG_B     | Input                              | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High. Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High during configuration<br>to allow configuration to start.<br>Connects to PROM's CF pin,<br>allowing JTAG PROM<br>programming algorithm to<br>reprogram the FPGA.                                                                                                                                                      | Drive PROG_B Low<br>and release to<br>reprogram FPGA.                                                     |

## Table 50: Serial Master Mode Connections

FPGA passes configuration data via its DOUT output pin to the next FPGA on the falling CCLK edge.

## Table 66: Slave Serial Mode Connections

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| HSWAP    | Input                           | User I/O Pull-Up Control. When<br>Low during configuration, enables<br>pull-up resistors in all I/O pins to<br>respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-up during configuration<br>1: No pull-ups                                                                                                                                                                                                                                                                                                  | Drive at valid logic level<br>throughout configuration.                                                   | User I/O                                                                                               |

| M[2:0]   | Input                           | Mode Select. Selects the FPGA<br>configuration mode. See Design<br>Considerations for the HSWAP,<br>M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                                                                    | M2 = 1, M1 = 1, M0 = 1 Sampled<br>when INIT_B goes High.                                                  | User I/O                                                                                               |

| DIN      | Input                           | Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Serial data provided by host.<br>FPGA captures data on rising<br>CCLK edge.                               | User I/O                                                                                               |

| CCLK     | Input                           | <b>Configuration Clock</b> . If CCLK<br>PCB trace is long or has multiple<br>connections, terminate this output<br>to maintain signal integrity. See<br>CCLK Design Considerations.                                                                                                                                                                                                                                                                                                                              | External clock.                                                                                           | User I/O                                                                                               |

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active<br>Low. Goes Low at start of<br>configuration during Initialization<br>memory clearing process.<br>Released at end of memory<br>clearing, when mode select pins<br>are sampled. In daisy-chain<br>applications, this signal requires<br>an external 4.7 kΩ pull-up resistor<br>to VCCO_2.                                                                                                                                                                               | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the application, drive INIT_B<br>High.                                          |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                    | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low.<br>When asserted Low for 500 ns or<br>longer, forces the FPGA to restart<br>its configuration process by<br>clearing configuration memory and<br>resetting the DONE and INIT_B<br>pins once PROG_B returns High.<br>Recommend external 4.7 kΩ<br>pull-up resistor to 2.5V. Internal<br>pull-up value may be weaker (see<br>Table 78). If driving externally with<br>a 3.3V output, use an open-drain<br>or open-collector driver or use a<br>current limiting series resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

# **EXILINX**.

## Readback

FPGA configuration data can be read back using either the Slave Parallel or JTAG mode. This function is disabled if the Bitstream Generator *Security* option is set to either *Level1* or *Level2*.

Along with the configuration data, it is possible to read back the contents of all registers and distributed RAM.

To synchronously control when register values are captured for readback, use the CAPTURE\_SPARTAN3 library primitive, which applies for both Spartan-3 and Spartan-3E FPGA families.

The Readback feature is available in most Spartan-3E FPGA product options, as indicated in Table 68. The Readback feature is not available in the XC3S1200E and XC3S1600E FPGAs when using the -4 speed grade in the Commercial temperature grade. Similarly, block RAM Readback support is not available in the -4 speed grade, Commercial temperature devices. If Readback is required in an XC3S1200E or XC3S1600E FPGA, or if block RAM Readback is required on any Spartan-3E FPGA, upgrade to either the Industrial temperature grade version or the -5 speed grade.

The Xilinx iMPACT programming software uses the Readback feature for its optional Verify and Readback operations. The Xilinx ChipScope™ software presently does not use Readback but may in future updates.

## Table 68: Readback Support in Spartan-3E FPGAs

| Temperature Range      | Comm           | Commercial |     |  |  |  |

|------------------------|----------------|------------|-----|--|--|--|

| Speed Grade            | -4             | -5         | -4  |  |  |  |

| Block RAM Readback     |                |            |     |  |  |  |

| All Spartan-3E FPGAs   | No             | Yes        | Yes |  |  |  |

| General Readback (regi | sters, distrit | outed RAM) |     |  |  |  |

| XC3S100E               | Yes            | Yes        | Yes |  |  |  |

| XC3S250E               | Yes            | Yes        | Yes |  |  |  |

| XC3S500E               | Yes            | Yes        | Yes |  |  |  |

| XC3S1200E              | No             | Yes        | Yes |  |  |  |

| XC3S1600E              | No             | Yes        | Yes |  |  |  |

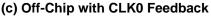

## Differential I/O Standards

Figure 69: Differential Input Voltages

| Table 82: Recommended C | Derating Conditions for  | r User I/Os Usina Di | ifferential Signal Standards  |

|-------------------------|--------------------------|----------------------|-------------------------------|

|                         | peruting contaitions for |                      | incremation orginal otamaarao |

| IOSTANDARD               | ۷۵      | <sub>CO</sub> for Drive | ers <sup>(1)</sup> | V <sub>ID</sub> |          |          | V <sub>ICM</sub> |         |         |

|--------------------------|---------|-------------------------|--------------------|-----------------|----------|----------|------------------|---------|---------|

| Attribute                | Min (V) | Nom (V)                 | Max (V)            | Min (mV)        | Nom (mV) | Max (mV) | Min (V)          | Nom (V) | Max (V) |

| LVDS_25                  | 2.375   | 2.50                    | 2.625              | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| BLVDS_25                 | 2.375   | 2.50                    | 2.625              | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| MINI_LVDS_25             | 2.375   | 2.50                    | 2.625              | 200             | -        | 600      | 0.30             | -       | 2.2     |

| LVPECL_25 <sup>(2)</sup> |         | Inputs Only             |                    | 100             | 800      | 1000     | 0.5              | 1.2     | 2.0     |

| RSDS_25                  | 2.375   | 2.50                    | 2.625              | 100             | 200      | -        | 0.3              | 1.20    | 1.4     |

| DIFF_HSTL_I_18           | 1.7     | 1.8                     | 1.9                | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_HSTL_III_18         | 1.7     | 1.8                     | 1.9                | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_SSTL18_I            | 1.7     | 1.8                     | 1.9                | 100             | -        | -        | 0.7              | -       | 1.1     |

| DIFF_SSTL2_I             | 2.3     | 2.5                     | 2.7                | 100             | -        | -        | 1.0              | -       | 1.5     |

#### Notes:

1. The  $V_{CCO}$  rails supply only differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

#### Table 90: Propagation Times for the IOB Input Path

|                     | Description                                                                                                                           |                                                  | IFD    |            | Speed | Grade |       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|------------|-------|-------|-------|

| Symbol              |                                                                                                                                       | Conditions                                       | DELAY_ | Device     | -5    | -4    | Units |

|                     |                                                                                                                                       |                                                  | VALUE= |            | Min   | Min   |       |

| Propagatio          | on Times                                                                                                                              |                                                  |        | •<br>•     |       |       |       |

| T <sub>IOPLI</sub>  | The time it takes for data to travel<br>from the Input pin through the<br>IFF latch to the I output with no<br>input delay programmed | LVCMOS25 <sup>(2)</sup> ,<br>IFD_DELAY_VALUE = 0 | 0      | All        | 1.96  | 2.25  | ns    |

| T <sub>IOPLID</sub> | The time it takes for data to travel                                                                                                  | LVCMOS25 <sup>(2)</sup> ,                        | 2      | XC3S100E   | 5.40  | 5.97  | ns    |

|                     | from the Input pin through the<br>IFF latch to the I output with the<br>input delay programmed                                        | IFD_DELAY_VALUE =<br>default software setting    | 3      | All Others | 6.30  | 7.20  |       |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

2. This propagation time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. When this is true, *add* the appropriate Input adjustment from Table 91.

| Convert Input Time from<br>LVCMOS25 to the | 7100  | Add the<br>Adjustment Below |       |  |  |

|--------------------------------------------|-------|-----------------------------|-------|--|--|

| Following Signal Standard                  | Speed | Grade                       | Units |  |  |

| (IOŜTANDARD)                               | -5    | -4                          |       |  |  |

| Single-Ended Standards                     |       |                             |       |  |  |

| LVTTL                                      | 0.42  | 0.43                        | ns    |  |  |

| LVCMOS33                                   | 0.42  | 0.43                        | ns    |  |  |

| LVCMOS25                                   | 0     | 0                           | ns    |  |  |

| LVCMOS18                                   | 0.96  | 0.98                        | ns    |  |  |

| LVCMOS15                                   | 0.62  | 0.63                        | ns    |  |  |

| LVCMOS12                                   | 0.26  | 0.27                        | ns    |  |  |

| PCI33_3                                    | 0.41  | 0.42                        | ns    |  |  |

| PCI66_3                                    | 0.41  | 0.42                        | ns    |  |  |

| HSTL_I_18                                  | 0.12  | 0.12                        | ns    |  |  |

| HSTL_III_18                                | 0.17  | 0.17                        | ns    |  |  |

| SSTL18_I                                   | 0.30  | 0.30                        | ns    |  |  |

| SSTL2_I                                    | 0.15  | 0.15                        | ns    |  |  |

#### Table 91: Input Timing Adjustments by IOSTANDARD

#### Table 91: Input Timing Adjustments by IOSTANDARD (Cont'd)

| Convert Input Time from   |       | l the<br>ent Below | · · · |  |

|---------------------------|-------|--------------------|-------|--|

| Following Signal Standard | Speed | Units              |       |  |

| (IOSTANDARD)              | -5    | -4                 |       |  |

| Differential Standards    |       | ·                  |       |  |

| LVDS_25                   | 0.48  | 0.49               | ns    |  |

| BLVDS_25                  | 0.39  | 0.39               | ns    |  |

| MINI_LVDS_25              | 0.48  | 0.49               | ns    |  |

| LVPECL_25                 | 0.27  | 0.27               | ns    |  |

| RSDS_25                   | 0.48  | 0.49               | ns    |  |

| DIFF_HSTL_I_18            | 0.48  | 0.49               | ns    |  |

| DIFF_HSTL_III_18          | 0.48  | 0.49               | ns    |  |

| DIFF_SSTL18_I             | 0.30  | 0.30               | ns    |  |

| DIFF_SSTL2_I              | 0.32  | 0.32               | ns    |  |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77, Table 80, and Table 82.

2. These adjustments are used to convert input path times originally specified for the LVCMOS25 standard to times that correspond to other signal standards.

## **Configuration Clock (CCLK) Characteristics**

## Table 112: Master Mode CCLK Output Period by ConfigRate Option Setting

| Symbol              | Description                                | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------|------------------------------|----------------------|---------|---------|-------|

| T <sub>CCLK1</sub>  | CCLK clock period by<br>ConfigRate setting | 1<br>(power-on value and     | Commercial           | 570     | 1,250   | ns    |

| CCLK1               | Comgnate setting                           | default value)               | Industrial           | 485     | 1,230   | ns    |

| т                   |                                            | 3                            | Commercial           | 285     | 625     | ns    |

| T <sub>CCLK3</sub>  |                                            | 5                            | Industrial           | 242     | 025     | ns    |

| т                   | _                                          | 6                            | Commercial           | 142     | 313     | ns    |

| T <sub>CCLK6</sub>  |                                            | 6                            | Industrial           | 121     |         | ns    |

| т                   | 10                                         | 12                           | Commercial           | 71.2    | - 157   | ns    |

| T <sub>CCLK12</sub> |                                            | 12                           | Industrial           | 60.6    | 157     | ns    |

| Τ                   |                                            | 25                           | Commercial           | 35.5    | 78.2    | ns    |

| T <sub>CCLK25</sub> | 25                                         | 25                           | Industrial           | 30.3    | 70.2    | ns    |

| <b>-</b>            |                                            | 50                           | Commercial           | 17.8    | 39.1    | ns    |

| T <sub>CCLK50</sub> |                                            | 50                           | Industrial           | 15.1    |         | ns    |

#### Notes:

1. Set the ConfigRate option value when generating a configuration bitstream. See Bitstream Generator (BitGen) Options in Module 2.

| Symbol              | Description                                                  | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum    | Maximum | Units |     |

|---------------------|--------------------------------------------------------------|------------------------------|----------------------|------------|---------|-------|-----|

| F <sub>CCLK1</sub>  | Equivalent CCLK clock frequency by <i>ConfigRate</i> setting | 1<br>(power-on value and     | Commercial           | 0.8        | 1.8     | MHz   |     |

| ' CCLK1             | by <b>comgnate</b> setting                                   | default value)               | Industrial           | 0.0        | 2.1     | MHz   |     |

| E                   | _                                                            | 3                            | Commercial           | 1.6        | 3.6     | MHz   |     |

| F <sub>CCLK3</sub>  |                                                              | 5                            | Industrial           | 1.0        | 4.2     | MHz   |     |

| Family              |                                                              | 6                            | 6                    | Commercial | 3.2     | 7.1   | MHz |

| F <sub>CCLK6</sub>  |                                                              | 0                            | Industrial           | 5.2        | 8.3     | MHz   |     |

| F                   |                                                              | 12                           | Commercial           | 6.4        | 14.1    | MHz   |     |

| F <sub>CCLK12</sub> |                                                              | 12                           | Industrial           | 0.4        | 16.5    | MHz   |     |

| E                   |                                                              | 25                           | Commercial           | 12.8       | 28.1    | MHz   |     |

| F <sub>CCLK25</sub> |                                                              | 25                           | Industrial           | 12.0       | 33.0    | MHz   |     |

| Familia             |                                                              | 50                           | Commercial           | 25.6       | 56.2    | MHz   |     |

| F <sub>CCLK50</sub> |                                                              | 50                           | Industrial           | 20.0       | 66.0    | MHz   |     |

## Table 114: Master Mode CCLK Output Minimum Low and High Time

| Symbol             | Description                         |            |     |     | ConfigR | ate Setting | 9    |     | Units |  |

|--------------------|-------------------------------------|------------|-----|-----|---------|-------------|------|-----|-------|--|

|                    | Description                         |            | 1   | 3   | 6       | 12          | 25   | 50  | Units |  |

| T <sub>MCCL,</sub> | Master mode CCLK minimum            | Commercial | 276 | 138 | 69      | 34.5        | 17.1 | 8.5 | ns    |  |

| I MCCH             | T <sub>MCCH</sub> Low and High time |            | 235 | 117 | 58      | 29.3        | 14.5 | 7.3 | ns    |  |

## Table 115: Slave Mode CCLK Input Low and High Time

| Symbol                                  | Description            | Min | Мах | Units |

|-----------------------------------------|------------------------|-----|-----|-------|

| T <sub>SCCL,</sub><br>T <sub>SCCH</sub> | CCLK Low and High time | 5   | ∞   | ns    |

## Table 133: CP132 Package Pinout (Cont'd)

| Bank | XC3S100E<br>Pin Name      | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                   |

|------|---------------------------|----------------------------------|------------|----------------------------------------|

| 0    | VCCO_0                    | VCCO_0                           | B10        | VCCO                                   |

| 1    | IO/A0                     | IO/A0                            | F12        | DUAL                                   |

| 1    | IO/VREF_1                 | IO/VREF_1                        | K13        | VREF                                   |

| 1    | IO_L01N_1/A15             | IO_L01N_1/A15                    | N14        | DUAL                                   |

| 1    | IO_L01P_1/A16             | IO_L01P_1/A16                    | N13        | DUAL                                   |

| 1    | IO_L02N_1/A13             | IO_L02N_1/A13                    | M13        | DUAL                                   |

| 1    | IO_L02P_1/A14             | IO_L02P_1/A14                    | M12        | DUAL                                   |

| 1    | IO_L03N_1/A11             | IO_L03N_1/A11                    | L14        | DUAL                                   |

| 1    | IO_L03P_1/A12             | IO_L03P_1/A12                    | L13        | DUAL                                   |

| 1    | IO_L04N_1/A9/RHCLK1       | IO_L04N_1/A9/RHCLK1              | J12        | RHCLK/DUAL                             |

| 1    | IO_L04P_1/A10/RHCLK0      | IO_L04P_1/A10/RHCLK0             | K14        | RHCLK/DUAL                             |

| 1    | IO_L05N_1/A7/RHCLK3/TRDY1 | IO_L05N_1/A7/RHCLK3/TRDY1        | J14        | RHCLK/DUAL                             |

| 1    | IO_L05P_1/A8/RHCLK2       | IO_L05P_1/A8/RHCLK2              | J13        | RHCLK/DUAL                             |

| 1    | IO_L06N_1/A5/RHCLK5       | IO_L06N_1/A5/RHCLK5              | H12        | RHCLK/DUAL                             |

| 1    | IO_L06P_1/A6/RHCLK4/IRDY1 | IO_L06P_1/A6/RHCLK4/IRDY1        | H13        | RHCLK/DUAL                             |

| 1    | IO_L07N_1/A3/RHCLK7       | IO_L07N_1/A3/RHCLK7              | G13        | RHCLK/DUAL                             |

| 1    | IO_L07P_1/A4/RHCLK6       | IO_L07P_1/A4/RHCLK6              | G14        | RHCLK/DUAL                             |

| 1    | IO_L08N_1/A1              | IO_L08N_1/A1                     | F13        | DUAL                                   |

| 1    | IO_L08P_1/A2              | IO_L08P_1/A2                     | F14        | DUAL                                   |

| 1    | IO_L09N_1/LDC0            | IO_L09N_1/LDC0                   | D12        | DUAL                                   |

| 1    | IO_L09P_1/HDC             | IO_L09P_1/HDC                    | D13        | DUAL                                   |

| 1    | IO_L10N_1/LDC2            | IO_L10N_1/LDC2                   | C13        | DUAL                                   |

| 1    | IO_L10P_1/LDC1            | IO_L10P_1/LDC1                   | C14        | DUAL                                   |

| 1    | IP/VREF_1                 | IP/VREF_1                        | G12        | VREF                                   |

| 1    | VCCO_1                    | VCCO_1                           | E13        | VCCO                                   |

| 1    | VCCO_1                    | VCCO_1                           | M14        | VCCO                                   |

| 2    | IO/D5                     | IO/D5                            | P4         | DUAL                                   |

| 2    | IO/M1                     | IO/M1                            | N7         | DUAL                                   |

| 2    | IP/VREF_2                 | IO/VREF_2                        | P11        | 100E: VREF(INPUT)<br>Others: VREF(I/O) |

| 2    | IO_L01N_2/INIT_B          | IO_L01N_2/INIT_B                 | N1         | DUAL                                   |

| 2    | IO_L01P_2/CSO_B           | IO_L01P_2/CSO_B                  | M2         | DUAL                                   |

| 2    | IO_L02N_2/MOSI/CSI_B      | IO_L02N_2/MOSI/CSI_B             | N2         | DUAL                                   |

| 2    | IO_L02P_2/DOUT/BUSY       | IO_L02P_2/DOUT/BUSY              | P1         | DUAL                                   |

| 2    | IO_L03N_2/D6/GCLK13       | IO_L03N_2/D6/GCLK13              | N4         | DUAL/GCLK                              |

| 2    | IO_L03P_2/D7/GCLK12       | IO_L03P_2/D7/GCLK12              | M4         | DUAL/GCLK                              |

| 2    | IO_L04N_2/D3/GCLK15       | IO_L04N_2/D3/GCLK15              | N5         | DUAL/GCLK                              |

| 2    | IO_L04P_2/D4/GCLK14       | IO_L04P_2/D4/GCLK14              | M5         | DUAL/GCLK                              |

| 2    | IO_L06N_2/D1/GCLK3        | IO_L06N_2/D1/GCLK3               | P7         | DUAL/GCLK                              |

| 2    | IO_L06P_2/D2/GCLK2        | IO_L06P_2/D2/GCLK2               | P6         | DUAL/GCLK                              |

| 2    | IO_L07N_2/DIN/D0          | IO_L07N_2/DIN/D0                 | N8         | DUAL                                   |

| 2    | IO_L07P_2/M0              | IO_L07P_2/M0                     | P8         | DUAL                                   |

| 2    | N.C. (�)                  | IO_L08N_2/A22                    | M9         | 100E: N.C.<br>Others: DUAL             |

## User I/Os by Bank

Table 134 shows how the 83 available user-I/O pins are distributed on the XC3S100E FPGA packaged in the CP132 package. Table 135 indicates how the 92 available user-I/O

pins are distributed on the XC3S250E and the XC3S500E FPGAs in the CP132 package.

#### Table 134: User I/Os Per Bank for the XC3S100E in the CP132 Package

| Package |          | Maximum 1/0 | All Possible I/O Pins by Type |       |      |                     |                    |

|---------|----------|-------------|-------------------------------|-------|------|---------------------|--------------------|

| Edge    | I/O Bank | Maximum I/O | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |

| Тор     | 0        | 18          | 6                             | 2     | 1    | 1                   | 8                  |

| Right   | 1        | 23          | 0                             | 0     | 21   | 2                   | 0 <sup>(2)</sup>   |

| Bottom  | 2        | 22          | 0                             | 0     | 20   | 2                   | 0 <sup>(2)</sup>   |

| Left    | 3        | 20          | 10                            | 0     | 0    | 2                   | 8                  |

| TOTAL   |          | 83          | 16                            | 2     | 42   | 7                   | 16                 |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

#### Table 135: User I/Os Per Bank for the XC3S250E and XC3S500E in the CP132 Package

| Package | VO Berli | Maximum 1/0 | All Possible I/O Pins by Type |       |      |                     |                    |  |

|---------|----------|-------------|-------------------------------|-------|------|---------------------|--------------------|--|

| Edge    | I/O Bank | Maximum I/O | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |  |

| Тор     | 0        | 22          | 11                            | 0     | 1    | 2                   | 8                  |  |

| Right   | 1        | 23          | 0                             | 0     | 21   | 2                   | 0 <sup>(2)</sup>   |  |

| Bottom  | 2        | 26          | 0                             | 0     | 24   | 2                   | 0(2)               |  |

| Left    | 3        | 21          | 11                            | 0     | 0    | 2                   | 8                  |  |

| TOTAL   |          | 92          | 22                            | 0     | 46   | 8                   | 16                 |  |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

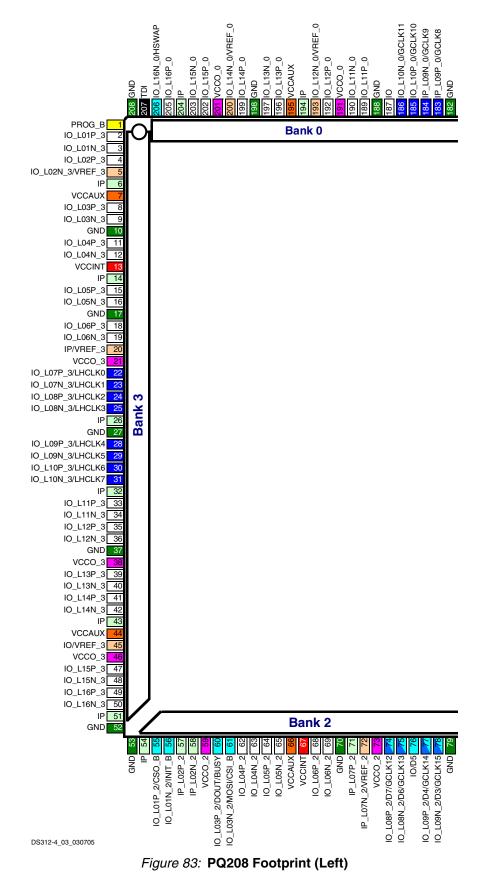

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| 3      | IO_L14P_3                        | P41          | I/O    |

| 3      | IO_L15N_3                        | P48          | I/O    |

| 3      | IO_L15P_3                        | P47          | I/O    |

| 3      | IO_L16N_3                        | P50          | I/O    |

| 3      | IO_L16P_3                        | P49          | I/O    |

| 3      | IP                               | P6           | INPUT  |

| 3      | IP                               | P14          | INPUT  |

| 3      | IP                               | P26          | INPUT  |

| 3      | IP                               | P32          | INPUT  |

| 3      | IP                               | P43          | INPUT  |

| 3      | IP                               | P51          | INPUT  |

| 3      | IP/VREF_3                        | P20          | VREF   |

| 3      | VCCO_3                           | P21          | VCCO   |

| 3      | VCCO_3                           | P38          | VCCO   |

| 3      | VCCO_3                           | P46          | VCCO   |

| GND    | GND                              | P10          | GND    |

| GND    | GND                              | P17          | GND    |

| GND    | GND                              | P27          | GND    |

| GND    | GND                              | P37          | GND    |

| GND    | GND                              | P52          | GND    |

| GND    | GND                              | P53          | GND    |

| GND    | GND                              | P70          | GND    |

| GND    | GND                              | P79          | GND    |

| GND    | GND                              | P85          | GND    |

| GND    | GND                              | P95          | GND    |

| GND    | GND                              | P105         | GND    |

| GND    | GND                              | P121         | GND    |

| GND    | GND                              | P131         | GND    |

| GND    | GND                              | P141         | GND    |

| GND    | GND                              | P156         | GND    |

| GND    | GND                              | P173         | GND    |

| GND    | GND                              | P182         | GND    |

| GND    | GND                              | P188         | GND    |

| GND    | GND                              | P198         | GND    |

| GND    | GND                              | P208         | GND    |

| VCCAUX | DONE                             | P104         | CONFIG |

| VCCAUX | PROG_B                           | P1           | CONFIG |

| VCCAUX | ТСК                              | P158         | JTAG   |

| VCCAUX | TDI                              | P207         | JTAG   |

| VCCAUX | TDO                              | P157         | JTAG   |

| VCCAUX | TMS                              | P155         | JTAG   |

| VCCAUX | VCCAUX                           | P7           | VCCAUX |

|        | 1                                |              |        |

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| VCCAUX | VCCAUX                           | P66          | VCCAUX |

| VCCAUX | VCCAUX                           | P92          | VCCAUX |

| VCCAUX | VCCAUX                           | P111         | VCCAUX |

| VCCAUX | VCCAUX                           | P149         | VCCAUX |

| VCCAUX | VCCAUX                           | P166         | VCCAUX |

| VCCAUX | VCCAUX                           | P195         | VCCAUX |

| VCCINT | VCCINT                           | P13          | VCCINT |

| VCCINT | VCCINT                           | P67          | VCCINT |

| VCCINT | VCCINT                           | P117         | VCCINT |

| VCCINT | VCCINT                           | P170         | VCCINT |

## PQ208 Footprint (Left)

## Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name    | XC3S500E Pin Name    | XC3S1200E Pin Name   | FT256<br>Ball | Туре                                                             |

|------|----------------------|----------------------|----------------------|---------------|------------------------------------------------------------------|

| 1    | IO                   | IO                   | IP                   | M14           | 250E: I/O<br>500E: I/O<br>1200E: INPUT                           |

| 1    | IO/VREF_1            | IP/VREF_1            | IP/VREF_1            | D16           | 250E: VREF(I/O)<br>500E:<br>VREF(INPUT)<br>1200E:<br>VREF(INPUT) |

| 1    | IP/VREF_1            | IP/VREF_1            | IP/VREF_1            | H13           | VREF                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | E15           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | G11           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | K11           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | M15           | VCCO                                                             |

| 2    | IP                   | IP                   | IO                   | M7            | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |

| 2    | IP                   | IP                   | IO                   | T12           | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |

| 2    | IO/D5                | IO/D5                | IO/D5                | Т8            | DUAL                                                             |

| 2    | IO/M1                | IO/M1                | IO/M1                | T10           | DUAL                                                             |

| 2    | IO/VREF_2            | IO/VREF_2            | IO/VREF_2            | P13           | VREF                                                             |

| 2    | IO/VREF_2            | IO/VREF_2            | IO/VREF_2            | R4            | VREF                                                             |

| 2    | IO_L01N_2/INIT_B     | IO_L01N_2/INIT_B     | IO_L01N_2/INIT_B     | P4            | DUAL                                                             |

| 2    | IO_L01P_2/CSO_B      | IO_L01P_2/CSO_B      | IO_L01P_2/CSO_B      | P3            | DUAL                                                             |

| 2    | IO_L03N_2/MOSI/CSI_B | IO_L03N_2/MOSI/CSI_B | IO_L03N_2/MOSI/CSI_B | N5            | DUAL                                                             |

| 2    | IO_L03P_2/DOUT/BUSY  | IO_L03P_2/DOUT/BUSY  | IO_L03P_2/DOUT/BUSY  | P5            | DUAL                                                             |

| 2    | IO_L04N_2            | IO_L04N_2            | IO_L04N_2            | T5            | I/O                                                              |

| 2    | IO_L04P_2            | IO_L04P_2            | IO_L04P_2            | T4            | I/O                                                              |

| 2    | IO_L05N_2            | IO_L05N_2            | IO_L05N_2            | N6            | I/O                                                              |

| 2    | IO_L05P_2            | IO_L05P_2            | IO_L05P_2            | M6            | I/O                                                              |

| 2    | IO_L06N_2            | IO_L06N_2            | IO_L06N_2            | P6            | I/O                                                              |

| 2    | IO_L06P_2            | IO_L06P_2            | IO_L06P_2            | R6            | I/O                                                              |

| 2    | N.C. (�)             | IO_L07N_2            | IO_L07N_2            | P7            | 250E: N.C.<br>500E: I/O<br>1200E: I/O                            |

| 2    | N.C. (♠)             | IO_L07P_2            | IO_L07P_2            | N7            | 250E: N.C.<br>500E: I/O<br>1200E: I/O                            |

| 2    | IO_L09N_2/D6/GCLK13  | IO_L09N_2/D6/GCLK13  | IO_L09N_2/D6/GCLK13  | L8            | DUAL/GCLK                                                        |

| 2    | IO_L09P_2/D7/GCLK12  | IO_L09P_2/D7/GCLK12  | IO_L09P_2/D7/GCLK12  | M8            | DUAL/GCLK                                                        |

| 2    | IO_L10N_2/D3/GCLK15  | IO_L10N_2/D3/GCLK15  | IO_L10N_2/D3/GCLK15  | P8            | DUAL/GCLK                                                        |

| 2    | IO_L10P_2/D4/GCLK14  | IO_L10P_2/D4/GCLK14  | IO_L10P_2/D4/GCLK14  | N8            | DUAL/GCLK                                                        |

| 2    | IO_L12N_2/D1/GCLK3   | IO_L12N_2/D1/GCLK3   | IO_L12N_2/D1/GCLK3   | N9            | DUAL/GCLK                                                        |

| 2    | IO_L12P_2/D2/GCLK2   | IO_L12P_2/D2/GCLK2   | IO_L12P_2/D2/GCLK2   | P9            | DUAL/GCLK                                                        |

| 2    | IO_L13N_2/DIN/D0     | IO_L13N_2/DIN/D0     | IO_L13N_2/DIN/D0     | M9            | DUAL                                                             |

| 2    | IO_L13P_2/M0         | IO_L13P_2/M0         | IO_L13P_2/M0         | L9            | DUAL                                                             |

# User I/Os by Bank

Table 144, Table 145, and Table 146 indicate how the available user-I/O pins are distributed between the four I/O banks on the FT256 package.

The XC3S250E FPGA in the FT256 package has 18 unconnected balls, labeled with an "N.C." type. These pins are also indicated with the black diamond (♦) symbol in Figure 85.

## Table 144: User I/Os Per Bank on XC3S250E in the FT256 Package

| Package | I/O Bank  | Maximum I/O | All Possible I/O Pins by Type |       |      |                     |                    |

|---------|-----------|-------------|-------------------------------|-------|------|---------------------|--------------------|

| Edge    | I/O Balik |             | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |

| Тор     | 0         | 44          | 20                            | 10    | 1    | 5                   | 8                  |

| Right   | 1         | 42          | 10                            | 7     | 21   | 4                   | 0(2)               |

| Bottom  | 2         | 44          | 8                             | 9     | 24   | 3                   | 0(2)               |

| Left    | 3         | 42          | 24                            | 7     | 0    | 3                   | 8                  |

| TOTAL   |           | 172         | 62                            | 33    | 46   | 15                  | 16                 |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

### Table 145: User I/Os Per Bank on XC3S500E in the FT256 Package

| Package | I/O Bank  | Maximum I/O |     | All Possible I/O Pins by Type |      |                     |                    |

|---------|-----------|-------------|-----|-------------------------------|------|---------------------|--------------------|

| Edge    | I/O Darik |             | I/O | INPUT                         | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |

| Тор     | 0         | 46          | 22  | 10                            | 1    | 5                   | 8                  |

| Right   | 1         | 48          | 15  | 7                             | 21   | 5                   | 0 <sup>(2)</sup>   |

| Bottom  | 2         | 48          | 11  | 9                             | 24   | 4                   | 0(2)               |

| Left    | 3         | 48          | 28  | 7                             | 0    | 5                   | 8                  |

| TOTAL   |           | 190         | 76  | 33                            | 46   | 19                  | 16                 |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

### Table 146: User I/Os Per Bank on XC3S1200E in the FT256 Package

| Package | I/O Bank  | Maximum I/O | All Possible I/O Pins by Type |       |      |                     |                    |

|---------|-----------|-------------|-------------------------------|-------|------|---------------------|--------------------|

| Edge    | I/O Darik |             | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |

| Тор     | 0         | 46          | 24                            | 8     | 1    | 5                   | 8                  |

| Right   | 1         | 48          | 14                            | 8     | 21   | 5                   | 0(2)               |

| Bottom  | 2         | 48          | 13                            | 7     | 24   | 4                   | 0(2)               |

| Left    | 3         | 48          | 27                            | 8     | 0    | 5                   | 8                  |

| TOTAL   |           | 190         | 78                            | 31    | 46   | 19                  | 16                 |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

## Table 148: FG320 Package Pinout (Cont'd)

| Bank   | XC3S500E Pin Name | XC3S1200E Pin Name | XC3S1600E Pin Name | FG320<br>Ball | Туре   |

|--------|-------------------|--------------------|--------------------|---------------|--------|

| GND    | GND               | GND                | GND                | K8            | GND    |

| GND    | GND               | GND                | GND                | K11           | GND    |

| GND    | GND               | GND                | GND                | K16           | GND    |

| GND    | GND               | GND                | GND                | L8            | GND    |

| GND    | GND               | GND                | GND                | L9            | GND    |

| GND    | GND               | GND                | GND                | L10           | GND    |

| GND    | GND               | GND                | GND                | L11           | GND    |

| GND    | GND               | GND                | GND                | M7            | GND    |

| GND    | GND               | GND                | GND                | M12           | GND    |

| GND    | GND               | GND                | GND                | Т9            | GND    |

| GND    | GND               | GND                | GND                | U2            | GND    |

| GND    | GND               | GND                | GND                | U17           | GND    |

| GND    | GND               | GND                | GND                | V1            | GND    |

| GND    | GND               | GND                | GND                | V18           | GND    |

| VCCAUX | DONE              | DONE               | DONE               | V17           | CONFIG |

| VCCAUX | PROG_B            | PROG_B             | PROG_B             | B1            | CONFIG |

| VCCAUX | ТСК               | TCK                | TCK                | A17           | JTAG   |

| VCCAUX | TDI               | TDI                | TDI                | A2            | JTAG   |

| VCCAUX | TDO               | TDO                | TDO                | C16           | JTAG   |

| VCCAUX | TMS               | TMS                | TMS                | D15           | JTAG   |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | B7            | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | B12           | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | G2            | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | G17           | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | M2            | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | M17           | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | U7            | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX             | VCCAUX             | U12           | VCCAUX |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | E5            | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | E14           | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | F6            | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | F13           | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | N6            | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | N13           | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | P5            | VCCINT |

| VCCINT | VCCINT            | VCCINT             | VCCINT             | P14           | VCCINT |

Spartan-3 FPGA Family: Pinout Descriptions

| Bank 0                              |                      |                                |                               |                                        |                             |                                      |                                    |                                        |                                |                                |        |      |