### AMD Xilinx - XC3S500E-4CPG132I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 1164                                                          |

| Number of Logic Elements/Cells | 10476                                                         |

| Total RAM Bits                 | 368640                                                        |

| Number of I/O                  | 92                                                            |

| Number of Gates                | 500000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 132-TFBGA, CSPBGA                                             |

| Supplier Device Package        | 132-CSPBGA (8x8)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s500e-4cpg132i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan-3E FPGAs provide additional input flexibility by allowing I/O standards to be mixed in different banks. For a particular V<sub>CCO</sub> voltage, Table 6 and Table 7 list all of the

IOSTANDARDs that can be combined and if the IOSTANDARD is supported as an input only or can be used for both inputs and outputs.

#### Table 6: Single-Ended IOSTANDARD Bank Compatibility

|              |                  | v <sub>cco</sub> s | Supply/Comp      | atibility        |                  | Input Rec          | quirements                                         |

|--------------|------------------|--------------------|------------------|------------------|------------------|--------------------|----------------------------------------------------|

| Single-Ended | 1.2V             | 1.5V               | 1.8V             | 2.5V             | 3.3V             | V <sub>REF</sub>   | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) |

| LVTTL        | -                | -                  | -                | -                | Input/<br>Output | N/R <sup>(1)</sup> | N/R                                                |

| LVCMOS33     | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| LVCMOS25     | -                | -                  | -                | Input/<br>Output | Input            | N/R                | N/R                                                |

| LVCMOS18     | -                | -                  | Input/<br>Output | Input            | Input            | N/R                | N/R                                                |

| LVCMOS15     | -                | Input/<br>Output   | Input            | Input            | Input            | N/R                | N/R                                                |

| LVCMOS12     | Input/<br>Output | Input              | Input            | Input            | Input            | N/R                | N/R                                                |

| PCI33_3      | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| PCI66_3      | -                | -                  | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| HSTL_I_18    | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| HSTL_III_18  | -                | -                  | Input/<br>Output | Input            | Input            | 1.1                | 1.8                                                |

| SSTL18_I     | -                | -                  | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| SSTL2_I      | -                | -                  | -                | Input/<br>Output | Input            | 1.25               | 1.25                                               |

#### Notes:

1. N/R - Not required for input operation.

The SLICEM pair supports two additional functions:

- Two 16x1 distributed RAM blocks, RAM16

- Two 16-bit shift registers, SRL16

Each of these elements is described in more detail in the following sections.

# Logic Cells

The combination of a LUT and a storage element is known as a "Logic Cell". The additional features in a slice, such as the wide multiplexers, carry logic, and arithmetic gates, add to the capacity of a slice, implementing logic that would otherwise require additional LUTs. Benchmarks have shown that the overall slice is equivalent to 2.25 simple logic cells. This calculation provides the equivalent logic cell count shown in Table 9.

## **Slice Details**

Figure 15 is a detailed diagram of the SLICEM. It represents a superset of the elements and connections to be found in all slices. The dashed and gray lines (blue when viewed in color) indicate the resources found only in the SLICEM and not in the SLICEL.

Each slice has two halves, which are differentiated as top and bottom to keep them distinct from the upper and lower slices in a CLB. The control inputs for the clock (CLK), Clock Enable (CE), Slice Write Enable (SLICEWE1), and Reset/Set (RS) are shared in common between the two halves.

The LUTs located in the top and bottom portions of the slice are referred to as "G" and "F", respectively, or the "G-LUT" and the "F-LUT". The storage elements in the top and bottom portions of the slice are called FFY and FFX, respectively.

Each slice has two multiplexers with F5MUX in the bottom portion of the slice and FiMUX in the top portion. Depending on the slice, the FiMUX takes on the name F6MUX, F7MUX, or F8MUX, according to its position in the multiplexer chain. The lower SLICEL and SLICEM both have an F6MUX. The upper SLICEM has an F7MUX, and the upper SLICEL has an F8MUX.

The carry chain enters the bottom of the slice as CIN and exits at the top as COUT. Five multiplexers control the chain: CYINIT, CYOF, and CYMUXF in the bottom portion and CYOG and CYMUXG in the top portion. The dedicated arithmetic logic includes the exclusive-OR gates XORF and XORG (bottom and top portions of the slice, respectively) as well as the AND gates FAND and GAND (bottom and top portions, respectively).

See Table 10 for a description of all the slice input and output signals.

| Name     | Location        | Direction | Description                                                                                                                     |

|----------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| F[4:1]   | SLICEL/M Bottom | Input     | F-LUT and FAND inputs                                                                                                           |

| G[4:1]   | SLICEL/M Top    | Input     | G-LUT and GAND inputs or Write Address (SLICEM)                                                                                 |

| BX       | SLICEL/M Bottom | Input     | Bypass to or output (SLICEM) or storage element, or control input to F5MUX, input to carry logic, or data input to RAM (SLICEM) |

| BY       | SLICEL/M Top    | Input     | Bypass to or output (SLICEM) or storage element, or control input to FiMUX, input to carry logic, or data input to RAM (SLICEM) |

| BXOUT    | SLICEM Bottom   | Output    | BX bypass output                                                                                                                |

| BYOUT    | SLICEM Top      | Output    | BY bypass output                                                                                                                |

| ALTDIG   | SLICEM Top      | Input     | Alternate data input to RAM                                                                                                     |

| DIG      | SLICEM Top      | Output    | ALTDIG or SHIFTIN bypass output                                                                                                 |

| SLICEWE1 | SLICEM Common   | Input     | RAM Write Enable                                                                                                                |

| F5       | SLICEL/M Bottom | Output    | Output from F5MUX; direct feedback to FiMUX                                                                                     |

| FXINA    | SLICEL/M Top    | Input     | Input to FiMUX; direct feedback from F5MUX or another FiMUX                                                                     |

| FXINB    | SLICEL/M Top    | Input     | Input to FiMUX; direct feedback from F5MUX or another FiMUX                                                                     |

| Fi       | SLICEL/M Top    | Output    | Output from FiMUX; direct feedback to another FiMUX                                                                             |

| CE       | SLICEL/M Common | Input     | FFX/Y Clock Enable                                                                                                              |

| SR       | SLICEL/M Common | Input     | FFX/Y Set or Reset or RAM Write Enable (SLICEM)                                                                                 |

| CLK      | SLICEL/M Common | Input     | FFX/Y Clock or RAM Clock (SLICEM)                                                                                               |

| SHIFTIN  | SLICEM Top      | Input     | Data input to G-LUT RAM                                                                                                         |

#### Table 10: Slice Inputs and Outputs

## **XILINX**.

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

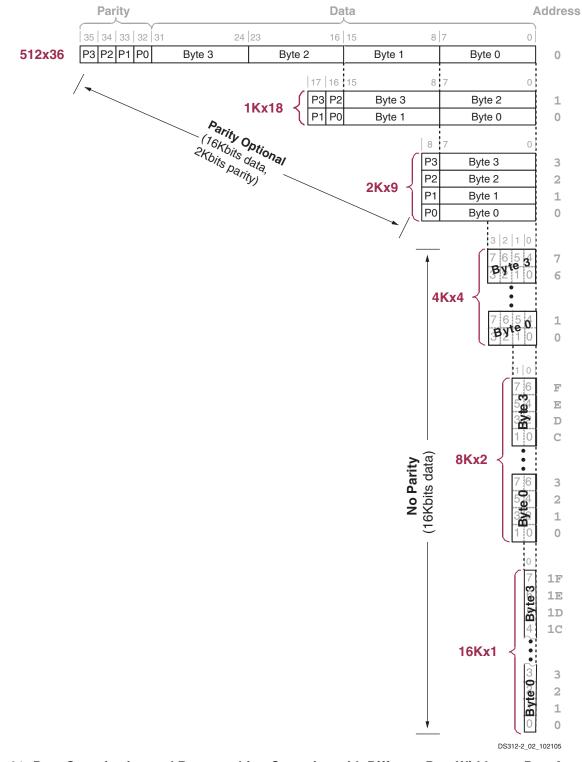

Figure 31: Data Organization and Bus-matching Operation with Different Port Widths on Port A and Port B

## Table 23: Block RAM Port Signals

| Signal<br>Description    | Port A<br>Signal<br>Name | Port B<br>Signal<br>Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------|--------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus              | ADDRA                    | ADDRB                    | Input     | The Address Bus selects a memory location for read or write operations.<br>The width (w) of the port's associated data path determines the number of<br>available address lines (r), as per Table 22.                                                                                                                                                                                                                                                                                                                                          |

|                          |                          |                          |           | Whenever a port is enabled (ENA or ENB = High), address transitions must<br>meet the data sheet setup and hold times with respect to the port clock<br>(CLKA or CLKB), as shown in Table 103, page 138. This requirement must<br>be met even if the RAM read output is of no interest.                                                                                                                                                                                                                                                         |

| Data Input Bus           | DIA                      | DIB                      | Input     | Data at the DI input bus is written to the RAM location specified by the address input bus (ADDR) during the active edge of the CLK input, when the clock enable (EN) and write enable (WE) inputs are active.                                                                                                                                                                                                                                                                                                                                 |

|                          |                          |                          |           | It is possible to configure a port's DI input bus width (w-p) based on Table 22. This selection applies to both the DI and DO paths of a given port.                                                                                                                                                                                                                                                                                                                                                                                           |

| Parity Data Input(s)     | DIPA                     | DIPB                     | Input     | Parity inputs represent additional bits included in the data input path.<br>Although referred to herein as "parity" bits, the parity inputs and outputs<br>have no special functionality for generating or checking parity and can be<br>used as additional data bits. The number of parity bits 'p' included in the DI<br>(same as for the DO bus) depends on a port's total data path width (w). See<br>Table 22.                                                                                                                            |

| Data Output Bus          | DOA                      | DOB                      | Output    | Data is written to the DO output bus from the RAM location specified by the address input bus, ADDR. See the DI signal description for DO port width configurations.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                          |                          |           | Basic data access occurs on the active edge of the CLK when WE is<br>inactive and EN is active. The DO outputs mirror the data stored in the<br>address ADDR memory location. Data access with WE active if the<br>WRITE_MODE attribute is set to the value: WRITE_FIRST, which<br>accesses data after the write takes place. READ_FIRST accesses data<br>before the write occurs. A third attribute, NO_CHANGE, latches the DO<br>outputs upon the assertion of WE. See Block RAM Data Operations for<br>details on the WRITE_MODE attribute. |

| Parity Data<br>Output(s) | DOPA                     | DOPB                     | Output    | Parity outputs represent additional bits included in the data input path. The number of parity bits 'p' included in the DI bus (same as for the DO bus) depends on a port's total data path width (w). See the DIP signal description for configuration details.                                                                                                                                                                                                                                                                               |

| Write Enable             | WEA                      | WEB                      | Input     | When asserted together with EN, this input enables the writing of data to the RAM. When WE is inactive with EN asserted, read operations are still possible. In this case, a latch passes data from the addressed memory location to the DO outputs.                                                                                                                                                                                                                                                                                           |

| Clock Enable             | ENA                      | ENB                      | Input     | When asserted, this input enables the CLK signal to perform read and write operations to the block RAM. When inactive, the block RAM does not perform any read or write operations.                                                                                                                                                                                                                                                                                                                                                            |

| Set/Reset                | SSRA                     | SSRB                     | Input     | When asserted, this pin forces the DO output latch to the value of the SRVAL attribute. It is synchronized to the CLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Clock                    | CLKA                     | CLKB                     | Input     | This input accepts the clock signal to which read and write operations are synchronized. All associated port inputs are required to meet setup times with respect to the clock signal's active edge. The data output bus responds after a clock-to-out delay referenced to the clock signal's active edge.                                                                                                                                                                                                                                     |

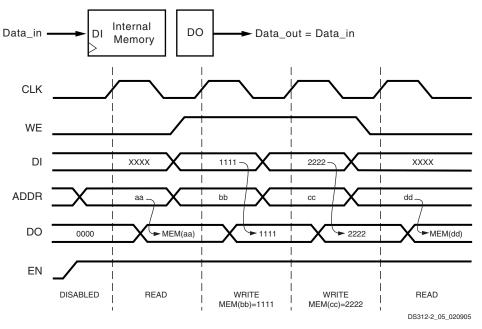

There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a output latch to the DO outputs. The timing for basic data access is shown in the

XILINX.

portions of Figure 33, Figure 34, and Figure 35 during which WE is Low.

Data also can be accessed on the DO outputs when asserting the WE input based on the value of the WRITE\_MODE attribute as described in Table 26.

#### Table 26: WRITE\_MODE Effect on Data Output Latches During Write Operations

| Write Mode                      | Effect on Same Port                                                                                                              | Effect on Opposite Port<br>(dual-port only with same address)   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| WRITE_FIRST<br>Read After Write | Data on DI and DIP inputs is written into specified RAM location and simultaneously appears on DO and DOP outputs.               | Invalidates data on DO and DOP outputs.                         |

| READ_FIRST<br>Read Before Write | Data from specified RAM location appears on DO and DOP outputs.<br>Data on DI and DIP inputs is written into specified location. | Data from specified RAM location appears on DO and DOP outputs. |

| NO_CHANGE<br>No Read on Write   | Data on DO and DOP outputs remains unchanged.<br>Data on DI and DIP inputs is written into specified<br>location.                | Invalidates data on DO and DOP outputs.                         |

Setting the WRITE\_MODE attribute to a value of WRITE\_FIRST, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE\_FIRST timing is shown in the portion of Figure 33 during which WE is High.

Setting the WRITE\_MODE attribute to a value of READ\_FIRST, data already stored in the addressed location passes to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ\_FIRST timing is shown in the portion of Figure 34 during which WE is High.

www.xilinx.com

cancel out the clock skew. When the DLL phase-aligns the CLK0 signal with the CLKIN signal, it asserts the LOCKED output, indicating a lock on to the CLKIN signal.

#### **DLL Attributes and Related Functions**

The DLL unit has a variety of associated attributes as described in Table 29. Each attribute is described in detail in the sections that follow.

#### Table 29: DLL Attributes

**EXILINX**

| Attribute Description |                                                                                                                       | Values                                                                                                |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| CLK_FEEDBACK          | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                                      | NONE, <u>1X</u> , 2X                                                                                  |  |

| CLKIN_DIVIDE_BY_2     | Halves the frequency of the CLKIN signal just as it enters the DCM                                                    | <i>FALSE</i> , TRUE                                                                                   |  |

| CLKDV_DIVIDE          | Selects the constant used to divide the CLKIN input frequency to generate the CLKDV output frequency                  | 1.5, <u>2</u> , 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6.0, 6.5, 7.0, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, and 16 |  |

| CLKIN_PERIOD          | Additional information that allows the DLL to operate with the most efficient lock time and the best jitter tolerance | Floating-point value representing the CLKIN period in nanoseconds                                     |  |

### **DLL Clock Input Connections**

For best results, an external clock source enters the FPGA via a Global Clock Input (GCLK). Each specific DCM has four possible direct, optimal GCLK inputs that feed the DCM's CLKIN input, as shown in Table 30. Table 30 also provides the specific pin numbers by package for each GCLK input. The two additional DCM's on the XC3S1200E and XC3S1600E have similar optimal connections from the left-edge LHCLK and the right-edge RHCLK inputs, as described in Table 31 and Table 32.

The DCM supports differential clock inputs (for example, LVDS, LVPECL\_25) via a pair of GCLK inputs that feed an internal single-ended signal to the DCM's CLKIN input.

#### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

## **Direct Connections**

Direct connect lines route signals to neighboring tiles: vertically, horizontally, and diagonally. These lines most often drive a signal from a "source" tile to a double, hex, or long line and conversely from the longer interconnect back to a direct line accessing a "destination" tile.

## Global Controls (STARTUP\_SPARTAN3E)

In addition to the general-purpose interconnect, Spartan-3E FPGAs have two global logic control signals, as described in Table 43. These signals are available to the FPGA application via the STARTUP SPARTAN3E primitive.

| Table 43: Sp | partan-3E Global | Logic Control | Signals |

|--------------|------------------|---------------|---------|

|--------------|------------------|---------------|---------|

| Global Control<br>Input | Description                                                                                                                                                                                                                                        |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GSR                     | <b>Global Set/Reset:</b> When High,<br>asynchronously places all registers and<br>flip-flops in their initial state (see Initialization,<br>page 31). Asserted automatically during the<br>FPGA configuration process (see Start-Up,<br>page 105). |  |  |  |  |

| GTS                     | <b>Global Three-State:</b> When High, asynchronously forces all I/O pins to a high-impedance state (Hi-Z, three-state).                                                                                                                            |  |  |  |  |

The Global Set/Reset (GSR) signal replaces the global reset signal included in many ASIC-style designs. Use the GSR control instead of a separate global reset signal in the design to free up CLB inputs, resulting in a smaller, more efficient design. Similarly, the GSR signal is asserted automatically during the FPGA configuration process, guaranteeing that the FPGA starts-up in a known state.

The STARTUP\_SPARTAN3E primitive also includes two other signals used specifically during configuration. The MBT signals are for Dynamically Loading Multiple Configuration Images Using MultiBoot Option, page 91. The CLK input is an alternate clock for configuration Start-Up, page 105.

# **Configuration Bitstream Image Sizes**

A specific Spartan-3E part type always requires a constant number of configuration bits, regardless of design complexity, as shown in Table 45. The configuration file size for a multiple-FPGA daisy-chain design roughly equals the sum of the individual file sizes.

# Table 45: Number of Bits to Program a Spartan-3EFPGA (Uncompressed Bitstreams)

| Spartan-3E FPGA | Number of<br>Configuration Bits |

|-----------------|---------------------------------|

| XC3S100E        | 581,344                         |

| XC3S250E        | 1,353,728                       |

| XC3S500E        | 2,270,208                       |

| XC3S1200E       | 3,841,184                       |

| XC3S1600E       | 5,969,696                       |

## **Pin Behavior During Configuration**

For additional information, refer to the "Configuration Pins and Behavior during Configuration" chapter in <u>UG332</u>.

Table 46 shows how various pins behave during the FPGAconfiguration process. The actual behavior depends on the

## Table 46: Pin Behavior during Configuration

values applied to the M2, M1, and M0 mode select pins and the HSWAP pin. The mode select pins determine which of the I/O pins are borrowed during configuration and how they function. In JTAG configuration mode, no user-I/O pins are borrowed for configuration.

All user-I/O pins, input-only pins, and dual-purpose pins that are not actively involved in the currently-select configuration mode are high impedance (floating, three-stated, Hi-Z) during the configuration process. These pins are indicated in Table 46 as gray shaded table entries or cells.

The HSWAP input controls whether all user-I/O pins, input-only pins, and dual-purpose pins have a pull-up resistor to the supply rail or not. When HSWAP is Low, each pin has an internal pull-up resistor that is active throughout configuration. After configuration, pull-up and pull-down resistors are available in the FPGA application as described in Pull-Up and Pull-Down Resistors.

The yellow-shaded table entries or cells represent pins where the pull-up resistor is always enabled during configuration, regardless of the HSWAP input. The post-configuration behavior of these pins is defined by Bitstream Generator options as defined in Table 69.

| Pin Name                           | Master Serial | SPI (Serial<br>Flash) | BPI (Parallel<br>NOR Flash) | JTAG   | Slave Parallel | Slave Serial | I/O Bank <sup>(3)</sup> |

|------------------------------------|---------------|-----------------------|-----------------------------|--------|----------------|--------------|-------------------------|

| IO* (user-I/O)<br>IP* (input-only) |               |                       |                             |        |                |              | -                       |

| TDI                                | TDI           | TDI                   | TDI                         | TDI    | TDI            | TDI          | V <sub>CCAUX</sub>      |

| TMS                                | TMS           | TMS                   | TMS                         | TMS    | TMS            | TMS          | V <sub>CCAUX</sub>      |

| ТСК                                | TCK           | ТСК                   | TCK                         | TCK    | TCK            | ТСК          | V <sub>CCAUX</sub>      |

| TDO                                | TDO           | TDO                   | TDO                         | TDO    | TDO            | TDO          | V <sub>CCAUX</sub>      |

| PROG_B                             | PROG_B        | PROG_B                | PROG_B                      | PROG_B | PROG_B         | PROG_B       | V <sub>CCAUX</sub>      |

| DONE                               | DONE          | DONE                  | DONE                        | DONE   | DONE           | DONE         | V <sub>CCAUX</sub>      |

| HSWAP                              | HSWAP         | HSWAP                 | HSWAP                       | HSWAP  | HSWAP          | HSWAP        | 0                       |

| M2                                 | 0             | 0                     | 0                           | 1      | 1              | 1            | 2                       |

| M1                                 | 0             | 0                     | 1                           | 0      | 1              | 1            | 2                       |

| MO                                 | 0             | 1                     | 0 = Up<br>1 = Down          | 1      | 0              | 1            | 2                       |

| CCLK                               | CCLK (I/O)    | CCLK (I/O)            | CCLK (I/O)                  |        | CCLK (I)       | CCLK (I)     | 2                       |

| INIT_B                             | INIT_B        | INIT_B                | INIT_B                      |        | INIT_B         | INIT_B       | 2                       |

| CSO_B                              |               | CSO_B                 | CSO_B                       |        | CSO_B          |              | 2                       |

| DOUT/BUSY                          | DOUT          | DOUT                  | BUSY                        |        | BUSY           | DOUT         | 2                       |

| MOSI/CSI_B                         |               | MOSI                  | CSI_B                       |        | CSI_B          |              | 2                       |

| D7                                 |               |                       | D7                          |        | D7             |              | 2                       |

| D6                                 |               |                       | D6                          |        | D6             |              | 2                       |

| D5                                 |               |                       | D5                          |        | D5             |              | 2                       |

| D4                                 |               |                       | D4                          |        | D4             |              | 2                       |

| D3                                 |               |                       | D3                          |        | D3             |              | 2                       |

| D2                                 |               |                       | D2                          |        | D2             |              | 2                       |

| D1                                 |               |                       | D1                          |        | D1             |              | 2                       |

www.xilinx.com

##

## SPI Serial Flash Mode

For additional information, refer to the "Master SPI Mode" chapter in UG332.

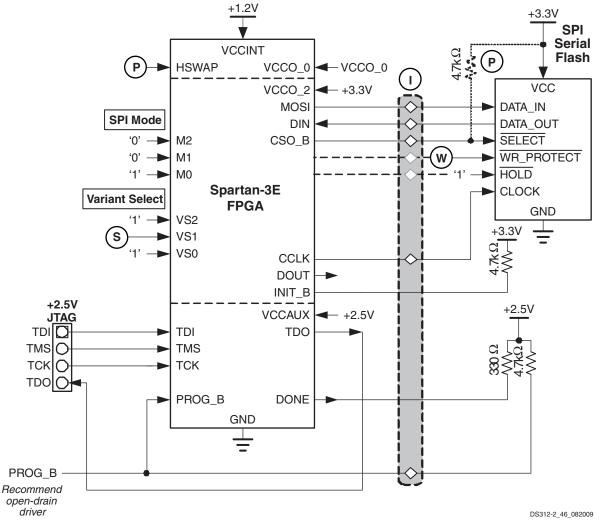

In SPI Serial Flash mode (M[2:0] = <0:0:1>), the Spartan-3E FPGA configures itself from an attached industry-standard SPI serial Flash PROM, as illustrated in Figure 53 and Figure 54. The FPGA supplies the CCLK output clock from its internal oscillator to the clock input of the attached SPI Flash PROM.

(S) Although SPI is a standard four-wire interface, various available SPI Flash PROMs use different command protocols. The FPGA's variant select pins, VS[2:0], define how the FPGA communicates with the SPI Flash, including which SPI Flash command the FPGA issues to start the read operation and the number of dummy bytes inserted before the FPGA expects to receive valid data from the SPI Flash. Table 53 shows the available SPI Flash PROMs expected to operate with Spartan-3E FPGAs. Other compatible devices might work but have not been tested for suitability with Spartan-3E FPGAs. All other VS[2:0] values are reserved for future use. Consult the data sheet for the desired SPI Flash device to determine its suitability. The basic timing requirements and waveforms are provided in

# Serial Peripheral Interface (SPI) Configuration Timing in Module 3.

Figure 53 shows the general connection diagram for those SPI Flash PROMs that support the 0x03 READ command or the 0x0B FAST READ commands.

Figure 54 shows the connection diagram for Atmel DataFlash serial PROMs, which also use an SPI-based protocol. 'B'-series DataFlash devices are limited to FPGA applications operating over the commercial temperature range. Industrial temperature range applications must use 'C'- or 'D'-series DataFlash devices, which have a shorter DataFlash select setup time, because of the faster FPGA CCLK frequency at cold temperatures. W Table 54 shows the connections between the SPI Flash PROM and the FPGA's SPI configuration interface. Each SPI Flash PROM vendor uses slightly different signal naming. The SPI Flash PROM's write protect and hold

controls are not used by the FPGA during configuration. However, the  $\overline{\text{HOLD}}$  pin must be High during the configuration process. The PROM's write protect input must be High in order to write or program the Flash memory.

#### Table 54: Example SPI Flash PROM Connections and Pin Naming

| SPI Flash Pin               | FPGA Connection                                                                                                                                                                                                                                                                   | STMicro | NexFlash | Silicon<br>Storage<br>Technology | Atmel<br>DataFlash |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|----------------------------------|--------------------|

| DATA_IN                     | MOSI                                                                                                                                                                                                                                                                              | D       | DI       | SI                               | SI                 |

| DATA_OUT                    | DIN                                                                                                                                                                                                                                                                               | Q       | DO       | SO                               | SO                 |

| SELECT                      | CSO_B                                                                                                                                                                                                                                                                             | S       | CS       | CE#                              | CS                 |

| CLOCK                       | CCLK                                                                                                                                                                                                                                                                              | С       | CLK      | SCK                              | SCK                |

| WR_PROTECT                  | Not required for FPGA configuration. Must be High<br>to program SPI Flash. Optional connection to<br>FPGA user I/O after configuration.                                                                                                                                           | W       | WP       | WP#                              | WP                 |

| HOLD<br>(see Figure 53)     | Not required for FPGA configuration but must be<br>High during configuration. Optional connection to<br>FPGA user I/O after configuration. Not applicable<br>to Atmel DataFlash.                                                                                                  | HOLD    | HOLD     | HOLD#                            | N/A                |

| RESET<br>(see Figure 54)    | Only applicable to Atmel DataFlash. Not required<br>for FPGA configuration but must be High during<br>configuration. Optional connection to FPGA user<br>I/O after configuration. Do not connect to FPGA's<br>PROG_B as this will prevent direct programming of<br>the DataFlash. | N/A     | N/A      | N/A                              | RESET              |

| RDY/BUSY<br>(see Figure 54) | Only applicable to Atmel DataFlash and only<br>available on certain packages. Not required for<br>FPGA configuration. Output from DataFlash<br>PROM. Optional connection to FPGA user I/O after<br>configuration.                                                                 | N/A     | N/A      | N/A                              | RDY/BUSY           |

The mode select pins, M[2:0], and the variant select pins, VS[2:0] are sampled when the FPGA's INIT\_B output goes High and must be at defined logic levels during this time. After configuration, when the FPGA's DONE output goes High, these pins are all available as full-featured user-I/O pins.

P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins or High to

disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

In a single-FPGA application, the FPGA's DOUT pin is not used but is actively driving during the configuration process.

#### Table 55: Serial Peripheral Interface (SPI) Connections

| Pin Name   | FPGA<br>Direction | Description                                                                                                                                                                                                     | During Configuration                                         | After Configuration |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|

| HSWAP<br>P | Input             | <b>User I/O Pull-Up Control</b> . When Low during configuration, enables pull-up resistors in all I/O pins to respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration<br>1: No pull-ups | Drive at valid logic level<br>throughout configuration.      | User I/O            |

| M[2:0]     | Input             | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                    | M2 = 0, M1 = 0, M0 = 1.<br>Sampled when INIT_B goes<br>High. | User I/O            |

## Single-Ended I/O Standards

#### Table 80: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

| IOSTANDARD                | V       | <sub>CCO</sub> for Drive | ers <sup>(2)</sup> |                | V <sub>REF</sub>          |         | V <sub>IL</sub>          | V <sub>IH</sub> <sup>(3)</sup> |

|---------------------------|---------|--------------------------|--------------------|----------------|---------------------------|---------|--------------------------|--------------------------------|

| Attribute                 | Min (V) | Nom (V)                  | Max (V)            | Min (V)        | Nom (V)                   | Max (V) | Max (V)                  | Min (V)                        |

| LVTTL                     | 3.0     | 3.3                      | 3.465              |                |                           |         | 0.8                      | 2.0                            |

| LVCMOS33 <sup>(4)</sup>   | 3.0     | 3.3                      | 3.465              |                |                           |         | 0.8                      | 2.0                            |

| LVCMOS25 <sup>(4,5)</sup> | 2.3     | 2.5                      | 2.7                |                |                           |         | 0.7                      | 1.7                            |

| LVCMOS18                  | 1.65    | 1.8                      | 1.95               | V <sub>R</sub> | <sub>FF</sub> is not used | d for   | 0.4                      | 0.8                            |

| LVCMOS15                  | 1.4     | 1.5                      | 1.6                | the            | ese I/O standa            | ards    | 0.4                      | 0.8                            |

| LVCMOS12                  | 1.1     | 1.2                      | 1.3                |                |                           |         | 0.4                      | 0.7                            |

| PCI33_3 <sup>(6)</sup>    | 3.0     | 3.3                      | 3.465              |                |                           |         | 0.3 • V <sub>CCO</sub>   | 0.5 • V <sub>CCO</sub>         |

| PCI66_3 <sup>(6)</sup>    | 3.0     | 3.3                      | 3.465              |                |                           |         | 0.3 • V <sub>CCO</sub>   | 0.5 • V <sub>CCO</sub>         |

| HSTL_I_18                 | 1.7     | 1.8                      | 1.9                | 0.8            | 0.9                       | 1.1     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_III_18               | 1.7     | 1.8                      | 1.9                | -              | - 1.1 -                   |         |                          | V <sub>REF</sub> + 0.1         |

| SSTL18_I                  | 1.7     | 1.8                      | 1.9                | 0.833          | 0.833 0.900 0.969         |         | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       |

| SSTL2_I                   | 2.3     | 2.5                      | 2.7                | 1.15           | 1.25                      | 1.35    | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       |

#### Notes:

- Descriptions of the symbols used in this table are as follows: 1.

- $\begin{array}{l} V_{CCO} \mbox{the symbols dised in this table are as follows.} \\ V_{CCO} \mbox{the supply voltage for output drivers} \\ V_{REF} \mbox{the reference voltage for setting the input switching threshold} \\ V_{IL} \mbox{the input voltage that indicates a Low logic level} \\ V_{IH} \mbox{the input voltage that indicates a High logic level} \end{array}$

- The V<sub>CCO</sub> rails supply only output drivers, not input circuits. 2.

- For device operation, the maximum signal voltage (V<sub>IH</sub> max) may be as high as V<sub>IN</sub> max. See Table 73. З.

- There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards. 4.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) use the LVCMOS25 standard and draw power from the V<sub>CCAUX</sub> rail (2.5V). The Dual-Purpose configuration pins use the LVCMOS standard before the User mode. When using these pins as part of a standard 2.5V 5. configuration interface, apply 2.5V to the V<sub>CCO</sub> lines of Banks 0, 1, and 2 at power-on as well as throughout configuration.

- For information on PCI IP solutions, see www.xilinx.com/pci. The PCIX IOSTANDARD is available and has equivalent characteristics but no 6. PCI-X IP is supported.

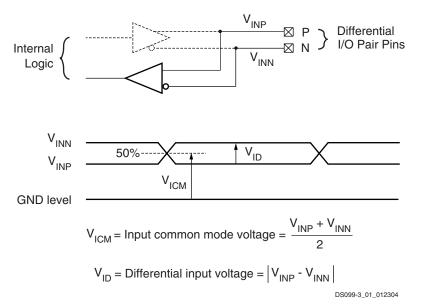

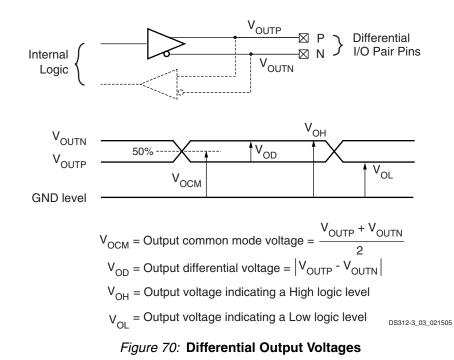

## Differential I/O Standards

Figure 69: Differential Input Voltages

| Table 82: Recommended O | perating Conditions for Use | r I/Os Using Differentia | Signal Standards   |

|-------------------------|-----------------------------|--------------------------|--------------------|

|                         | peruang contantene for coo  | i woo oonig binoronda    | orginal otariaarao |

| IOSTANDARD               | V <sub>CCO</sub> for Drivers <sup>(1)</sup> |             |         |          | V <sub>ID</sub> |          |         | V <sub>ICM</sub> |         |  |  |

|--------------------------|---------------------------------------------|-------------|---------|----------|-----------------|----------|---------|------------------|---------|--|--|

| Attribute                | Min (V)                                     | Nom (V)     | Max (V) | Min (mV) | Nom (mV)        | Max (mV) | Min (V) | Nom (V)          | Max (V) |  |  |

| LVDS_25                  | 2.375                                       | 2.50        | 2.625   | 100      | 350             | 600      | 0.30    | 1.25             | 2.20    |  |  |

| BLVDS_25                 | 2.375                                       | 2.50        | 2.625   | 100      | 350             | 600      | 0.30    | 1.25             | 2.20    |  |  |

| MINI_LVDS_25             | 2.375                                       | 2.50        | 2.625   | 200      | -               | 600      | 0.30    | -                | 2.2     |  |  |

| LVPECL_25 <sup>(2)</sup> |                                             | Inputs Only |         | 100      | 800             | 1000     | 0.5     | 1.2              | 2.0     |  |  |

| RSDS_25                  | 2.375                                       | 2.50        | 2.625   | 100      | 200             | -        | 0.3     | 1.20             | 1.4     |  |  |

| DIFF_HSTL_I_18           | 1.7                                         | 1.8         | 1.9     | 100      | -               | -        | 0.8     | -                | 1.1     |  |  |

| DIFF_HSTL_III_18         | 1.7                                         | 1.8         | 1.9     | 100      | -               | -        | 0.8     | -                | 1.1     |  |  |

| DIFF_SSTL18_I            | 1.7                                         | 1.8         | 1.9     | 100      | -               | -        | 0.7     | -                | 1.1     |  |  |

| DIFF_SSTL2_I             | 2.3                                         | 2.5         | 2.7     | 100      | -               | -        | 1.0     | -                | 1.5     |  |  |

#### Notes:

1. The  $V_{CCO}$  rails supply only differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

Table 83: DC Characteristics of User I/Os Using Differential Signal Standards

| IOSTANDARD       | V <sub>OD</sub> |             | $\Delta V_{OD}$ |             | V <sub>OCM</sub> |            |            | ΔV <sub>C</sub> | ОСМ         | V <sub>OH</sub> | V <sub>OL</sub>         |                         |

|------------------|-----------------|-------------|-----------------|-------------|------------------|------------|------------|-----------------|-------------|-----------------|-------------------------|-------------------------|

| Attribute        | Min<br>(mV)     | Typ<br>(mV) | Max<br>(mV)     | Min<br>(mV) | Max<br>(mV)      | Min<br>(V) | Тур<br>(V) | Max<br>(V)      | Min<br>(mV) | Max<br>(mV)     | Min<br>(V)              | Max<br>(V)              |

| LVDS_25          | 250             | 350         | 450             | -           | -                | 1.125      | -          | 1.375           | -           | -               | -                       | -                       |

| BLVDS_25         | 250             | 350         | 450             | -           | -                | -          | 1.20       | -               | -           | -               | -                       | -                       |

| MINI_LVDS_25     | 300             | -           | 600             | -           | 50               | 1.0        | -          | 1.4             | -           | 50              | -                       | _                       |

| RSDS_25          | 100             | -           | 400             | -           | -                | 1.1        | _          | 1.4             | -           | _               | -                       | _                       |

| DIFF_HSTL_I_18   | -               | -           | -               | -           | -                | -          | _          | -               | -           | -               | $V_{\rm CCO} - 0.4$     | 0.4                     |

| DIFF_HSTL_III_18 | -               | -           | -               | _           | -                | -          | -          | -               | _           | _               | $V_{CCO} - 0.4$         | 0.4                     |

| DIFF_SSTL18_I    | -               | -           | _               | -           | -                | -          | -          | -               | -           | -               | V <sub>TT</sub> + 0.475 | V <sub>TT</sub> – 0.475 |

| DIFF_SSTL2_I     | Ι               | -           | -               | -           | -                | -          | -          | -               | -           | -               | V <sub>TT</sub> + 0.61  | V <sub>TT</sub> – 0.61  |

#### Notes:

1. The numbers in this table are based on the conditions set forth in Table 77 and Table 82.

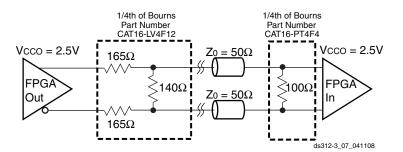

Output voltage measurements for all differential standards are made with a termination resistor (R<sub>T</sub>) of 100Ω across the N and P pins of the differential signal pair. The exception is for BLVDS, shown in Figure 71.

3. At any given time, no more than two of the following differential output standards may be assigned to an I/O bank: LVDS\_25, RSDS\_25, MINI\_LVDS\_25

Figure 71: External Termination Resistors for BLVDS Transmitter and BLVDS Receiver

#### Table 92: Timing for the IOB Output Path

|                     |                                                                                                                                           |                                                                    |        | Speed | Grade |       |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|-------|-------|-------|--|

| Symbol              | Description                                                                                                                               | Conditions                                                         | Device | -5    | -4    | Units |  |

|                     |                                                                                                                                           |                                                                    |        | Min   | Min   | -     |  |

| Clock-to-Outpu      | t Times                                                                                                                                   | 1                                                                  | 1      |       |       |       |  |

| T <sub>IOCKP</sub>  | When reading from the Output Flip-Flop (OFF), the time from the active transition at the OCLK input to data appearing at the Output pin   | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,<br>Fast slew rate | All    | 2.18  | 2.50  | ns    |  |

| Propagation Ti      | mes                                                                                                                                       | .1                                                                 | 3      |       |       |       |  |

| T <sub>IOOP</sub>   | The time it takes for data to travel from the IOB's O input to the Output pin                                                             | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,                   | All    | 2.24  | 2.58  | ns    |  |

| T <sub>IOOLP</sub>  | The time it takes for data to travel from the O input through the OFF latch to the Output pin                                             | Fast slew rate                                                     |        | 2.32  | 2.67  | ns    |  |

| Set/Reset Time      | S                                                                                                                                         |                                                                    |        |       |       |       |  |

| T <sub>IOSRP</sub>  | Time from asserting the OFF's SR input to setting/resetting data at the Output pin                                                        | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,                   | All    | 3.27  | 3.76  | ns    |  |

| T <sub>IOGSRQ</sub> | Time from asserting the Global Set Reset (GSR)<br>input on the STARTUP_SPARTAN3E primitive to<br>setting/resetting data at the Output pin | Fast slew rate                                                     |        | 8.40  | 9.65  | ns    |  |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 94.

3. For minimum delays use the values reported by the Timing Analyzer.

#### Table 93: Timing for the IOB Three-State Path

|                                    |                                                                                                                                                    |                                                    |        | Speed | Grade |       |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|-------|-------|-------|--|

| Symbol                             | Description                                                                                                                                        | Conditions                                         | Device | -5    | -4    | Units |  |

|                                    |                                                                                                                                                    |                                                    |        | Мах   | Max   |       |  |

| Synchronous                        | Output Enable/Disable Times                                                                                                                        |                                                    |        |       |       |       |  |

| Т <sub>ЮСКНZ</sub>                 | Time from the active transition at the OTCLK input<br>of the Three-state Flip-Flop (TFF) to when the<br>Output pin enters the high-impedance state | LVCMOS25, 12 mA<br>output drive, Fast<br>slew rate | All    | 1.49  | 1.71  | ns    |  |

| T <sub>IOCKON</sub> <sup>(2)</sup> | Time from the active transition at TFF's OTCLK input to when the Output pin drives valid data                                                      |                                                    | All    | 2.70  | 3.10  | ns    |  |

| Asynchronous                       | output Enable/Disable Times                                                                                                                        |                                                    |        |       | 1     |       |  |

| T <sub>GTS</sub>                   | Time from asserting the Global Three State (GTS) input on the STARTUP_SPARTAN3E primitive to when the Output pin enters the high-impedance state   | LVCMOS25, 12 mA<br>output drive, Fast<br>slew rate | All    | 8.52  | 9.79  | ns    |  |

| Set/Reset Time                     | es                                                                                                                                                 |                                                    |        |       |       | _     |  |

| T <sub>IOSRHZ</sub>                | Time from asserting TFF's SR input to when the<br>Output pin enters a high-impedance state                                                         | LVCMOS25, 12 mA output drive, Fast                 | All    | 2.11  | 2.43  | ns    |  |

| T <sub>IOSRON</sub> <sup>(2)</sup> | Time from asserting TFF's SR input at TFF to when the Output pin drives valid data                                                                 | slew rate                                          | All    | 3.32  | 3.82  | ns    |  |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 94.

3. For minimum delays use the values reported by the Timing Analyzer.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/23/05 | 2.0     | Added AC timing information and additional DC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Finalized production timing parameters. All speed grades for all Spartan-3E FPGAs are now Production status using the v1.21 speed files, as shown in Table 84. Expanded description in Note 2, Table 78. Updated pin-to-pin and clock-to-output timing based on final characterization, shown in Table 86. Updated system-synchronous input setup and hold times based on final characterization, shown in Table 87 and Table 88. Updated other I/O timing in Table 90. Provided input and output adjustments for LVPECL_25, DIFF_SSTL and DIFF_HSTL I/O standards that supersede the v1.21 speed file values, in Table 91 and Table 94. Reduced I/O three-state and set/reset delays in Table 93. Added XC3S100E FPGA in CP132 package to Table 96. Increased T <sub>AS</sub> slice flip-flop timing by 100 ps in Table 98. Updated distributed RAM timing in Table 99 and SRL16 timing in Table 100. Updated global clock timing, removed left/right clock buffer limits in Table 101. Updated block RAM timing in Table 103. Added DCM parameters for remainder of Step 0 device; added improved Step 1 DCM performance to Table 104, Table 105, Table 106, and Table 107. Added minimum INIT_B pulse width specification, T <sub>INIT</sub> , in Table 111. Increased data hold time for Slave Parallel mode to 1.0 ns (T <sub>SMCCD</sub> ) in Table 106, and Table 107. Corrected links in Table 118 and Table 120. Added MultiBoot timing specifications to Table 122. |

| 04/07/06 | 3.1     | Improved SSO limits for LVDS_25, MINI_LVDS_25, and RSDS_25 I/O standards in the QFP packages (Table 97). Removed potentially confusing Note 2 from Table 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 05/19/06 | 3.2     | Clarified that 100 mV of hysteresis applies to LVCMOS33 and LVCMOS25 I/O standards (Note 4, Table 80). Other minor edits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 05/30/06 | 3.2.1   | Corrected various typos and incorrect links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11/09/06 | 3.4     | Improved absolute maximum voltage specifications in Table 73, providing additional overshoot allowance. Widened the recommended voltage range for PCI and PCI-X standards in Table 80. Clarified Note 2, Table 83. Improved various timing specifications for v1.26 speed file. Added Table 85 to summarize the history of speed file releases after which time all devices became Production status. Added absolute minimum values for Table 86, Table 92, and Table 93. Updated pin-to-pin setup and hold timing based on default IFD_DELAY_VALUE settings in Table 87, Table 88, and Table 90. Added Table 89 about source-synchronous input capture sample window. Promoted Module 3 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 03/16/07 | 3.5     | Based on extensive 90 nm production data, improved (reduced) the maximum quiescent current limits for the $I_{CCINTQ}$ , $I_{CCAUXQ}$ , and $I_{CCOQ}$ specifications in Table 79 by an average of 50%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 05/29/07 | 3.6     | Added note to Table 74 and Table 75 regarding HSWAP in step 0 devices. Updated t <sub>RPW_CLB</sub> in Table 98 to match value in speed file. Improved CLKOUT_FREQ_CLK90 to 200 MHz for Stepping 1 in Table 105.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |