# EXF

Welcome to E-XFL.COM

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details |  |

|---------|--|

|         |  |

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1164                                                         |

| Number of Logic Elements/Cells | 10476                                                        |

| Total RAM Bits                 | 368640                                                       |

| Number of I/O                  | 158                                                          |

| Number of Gates                | 500000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s500e-4pq208i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan-3E FPGAs provide additional input flexibility by allowing I/O standards to be mixed in different banks. For a particular V<sub>CCO</sub> voltage, Table 6 and Table 7 list all of the

IOSTANDARDs that can be combined and if the IOSTANDARD is supported as an input only or can be used for both inputs and outputs.

#### Table 6: Single-Ended IOSTANDARD Bank Compatibility

|              | V <sub>CCO</sub> Supply/Compatibility |                  |                  |                  |                  | Input Requirements |                                                    |

|--------------|---------------------------------------|------------------|------------------|------------------|------------------|--------------------|----------------------------------------------------|

| Single-Ended | 1.2V                                  | 1.5V             | 1.8V             | 2.5V             | 3.3V             | V <sub>REF</sub>   | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) |

| LVTTL        | -                                     | -                | -                | -                | Input/<br>Output | N/R <sup>(1)</sup> | N/R                                                |

| LVCMOS33     | -                                     | -                | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| LVCMOS25     | -                                     | -                | -                | Input/<br>Output | Input            | N/R                | N/R                                                |

| LVCMOS18     | -                                     | -                | Input/<br>Output | Input            | Input            | N/R                | N/R                                                |

| LVCMOS15     | -                                     | Input/<br>Output | Input            | Input            | Input            | N/R                | N/R                                                |

| LVCMOS12     | Input/<br>Output                      | Input            | Input            | Input            | Input            | N/R                | N/R                                                |

| PCI33_3      | -                                     | -                | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| PCI66_3      | -                                     | -                | -                | -                | Input/<br>Output | N/R                | N/R                                                |

| HSTL_I_18    | -                                     | -                | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| HSTL_III_18  | -                                     | -                | Input/<br>Output | Input            | Input            | 1.1                | 1.8                                                |

| SSTL18_I     | -                                     | -                | Input/<br>Output | Input            | Input            | 0.9                | 0.9                                                |

| SSTL2_I      | -                                     | -                | -                | Input/<br>Output | Input            | 1.25               | 1.25                                               |

#### Notes:

1. N/R - Not required for input operation.

## **Pull-Up and Pull-Down Resistors**

Pull-up and pull-down resistors inside each IOB optionally force a floating I/O or Input-only pin to a determined state. Pull-up and pull-down resistors are commonly applied to unused I/Os, inputs, and three-state outputs, but can be used on any I/O or Input-only pin. The pull-up resistor connects an IOB to  $V_{CCO}$  through a resistor. The resistance value depends on the  $V_{CCO}$  voltage (see Module 3, DC and Switching Characteristics for the specifications). The pull-down resistor similarly connects an IOB to ground with a resistor. The PULLUP and PULLDOWN attributes and library primitives turn on these optional resistors.

By default, PULLDOWN resistors terminate all unused I/O and Input-only pins. Unused I/O and Input-only pins can alternatively be set to PULLUP or FLOAT. To change the unused I/O Pad setting, set the Bitstream Generator (BitGen) option *UnusedPin* to PULLUP, PULLDOWN, or FLOAT. The *UnusedPin* option is accessed through the Properties for Generate Programming File in ISE. See Bitstream Generator (BitGen) Options.

During configuration a Low logic level on the HSWAP pin activates pull-up resistors on all I/O and Input-only pins not actively used in the selected configuration mode.

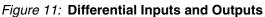

## **Keeper Circuit**

Each I/O has an optional keeper circuit (see Figure 12) that keeps bus lines from floating when not being actively driven. The KEEPER circuit retains the last logic level on a line after all drivers have been turned off. Apply the KEEPER attribute or use the KEEPER library primitive to use the KEEPER circuitry. Pull-up and pull-down resistors override the KEEPER settings.

Figure 12: Keeper Circuit

## Slew Rate Control and Drive Strength

Each IOB has a slew-rate control that sets the output switching edge-rate for LVCMOS and LVTTL outputs. The SLEW attribute controls the slew rate and can either be set to SLOW (default) or FAST.

Each LVCMOS and LVTTL output additionally supports up to six different drive current strengths as shown in Table 8. To adjust the drive strength for each output, the DRIVE attribute is set to the desired drive strength: 2, 4, 6, 8, 12, and 16. Unless otherwise specified in the FPGA application, the software default IOSTANDARD is LVCMOS25, SLOW slew rate, and 12 mA output drive.

| Table | 8: | Programmable | Output | Drive | Current |

|-------|----|--------------|--------|-------|---------|

|-------|----|--------------|--------|-------|---------|

| IOSTANDARD | Output Drive Current (mA) |   |   |   |    |    |

|------------|---------------------------|---|---|---|----|----|

| IOSTANDAND | 2                         | 4 | 6 | 8 | 12 | 16 |

| LVTTL      | ~                         | ~ | ~ | ~ | ~  | ~  |

| LVCMOS33   | ~                         | ~ | ~ | ~ | ~  | ~  |

| LVCMOS25   | ~                         | ~ | ~ | ~ | ~  | -  |

| LVCMOS18   | ~                         | ~ | ~ | ~ | -  | -  |

| LVCMOS15   | ~                         | ~ | ~ | - | -  | -  |

| LVCMOS12   | ~                         | - | - | - | -  | -  |

High output current drive strength and FAST output slew rates generally result in fastest I/O performance. However, these same settings generally also result in transmission line effects on the printed circuit board (PCB) for all but the shortest board traces. Each IOB has independent slew rate and drive strength controls. Use the slowest slew rate and lowest output drive current that meets the performance requirements for the end application.

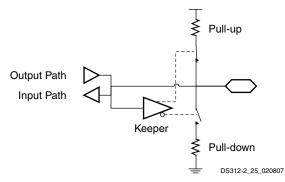

Likewise, due to lead inductance, a given package supports a limited number of simultaneous switching outputs (SSOs) when using fast, high-drive outputs. Only use fast, high-drive outputs when required by the application. There are a number of different conditions under which data can be accessed at the DO outputs. Basic data access always occurs when the WE input is inactive. Under this condition, data stored in the memory location addressed by the ADDR lines passes through a output latch to the DO outputs. The timing for basic data access is shown in the

XILINX.

portions of Figure 33, Figure 34, and Figure 35 during which WE is Low.

Data also can be accessed on the DO outputs when asserting the WE input based on the value of the WRITE\_MODE attribute as described in Table 26.

#### Table 26: WRITE\_MODE Effect on Data Output Latches During Write Operations

| Write Mode                      | Effect on Same Port                                                                                                              | Effect on Opposite Port<br>(dual-port only with same address)   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| WRITE_FIRST<br>Read After Write | Data on DI and DIP inputs is written into specified RAM location and simultaneously appears on DO and DOP outputs.               | Invalidates data on DO and DOP outputs.                         |

| READ_FIRST<br>Read Before Write | Data from specified RAM location appears on DO and DOP outputs.<br>Data on DI and DIP inputs is written into specified location. | Data from specified RAM location appears on DO and DOP outputs. |

| NO_CHANGE<br>No Read on Write   | Data on DO and DOP outputs remains unchanged.<br>Data on DI and DIP inputs is written into specified<br>location.                | Invalidates data on DO and DOP outputs.                         |

Setting the WRITE\_MODE attribute to a value of WRITE\_FIRST, data is written to the addressed memory location on an enabled active CLK edge and is also passed to the DO outputs. WRITE\_FIRST timing is shown in the portion of Figure 33 during which WE is High.

Setting the WRITE\_MODE attribute to a value of READ\_FIRST, data already stored in the addressed location passes to the DO outputs before that location is overwritten with new data from the DI inputs on an enabled active CLK edge. READ\_FIRST timing is shown in the portion of Figure 34 during which WE is High.

www.xilinx.com

# **Digital Clock Managers (DCMs)**

For additional information, refer to the "Using Digital Clock Managers (DCMs)" chapter in  $\underline{\text{UG331}}$ .

# **Differences from the Spartan-3 Architecture**

- Spartan-3E FPGAs have two, four, or eight DCMs, depending on device size.

- The variable phase shifting feature functions differently on Spartan-3E FPGAs than from Spartan-3 FPGAs.

- The Spartan-3E DLLs support lower input frequencies, down to 5 MHz. Spartan-3 DLLs support down to 18 MHz.

## Overview

Spartan-3E FPGA Digital Clock Managers (DCMs) provide flexible, complete control over clock frequency, phase shift and skew. To accomplish this, the DCM employs a Delay-Locked Loop (DLL), a fully digital control system that uses feedback to maintain clock signal characteristics with a high degree of precision despite normal variations in operating temperature and voltage. This section provides a fundamental description of the DCM.

The XC3S100E FPGA has two DCMs, one at the top and one at the bottom of the device. The XC3S250E and XC3S500E FPGAs each include four DCMs, two at the top and two at the bottom. The XC3S1200E and XC3S1600E FPGAs contain eight DCMs with two on each edge (see also Figure 45). The DCM in Spartan-3E FPGAs is surrounded by CLBs within the logic array and is no longer located at the top and bottom of a column of block RAM as in the Spartan-3 architecture. The Digital Clock Manager is instantiated within a design using a "DCM" primitive.

The DCM supports three major functions:

- **Clock-skew Elimination:** Clock skew within a system occurs due to the different arrival times of a clock signal at different points on the die, typically caused by the clock signal distribution network. Clock skew increases setup and hold time requirements and increases clock-to-out times, all of which are undesirable in high frequency applications. The DCM eliminates clock skew by phase-aligning the output clock signal that it generates with the incoming clock signal. This mechanism effectively cancels out the clock distribution delays.

- **Frequency Synthesis:** The DCM can generate a wide range of different output clock frequencies derived from the incoming clock signal. This is accomplished by either multiplying and/or dividing the frequency of the input clock signal by any of several different factors.

- **Phase Shifting:** The DCM provides the ability to shift the phase of all its output clock signals with respect to the input clock signal.

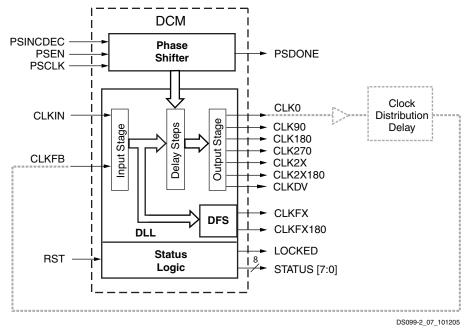

Although a single design primitive, the DCM consists of four interrelated functional units: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), the Phase Shifter (PS), and the Status Logic. Each component has its associated signals, as shown in Figure 40.

Figure 40: DCM Functional Blocks and Associated Signals

# Delay-Locked Loop (DLL)

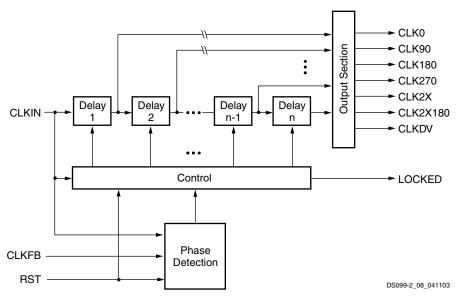

The most basic function of the DLL component is to eliminate clock skew. The main signal path of the DLL consists of an input stage, followed by a series of discrete delay elements or *steps*, which in turn leads to an output stage. This path together with logic for phase detection and control forms a system complete with feedback as shown in Figure 41. In Spartan-3E FPGAs, the DLL is implemented using a counter-based delay line. The DLL component has two clock inputs, CLKIN and CLKFB, as well as seven clock outputs, CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV as described in Table 28. The clock outputs drive simultaneously. Signals that initialize and report the state of the DLL are discussed in Status Logic.

Figure 41: Simplified Functional Diagram of DLL

#### Table 28: DLL Signals

| Signal   | Direction | Description                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | Input     | Receives the incoming clock signal. See Table 30, Table 31, and Table 32 for optimal external inputs to a DCM.             |

| CLKFB    | Input     | Accepts either CLK0 or CLK2X as the feedback signal. (Set the CLK_FEEDBACK attribute accordingly).                         |

| CLK0     | Output    | Generates a clock signal with the same frequency and phase as CLKIN.                                                       |

| CLK90    | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 90°.                                           |

| CLK180   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 180°.                                          |

| CLK270   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 270°.                                          |

| CLK2X    | Output    | Generates a clock signal with the same phase as CLKIN, and twice the frequency.                                            |

| CLK2X180 | Output    | Generates a clock signal with twice the frequency of CLKIN, and phase-shifted 180° with respect to CLK2X.                  |

| CLKDV    | Output    | Divides the CLKIN frequency by CLKDV_DIVIDE value to generate lower frequency clock signal that is phase-aligned to CLKIN. |

The clock signal supplied to the CLKIN input serves as a reference waveform. The DLL seeks to align the rising-edge of feedback signal at the CLKFB input with the rising-edge of CLKIN input. When eliminating clock skew, the common approach to using the DLL is as follows: The CLK0 signal is passed through the clock distribution network that feeds all the registers it synchronizes. These registers are either

internal or external to the FPGA. After passing through the clock distribution network, the clock signal returns to the DLL via a feedback line called CLKFB. The control block inside the DLL measures the phase error between CLKFB and CLKIN. This phase error is a measure of the clock skew that the clock distribution network introduces. The control block activates the appropriate number of delay steps to

cancel out the clock skew. When the DLL phase-aligns the CLK0 signal with the CLKIN signal, it asserts the LOCKED output, indicating a lock on to the CLKIN signal.

#### **DLL Attributes and Related Functions**

The DLL unit has a variety of associated attributes as described in Table 29. Each attribute is described in detail in the sections that follow.

#### Table 29: DLL Attributes

**EXILINX**

| Attribute         | Description                                                                                                           | Values                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| CLK_FEEDBACK      | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                                      | NONE, <u>1X</u> , 2X                                                                                  |

| CLKIN_DIVIDE_BY_2 | Halves the frequency of the CLKIN signal just as it enters the DCM                                                    | <i>FALSE</i> , TRUE                                                                                   |

| CLKDV_DIVIDE      | Selects the constant used to divide the CLKIN input frequency to generate the CLKDV output frequency                  | 1.5, <u>2</u> , 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6.0, 6.5, 7.0, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, and 16 |

| CLKIN_PERIOD      | Additional information that allows the DLL to operate with the most efficient lock time and the best jitter tolerance | Floating-point value representing the CLKIN period in nanoseconds                                     |

## **DLL Clock Input Connections**

For best results, an external clock source enters the FPGA via a Global Clock Input (GCLK). Each specific DCM has four possible direct, optimal GCLK inputs that feed the DCM's CLKIN input, as shown in Table 30. Table 30 also provides the specific pin numbers by package for each GCLK input. The two additional DCM's on the XC3S1200E and XC3S1600E have similar optimal connections from the left-edge LHCLK and the right-edge RHCLK inputs, as described in Table 31 and Table 32.

The DCM supports differential clock inputs (for example, LVDS, LVPECL\_25) via a pair of GCLK inputs that feed an internal single-ended signal to the DCM's CLKIN input.

### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

## VARIABLE Phase Shift Mode

In VARIABLE phase shift mode, the FPGA application dynamically adjusts the fine phase shift value using three

Table 36: Signals for Variable Phase Mode

inputs to the PS unit (PSEN, PSCLK, and PSINCDEC), as defined in Table 36 and shown in Figure 40.

| •                       |           |                                                                                                                                                                              |

|-------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                  | Direction | Description                                                                                                                                                                  |

| PSEN <sup>(1)</sup>     | Input     | Enables the Phase Shift unit for variable phase adjustment.                                                                                                                  |

| PSCLK <sup>(1)</sup>    | Input     | Clock to synchronize phase shift adjustment.                                                                                                                                 |

| PSINCDEC <sup>(1)</sup> | Input     | When High, increments the current phase shift value. When Low, decrements the current phase shift value. This signal is synchronized to the PSCLK signal.                    |

| PSDONE                  | Output    | Goes High to indicate that the present phase adjustment is complete and PS unit is ready for next phase adjustment request. This signal is synchronized to the PSCLK signal. |

#### Notes:

1. This input supports either a true or inverted polarity.

The FPGA application uses the three PS inputs on the Phase Shift unit to dynamically and incrementally increase or decrease the phase shift amount on all nine DCM clock outputs.

To adjust the current phase shift value, the PSEN enable signal must be High to enable the PS unit. Coincidently, PSINCDEC must be High to increment the current phase shift amount or Low to decrement the current amount. All VARIABLE phase shift operations are controlled by the PSCLK input, which can be the CLKIN signal or any other clock signal.

#### Design Note

The VARIABLE phase shift feature operates differently from the Spartan-3 DCM; use the DCM\_SP primitive, not the DCM primitive.

#### DCM\_DELAY\_STEP

DCM\_DELAY\_STEP is the finest delay resolution available in the PS unit. Its value is provided at the bottom of Table 105 in Module 3. For each enabled PSCLK cycle that PSINCDEC is High, the PS unit adds one DCM\_ DELAY\_STEP of phase shift to all nine DCM outputs. Similarly, for each enabled PSCLK cycle that PSINCDEC is Low, the PS unit subtracts one DCM\_ DELAY\_STEP of phase shift from all nine DCM outputs.

Because each DCM\_DELAY\_STEP has a minimum and maximum value, the actual phase shift delay for the present phase increment/decrement value (VALUE) falls within the minimum and maximum values according to Equation 4 and Equation 5.

$T_{PS}(Max) = VALUE \bullet DCM_DELAY_STEP_MAX Eq 4$

$T_{PS}(Min) = VALUE \bullet DCM_DELAY_STEP_MIN Eq 5$

The maximum variable phase shift steps, MAX\_STEPS, is described in Equation 6 or Equation 7, for a given CLKIN input period,  $T_{CLKIN}$ , in nanoseconds. To convert this to a

phase shift range measured in time and not steps, use MAX\_STEPS derived in Equation 6 and Equation 7 for VALUE in Equation 4 and Equation 5.

If CLKIN < 60 MHz:

$MAX\_STEPS = \pm[INTEGER(10 \bullet (T_{CLKIN}-3))] Eq 6$

If CLKIN  $\geq$  60 MHz:

MAX\_STEPS =  $\pm [INTEGER(15 \bullet (T_{CLKIN} - 3))]$  Eq.7

The phase adjustment might require as many as 100 CLKIN cycles plus 3 PSCLK cycles to take effect, at which point the DCM's PSDONE output goes High for one PSCLK cycle. This pulse indicates that the PS unit completed the previous adjustment and is now ready for the next request.

Asserting the Reset (RST) input returns the phase shift to zero.

Also, in a multi-FPGA daisy-chain configuration of more than two devices, all intermediate FPGAs between the first and last devices must be Spartan-3E or Virtex-5 FPGAs. The last FPGA in the chain can be from any Xilinx FPGA family.

# BPI Mode Interaction with Right and Bottom Edge Global Clock Inputs

Some of the BPI mode configuration pins are shared with global clock inputs along the right and bottom edges of the device (Bank 1 and Bank 2, respectively). These pins are not easily reclaimable for clock inputs after configuration, especially if the FPGA application access the parallel NOR Flash after configuration. Table 64 summarizes the shared pins.

# Table 64: Shared BPI Configuration Mode and GlobalBuffer Input Pins

| Device<br>Edge | Global Buffer<br>Input Pin | BPI Mode<br>Configuration Pin |

|----------------|----------------------------|-------------------------------|

|                | GCLK0                      | RDWR_B                        |

|                | GCLK2                      | D2                            |

|                | GCLK3                      | D1                            |

| Bottom         | GCLK12                     | D7                            |

|                | GCLK13                     | D6                            |

|                | GCLK14                     | D4                            |

|                | GCLK15                     | D3                            |

|                | RHCLK0                     | A10                           |

|                | RHCLK1                     | A9                            |

|                | RHCLK2                     | A8                            |

| Diabt          | RHCLK3                     | A7                            |

| Right          | RHCLK4                     | A6                            |

|                | RHCLK5                     | A5                            |

|                | RHCLK6                     | A4                            |

|                | RHCLK7                     | A3                            |

# **EXILINX**.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/16/07 | 3.5     | Added information about new Spartan-3 Generation user guides (Design Documentation Available).<br>Added cross-references to <u>UG331</u> : Spartan-3 Generation FPGA User Guide and to <u>UG332</u> : Spartan-3<br>Generation Configuration User Guide. Added note about possible JTAG configuration issues when the<br>FPGA mode pins are set for Master mode and using software prior to ISE 9.1.01i (JTAG Mode).<br>Removed a few lingering references to "weak" pull-up resistors, including in Figure 12. Removed<br>vestigial references regarding the LDC[2:0] and HDC pins during Slave Parallel Mode configuration.<br>These pins are not used in this configuration mode. |

| 05/29/07 | 3.6     | Added information about HSWAP and PCI differences between steppings to Table 71. Removed<br>"Performance Differences between Global Buffers" to match improved specs in Module 3. Updated<br>PROG_B pulse width descriptions to match specification in Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 04/18/08 | 3.7     | Corrected Figure 6 to show six taps and updated associated text. Added note for recommended pull-up on DONE in Table 55 and elsewhere. Added a caution regarding Persist of pins A20-A23. Updated Stepping description in Table 71 to note that only Stepping 1 is in production today. Updated links.                                                                                                                                                                                                                                                                                                                                                                              |

| 08/26/09 | 3.8     | Added a frequency limitation to Equation 6. Added a new Equation 7 with a frequency limitation. Added a Spread Spectrum, page 56 paragraph. Added Table 42, page 60. Updated a Flash vendor name in Table 61, page 88. Removed the < symbol from the flash read access times in Table 62, page 88. Revised the first paragraph in Configuration Sequence, page 101. Revised the first paragraph in Power-On Behavior, page 110. Revised the second paragraph in Production Stepping, page 111. Revised the first paragraph in Ordering a Later Stepping, page 111.                                                                                                                  |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated the design note section in VARIABLE Phase Shift Mode. Added the VQ100 to the Quadrant Clock Routing section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

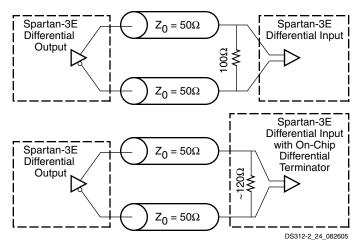

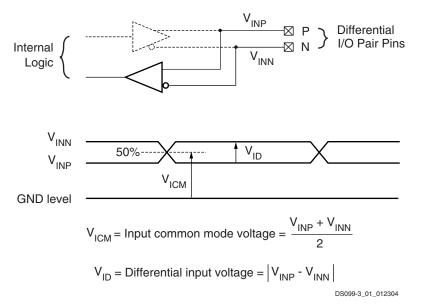

# Differential I/O Standards

Figure 69: Differential Input Voltages

| Table 82: Recommended C | Derating Conditions for  | r User I/Os Usina Di | ifferential Signal Standards  |

|-------------------------|--------------------------|----------------------|-------------------------------|

|                         | peruting contaitions for |                      | incremation orginal otamaarao |

| IOSTANDARD               | V <sub>CCO</sub> for Drivers <sup>(1)</sup> |             |         | V <sub>ID</sub> |          |          | V <sub>ICM</sub> |         |         |

|--------------------------|---------------------------------------------|-------------|---------|-----------------|----------|----------|------------------|---------|---------|

| Attribute                | Min (V)                                     | Nom (V)     | Max (V) | Min (mV)        | Nom (mV) | Max (mV) | Min (V)          | Nom (V) | Max (V) |

| LVDS_25                  | 2.375                                       | 2.50        | 2.625   | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| BLVDS_25                 | 2.375                                       | 2.50        | 2.625   | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| MINI_LVDS_25             | 2.375                                       | 2.50        | 2.625   | 200             | -        | 600      | 0.30             | -       | 2.2     |

| LVPECL_25 <sup>(2)</sup> |                                             | Inputs Only |         | 100             | 800      | 1000     | 0.5              | 1.2     | 2.0     |

| RSDS_25                  | 2.375                                       | 2.50        | 2.625   | 100             | 200      | -        | 0.3              | 1.20    | 1.4     |

| DIFF_HSTL_I_18           | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_HSTL_III_18         | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_SSTL18_I            | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.7              | -       | 1.1     |

| DIFF_SSTL2_I             | 2.3                                         | 2.5         | 2.7     | 100             | -        | -        | 1.0              | -       | 1.5     |

#### Notes:

1. The  $V_{CCO}$  rails supply only differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

#### Table 107: Switching Characteristics for the DFS

|                                      |                                                                                                                                                                                     |                                                                                                                     |                                  | Speed Grade                |                                      |                            |                                      |         |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|--------------------------------------|----------------------------|--------------------------------------|---------|

| Symbol                               | Description                                                                                                                                                                         | I                                                                                                                   | Device                           | -5                         |                                      | -4                         |                                      | Units   |

|                                      |                                                                                                                                                                                     |                                                                                                                     |                                  | Min                        | Max                                  | Min                        | Max                                  |         |

| <b>Output Frequency Range</b>        | S                                                                                                                                                                                   |                                                                                                                     |                                  |                            |                                      |                            |                                      | <u></u> |

| CLKOUT_FREQ_FX_LF                    | Frequency for the CLKFX and<br>CLKFX180 outputs, low<br>frequencies                                                                                                                 | Stepping 0                                                                                                          | XC3S100E<br>XC3S250E<br>XC3S500E | N/A                        | N/A                                  | 5                          | 90                                   | MHz     |

| CLKOUT_FREQ_FX_HF                    | Frequency for the CLKFX and<br>CLKFX180 outputs, high<br>frequencies                                                                                                                | -                                                                                                                   | XC3S1600E                        |                            |                                      | 220                        | 307                                  | MHz     |

| CLKOUT_FREQ_FX                       | Frequency for the CLKFX and                                                                                                                                                         | Stepping 0                                                                                                          | XC3S1200E                        |                            |                                      | 5                          | 307                                  | MHz     |

|                                      | CLKFX180 outputs                                                                                                                                                                    | Stepping 1                                                                                                          | All                              | 5                          | 333                                  |                            | 311                                  | MHz     |

| Output Clock Jitter <sup>(2,3)</sup> |                                                                                                                                                                                     |                                                                                                                     |                                  | r                          |                                      |                            |                                      |         |

| CLKOUT_PER_JITT_FX                   | Period jitter at the CLKFX and                                                                                                                                                      |                                                                                                                     | All                              | Тур                        | Max                                  | Тур                        | Max                                  |         |

|                                      | CLKFX180 outputs.                                                                                                                                                                   | CLKIN ≤ 20 MHz                                                                                                      | -                                |                            | Note 6                               |                            |                                      | ps      |

|                                      |                                                                                                                                                                                     | CLKIN > 20 MHz                                                                                                      | -                                | ±[1% of<br>CLKFX<br>period | CLKFX<br>period                      | ±[1% of<br>CLKFX<br>period | CLKFX<br>period                      | ps      |

|                                      |                                                                                                                                                                                     |                                                                                                                     |                                  | + 100]                     | + 200]                               | + 100]                     | + 200]                               |         |

| Duty Cycle <sup>(4,5)</sup>          |                                                                                                                                                                                     |                                                                                                                     | i                                |                            | ±[1% of                              |                            |                                      |         |

| CLKOUT_DUTY_CYCLE_FX                 |                                                                                                                                                                                     | Duty cycle precision for the CLKFX and CLKFX180 outputs, including the BUFGMUX and clock tree duty-cycle distortion |                                  |                            |                                      | -                          | ±[1% of<br>CLKFX<br>period<br>+ 400] | ps      |

| Phase Alignment <sup>(5)</sup>       |                                                                                                                                                                                     |                                                                                                                     |                                  |                            | I                                    |                            |                                      |         |

| CLKOUT_PHASE_FX                      | Phase offset between the DFS CL<br>DLL CLK0 output when both the<br>used                                                                                                            |                                                                                                                     | All                              | -                          | ±200                                 | -                          | ±200                                 | ps      |

| CLKOUT_PHASE_FX180                   |                                                                                                                                                                                     | Phase offset between the DFS CLKFX180 output and the DLL CLK0 output when both the DFS and DLL are                  |                                  |                            | ±[1% of<br>CLKFX<br>period<br>+ 300] | -                          | ±[1% of<br>CLKFX<br>period<br>+ 300] | ps      |

| Lock Time                            |                                                                                                                                                                                     |                                                                                                                     |                                  | 1                          | 1                                    |                            |                                      |         |

| LOCK_FX <sup>(2)</sup>               | The time from deassertion at the DCM's Reset input to the rising transition at its LOCKED output.                                                                                   | $5 \text{ MHz} \leq \text{F}_{\text{CLKIN}} \\ \leq 15 \text{ MHz}$                                                 | All                              | -                          | 5                                    | -                          | 5                                    | ms      |

|                                      | The DFS asserts LOCKED butput.<br>The DFS asserts LOCKED when<br>the CLKFX and CLKFX180<br>signals are valid. If using both<br>the DLL and the DFS, use the<br>longer locking time. | F <sub>CLKIN</sub> > 15 MHz                                                                                         |                                  | -                          | 450                                  | -                          | 450                                  | μs      |

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 106.

- 2. For optimal jitter tolerance and faster lock time, use the CLKIN\_PERIOD attribute.

- Maximum output jitter is characterized within a reasonable noise environment (150 ps input period jitter, 40 SSOs and 25% CLB switching). Output jitter strongly depends on the environment, including the number of SSOs, the output drive strength, CLB utilization, CLB switching activities, switching frequency, power supply and PCB design. The actual maximum output jitter depends on the system application.

- 4. The CLKFX and CLKFX180 outputs always have an approximate 50% duty cycle.

- Some duty-cycle and alignment specifications include 1% of the CLKFX output period or 0.01 UI.

*Example:* The data sheet specifies a maximum jitter of ±[1% of CLKFX period + 300]. Assume the CLKFX output frequency is 100 MHz. The equivalent CLKFX period is 10 ns and 1% of 10 ns is 0.1 ns or 100 ps. According to the data sheet, the maximum jitter is ±[100 ps + 300 ps] = ±400 ps.

- 6. Use the Spartan-3A Jitter Calculator (www.xilinx.com/support/documentation/data\_sheets/s3a\_jitter\_calc.zip) to estimate DFS output jitter. Use the Clocking Wizard to determine jitter for a specific design.

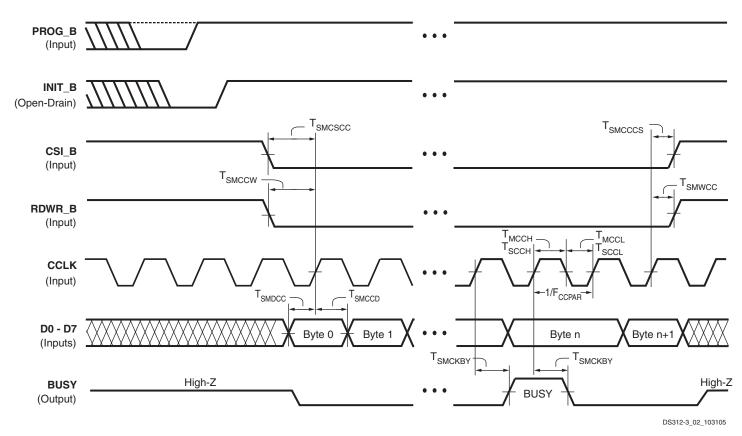

### **Slave Parallel Mode Timing**

#### Notes:

1. It is possible to abort configuration by pulling CSI\_B Low in a given CCLK cycle, then switching RDWR\_B Low or High in any subsequent cycle for which CSI\_B remains Low. The RDWR\_B pin asynchronously controls the driver impedance of the D0 - D7 bus. When RDWR\_B switches High, be careful to avoid contention on the D0 - D7 bus.

#### Figure 75: Waveforms for Slave Parallel Configuration

| Table 117: Timing for the Slave Parallel Configuration Mode | Table | 117: | Timing for the | e Slave | Parallel | Configuration | n Mode |

|-------------------------------------------------------------|-------|------|----------------|---------|----------|---------------|--------|

|-------------------------------------------------------------|-------|------|----------------|---------|----------|---------------|--------|

| Description                                                                                                  | All Spee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Unite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                  | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| put Times                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The time from the rising transition on the CCLK pin to a signal transition at the BUSY pin                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The time from the setup of data at the D0-D7 pins to the active edge the CCLK pin                            | 11.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Setup time on the CSI_B pin before the active edge of the CCLK pin                                           | 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Setup time on the RDWR_B pin before active edge of the CCLK pin                                              | 23.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The time from the active edge of the CCLK pin to the point when data is last held at the D0-D7 pins          | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |