# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 1164                                                          |

| Number of Logic Elements/Cells | 10476                                                         |

| Total RAM Bits                 | 368640                                                        |

| Number of I/O                  | 66                                                            |

| Number of Gates                | 500000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 100-TQFP                                                      |

| Supplier Device Package        | 100-VQFP (14x14)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s500e-4vqg100c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

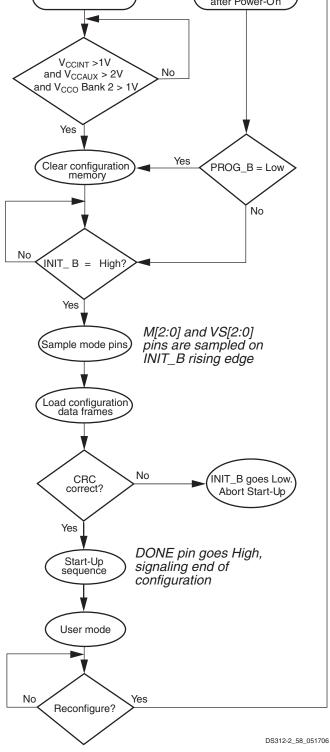

# Configuration

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

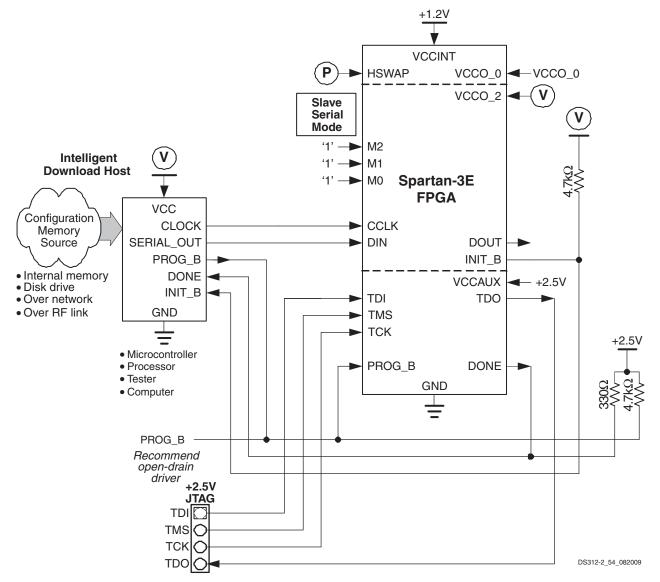

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

# I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, <u>66 MHz</u>

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

| Package                | VQ1<br>VQG                      |                  | CP <sup>.</sup><br>CPG | 132<br>132       |                    | 144<br>6144      | PQ:<br>PQC         |                  |                    | 256<br>1256      |                    | 320<br>3320       |                    | 400<br>6400        | FG4<br>FGG         |                    |

|------------------------|---------------------------------|------------------|------------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|

| Footprint<br>Size (mm) | 16 x                            | 16               | 8 :                    | x 8              | 22 >               | c 22             | 30.5 >             | c 30.5           | 17 ג               | k 17             | 19 >               | c 19              | 21 >               | k 21               | <b>23</b> x        | x 23               |

| Device                 | User                            | Diff             | User                   | Diff             | User               | Diff             | User               | Diff             | User               | Diff             | User               | Diff              | User               | Diff               | User               | Diff               |

| XC3S100E               | <b>66<sup>(2)</sup></b><br>9(7) | <b>30</b><br>(2) | <b>83</b><br>(11)      | <b>35</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | -                  | -                | -                  | -                | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S250E               | <b>66</b><br>(7)                | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>172</b><br>(40) | <b>68</b><br>(8) | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S500E               | <b>66<sup>(3)</sup></b><br>(7)  | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | -                  | -                | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>190</b><br>(41) | <b>77</b><br>(8) | <b>232</b><br>(56) | <b>92</b><br>(12) | -                  | -                  | -                  | -                  |

| XC3S1200E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | <b>190</b><br>(40) | <b>77</b><br>(8) | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | -                  | -                  |

| XC3S1600E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | -                  | -                | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | <b>376</b><br>(82) | <b>156</b><br>(21) |

## Table 2: Available User I/Os and Differential (Diff) I/O Pairs

#### Notes:

1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

3. The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical and general references to the VQ100 will apply to the XC3S500E.

#### Notes:

- 1. Options to invert signal polarity as well as other options that enable lines for various functions are not shown.

- 2. The index i can be 6, 7, or 8, depending on the slice. The upper SLICEL has an F8MUX, and the upper SLICEM has an F7MUX. The lower SLICEL and SLICEM both have an F6MUX.

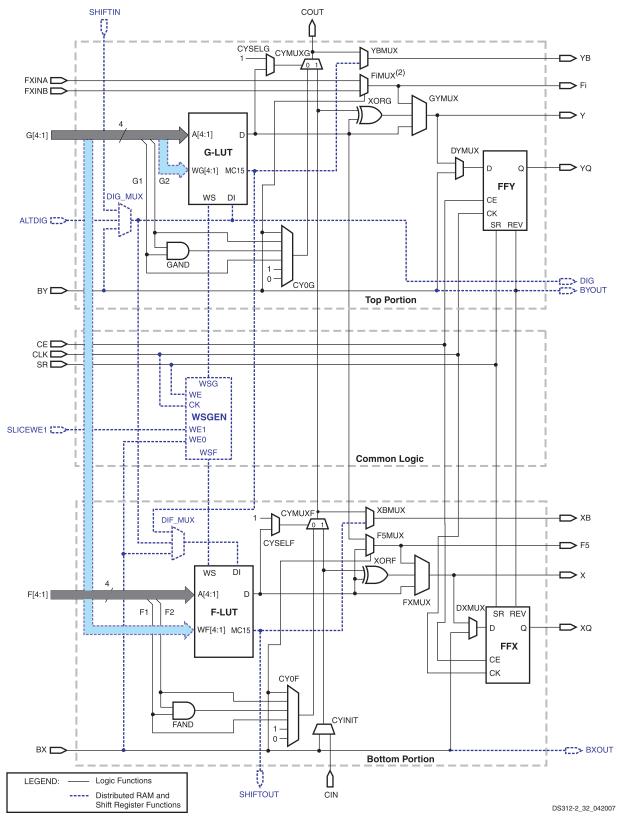

#### Figure 15: Simplified Diagram of the Left-Hand SLICEM

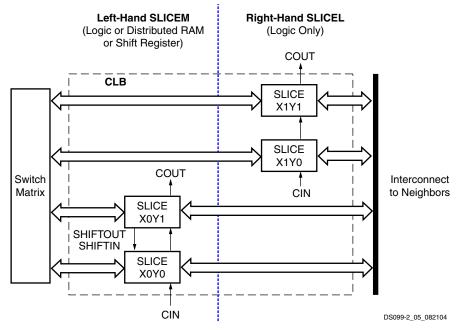

Figure 16: Arrangement of Slices within the CLB

### **Slice Location Designations**

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

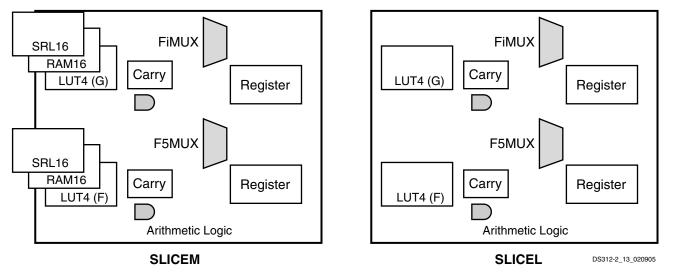

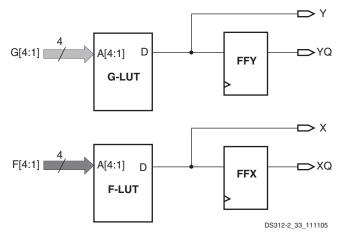

## **Slice Overview**

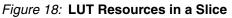

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

# Wide Multiplexers

For additional information, refer to the "Using Dedicated Multiplexers" chapter in UG331.

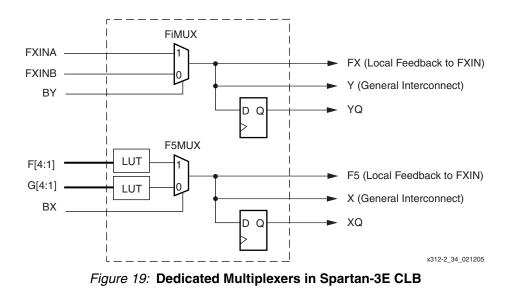

Wide-function multiplexers effectively combine LUTs in order to permit more complex logic operations. Each slice has two of these multiplexers with F5MUX in the bottom portion of the slice and FiMUX in the top portion. The F5MUX multiplexes the two LUTs in a slice. The FiMUX multiplexes two CLB inputs which connect directly to the F5MUX and FiMUX results from the same slice or from other slices. See Figure 19.

Depending on the slice, FiMUX takes on the name F6MUX, F7MUX, or F8MUX. The designation indicates the number of inputs possible without restriction on the function. For example, an F7MUX can generate any function of seven inputs. Figure 20 shows the names of the multiplexers in each position in the Spartan-3E CLB. The figure also includes the direct connections within the CLB, along with the F7MUX connection to the CLB below.

Each mux can create logic functions of more inputs than indicated by its name. The F5MUX, for example, can generate any function of five inputs, with four inputs duplicated to two LUTs and the fifth input controlling the mux. Because each LUT can implement independent 2:1 muxes, the F5MUX can combine them to create a 4:1 mux, which is a six-input function. If the two LUTs have completely independent sets of inputs, some functions of all nine inputs can be implemented. Table 11 shows the connections for each multiplexer and the number of inputs possible for different types of functions.

## Table 23: Block RAM Port Signals

| Signal<br>Description    | Port A<br>Signal<br>Name | Port B<br>Signal<br>Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------|--------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus              | ADDRA                    | ADDRB                    | Input     | The Address Bus selects a memory location for read or write operations.<br>The width (w) of the port's associated data path determines the number of<br>available address lines (r), as per Table 22.                                                                                                                                                                                                                                                                                                                                          |

|                          |                          |                          |           | Whenever a port is enabled (ENA or ENB = High), address transitions must<br>meet the data sheet setup and hold times with respect to the port clock<br>(CLKA or CLKB), as shown in Table 103, page 138. This requirement must<br>be met even if the RAM read output is of no interest.                                                                                                                                                                                                                                                         |

| Data Input Bus           | DIA                      | DIB                      | Input     | Data at the DI input bus is written to the RAM location specified by the address input bus (ADDR) during the active edge of the CLK input, when the clock enable (EN) and write enable (WE) inputs are active.                                                                                                                                                                                                                                                                                                                                 |

|                          |                          |                          |           | It is possible to configure a port's DI input bus width (w-p) based on Table 22. This selection applies to both the DI and DO paths of a given port.                                                                                                                                                                                                                                                                                                                                                                                           |

| Parity Data Input(s)     | DIPA                     | DIPB                     | Input     | Parity inputs represent additional bits included in the data input path.<br>Although referred to herein as "parity" bits, the parity inputs and outputs<br>have no special functionality for generating or checking parity and can be<br>used as additional data bits. The number of parity bits 'p' included in the DI<br>(same as for the DO bus) depends on a port's total data path width (w). See<br>Table 22.                                                                                                                            |

| Data Output Bus          | DOA                      | DOB                      | Output    | Data is written to the DO output bus from the RAM location specified by the address input bus, ADDR. See the DI signal description for DO port width configurations.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                          |                          |           | Basic data access occurs on the active edge of the CLK when WE is<br>inactive and EN is active. The DO outputs mirror the data stored in the<br>address ADDR memory location. Data access with WE active if the<br>WRITE_MODE attribute is set to the value: WRITE_FIRST, which<br>accesses data after the write takes place. READ_FIRST accesses data<br>before the write occurs. A third attribute, NO_CHANGE, latches the DO<br>outputs upon the assertion of WE. See Block RAM Data Operations for<br>details on the WRITE_MODE attribute. |

| Parity Data<br>Output(s) | DOPA                     | DOPB                     | Output    | Parity outputs represent additional bits included in the data input path. The number of parity bits 'p' included in the DI bus (same as for the DO bus) depends on a port's total data path width (w). See the DIP signal description for configuration details.                                                                                                                                                                                                                                                                               |

| Write Enable             | WEA                      | WEB                      | Input     | When asserted together with EN, this input enables the writing of data to the RAM. When WE is inactive with EN asserted, read operations are still possible. In this case, a latch passes data from the addressed memory location to the DO outputs.                                                                                                                                                                                                                                                                                           |

| Clock Enable             | ENA                      | ENB                      | Input     | When asserted, this input enables the CLK signal to perform read and write operations to the block RAM. When inactive, the block RAM does not perform any read or write operations.                                                                                                                                                                                                                                                                                                                                                            |

| Set/Reset                | SSRA                     | SSRB                     | Input     | When asserted, this pin forces the DO output latch to the value of the SRVAL attribute. It is synchronized to the CLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Clock                    | CLKA                     | CLKB                     | Input     | This input accepts the clock signal to which read and write operations are synchronized. All associated port inputs are required to meet setup times with respect to the clock signal's active edge. The data output bus responds after a clock-to-out delay referenced to the clock signal's active edge.                                                                                                                                                                                                                                     |

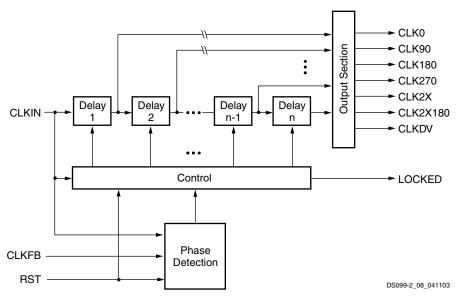

# Delay-Locked Loop (DLL)

The most basic function of the DLL component is to eliminate clock skew. The main signal path of the DLL consists of an input stage, followed by a series of discrete delay elements or *steps*, which in turn leads to an output stage. This path together with logic for phase detection and control forms a system complete with feedback as shown in Figure 41. In Spartan-3E FPGAs, the DLL is implemented using a counter-based delay line. The DLL component has two clock inputs, CLKIN and CLKFB, as well as seven clock outputs, CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV as described in Table 28. The clock outputs drive simultaneously. Signals that initialize and report the state of the DLL are discussed in Status Logic.

Figure 41: Simplified Functional Diagram of DLL

#### Table 28: DLL Signals

| Signal   | Direction | Description                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | Input     | Receives the incoming clock signal. See Table 30, Table 31, and Table 32 for optimal external inputs to a DCM.             |

| CLKFB    | Input     | Accepts either CLK0 or CLK2X as the feedback signal. (Set the CLK_FEEDBACK attribute accordingly).                         |

| CLK0     | Output    | Generates a clock signal with the same frequency and phase as CLKIN.                                                       |

| CLK90    | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 90°.                                           |

| CLK180   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 180°.                                          |

| CLK270   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 270°.                                          |

| CLK2X    | Output    | Generates a clock signal with the same phase as CLKIN, and twice the frequency.                                            |

| CLK2X180 | Output    | Generates a clock signal with twice the frequency of CLKIN, and phase-shifted 180° with respect to CLK2X.                  |

| CLKDV    | Output    | Divides the CLKIN frequency by CLKDV_DIVIDE value to generate lower frequency clock signal that is phase-aligned to CLKIN. |

The clock signal supplied to the CLKIN input serves as a reference waveform. The DLL seeks to align the rising-edge of feedback signal at the CLKFB input with the rising-edge of CLKIN input. When eliminating clock skew, the common approach to using the DLL is as follows: The CLK0 signal is passed through the clock distribution network that feeds all the registers it synchronizes. These registers are either

internal or external to the FPGA. After passing through the clock distribution network, the clock signal returns to the DLL via a feedback line called CLKFB. The control block inside the DLL measures the phase error between CLKFB and CLKIN. This phase error is a measure of the clock skew that the clock distribution network introduces. The control block activates the appropriate number of delay steps to

# **Daisy-Chaining**

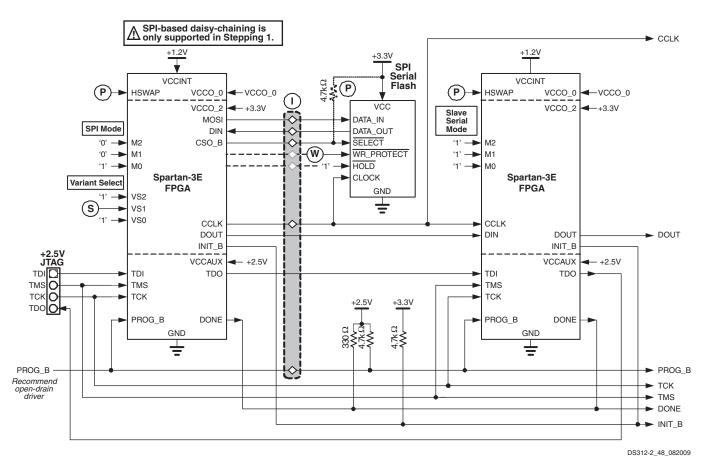

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 57. Daisy-chaining from a single SPI serial Flash PROM is supported in Stepping 1 devices. It is not supported in Stepping 0 devices. Use SPI Flash mode (M[2:0] = <0:0:1>) for the FPGA connected to the Platform Flash PROM and Slave Serial mode (M[2:0] = <1:1:1>) for all other FPGAs in the daisy-chain. After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the SPI Flash PROM, the master device uses its DOUT output pin to supply data to the next device in the daisy-chain, on the falling CCLK edge.

#### Design Note

SPI mode daisy chains are supported only in Stepping 1 silicon versions.

Figure 57: Daisy-Chaining from SPI Flash Mode (Stepping 1)

### **Programming Support**

For successful daisy-chaining, the *DONE\_cycle* configuration option must be set to cycle 5 or sooner. The default cycle is 4. See Table 69 and the Start-Up section for additional information.

U In production applications, the SPI Flash PROM is usually pre-programmed before it is mounted on the printed circuit board. The <u>Xilinx ISE development software</u> produces industry-standard programming files that can be used with third-party gang programmers. Consult your specific SPI Flash vendor for recommended production programming solutions. In-system programming support is available from some third-party PROM programmers using a socket adapter with attached wires. To gain access to the SPI Flash signals, drive the FPGA's PROG\_B input Low with an open-drain driver. This action places all FPGA I/O pins, including those attached to the SPI Flash, in high-impedance (Hi-Z). If the HSWAP input is Low, the I/Os have pull-up resistors to the V<sub>CCO</sub> input on their respective I/O bank. The external programming hardware then has direct access to the SPI Flash pins. The programming access points are highlighted in the gray box in Figure 53, Figure 54, and Figure 57.

Beginning with the Xilinx ISE 8.2i software release, the iMPACT programming utility provides direct, in-system prototype programming support for STMicro M25P-series

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | During Configuration                               | After Configuration                                                                                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                            | Low indicates that the FPGA is not yet configured. | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA is<br>successfully configured.                                                              |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer,<br>forces the FPGA to restart its<br>configuration process by clearing<br>configuration memory and resetting<br>the DONE and INIT_B pins once<br>PROG_B returns High.<br>Recommend external 4.7 k $\Omega$<br>pull-up resistor to 2.5V. Internal<br>pull-up value may be weaker (see<br>Table 78). If driving externally with a<br>3.3V output, use an open-drain or<br>open-collector driver or use a<br>current limiting series resistor. | Must be High to allow configuration to start.      | Drive PROG_B Low and<br>release to reprogram<br>FPGA. Hold PROG_B to<br>force FPGA I/O pins into<br>Hi-Z, allowing direct<br>programming access to<br>Flash PROM pins. |

#### Table 59: Byte-Wide Peripheral Interface (BPI) Connections (Cont'd)

### **Voltage Compatibility**

V The FPGA's parallel Flash interface signals are within I/O Banks 1 and 2. The majority of parallel Flash PROMs use a single 3.3V supply voltage. Consequently, in most cases, the FPGA's VCCO\_1 and VCCO\_2 supply voltages must also be 3.3V to match the parallel Flash PROM. There are some 1.8V parallel Flash PROMs available and the FPGA interfaces with these devices if the VCCO\_1 and VCCO\_2 supplies are also 1.8V.

# Power-On Precautions if PROM Supply is Last in Sequence

Like SPI Flash PROMs, parallel Flash PROMs typically require some amount of internal initialization time when the supply voltage reaches its minimum value.

The PROM supply voltage also connects to the FPGA's VCCO\_2 supply input. In many systems, the PROM supply feeding the FPGA's VCCO\_2 input is valid before the FPGA's other V<sub>CCINT</sub> and V<sub>CCAUX</sub> supplies, and consequently, there is no issue. However, if the PROM supply is last in the sequence, a potential race occurs between the FPGA and the parallel Flash PROM. See

Power-On Precautions if 3.3V Supply is Last in Sequence for a similar description of the issue for SPI Flash PROMs.

#### **Supported Parallel NOR Flash PROM Densities**

Table 60 indicates the smallest usable parallel Flash PROMto program a single Spartan-3E FPGA. Parallel Flashdensity is specified in bits but addressed as bytes. TheFPGA presents up to 24 address lines during configurationbut not all are required for single FPGA applications.Table 60 shows the minimum required number of addresslines between the FPGA and parallel Flash PROM. Theactual number of address line required depends on thedensity of the attached parallel Flash PROM.

A multiple-FPGA daisy-chained application requires a parallel Flash PROM large enough to contain the sum of the FPGA file sizes. An application can also use a larger-density parallel Flash PROM to hold additional data beyond just FPGA configuration data. For example, the parallel Flash PROM can also contain the application code for a MicroBlaze RISC processor core implemented within the Spartan-3E FPGA. After configuration, the MicroBlaze processor can execute directly from external Flash or can copy the code to other, faster system memory before executing the code.

#### Table 60: Number of Bits to Program a Spartan-3E FPGA and Smallest Parallel Flash PROM

| Spartan-3E FPGA | Uncompressed<br>File Sizes (bits) | Smallest Usable<br>Parallel Flash PROM | Minimum Required<br>Address Lines |  |  |

|-----------------|-----------------------------------|----------------------------------------|-----------------------------------|--|--|

| XC3S100E        | 581,344                           | 1 Mbit                                 | A[16:0]                           |  |  |

| XC3S250E        | 1,353,728                         | 2 Mbit                                 | A[17:0]                           |  |  |

| XC3S500E        | 2,270,208                         | 4 Mbit                                 | A[18:0]                           |  |  |

| XC3S1200E       | 3,841,184                         | 4 Mbit                                 | A[18:0]                           |  |  |

| XC3S1600E       | 5,969,696                         | 8 Mbit                                 | A[19:0]                           |  |  |

support byte-wide data. However, after configuration, the FPGA supports either x8 or x16 modes. In x16 mode, up to eight additional user I/O pins are required for the upper data bits, D[15:8].

Connecting a Spartan-3E FPGA to a x8/x16 Flash PROM is simple, but does require a precaution. Various Flash PROM vendors use slightly different interfaces to support both x8 and x16 modes. Some vendors (Intel, Micron, some STMicroelectronics devices) use a straightforward interface with pin naming that matches the FPGA connections. However, the PROM's A0 pin is wasted in x16 applications and a separate FPGA user-I/O pin is required for the D15 data line. Fortunately, the FPGA A0 pin is still available as a user I/O after configuration, even though it connects to the Flash PROM. Other vendors (AMD, Atmel, Silicon Storage Technology, some STMicroelectronics devices) use a pin-efficient interface but change the function of one pin, called IO15/A-1, depending if the PROM is in x8 or x16 mode. In x8 mode, BYTE# = 0, this pin is the least-significant address line. The A0 address line selects the halfword location. The A-1 address line selects the byte location. When in x16 mode, BYTE# = 1, the IO15/A-1 pin becomes the most-significant data bit, D15 because byte addressing is not required in this mode. Check to see if the Flash PROM has a pin named "IO15/A-1" or "DQ15/A-1". If so, be careful to connect x8/x16 Flash PROMs correctly, as shown in Table 63. Also, remember that the D[14:8] data connections require FPGA user I/O pins but that the D15 data is already connected for the FPGA's A0 pin.

| FPGA Pin | Connection to Flash PROM with<br>IO15/A-1 Pin                                                       | x8 Flash PROM Interface After<br>FPGA Configuration                       | x16 Flash PROM Interface After<br>FPGA Configuration |  |  |

|----------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|--|--|

| LDC2     | BYTE#                                                                                               | Drive LDC2 Low or leave<br>unconnected and tie PROM BYTE#<br>input to GND | Drive LCD2 High                                      |  |  |

| LDC1     | OE#                                                                                                 | Active-Low Flash PROM<br>output-enable control                            | Active-Low Flash PROM<br>output-enable control       |  |  |

| LDC0     | CS#                                                                                                 | Active-Low Flash PROM chip-select control                                 | Active-Low Flash PROM chip-select<br>control         |  |  |

| HDC      | WE#                                                                                                 | Flash PROM write-enable control                                           | Flash PROM write-enable control                      |  |  |

| A[23:1]  | A[n:0]                                                                                              | A[n:0]                                                                    | A[n:0]                                               |  |  |

| A0       | IO15/A-1                                                                                            | IO15/A-1 is the least-significant address input                           | IO15/A-1 is the most-significant data line, IO15     |  |  |

| D[7:0]   | IO[7:0]                                                                                             | IO[7:0]                                                                   | IO[7:0]                                              |  |  |

| User I/O | Upper data lines IO[14:8] not required<br>unless used as x16 Flash interface after<br>configuration | Upper data lines IO[14:8] not required                                    | IO[14:8]                                             |  |  |

Table 63: FPGA Connections to Flash PROM with IO15/A-1 Pin

Some x8/x16 Flash PROMs have a long setup time requirement on the BYTE# signal. For the FPGA to configure correctly, the PROM must be in x8 mode with BYTE# = 0 at power-on or when the FPGA's PROG\_B pin is pulsed Low. If required, extend the BYTE# setup time for a 3.3V PROM using an external 680  $\Omega$  pull-down resistor on the FPGA's LDC2 pin or by delaying assertion of the CSI\_B select input to the FPGA.

# **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 59. Use BPI mode (M[2:0] = <0:1:0> or <0:1:1>) for the FPGA connected to the parallel NOR Flash PROM and Slave Parallel mode (M[2:0] = <1:1:0>) for all downstream FPGAs in the daisy-chain. If there are more than two FPGAs in the chain, then last FPGA in the chain can be from any Xilinx FPGA family. However, all intermediate FPGAs located in the

chain between the first and last FPGAs must from either the Spartan-3E or Virtex®-5 FPGA families.

After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the parallel Flash PROM, the master device continues generating addresses to the Flash PROM and asserts its CSO\_B output Low, enabling the next FPGA in the daisy-chain. The next FPGA then receives parallel configuration data from the Flash PROM. The master FPGA's CCLK output synchronizes data capture.

If HSWAP = 1, an external  $4.7k\Omega$  pull-up resistor must be added on the CSO\_B pin. If HSWAP = 0, no external pull-up is necessary.

### Design Note

BPI mode daisy chain software support is available starting in ISE 8.2i.

http://www.xilinx.com/support/answers/23061.htm

Figure 63: Slave Serial Configuration

The mode select pins, M[2:0], are sampled when the FPGA's INIT\_B output goes High and must be at defined logic levels during this time. After configuration, when the FPGA's DONE output goes High, the mode pins are available as full-featured user-I/O pins.

P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins or High to disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

### Voltage Compatibility

W Most Slave Serial interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 3.3V, 2.5V, or 1.8V to match the requirements of the external host, ideally 2.5V. Using 3.3V or 1.8V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 64. Use Slave Serial mode (M[2:0] = <1:1:>) for all FPGAs in the daisy-chain. After the lead FPGA is filled with its configuration data, the lead

# **EXILINX**.

# General DC Characteristics for I/O Pins

#### Table 78: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

| Symbol                          | Description                                                                                                                | Test Conditions                                                                                                                                                       | Min   | Тур | Мах   | Units |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| ۱ <sub>L</sub> (3)              | Leakage current at User I/O, Input-only,<br>Dual-Purpose, and Dedicated pins                                               | Driver is in a high-impedance state, V <sub>IN</sub> = 0V or V <sub>CCO</sub> max, sample-tested                                                                      | -10   | _   | +10   | μA    |

| I <sub>RPU</sub> (2)            | Current through pull-up resistor at User I/O,                                                                              | $V_{IN} = 0V, V_{CCO} = 3.3V$                                                                                                                                         | -0.36 | _   | -1.24 | mA    |

|                                 | Dual-Purpose, Input-only, and Dedicated pins                                                                               | $V_{IN} = 0V, V_{CCO} = 2.5V$                                                                                                                                         | -0.22 | -   | -0.80 | mA    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.8V$                                                                                                                                         | -0.10 | -   | -0.42 | mA    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.5V$                                                                                                                                         | -0.06 | -   | -0.27 | mA    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.2V$                                                                                                                                         | -0.04 | -   | -0.22 | mA    |

| R <sub>PU</sub> (2)             | Equivalent pull-up resistor value at User                                                                                  | $V_{IN} = 0V, V_{CCO} = 3.0V \text{ to } 3.465V$                                                                                                                      | 2.4   | _   | 10.8  | kΩ    |

|                                 | I/O, Dual-Purpose, Input-only, and<br>Dedicated pins (based on I <sub>RPU</sub> per Note 2)                                | $V_{IN} = 0V, V_{CCO} = 2.3V \text{ to } 2.7V$                                                                                                                        | 2.7   | -   | 11.8  | kΩ    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.7V \text{ to } 1.9V$                                                                                                                        | 4.3   | -   | 20.2  | kΩ    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.4V \text{ to } 1.6V$                                                                                                                        | 5.0   | -   | 25.9  | kΩ    |

|                                 |                                                                                                                            | $V_{IN} = 0V, V_{CCO} = 1.14V$ to 1.26V                                                                                                                               | 5.5   | _   | 32.0  | kΩ    |

| I <sub>RPD</sub> <sup>(2)</sup> | Current through pull-down resistor at User<br>I/O, Dual-Purpose, Input-only, and<br>Dedicated pins                         | V <sub>IN</sub> = V <sub>CCO</sub>                                                                                                                                    | 0.10  | _   | 0.75  | mA    |

| R <sub>PD</sub> <sup>(2)</sup>  | Equivalent pull-down resistor value at User                                                                                | $V_{IN} = V_{CCO} = 3.0V \text{ to } 3.465V$                                                                                                                          | 4.0   | _   | 34.5  | kΩ    |

|                                 | I/O, Dual-Purpose, Input-only, and<br>Dedicated pins (based on I <sub>RPD</sub> per Note 2)                                | $V_{IN} = V_{CCO} = 2.3V$ to 2.7V                                                                                                                                     | 3.0   | -   | 27.0  | kΩ    |

|                                 | nor in the second se            | $V_{IN} = V_{CCO} = 1.7V$ to 1.9V                                                                                                                                     | 2.3   | _   | 19.0  | kΩ    |

|                                 |                                                                                                                            | $V_{IN} = V_{CCO} = 1.4V$ to 1.6V                                                                                                                                     | 1.8   | _   | 16.0  | kΩ    |

|                                 |                                                                                                                            | $V_{IN} = V_{CCO} = 1.14V$ to 1.26V                                                                                                                                   | 1.5   | _   | 12.6  | kΩ    |

| I <sub>REF</sub>                | V <sub>REF</sub> current per pin                                                                                           | All V <sub>CCO</sub> levels                                                                                                                                           | -10   | _   | +10   | μA    |

| C <sub>IN</sub>                 | Input capacitance                                                                                                          | _                                                                                                                                                                     | -     | -   | 10    | pF    |

| R <sub>DT</sub>                 | Resistance of optional differential termination circuit within a differential I/O pair. Not available on Input-only pairs. | $\begin{array}{c} V_{OCM} \mbox{ Min} \leq V_{ICM} \leq V_{OCM} \mbox{ Max} \\ V_{OD} \mbox{ Min} \leq V_{ID} \leq V_{OD} \mbox{ Max} \\ V_{CCO} = 2.5 V \end{array}$ | _     | 120 | _     | Ω     |

Notes:

The numbers in this table are based on the conditions set forth in Table 77. 1.

2.

This parameter is based on characterization. The pull-up resistance  $R_{PU} = V_{CCO} / I_{RPU}$ . The pull-down resistance  $R_{PD} = V_{IN} / I_{RPD}$ . For single-ended signals that are placed on a differential-capable I/O,  $V_{IN}$  of -0.2V to -0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*. З.

# I/O Timing

#### Table 86: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

|                    |                                                                                                                                                                          |                                                                                             |           | Speed              |                    |       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------|--------------------|--------------------|-------|

| Symbol             | Description                                                                                                                                                              | Conditions                                                                                  | Device    | -5                 | -4                 | Units |

|                    |                                                                                                                                                                          |                                                                                             |           | Max <sup>(2)</sup> | Max <sup>(2)</sup> |       |

| Clock-to-Outp      | out Times                                                                                                                                                                |                                                                                             |           |                    |                    |       |

| TICKOFDCM          | When reading from the Output Flip-Flop<br>(OFF), the time from the active transition<br>on the Global Clock pin to data appearing<br>at the Output pin. The DCM is used. | LVCMOS25 <sup>(3)</sup> , 12 mA<br>output drive, Fast slew<br>rate, with DCM <sup>(4)</sup> | XC3S100E  | 2.66               | 2.79               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S250E  | 3.00               | 3.45               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S500E  | 3.01               | 3.46               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S1200E | 3.01               | 3.46               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S1600E | 3.00               | 3.45               | ns    |

| T <sub>ICKOF</sub> | When reading from OFF, the time from the                                                                                                                                 | LVCMOS25 <sup>(3)</sup> , 12 mA                                                             | XC3S100E  | 5.60               | 5.92               | ns    |

|                    | active transition on the Global Clock pin to<br>data appearing at the Output pin. The                                                                                    | output drive, Fast slew<br>rate, without DCM                                                | XC3S250E  | 4.91               | 5.43               | ns    |

|                    | DCM is not used.                                                                                                                                                         |                                                                                             | XC3S500E  | 4.98               | 5.51               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S1200E | 5.36               | 5.94               | ns    |

|                    |                                                                                                                                                                          |                                                                                             | XC3S1600E | 5.45               | 6.05               | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

- 2. For minimums, use the values reported by the Xilinx timing analyzer.

- 3. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, *add* the appropriate Input adjustment from Table 91. If the latter is true, *add* the appropriate Output adjustment from Table 94.

- 4. DCM output jitter is included in all measurements.

## Table 105: Switching Characteristics for the DLL (Cont'd)

|                                |                                                                                                                                                   |                                                                                    |     |    | Speed                                | Grade |                                      |    |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|----|--------------------------------------|-------|--------------------------------------|----|

| Symbol                         | Description                                                                                                                                       | Description                                                                        |     |    | -5                                   |       | -4                                   |    |

|                                |                                                                                                                                                   |                                                                                    |     |    | Мах                                  | Min   | Max                                  | -  |

| Phase Alignment <sup>(4)</sup> |                                                                                                                                                   |                                                                                    |     |    |                                      |       |                                      |    |

| CLKIN_CLKFB_PHASE              | Phase offset between the CLK inputs                                                                                                               | Phase offset between the CLKIN and CLKFB inputs                                    |     | -  | ±200                                 | -     | ±200                                 | ps |

| CLKOUT_PHASE_DLL               | OUT_PHASE_DLL       Phase offset between DLL       CLK0 to CLK2X         outputs       (not CLK2X180)                                             |                                                                                    |     | -  | ±[1% of<br>CLKIN<br>period<br>+ 100] | -     | ±[1% of<br>CLKIN<br>period<br>+ 100] | ps |

|                                |                                                                                                                                                   | All others                                                                         |     | -  | ±[1% of<br>CLKIN<br>period<br>+ 200] | -     | ±[1% of<br>CLKIN<br>period<br>+ 200] | ps |

| Lock Time                      |                                                                                                                                                   |                                                                                    |     |    |                                      |       |                                      |    |

| LOCK_DLL <sup>(3)</sup>        | When using the DLL alone:<br>The time from deassertion at                                                                                         | $\begin{array}{l} 5 \text{ MHz} \leq F_{CLKIN} \\ \leq 15 \text{ MHz} \end{array}$ | All | -  | 5                                    | -     | 5                                    | ms |

|                                | the DCM's Reset input to the<br>rising transition at its<br>LOCKED output. When the<br>DCM is locked, the CLKIN and<br>CLKFB signals are in phase | F <sub>CLKIN</sub> > 15 MHz                                                        |     | -  | 600                                  | -     | 600                                  | μs |

| Delay Lines                    |                                                                                                                                                   |                                                                                    |     |    |                                      |       |                                      |    |

| DCM_DELAY_STEP                 | Finest delay resolution                                                                                                                           |                                                                                    | All | 20 | 40                                   | 20    | 40                                   | ps |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 104.

2. Indicates the maximum amount of output jitter that the DCM adds to the jitter on the CLKIN input.

3. For optimal jitter tolerance and faster lock time, use the CLKIN\_PERIOD attribute.

4. Some jitter and duty-cycle specifications include 1% of input clock period or 0.01 UI. Example: The data sheet specifies a maximum jitter of ±[1% of CLKIN period + 150]. Assume the CLKIN frequency is 100 MHz. The equivalent CLKIN period is 10 ns and 1% of 10 ns is 0.1 ns or 100 ps. According to the data sheet, the maximum jitter is ±[100 ps + 150 ps] = ±250 ps.

### Digital Frequency Synthesizer (DFS)

#### Table 106: Recommended Operating Conditions for the DFS

| Symbol             |                                                                   |                                  |                                 |       |                      |       |                      |     |

|--------------------|-------------------------------------------------------------------|----------------------------------|---------------------------------|-------|----------------------|-------|----------------------|-----|

|                    |                                                                   | Description                      | -                               | 5     | -                    | Units |                      |     |

|                    |                                                                   |                                  |                                 | Min   | Max                  | Min   | Max                  |     |

| Input Fre          | quency Ranges <sup>(2)</sup>                                      |                                  |                                 |       |                      |       |                      |     |

| F <sub>CLKIN</sub> | CLKIN_FREQ_FX                                                     | Frequency for the CLKIN input    |                                 | 0.200 | 333 <mark>(4)</mark> | 0.200 | 333 <mark>(4)</mark> | MHz |

| Input Clo          | ck Jitter Tolerance <sup>(3)</sup>                                |                                  |                                 |       |                      |       |                      |     |

| CLKIN_C            | YC_JITT_FX_LF                                                     | Cycle-to-cycle jitter at the     | $F_{CLKFX} \le 150 \text{ MHz}$ | -     | ±300                 | -     | ±300                 | ps  |

| CLKIN_C            | CLKIN_CYC_JITT_FX_HF CLKIN input, based on CLKFX output frequency |                                  | F <sub>CLKFX</sub> > 150 MHz    | -     | ±150                 | -     | ±150                 | ps  |

| CLKIN_P            | ER_JITT_FX                                                        | Period jitter at the CLKIN input |                                 | -     | ±1                   | -     | ±1                   | ns  |

#### Notes:

1. DFS specifications apply when either of the DFS outputs (CLKFX or CLKFX180) are used.

2. If both DFS and DLL outputs are used on the same DCM, follow the more restrictive CLKIN\_FREQ\_DLL specifications in Table 104.

3. CLKIN input jitter beyond these limits may cause the DCM to lose lock.

4. To support double the maximum effective FCLKIN limit, set the CLKIN\_DIVIDE\_BY\_2 attribute to TRUE. This attribute divides the incoming clock frequency by two as it enters the DCM.

# User I/Os by Bank

Table 132 indicates how the 66 available user-I/O pins are distributed between the four I/O banks on the VQ100 package.

#### Table 132: User I/Os Per Bank for XC3S100E, XC3S250E, and XC3S500E in the VQ100 Package

| Package<br>Edge | VO Bonk  | Maximum | All Possible I/O Pins by Type |       |      |                     |                    |  |  |

|-----------------|----------|---------|-------------------------------|-------|------|---------------------|--------------------|--|--|

|                 | I/O Bank | I/O     | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |  |  |

| Тор             | 0        | 15      | 5                             | 0     | 1    | 1                   | 8                  |  |  |

| Right           | 1        | 15      | 6                             | 0     | 0    | 1                   | 8                  |  |  |

| Bottom          | 2        | 19      | 0                             | 0     | 18   | 1                   | 0 <sup>(2)</sup>   |  |  |

| Left            | 3        | 17      | 5                             | 1     | 2    | 1                   | 8                  |  |  |

| TOTAL           |          | 66      | 16                            | 1     | 21   | 4                   | 24                 |  |  |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

## **Footprint Migration Differences**

The production XC3S100E, XC3S250E, and XC3S500E FPGAs have identical footprints in the VQ100 package. Designs can migrate between the devices without further consideration.

# CP132: 132-ball Chip-scale Package

The XC3S100E, XC3S250E and the XC3S500E FPGAs are available in the 132-ball chip-scale package, CP132. The devices share a common footprint for this package as shown in Table 133 and Figure 81.

Table 133 lists all the CP132 package pins. They are sorted by bank number and then by pin name. Pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

Physically, the D14 and K2 balls on the XC3S100E and XC3S250E FPGAs are not connected but should be connected to VCCINT to maintain density migration compatibility.

Similarly, the A4, C1, and P10 balls on the XC3S100E FPGA are not connected but should be connected to GND to maintain density migration compatibility.

The XC3S100E FPGA has four fewer BPI address pins, A[19:0], whereas the XC3S250E and XC3S500E support A[23:0].

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx web site at:

http://www.xilinx.com/support/documentation/data\_sheets/s3e\_pin.zip

# **Pinout Table**

Table 133:

CP132 Package Pinout

| Bank | XC3S100E<br>Pin Name | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                     |

|------|----------------------|----------------------------------|------------|------------------------------------------|

| 0    | IO_L01N_0            | IO_L01N_0                        | C12        | I/O                                      |

| 0    | IO_L01P_0            | IO_L01P_0                        | A13        | I/O                                      |

| 0    | N.C. (�)             | IO_L02N_0                        | A12        | 100E: N.C.<br>Others: I/O                |

| 0    | N.C. (�)             | IO_L02P_0                        | B12        | 100E: N.C.<br>Others: I/O                |

| 0    | N.C. (�)             | IO_L03N_0/VREF_0                 | B11        | 100E: N.C.<br>Others: VREF (I/O)         |

| 0    | IP                   | IO_L03P_0                        | C11        | <b>100E:</b> INPUT<br><b>Others:</b> I/O |

| 0    | IO_L04N_0/GCLK5      | IO_L04N_0/GCLK5                  | C9         | GCLK                                     |

| 0    | IO_L04P_0/GCLK4      | IO_L04P_0/GCLK4                  | A10        | GCLK                                     |

| 0    | IO_L05N_0/GCLK7      | IO_L05N_0/GCLK7                  | A9         | GCLK                                     |

| 0    | IO_L05P_0/GCLK6      | IO_L05P_0/GCLK6                  | B9         | GCLK                                     |

| 0    | IO_L07N_0/GCLK11     | IO_L07N_0/GCLK11                 | B7         | GCLK                                     |

| 0    | IO_L07P_0/GCLK10     | IO_L07P_0/GCLK10                 | A7         | GCLK                                     |

| 0    | IO_L08N_0/VREF_0     | IO_L08N_0/VREF_0                 | C6         | VREF                                     |

| 0    | IO_L08P_0            | IO_L08P_0                        | B6         | I/O                                      |

| 0    | IO_L09N_0            | IO_L09N_0                        | C5         | I/O                                      |

| 0    | IO_L09P_0            | IO_L09P_0                        | B5         | I/O                                      |

| 0    | N.C. (�)             | IO_L10N_0                        | C4         | 100E: N.C.<br>Others: I/O                |

| 0    | IP                   | IO_L10P_0                        | B4         | 100E: INPUT<br>Others: I/O               |

| 0    | IO_L11N_0/HSWAP      | IO_L11N_0/HSWAP                  | B3         | DUAL                                     |

| 0    | IO_L11P_0            | IO_L11P_0                        | A3         | I/O                                      |

| 0    | IP_L06N_0/GCLK9      | IP_L06N_0/GCLK9                  | C8         | GCLK                                     |

| 0    | IP_L06P_0/GCLK8      | IP_L06P_0/GCLK8                  | B8         | GCLK                                     |

| 0    | VCCO_0               | VCCO_0                           | A6         | VCCO                                     |

www.xilinx.com

## Table 133: CP132 Package Pinout (Cont'd)

| Bank | XC3S100E<br>Pin Name   | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                   |

|------|------------------------|----------------------------------|------------|----------------------------------------|

| 2    | N.C. (♦)               | IO_L08P_2/A23                    | N9         | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09N_2/A20                    | M10        | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09P_2/A21                    | N10        | 100E: N.C.<br>Others: DUAL             |

| 2    | IO_L10N_2/VS1/A18      | IO_L10N_2/VS1/A18                | M11        | DUAL                                   |

| 2    | IO_L10P_2/VS2/A19      | IO_L10P_2/VS2/A19                | N11        | DUAL                                   |

| 2    | IO_L11N_2/CCLK         | IO_L11N_2/CCLK                   | N12        | DUAL                                   |

| 2    | IO_L11P_2/VS0/A17      | IO_L11P_2/VS0/A17                | P12        | DUAL                                   |

| 2    | IP/VREF_2              | IP/VREF_2                        | N3         | VREF                                   |

| 2    | IP_L05N_2/M2/GCLK1     | IP_L05N_2/M2/GCLK1               | N6         | DUAL/GCLK                              |

| 2    | IP_L05P_2/RDWR_B/GCLK0 | IP_L05P_2/RDWR_B/GCLK0           | M6         | DUAL/GCLK                              |

| 2    | VCCO_2                 | VCCO_2                           | M8         | VCCO                                   |

| 2    | VCCO_2                 | VCCO_2                           | P3         | VCCO                                   |

| 3    | IO                     | IO                               | J3         | I/O                                    |

| 3    | IP/VREF_3              | IO/VREF_3                        | K3         | 100E: VREF(INPUT)<br>Others: VREF(I/O) |

| 3    | IO_L01N_3              | IO_L01N_3                        | B1         | I/O                                    |

| 3    | IO_L01P_3              | IO_L01P_3                        | B2         | I/O                                    |

| 3    | IO_L02N_3              | IO_L02N_3                        | C2         | I/O                                    |

| 3    | IO_L02P_3              | IO_L02P_3                        | C3         | I/O                                    |

| 3    | N.C. (♠)               | IO_L03N_3                        | D1         | 100E: N.C.<br>Others: I/O              |

| 3    | IO                     | IO_L03P_3                        | D2         | I/O                                    |

| 3    | IO_L04N_3/LHCLK1       | IO_L04N_3/LHCLK1                 | F2         | LHCLK                                  |

| 3    | IO_L04P_3/LHCLK0       | IO_L04P_3/LHCLK0                 | F3         | LHCLK                                  |

| 3    | IO_L05N_3/LHCLK3/IRDY2 | IO_L05N_3/LHCLK3/IRDY2           | G1         | LHCLK                                  |

| 3    | IO_L05P_3/LHCLK2       | IO_L05P_3/LHCLK2                 | F1         | LHCLK                                  |

| 3    | IO_L06N_3/LHCLK5       | IO_L06N_3/LHCLK5                 | H1         | LHCLK                                  |

| 3    | IO_L06P_3/LHCLK4/TRDY2 | IO_L06P_3/LHCLK4/TRDY2           | G3         | LHCLK                                  |

| 3    | IO_L07N_3/LHCLK7       | IO_L07N_3/LHCLK7                 | H3         | LHCLK                                  |

| 3    | IO_L07P_3/LHCLK6       | IO_L07P_3/LHCLK6                 | H2         | LHCLK                                  |

| 3    | IO_L08N_3              | IO_L08N_3                        | L2         | I/O                                    |

| 3    | IO_L08P_3              | IO_L08P_3                        | L1         | I/O                                    |

| 3    | IO_L09N_3              | IO_L09N_3                        | M1         | I/O                                    |

| 3    | IO_L09P_3              | IO_L09P_3                        | L3         | I/O                                    |

| 3    | IP/VREF_3              | IP/VREF_3                        | E2         | VREF                                   |

| 3    | VCCO_3                 | VCCO_3                           | E1         | VCCO                                   |

| 3    | VCCO_3                 | VCCO_3                           | J2         | VCCO                                   |

| GND  | N.C. (GND)             | GND                              | A4         | GND                                    |

| GND  | GND                    | GND                              | A8         | GND                                    |

| GND  | N.C. (GND)             | GND                              | C1         | GND                                    |

| GND  | GND                    | GND                              | C7         | GND                                    |

www.xilinx.com

## Table 133: CP132 Package Pinout (Cont'd)

| Bank   | XC3S100E<br>Pin Name | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре   |

|--------|----------------------|----------------------------------|------------|--------|

| GND    | GND                  | GND                              | C10        | GND    |

| GND    | GND                  | GND                              | E3         | GND    |

| GND    | GND                  | GND                              | E14        | GND    |

| GND    | GND                  | GND                              | G2         | GND    |

| GND    | GND                  | GND                              | H14        | GND    |

| GND    | GND                  | GND                              | J1         | GND    |

| GND    | GND                  | GND                              | K12        | GND    |

| GND    | GND                  | GND                              | M3         | GND    |

| GND    | GND                  | GND                              | M7         | GND    |

| GND    | GND                  | GND                              | P5         | GND    |

| GND    | N.C. (GND)           | GND                              | P10        | GND    |

| GND    | GND                  | GND                              | P14        | GND    |

| VCCAUX | DONE                 | DONE                             | P13        | CONFIG |

| VCCAUX | PROG_B               | PROG_B                           | A1         | CONFIG |

| VCCAUX | ТСК                  | ТСК                              | B13        | JTAG   |

| VCCAUX | TDI                  | TDI                              | A2         | JTAG   |

| VCCAUX | TDO                  | TDO                              | A14        | JTAG   |

| VCCAUX | TMS                  | TMS                              | B14        | JTAG   |

| VCCAUX | VCCAUX               | VCCAUX                           | A5         | VCCAUX |

| VCCAUX | VCCAUX               | VCCAUX                           | E12        | VCCAUX |

| VCCAUX | VCCAUX               | VCCAUX                           | K1         | VCCAUX |

| VCCAUX | VCCAUX               | VCCAUX                           | P9         | VCCAUX |

| VCCINT | VCCINT               | VCCINT                           | A11        | VCCINT |

| VCCINT | VCCINT               | VCCINT                           | D3         | VCCINT |

| VCCINT | N.C. (VCCINT)        | VCCINT                           | D14        | VCCINT |

| VCCINT | N.C. (VCCINT)        | VCCINT                           | K2         | VCCINT |

| VCCINT | VCCINT               | VCCINT                           | L12        | VCCINT |

| VCCINT | VCCINT               | VCCINT                           | P2         | VCCINT |

## Table 152: FG400 Package Pinout (Cont'd)

| Bank | XC3S1200E<br>XC3S1600E<br>Pin Name | FG400<br>Ball | Туре           |

|------|------------------------------------|---------------|----------------|

| 0    | IP_L17P_0/GCLK8                    | H10           | GCLK           |

| 0    | IP_L20N_0                          | G9            | INPUT          |

| 0    | IP_L20P_0                          | G8            | INPUT          |

| 0    | IP_L23N_0                          | C8            | INPUT          |

| 0    | IP_L23P_0                          | D8            | INPUT          |

| 0    | IP_L26N_0                          | E6            | INPUT          |

| 0    | IP_L26P_0                          | E7            | INPUT          |

| 0    | IP_L29N_0                          | A4            | INPUT          |

| 0    | IP_L29P_0                          | A5            | INPUT          |

| 0    | VCCO_0                             | B4            | VCCO           |

| 0    | VCCO_0                             | B10           | VCCO           |

| 0    | VCCO_0                             | B16           | VCCO           |

| 0    | VCCO_0                             | D7            | VCCO           |

| 0    | VCCO_0                             | D13           | VCCO           |

| 0    | VCCO_0                             | F10           | VCCO           |

| 1    | IO_L01N_1/A15                      | U18           | DUAL           |

| 1    | IO_L01P_1/A16                      | U17           | DUAL           |