### NXP USA Inc. - MC9RS08KA8CTGR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | RS08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 14                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 254 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9rs08ka8ctgr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1 | MCU    | Block Diagram                              |

|---|--------|--------------------------------------------|

| 2 |        | ssignments                                 |

| 3 | Electr | rical Characteristics                      |

|   | 3.1    | Introduction                               |

|   | 3.2    | Parameter Classification                   |

|   | 3.3    | Absolute Maximum Ratings                   |

|   | 3.4    | Thermal Characteristics                    |

|   | 3.5    | ESD Protection and Latch-Up Immunity7      |

|   | 3.6    | DC Characteristics                         |

|   | 3.7    | Supply Current Characteristics             |

|   | 3.8    | External Oscillator (XOSC) Characteristics |

|   | 3.9  | AC Characteristics                    |

|---|------|---------------------------------------|

|   |      | 3.9.1 Control Timing 19               |

|   |      | 3.9.2 TPM/MTIM Module Timing          |

|   | 3.10 | Analog Comparator (ACMP) Electrical   |

|   | 3.11 | Internal Clock Source Characteristics |

|   | 3.12 | ADC Characteristics                   |

|   |      | Flash Specifications                  |

| 4 | Orde | ring Information                      |

| 5 | Mech | nanical Drawings                      |

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision | Date      | Description of Changes                                                                                               |  |  |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 1        | 1/22/2008 | Initial public release                                                                                               |  |  |

| 2        | 10/7/2008 | Updated Figure 4 and Figure 10.<br>Updated "How to Reach Us" information.<br>Added 16-pin TSSOP package information. |  |  |

| 3        | 11/4/2008 | Updated operating voltage in Table 7.                                                                                |  |  |

| 4        | 6/11/2009 | Added output voltage of high drive at 5 V, $I_{load} = 10$ mA in the Table 7.                                        |  |  |

## **Related Documentation**

Find the most current versions of all documents at: http://www.freescale.com

#### Reference Manual (MC9RS08KA8RM)

Contains extensive product information including modes of operation, memory, resets and interrupts, register definition, port pins, CPU, and all module information.

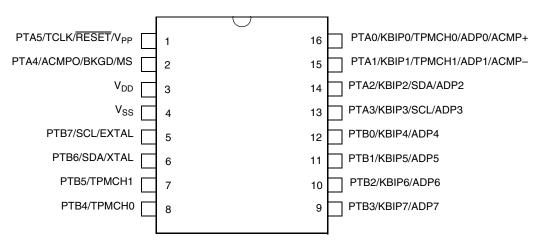

Figure 3. MC9RS08KA8 Series in 16-Pin PDIP/SOIC/TSSOP Package

## **3 Electrical Characteristics**

### 3.1 Introduction

This chapter contains electrical and timing specifications for the MC9RS08KA8 series of microcontrollers available at the time of publication.

### 3.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Table 2. Parameter Cla | assifications |

|------------------------|---------------|

|------------------------|---------------|

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

| Model         | Description                 | Symbol | Value | Unit |

|---------------|-----------------------------|--------|-------|------|

|               | Series resistance           | R1     | 1500  | Ω    |

| Human<br>Body | Storage capacitance         | С      | 100   | pF   |

| 2003          | Number of pulses per pin    | —      | 3     | _    |

|               | Series resistance           | R1     | 0     | Ω    |

| Machine       | Storage capacitance         | С      | 200   | pF   |

|               | Number of pulses per pin    | —      | 3     | _    |

| Latch-up      | Minimum input voltage limit | —      | -2.5  | V    |

|               | Maximum input voltage limit | —      | 7.5   | V    |

Table 5. ESD and Latch-up Test Conditions

| Table 6. ESD and Latch-Up Protection Characterist | ics |

|---------------------------------------------------|-----|

|---------------------------------------------------|-----|

| No. | Rating <sup>1</sup>                                                                         | Symbol           | Min               | Max | Unit |

|-----|---------------------------------------------------------------------------------------------|------------------|-------------------|-----|------|

| 1   | Human body model (HBM)                                                                      | V <sub>HBM</sub> | ±2000             | —   | V    |

| 2   | Machine model (MM)                                                                          | V <sub>MM</sub>  | ±200              | —   | V    |

| 3   | Charge device model (CDM)                                                                   | V <sub>CDM</sub> | ±500              | —   | V    |

| 4   | Latch-up current at $T_A = 85^{\circ}C$<br>(applies to all pins except pin 9<br>PTC3/ADP11) | I <sub>LAT</sub> | ±100 <sup>2</sup> | _   | mA   |

|     | Latch-up current at $T_A = 85^{\circ}C$<br>(applies to pin 9 PTC3/ADP11)                    | I <sub>LAT</sub> | ±75 <sup>3</sup>  | _   | mA   |

<sup>1</sup> Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

$^2~$  These pins meet JESD78A Class II (section 1.2) Level A (section 1.3) requirement of  $\pm 100 m A.$

$^3\,$  This pin meets JESD78A Class II (section 1.2) Level B (section 1.3) characterization to  $\pm 75$  mA. This pin is only present on 20 pin package types.

### 3.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Parameter                                                                                                                      | Symbol                        | Min              | Typical      | Max          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|--------------|--------------|------|

| Supply voltage (run, wait and stop modes.)<br>0 < f <sub>Bus</sub> <10MHz<br>V <sub>DD</sub> rising<br>V <sub>DD</sub> falling | V <sub>DD</sub>               | 2.0<br>1.8       | _            | 5.5          | v    |

| Minimum RAM retention supply voltage applied to $V_{DD}$                                                                       | V <sub>RAM</sub>              | 0.8 <sup>1</sup> | —            | —            | V    |

| Low-voltage Detection threshold<br>(V <sub>DD</sub> falling)<br>(V <sub>DD</sub> rising)                                       | V <sub>LVD</sub>              | 1.80<br>1.88     | 1.86<br>1.94 | 1.95<br>2.03 | v    |

| Power on RESET (POR) voltage                                                                                                   | V <sub>POR</sub> <sup>1</sup> | 0.9              | —            | 1.7          | V    |

| Parameter                                                                                                                                                                               | Symbol                        | Min                   | Typical     | Max                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-------------|----------------------|------|

| Input high voltage (V <sub>DD</sub> > 2.3V) (all digital inputs)                                                                                                                        | V <sub>IH</sub>               | $0.70 \times V_{DD}$  | _           | —                    | V    |

| Input high voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                     | V <sub>IH</sub>               | $0.85 \times V_{DD}$  | _           | —                    | V    |

| Input low voltage (V <sub>DD</sub> > 2.3 V) (all digital inputs)                                                                                                                        | V <sub>IL</sub>               | _                     | _           | $0.30 \times V_{DD}$ | V    |

| Input low voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                      | V <sub>IL</sub>               | —                     |             | $0.30\times V_{DD}$  | V    |

| Input hysteresis (all digital inputs)                                                                                                                                                   | V <sub>hys</sub> <sup>1</sup> | $0.06 \times V_{DD}$  | —           | —                    | V    |

| Input leakage current (per pin)<br>$V_{In} = V_{DD}$ or $V_{SS}$ , all input only pins                                                                                                  | llinl                         | —                     | 0.025       | 1.0                  | μA   |

| High impedance (off-state) leakage current (per pin) $V_{In} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                   | llozi                         | —                     | 0.025       | 1.0                  | μA   |

| Internal pullup resistors <sup>2</sup> (all port pins)                                                                                                                                  | R <sub>PU</sub>               | 20                    | 45          | 65                   | kΩ   |

| Internal pulldown resistors <sup>2</sup> (all port pins except PTA5)                                                                                                                    | R <sub>PD</sub>               | 20                    | 45          | 65                   | kΩ   |

| PTA5 Internal pulldown resistor                                                                                                                                                         | _                             | 45                    | —           | 95                   | kΩ   |

| Output high voltage — Low Drive (PTxDSn = 0)<br>5 V, $I_{Load} = 2 \text{ mA}$<br>3 V, $I_{Load} = 1 \text{ mA}$<br>1.8 V, $I_{Load} = 0.5 \text{ mA}$                                  |                               | V <sub>DD</sub> – 0.8 |             | <br>                 |      |

| Output high voltage — High Drive (PTxDSn = 1)<br>5 V, $I_{Load}$ = 10 mA<br>5 V, $I_{Load}$ = 5 mA<br>3 V, $I_{Load}$ = 3 mA<br>1.8 V, $I_{Load}$ = 2 mA                                | V <sub>OH</sub>               | V <sub>DD</sub> – 0.8 | _<br>_<br>_ | <br>                 | V    |

| Maximum total IOH for all port pins                                                                                                                                                     | I <sub>OHT</sub>              | —                     |             | 40                   | mA   |

| Output low voltage — Low Drive (PTxDSn = 0)<br>5 V, $I_{Load} = 2 \text{ mA}$<br>3 V, $I_{Load} = 1 \text{ mA}$<br>1.8 V, $I_{Load} = 0.5 \text{ mA}$                                   |                               |                       |             | 0.8                  |      |

| Output low voltage — High Drive (PTxDSn = 1)<br>5 V, $I_{Load} = 10 \text{ mA}$<br>5 V, $I_{Load} = 5 \text{ mA}$<br>3 V, $I_{Load} = 3 \text{ mA}$<br>1.8 V, $I_{Load} = 2 \text{ mA}$ | V <sub>OL</sub>               | <br>                  | <br>        | 0.8                  | V    |

| Maximum total IoL for all port pins                                                                                                                                                     | I <sub>OLT</sub>              | —                     | —           | 40                   | mA   |

| DC injection current <sup>3, 4, 5, 6</sup><br>$V_{In} < V_{SS}, V_{In} > V_{DD}$<br>Single pin limit<br>Total MCU limit, includes sum of all stressed pins                              |                               |                       |             | 0.2<br>0.8           | mA   |

| Input capacitance (all non-supply pins)                                                                                                                                                 | C <sub>In</sub>               | —                     | —           | 7                    | pF   |

#### Table 7. DC Characteristics (Temperature Range = -40 to 85°C Ambient) (continued)

<sup>1</sup> This parameter is characterized and not tested on each device.

$^2~$  Measurement condition for pull resistors: V\_In = V\_{SS} for pullup and V\_In = V\_{DD} for pulldown.

<sup>3</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> except the RESET/V<sub>PP</sub> which is internally clamped to V<sub>SS</sub> only.

- <sup>4</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>5</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>6</sup> This parameter is characterized and not tested on each device.

MC9RS08KA8 Series MCU Data Sheet, Rev. 4

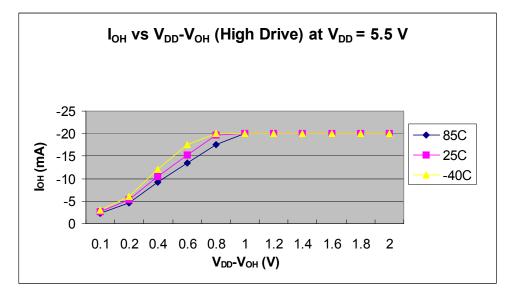

Figure 4. Typical  $I_{OH}$  vs.  $V_{DD}$ – $V_{OH}$  $V_{DD}$  = 5.5 V (High Drive)

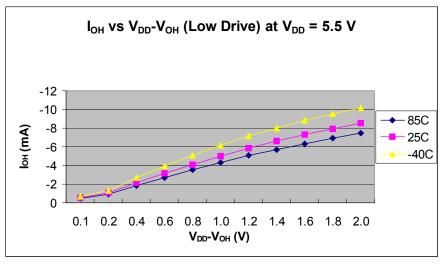

Figure 5. Typical I<sub>OH</sub> vs. V<sub>DD</sub>–V<sub>OH</sub> V<sub>DD</sub> = 5.5 V (Low Drive)

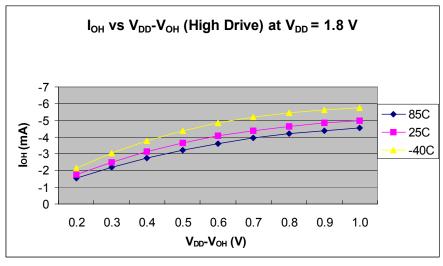

Figure 8. Typical  $I_{OH}$  vs.  $V_{DD}$ - $V_{OH}$  $V_{DD}$  = 1.8 V (High Drive)

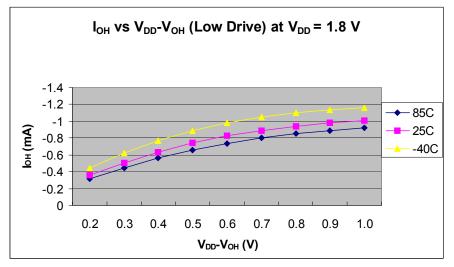

Figure 9. Typical I<sub>OH</sub> vs. V<sub>DD</sub>–V<sub>OH</sub> V<sub>DD</sub> = 1.8 V (Low Drive)

| Parameter                                                                    | Symbol            | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup> | Temp. (°C) |

|------------------------------------------------------------------------------|-------------------|---------------------|----------------------|------------------|------------|

|                                                                              |                   | 5                   | 0.42 mA              | 2 mA             | 25<br>85   |

| Run supply current <sup>3</sup> measured at<br>(f <sub>Bus</sub> = 1.25 MHz) | RI <sub>DD1</sub> | 3                   | 0.42 mA              | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 0.3 mA               | _                | 25<br>85   |

|                                                                              |                   | 5                   | 2.4 μA               | 5 μΑ<br>8 μΑ     | 25<br>85   |

| Stop mode supply current                                                     | SI <sub>DD</sub>  | 3                   | 2 μΑ                 | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 1.5 μA               | _                | 25<br>85   |

|                                                                              |                   | 5                   | 128 μA               | 150 μΑ<br>165 μΑ | 25<br>85   |

| ADC adder from stop <sup>4</sup>                                             | _                 | 3                   | 121 μA               | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 79 μA                | _                | 25<br>85   |

|                                                                              | _                 | 5                   | 21 μA                | 22 μA            | 25<br>85   |

| ACMP adder from stop<br>(ACME = 1)                                           |                   | 3                   | 18.5 μA              | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 17.5 μA              | _                | 25<br>85   |

|                                                                              |                   | 5                   | 2.4 μA               | 2 μΑ             | 25<br>85   |

| RTI adder from stop<br>with 1 kHz clock source enabled <sup>5</sup>          | _                 | 3                   | 1.9 μA               | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 1.5 μA               | _                | 25<br>85   |

|                                                                              |                   | 5                   | 2.1 μA               | 2 μΑ             | 25<br>85   |

| RTI adder from stop<br>with 1 MHz external clock source reference<br>enabled | _                 | 3                   | 1.6 μA               | _                | 25<br>85   |

| enableu                                                                      |                   | 1.80                | 1.2 μA               | _                | 25<br>85   |

|                                                                              |                   | 5                   | 70 μA                | 80 μA            | 25<br>85   |

| LVI adder from stop<br>(LVDE=1 and LVDSE=1)                                  | _                 | 3                   | 65 μA                | _                | 25<br>85   |

|                                                                              |                   | 1.80                | 60 μA                |                  | 25<br>85   |

<sup>1</sup> Typicals are measured at 25°C.

<sup>2</sup> Maximum value is measured at the nominal  $V_{DD}$  voltage times 10% tolerance. Values given here are preliminary estimates prior to completing characterization.

<sup>3</sup> Not include any DC loads on port pins.

<sup>4</sup> Required asynchronous ADC clock and LVD to be enabled.

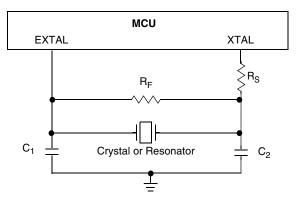

### 3.8 External Oscillator (XOSC) Characteristics

Table 9. Oscillator Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Num | С | Rating                                                                                                                                                                                                                                           | Symbol                                                                          | Min                                              | Typical <sup>1</sup>         | Max                  | Unit                     |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|----------------------|--------------------------|

| 1   | С | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)<br>Low range (RANGE = 0)<br>High range (RANGE = 1) FEE or FBE mode <sup>2</sup><br>High range (RANGE = 1, HGO = 1) FBELP mode<br>High range (RANGE = 1, HGO = 0) FBELP mode             | f <sub>lo</sub><br>f <sub>hi</sub><br>f <sub>hi-hgo</sub><br>f <sub>hi-lp</sub> | 32<br>1<br>1<br>1                                |                              | 38.4<br>5<br>16<br>8 | kHz<br>MHz<br>MHz<br>MHz |

| 2   | D | Load capacitors                                                                                                                                                                                                                                  | C <sub>1,</sub> C <sub>2</sub>                                                  | See crystal or res<br>manufacture<br>recommendat |                              | urer's               |                          |

| 3   | D | Feedback resistor<br>Low range (32 kHz to 100 kHz)<br>High range (1 MHz to 16 MHz)                                                                                                                                                               | R <sub>F</sub>                                                                  | _                                                | 10<br>1                      | _                    | MΩ                       |

| 4   | D | Series resistor<br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0)<br>High range, high gain (RANGE = 1, HGO = 1)<br>$\geq 8 \text{ MHz}$<br>4 MHz<br>1 MHz    | R <sub>S</sub>                                                                  |                                                  | 0<br>100<br>0<br>0<br>0<br>0 | <br><br>10<br>20     | kΩ                       |

| 5   | С | Crystal start-up time <sup>3</sup><br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0) <sup>4</sup><br>High range, high gain (RANGE = 1, HGO = 1) <sup>4</sup> | t<br>CSTL-LP<br>t<br>CSTL-HGO<br>t<br>CSTH-LP<br>t<br>CSTH-HGO                  |                                                  | 200<br>400<br>5<br>20        |                      | ms                       |

| 6   | D | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1)<br>FEE or FBE mode <sup>2</sup><br>FBELP mode                                                                                                                                         | f <sub>extal</sub>                                                              | 0.03125<br>0                                     | _                            | 5<br>40              | MHz                      |

<sup>1</sup> Typical data was characterized at 5.0 V, 25 °C or is recommended value.

<sup>2</sup> The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

<sup>4</sup> 4 MHz crystal.

### 3.9 AC Characteristics

This section describes AC timing characteristics for each peripheral system.

### 3.9.1 Control Timing

| Num | С | Parameter                                                                                                                             | Symbol                                | Min                  | Typical  | Мах  | Unit |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------|------|------|

| 1   | D | Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> )                                                                                | f <sub>Bus</sub>                      | 0                    | _        | 10   | MHz  |

| 2   | D | Real time interrupt internal oscillator period                                                                                        | t <sub>RTI</sub>                      | 700                  | 1000     | 1300 | μS   |

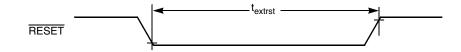

| 3   | D | External RESET pulse width <sup>1</sup>                                                                                               | t <sub>extrst</sub>                   | 150                  | _        | —    | ns   |

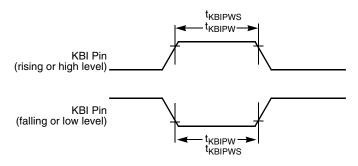

| 4   | D | KBI pulse width <sup>2</sup>                                                                                                          | t <sub>KBIPW</sub>                    | 1.5 t <sub>cyc</sub> | _        | —    | ns   |

| 5   | D | KBI pulse width in stop <sup>1</sup>                                                                                                  | t <sub>KBIPWS</sub>                   | 100                  | _        | —    | ns   |

| 6   | D | Port rise and fall time $(load = 50 \text{ pF})^3$<br>Slew rate control disabled (PTxSE = 0)<br>Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> |                      | 11<br>35 |      | ns   |

<sup>1</sup> This is the shortest pulse guaranteed to pass through the pin input filter circuitry. Shorter pulses may or may not be recognized.

<sup>2</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^3$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 85°C.

Figure 17. Reset Timing

Figure 18. KBI Pulse Width

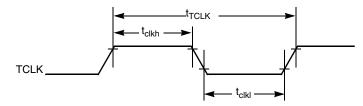

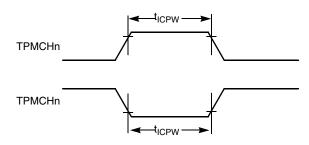

### 3.9.2 TPM/MTIM Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Num | С | Rating                    | Symbol              | Min | Max                 | Unit             |

|-----|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1   | D | External clock frequency  | f <sub>TPMext</sub> | DC  | f <sub>Bus</sub> /4 | MHz              |

| 2   | D | External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

Figure 19. Timer External Clock

Figure 20. Timer Input Capture Pulse

### 3.10 Analog Comparator (ACMP) Electrical

### Table 12. Analog Comparator Electrical Specifications

| Num | С | Characteristic                            | Symbol             | Min                   | Typical | Max             | Unit |

|-----|---|-------------------------------------------|--------------------|-----------------------|---------|-----------------|------|

| 1   | D | Supply voltage                            | V <sub>DD</sub>    | 1.80                  |         | 5.5             | V    |

| 2   | Р | Supply current (active)                   | I <sub>DDAC</sub>  | _                     | 20      | 35              | μA   |

| 3   | D | Analog input voltage <sup>1</sup>         | V <sub>AIN</sub>   | V <sub>SS</sub> – 0.3 | —       | V <sub>DD</sub> | V    |

| 4   | Р | Analog input offset voltage <sup>1</sup>  | V <sub>AIO</sub>   | _                     | 20      | 40              | mV   |

| 5   | С | Analog Comparator hysteresis <sup>1</sup> | V <sub>H</sub>     | 3.0                   | 9.0     | 15.0            | mV   |

| 6   | С | Analog source impedance <sup>1</sup>      | R <sub>AS</sub>    | _                     | _       | 10              | kΩ   |

| 7   | Р | Analog input leakage current              | I <sub>ALKG</sub>  | —                     | —       | 1.0             | μA   |

| 8   | С | Analog Comparator initialization delay    | t <sub>AINIT</sub> | _                     | —       | 1.0             | μS   |

| Num | С | Characteristic                              | Symbol   | Min | Typical | Max | Unit |

|-----|---|---------------------------------------------|----------|-----|---------|-----|------|

| 9   | Ρ | Analog Comparator bandgap reference voltage | $V_{BG}$ | 1.1 | 1.208   | 1.3 | V    |

Table 12. Analog Comparator Electrical Specifications (continued)

<sup>1</sup> These data are characterized but not production tested.

### 3.11 Internal Clock Source Characteristics

### Table 13. Internal Clock Source Specifications

| Num | С | Characteristic                                                                                 | Symbol                   | Min   | Typical <sup>1</sup> | Max     | Unit  |

|-----|---|------------------------------------------------------------------------------------------------|--------------------------|-------|----------------------|---------|-------|

| 1   | С | Average internal reference frequency — untrimmed                                               | f <sub>int_ut</sub>      | 25    | 31.25                | 41.66   | kHz   |

| 2   | Ρ | Average internal reference frequency — trimmed                                                 | f <sub>int_t</sub>       | 31.25 | 39.06                | 39.0625 | kHz   |

| 3   | С | DCO output frequency range — untrimmed                                                         | f <sub>dco_ut</sub>      | 12.8  | 16                   | 21.33   | MHz   |

| 4   | Ρ | DCO output frequency range — trimmed                                                           | f <sub>dco_t</sub>       | 16    | 20                   | 20      | MHz   |

| 5   | С | Resolution of trimmed DCO output frequency<br>at fixed voltage and temperature                 | $\Delta f_{dco\_res\_t}$ | _     | _                    | 0.2     | %fdco |

| 6   | С | Total deviation of trimmed DCO output frequency over voltage and temperature                   | $\Delta f_{dco_t}$       | _     | _                    | 2       | %fdco |

| 7   | С | FLL acquisition time <sup>2,3</sup>                                                            | t <sub>acquire</sub>     | _     | —                    | 1       | ms    |

| 8   | С | Stop recovery time (FLL wakeup to previous acquired frequency)<br>IREFSTEN = 0<br>IREFSTEN = 1 | t_wakeup                 | _     | 100<br>86            | _       | μS    |

<sup>1</sup> Data in typical column was characterized at 3.0 V and 5.0 V, 25 °C or is typical recommended value.

<sup>2</sup> This parameter is characterized and not tested on each device.

<sup>3</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (FBILP) to FLL enabled (FEI, FBI).

### 3.12 ADC Characteristics

### Table 14. 5 Volt 10-bit ADC Operating Conditions

| С | Characteristic                              | Conditions                                                          | Symb              | Min.     | Typical | Max.     | Unit |

|---|---------------------------------------------|---------------------------------------------------------------------|-------------------|----------|---------|----------|------|

| D | Input voltage                               | —                                                                   | V <sub>ADIN</sub> | $V_{SS}$ | —       | $V_{DD}$ | V    |

| С | Accuracy                                    | V <sub>DD</sub> = 2 V                                               |                   |          | 8 bit   | _        | —    |

| С | Input capacitance                           | —                                                                   | C <sub>ADIN</sub> | _        | 4.5     | 5.5      | pF   |

| С | Input resistance                            | —                                                                   | R <sub>ADIN</sub> | _        | 3       | 5        | kΩ   |

| С | Analog source resistance<br>external to MCU | 10 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   |          |         | 5<br>10  | kΩ   |

|   |                                             | 8 bit mode (all valid f <sub>ADCK</sub> )                           |                   | _        | _       | 10       |      |

| Characteristic                 | Conditions                                                           | С        | Symb               | Min | Typical <sup>1</sup> | Max  | Unit             |  |

|--------------------------------|----------------------------------------------------------------------|----------|--------------------|-----|----------------------|------|------------------|--|

| Supply current                 | Stop, reset, module off                                              | т        | I <sub>DDAD</sub>  | _   | 0.011                | 1    | μA               |  |

| ADC asynchronous clock         | High speed (ADLPC = 0)                                               |          | f                  | —   | 3.3                  | —    | MHz              |  |

| source                         | Low power (ADLPC = 1)                                                | Т        | f <sub>ADACK</sub> | _   | 2                    | —    |                  |  |

| Conversion time (including     | Short sample (ADLSMP=0)                                              | Р        | +                  | _   | 20                   | _    | ADCK             |  |

| sample time)                   | Long sample (ADLSMP=1)                                               |          | t <sub>ADC</sub>   | _   | 40                   | —    | cycles           |  |

| Sample time                    | Short sample (ADLSMP=0)                                              | Р        | +                  | —   | 3.5                  | —    | ADCK             |  |

| Sample line                    | Long sample (ADLSMP=1)                                               |          | t <sub>ADS</sub>   | _   | 23.5                 | _    | cycles           |  |

| Total upadiusted array         | 10 bit mode                                                          | <u> </u> | C E <sub>TUE</sub> | —   | ±1                   | ±2.5 | LSB <sup>2</sup> |  |

| Total unadjusted error         | 8 bit mode                                                           |          |                    | _   | ±0.5                 | ±1.0 |                  |  |

|                                | 10 bit mode                                                          | Р        | DNL                | —   | ±0.5                 | ±1.0 | LSB <sup>2</sup> |  |

| Differential non-linearity     | 8 bit mode                                                           | Т        | DINL               | _   | ±0.3                 | ±0.5 | 200              |  |

|                                | rity 8 bit mode T — ±0.<br>Monotonicity and No-Missing-Codes guarant |          | guaranteed         |     |                      |      |                  |  |

| Integral non-linearity         | 10 bit mode                                                          | с        | INL                | —   | ±0.5                 | ±1.0 | LSB <sup>2</sup> |  |

| integral non-linearity         | 8 bit mode                                                           |          | IINL               | _   | ±0.3                 | ±0.5 | LOD              |  |

| Zero-scale error               | 10 bit mode                                                          | Р        | E                  | —   | ±0.5                 | ±1.5 | LSB <sup>2</sup> |  |

|                                | 8 bit mode                                                           | Т        | E <sub>ZS</sub>    | _   | ±0.5                 | ±0.5 | LOD              |  |

| Full-Scale error               | 10 bit mode                                                          | Р        | E                  | —   | ±0.5                 | ±1.5 | LSB <sup>2</sup> |  |

| VADIN = VDDA                   | 8 bit mode                                                           | Т        | E <sub>FS</sub>    | _   | ±0.5                 | ±0.5 | LSB-             |  |

| Quantization arrar             | 10 bit mode                                                          | D        | E                  | —   | —                    | ±0.5 | LSB <sup>2</sup> |  |

| Quantization error             | 8 bit mode                                                           |          | EQ                 | —   | _                    | ±0.5 | LOR-             |  |

| Input leakage error            | 10 bit mode                                                          |          | E                  | —   | ±0.2                 | ±2.5 | LSB <sup>2</sup> |  |

| pad leakage <sup>3</sup> * RAS | 8 bit mode                                                           | D        | E <sub>IL</sub>    | _   | ±0.1                 | ±1   | LOD              |  |

<sup>1</sup> Typical values assume Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> 1 LSB =  $(V_{REFH} - V_{REFL})/2^{N}$

<sup>3</sup> Based on input pad leakage current. Refer to pad electrical.

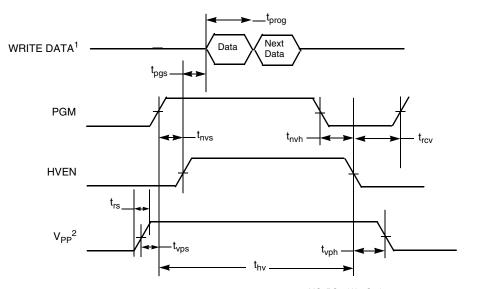

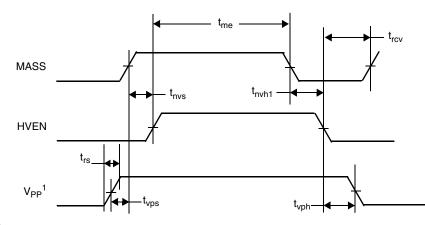

### 3.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the flash memory. For detailed information about program/erase operations, see the reference manual.

| Table 1 | 16. | Flash | Characteristics |

|---------|-----|-------|-----------------|

|---------|-----|-------|-----------------|

| Characteristic                   | Symbol          | Min | Typical <sup>1</sup> | Max | Unit |

|----------------------------------|-----------------|-----|----------------------|-----|------|

| Supply voltage for program/erase | V <sub>DD</sub> | 2.7 | _                    | 5.5 | V    |

### MC9RS08KA8 Series MCU Data Sheet, Rev. 4

| Characteristic                                                          | Symbol                                          | Min  | Typical <sup>1</sup> | Мах        | Unit                     |

|-------------------------------------------------------------------------|-------------------------------------------------|------|----------------------|------------|--------------------------|

| Program/Erase voltage                                                   | V <sub>PP</sub>                                 | 11.8 | 12                   | 12.2       | V                        |

| VPP current<br>Program<br>Mass erase                                    | I <sub>VPP_prog</sub><br>I <sub>VPP_erase</sub> | _    |                      | 200<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| Supply voltage for read operation<br>0 < fBus < 10 MHz                  | V <sub>Read</sub>                               | 1.8  | _                    | 5.5        | V                        |

| Byte program time                                                       | t <sub>prog</sub>                               | 20   | —                    | 40         | μS                       |

| Mass erase time                                                         | t <sub>me</sub>                                 | 500  | —                    |            | ms                       |

| Cumulative program HV time <sup>2</sup>                                 | t <sub>hv</sub>                                 | _    | —                    | 8          | ms                       |

| Total cumulative HV time<br>(total of tme & thy applied to device)      | t <sub>hv_total</sub>                           | _    | —                    | 2          | hours                    |

| HVEN to program setup time                                              | t <sub>pgs</sub>                                | 10   | —                    |            | μS                       |

| PGM/MASS to HVEN setup time                                             | t <sub>nvs</sub>                                | 5    | —                    |            | μS                       |

| HVEN hold time for PGM                                                  | t <sub>nvh</sub>                                | 5    | —                    |            | μS                       |

| HVEN hold time for MASS                                                 | t <sub>nvh1</sub>                               | 100  | —                    |            | μS                       |

| V <sub>PP</sub> to PGM/MASS setup time                                  | t <sub>vps</sub>                                | 20   | —                    |            | ns                       |

| HVEN to V <sub>PP</sub> hold time                                       | t <sub>vph</sub>                                | 20   | —                    |            | ns                       |

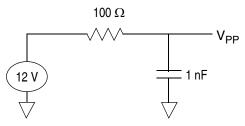

| V <sub>PP</sub> rise time <sup>3</sup>                                  | t <sub>vrs</sub>                                | 200  | —                    |            | ns                       |

| Recovery time                                                           | t <sub>rcv</sub>                                | 1    | —                    |            | μS                       |

| Program/erase endurance<br>TL to TH = $-40^{\circ}$ C to $85^{\circ}$ C | _                                               | 1000 | —                    |            | cycles                   |

| Data retention                                                          | t <sub>D_ret</sub>                              | 15   | —                    |            | years                    |

#### Table 16. Flash Characteristics (continued)

<sup>1</sup> Typicals are measured at 25 °C.

<sup>2</sup>  $t_{hv}$  is the cumulative high voltage programming time to the same row before next erase. Same address can not be programmed more than twice before next erase.

<sup>3</sup> Fast V<sub>PP</sub> rise time may potentially trigger the ESD protection structure, which may result in over current flowing into the pad and cause permanent damage to the pad. External filtering for the V<sub>PP</sub> power source is recommended. An example V<sub>PP</sub> filter is shown in Figure 22.

Figure 22. Example V<sub>PP</sub> Filtering

<sup>1</sup> Next Data applies if programming multiple bytes in a single row, refer to  $^{MC9RS08KA8 Series}$  Reference Manual. <sup>2</sup> V<sub>DD</sub> must be at a valid operating voltage before voltage is applied or removed from the V<sub>PP</sub> pin.

Figure 23. Flash Program Timing

$^{1}$  V<sub>DD</sub> must be at a valid operating voltage before voltage is applied or removed from the V<sub>PP</sub> pin.

Figure 24. Flash Mass Erase Timing

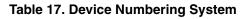

**Ordering Information**

# 4 Ordering Information

This section contains ordering numbers for MC9RS08KA8 series devices. See below for an example of the device numbering system.

| Device Number            | Memory               |                        | Package   |            |              |  |

|--------------------------|----------------------|------------------------|-----------|------------|--------------|--|

|                          | Flash                | RAM                    | Туре      | Designator | Document No. |  |

| MC9RS08KA8<br>MC9RS08KA4 | 8K bytes<br>4K bytes | 254 bytes<br>126 bytes | 16 PDIP   | PG         | 98ASB42431B  |  |

|                          |                      |                        | 16 W-SOIC | WG         | 98ASB42567B  |  |

|                          |                      |                        | 16 TSSOP  | TG         | 98ASH70247A  |  |

|                          |                      |                        | 20 PDIP   | PJ         | 98ASB42899B  |  |

|                          |                      |                        | 20 W-SOIC | WJ         | 98ASB42343B  |  |

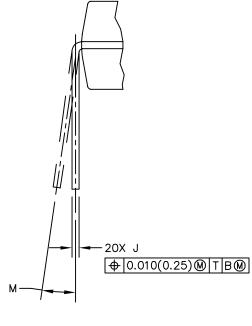

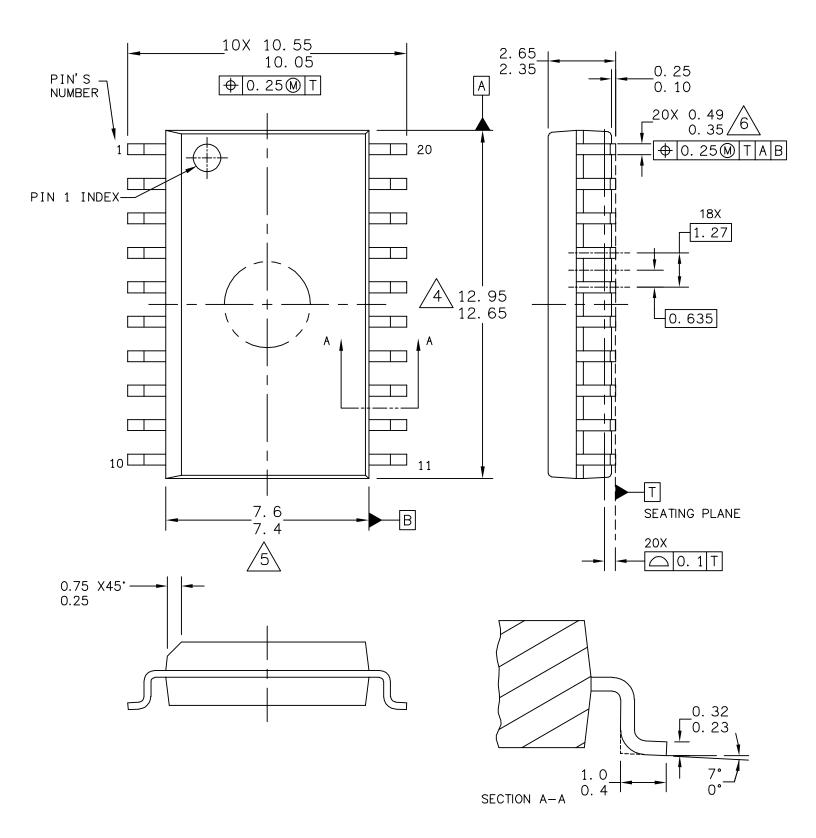

# 5 Mechanical Drawings

This following pages contain mechanical specifications for MC9RS08KA8 series package options.

- 16-pin PDIP (plastic dual in-line pin)

- 16-pin W-SOIC (wide body small outline integrated circuit)

- 16-pin TSSOP (thin shrink sSmall outline package)

- 20-pin PDIP (plastic dual in-line pin)

- 20-pin W-SOIC (wide body small outline integrated circuit)

### STYLE 1:

### PIN 1. CATHODE

- 2. CATHODE

- 3. CATHODE

- 4. CATHODE

- 5. CATHODE

- 6. CATHODE

- 7. CATHODE

- 8. CATHODE

- 9. ANODE

- 10. ANODE

- 11. ANODE

- 12. ANODE

- 13. ANODE

- 14. ANODE

- 15. ANODE

- 16. ANODE

STYLE 2:

- PIN 1. COMMON DRAIN

- 2. COMMON DRAIN

- 3. COMMON DRAIN

- 4. COMMON DRAIN

- 5. COMMON DRAIN

- 6. COMMON DRAIN

- 7. COMMON DRAIN

- 8. COMMON DRAIN

- 9. GATE

- 10. SOURCE

- 11. GATE

- 12. SOURCE

- 13. GATE

- 14. SOURCE

- 15. GATE

- 16. SOURCE

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                     | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|---------------------|----------------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NO         | ): 98ASB42431B             | REV: T      |

| 16 LD PDIP                                              |                    | CASE NUMBER         | 8:648-08                   | 19 MAY 2005 |

|                                                         |                    | STANDARD: NON-JEDEC |                            |             |

VIEW D

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. | MECHANICAL OUTLINE | PRINT VERSION NO | IT TO SCALE |

|---------------------------------------------------------|--------------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT           | ND: 98ASB42899B  | RE∨: B      |

| 20LD .300 PDI                                           | CASE NUMB          | ER: 738C-01      | 24 MAY 2005 |

|                                                         | STANDARD:          | NON-JEDEC        |             |

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. | MECHANICA    | L OUTLINE      | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|--------------|----------------|------------------|-------------|

| TITLE:                                                  | DOCUMENT NO  | ): 98ASB42343B | REV: J           |             |

| 20LD SOIC W/B, 1.27 PITCH<br>CASE-OUTLINE               |              | CASE NUMBER    | R: 751D-07       | 23 MAR 2005 |

|                                                         | STANDARD: JE | DEC MS-013AC   |                  |             |