Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                    |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 118                                                                             |

| Program Memory Size        | 576KB (576K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 50K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-144-4                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe167h-72f66l-ac |

| 1                                                                                                                | Summary of Features 4                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1                                                                                                  | General Device Information       8         Pin Configuration and Definition       9                                                                                                                                                                                                                                                                                                                                              |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                         | Functional Description36Memory Subsystem and Organization37External Bus Controller40Central Processing Unit (CPU)41Interrupt System43On-Chip Debug Support (OCDS)49Capture/Compare Unit (CAPCOM2)50Capture/Compare Units CCU6x53General Purpose Timer (GPT12E) Unit55Real Time Clock59A/D Converters61Universal Serial Interface Channel Modules (USIC)62MultiCAN Module64                                                       |

| 3.13<br>3.14<br>3.15<br>3.16                                                                                     | Watchdog Timer 66 Clock Generation 66 Parallel Ports 67 Instruction Set Summary 69                                                                                                                                                                                                                                                                                                                                               |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.6.5<br>4.6.6 | Electrical Parameters72General Parameters72DC Parameters76DC Parameters for Upper Voltage Area78DC Parameters for Lower Voltage Area80Power Consumption82Analog/Digital Converter Parameters86System Parameters89Flash Memory Parameters91AC Parameters93Testing Waveforms93Definition of Internal Timing94External Clock Input Parameters99External Bus Timing101Synchronous Serial Interface Timing112JTAG Interface Timing115 |

| <b>5</b><br>5.1<br>5.2                                                                                           | Package and Reliability       117         Packaging       117         Thermal Considerations       118                                                                                                                                                                                                                                                                                                                           |

Data Sheet 3 V2.1, 2008-08

## **Summary of Features**

The XE167 types are offered with several Flash memory sizes. **Table 2** describes the location of the available memory areas for each Flash memory size.

Table 2 Flash Memory Allocation

| Total Flash Size | Flash Area A <sup>1)</sup>                   | Flash Area B                                 | Flash Area C |

|------------------|----------------------------------------------|----------------------------------------------|--------------|

| 768 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>CB'FFFF <sub>H</sub> | n.a.         |

| 576 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C8'FFFF <sub>H</sub> | n.a.         |

| 384 Kbytes       | C0'0000 <sub>H</sub><br>C0'EFFF <sub>H</sub> | C1'0000 <sub>H</sub><br>C5'FFFF <sub>H</sub> | n.a.         |

<sup>1)</sup> The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE167 types are offered with different interface options. **Table 3** lists the available channels for each option.

Table 3 Interface Channel Association

| Total Number      | Available Channels                 |

|-------------------|------------------------------------|

| 16 ADC0 channels  | CH0 CH15                           |

| 8 ADC0 channels   | CH0 CH7                            |

| 8 ADC1 channels   | CH0 CH7                            |

| 5 CAN nodes       | CAN0, CAN1, CAN2, CAN3, CAN4       |

| 2 CAN nodes       | CAN0, CAN1                         |

| 6 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1 |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1             |

Data Sheet 7 V2.1, 2008-08

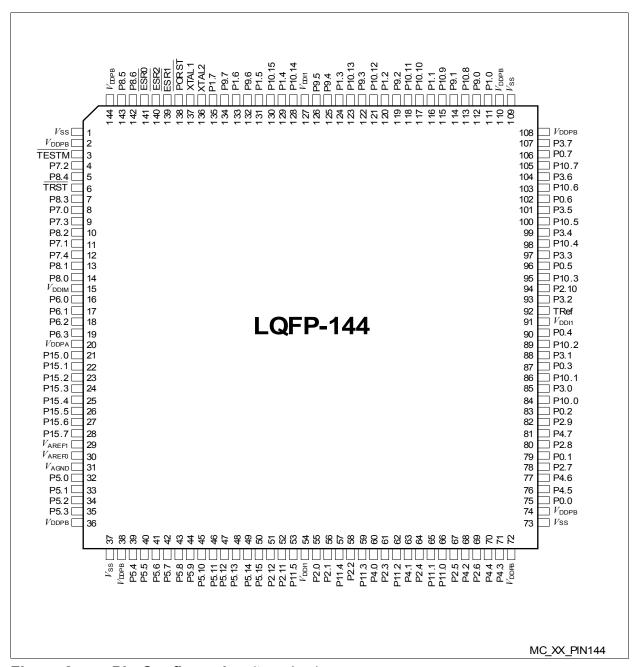

### 2.1 Pin Configuration and Definition

The pins of the XE167 are described in detail in **Table 4**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. **Figure 2** summarizes all pins, showing their locations on the four sides of the package.

Figure 2 Pin Configuration (top view)

Data Sheet 9 V2.1, 2008-08

#### **Notes to Pin Definitions**

- Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

- 2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

Table 4 Pin Definitions and Functions

| Iable | able 4 Fill Definitions and Functions |        |      |                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------|---------------------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                            |  |  |

| 3     | TESTM                                 | I      | In/B | $\begin{tabular}{ll} \textbf{Testmode Enable} \\ \textbf{Enables factory test modes, must be held HIGH for} \\ \textbf{normal operation (connect to $V_{\rm DDPB}$).} \\ \textbf{An internal pullup device will hold this pin high} \\ \textbf{when nothing is driving it.} \\ \end{tabular}$                                       |  |  |

| 4     | P7.2                                  | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                       |  |  |

|       | EMUX0                                 | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                         |  |  |

|       | TxDC4                                 | O2     | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                                                                                                                                                                     |  |  |

|       | CCU62_<br>CCPOS0A                     | 1      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                              |  |  |

|       | TDI_C                                 | I      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                |  |  |

| 5     | P8.4                                  | O0 / I | St/B | Bit 4 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                       |  |  |

|       | CCU60_<br>COUT61                      | O1     | St/B | CCU60 Channel 1 Output                                                                                                                                                                                                                                                                                                              |  |  |

|       | TMS_D                                 | I      | St/B | JTAG Test Mode Selection Input                                                                                                                                                                                                                                                                                                      |  |  |

| 6     | TRST                                  | I      | In/B | Test-System Reset Input For normal system operation, pin TRST should be held low. A high level at this pin at the rising edge of PORST activates the XE167's debug system. In this case, pin TRST must be driven low once to reset the debug system. An internal pulldown device will hold this pin low when nothing is driving it. |  |  |

| 7     | P8.3                                  | O0 / I | St/B | Bit 3 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                       |  |  |

|       | CCU60_<br>COUT60                      | O1     | St/B | CCU60 Channel 0 Output                                                                                                                                                                                                                                                                                                              |  |  |

|       | TDI_D                                 | I      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                |  |  |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |  |

|-----|------------------|--------|------|-----------------------------------------------|--|

| 18  | P6.2             | O0 / I | St/A | Bit 2 of Port 6, General Purpose Input/Output |  |

|     | EMUX2            | 01     | St/A | External Analog MUX Control Output 2 (ADC0)   |  |

|     | T6OUT            | O2     | St/A | GPT2 Timer T6 Toggle Latch Output             |  |

|     | U1C1_<br>SCLKOUT | О3     | St/A | USIC1 Channel 1 Shift Clock Output            |  |

|     | U1C1_DX1C        | I      | St/A | USIC1 Channel 1 Shift Clock Input             |  |

| 19  | P6.3             | O0 / I | St/A | Bit 3 of Port 6, General Purpose Input/Output |  |

|     | T3OUT            | O2     | St/A | GPT1 Timer T3 Toggle Latch Output             |  |

|     | U1C1_<br>SELO0   | O3     | St/A | USIC1 Channel 1 Select/Control 0 Output       |  |

|     | U1C1_DX2D        | I      | St/A | USIC1 Channel 1 Shift Control Input           |  |

|     | ADCx_<br>REQTRyD | I      | St/A | External Request Trigger Input for ADC0/1     |  |

| 21  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input       |  |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1               |  |

| 22  | P15.1            | I      | In/A | Bit 1 of Port 15, General Purpose Input       |  |

|     | ADC1_CH1         | I      | In/A | Analog Input Channel 1 for ADC1               |  |

| 23  | P15.2            | I      | In/A | Bit 2 of Port 15, General Purpose Input       |  |

|     | ADC1_CH2         | I      | In/A | Analog Input Channel 2 for ADC1               |  |

|     | T5IN             | I      | In/A | GPT2 Timer T5 Count/Gate Input                |  |

| 24  | P15.3            | 1      | In/A | Bit 3 of Port 15, General Purpose Input       |  |

|     | ADC1_CH3         | 1      | In/A | Analog Input Channel 3 for ADC1               |  |

|     | T5EUD            | I      | In/A | GPT2 Timer T5 External Up/Down Control Input  |  |

| 25  | P15.4            | I      | In/A | Bit 4 of Port 15, General Purpose Input       |  |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1               |  |

|     | T6IN             | I      | In/A | GPT2 Timer T6 Count/Gate Input                |  |

| 26  | P15.5            | I      | In/A | Bit 5 of Port 15, General Purpose Input       |  |

|     | ADC1_CH5         | I      | In/A | Analog Input Channel 5 for ADC1               |  |

|     | T6EUD            | I      | In/A | GPT2 Timer T6 External Up/Down Control Input  |  |

| 27  | P15.6            | I      | In/A | Bit 6 of Port 15, General Purpose Input       |  |

|     | ADC1_CH6         | I      | In/A | Analog Input Channel 6 for ADC1               |  |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl. | Туре | Function                                     |  |  |  |

|-----|------------------|-------|------|----------------------------------------------|--|--|--|

| 28  | P15.7            | I     | In/A | Bit 7 of Port 15, General Purpose Input      |  |  |  |

|     | ADC1_CH7         | I     | In/A | Analog Input Channel 7 for ADC1              |  |  |  |

| 29  | $V_{AREF1}$      | -     | PS/A | Reference Voltage for A/D Converter ADC1     |  |  |  |

| 30  | $V_{AREF0}$      | -     | PS/A | Reference Voltage for A/D Converter ADC0     |  |  |  |

| 31  | $V_{AGND}$       | -     | PS/A | Reference Ground for A/D Converters ADC0/1   |  |  |  |

| 32  | P5.0             | I     | In/A | Bit 0 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH0         | I     | In/A | Analog Input Channel 0 for ADC0              |  |  |  |

| 33  | P5.1             | I     | In/A | Bit 1 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH1         | I     | In/A | Analog Input Channel 1 for ADC0              |  |  |  |

| 34  | P5.2             | I     | In/A | Bit 2 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH2         | I     | In/A | Analog Input Channel 2 for ADC0              |  |  |  |

|     | TDI_A            | I     | In/A | JTAG Test Data Input                         |  |  |  |

| 35  | P5.3             | I     | In/A | Bit 3 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH3         | I     | In/A | Analog Input Channel 3 for ADC0              |  |  |  |

|     | T3IN             | I     | In/A | GPT1 Timer T3 Count/Gate Input               |  |  |  |

| 39  | P5.4             | I     | In/A | Bit 4 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH4         | I     | In/A | Analog Input Channel 4 for ADC0              |  |  |  |

|     | CCU63_<br>T12HRB | I     | In/A | External Run Control Input for T12 of CCU63  |  |  |  |

|     | T3EUD            | I     | In/A | GPT1 Timer T3 External Up/Down Control Input |  |  |  |

|     | TMS_A            | I     | In/A | JTAG Test Mode Selection Input               |  |  |  |

| 40  | P5.5             | I     | In/A | Bit 5 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH5         | I     | In/A | Analog Input Channel 5 for ADC0              |  |  |  |

|     | CCU60_<br>T12HRB | 1     | In/A | External Run Control Input for T12 of CCU60  |  |  |  |

| 41  | P5.6             | I     | In/A | Bit 6 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH6         | I     | In/A | Analog Input Channel 6 for ADC0              |  |  |  |

| 42  | P5.7             | I     | In/A | Bit 7 of Port 5, General Purpose Input       |  |  |  |

|     | ADC0_CH7         | I     | In/A | Analog Input Channel 7 for ADC0              |  |  |  |

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 5**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**Up to 768 Kbytes of on-chip Flash memory** store code, constant data, and control data. The on-chip Flash memory consists of up to three modules with a maximum capacity of 256 Kbytes each. Each module is organized in 4-Kbyte sectors.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen derivative (see **Table 1**).

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see **Section 4.5**.

Data Sheet 39 V2.1, 2008-08

<sup>1)</sup> To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

## 3.4 Interrupt System

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks (in the case of internal program execution), the XE167 can react quickly to the occurrence of non-deterministic events.

The architecture of the XE167 supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Where in a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XE167 has eight PEC channels, each whith fast interrupt-driven data transfer capabilities.

Each of the possible interrupt nodes has a separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield. Each node can be programmed by its related register to one of sixteen interrupt priority levels. Once accepted by the CPU, an interrupt service can only be interrupted by a higher-priority service request. For standard interrupt processing, each possible interrupt node has a dedicated vector location.

Fast external interrupt inputs can service external interrupts with high-precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge, or both edges).

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 6** shows all of the possible XE167 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not assigned to peripherals (unassigned nodes) may be used to generate software-controlled interrupt requests by setting the respective interrupt request bit (xIR).

Data Sheet 43 V2.1, 2008-08

<sup>1)</sup> Depending if the jump cache is used or not.

# XE167x XE166 Family Derivatives

# **Functional Description**

Table 6 XE167 Interrupt Nodes

| Source of Interrupt or PEC Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|--------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 16, or ERU Request 0       | CC2_CC16IC          | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |

| CAPCOM Register 17, or ERU Request 1       | CC2_CC17IC          | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |

| CAPCOM Register 18, or ERU Request 2       | CC2_CC18IC          | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |

| CAPCOM Register 19, or ERU Request 3       | CC2_CC19IC          | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |

| CAPCOM Register 20, or USIC0 Request 6     | CC2_CC20IC          | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |

| CAPCOM Register 21, or USIC0 Request 7     | CC2_CC21IC          | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |

| CAPCOM Register 22, or USIC1 Request 6     | CC2_CC22IC          | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |

| CAPCOM Register 23, or USIC1 Request 7     | CC2_CC23IC          | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |

| CAPCOM Register 24, or ERU Request 0       | CC2_CC24IC          | xx'0060 <sub>H</sub>             | 18 <sub>H</sub> / 24 <sub>D</sub> |

| CAPCOM Register 25, or ERU Request 1       | CC2_CC25IC          | xx'0064 <sub>H</sub>             | 19 <sub>H</sub> / 25 <sub>D</sub> |

| CAPCOM Register 26, or ERU Request 2       | CC2_CC26IC          | xx'0068 <sub>H</sub>             | 1A <sub>H</sub> / 26 <sub>D</sub> |

| CAPCOM Register 27, or ERU Request 3       | CC2_CC27IC          | xx'006C <sub>H</sub>             | 1B <sub>H</sub> / 27 <sub>D</sub> |

| CAPCOM Register 28, or USIC2 Request 6     | CC2_CC28IC          | xx'0070 <sub>H</sub>             | 1C <sub>H</sub> / 28 <sub>D</sub> |

| CAPCOM Register 29, or USIC2 Request 7     | CC2_CC29IC          | xx'0074 <sub>H</sub>             | 1D <sub>H</sub> / 29 <sub>D</sub> |

| CAPCOM Register 30                         | CC2_CC30IC          | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |

| CAPCOM Register 31                         | CC2_CC31IC          | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |

| GPT1 Timer 2                               | GPT12E_T2IC         | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| GPT1 Timer 3                               | GPT12E_T3IC         | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| GPT1 Timer 4                               | GPT12E_T4IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

# XE167x XE166 Family Derivatives

# **Functional Description**

Table 6 XE167 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAN Request 1                                 | CAN_1IC             | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| CAN Request 2                                 | CAN_2IC             | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

| CAN Request 3                                 | CAN_3IC             | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| CAN Request 4                                 | CAN_4IC             | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAN Request 5                                 | CAN_5IC             | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAN Request 6                                 | CAN_6IC             | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAN Request 7                                 | CAN_7IC             | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| CAN Request 8                                 | CAN_8IC             | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| CAN Request 9                                 | CAN_9IC             | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| CAN Request 10                                | CAN_10IC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

| CAN Request 11                                | CAN_11IC            | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| CAN Request 12                                | CAN_12IC            | xx'0130 <sub>H</sub>             | 4C <sub>H</sub> / 76 <sub>D</sub> |

| CAN Request 13                                | CAN_13IC            | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |

| CAN Request 14                                | CAN_14IC            | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAN Request 15                                | CAN_15IC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| USIC0 Cannel 0, Request 0                     | U0C0_0IC            | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| USIC0 Cannel 0, Request 1                     | U0C0_1IC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| USIC0 Cannel 0, Request 2                     | U0C0_2IC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| USIC0 Cannel 1, Request 0                     | U0C1_0IC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| USIC0 Cannel 1, Request 1                     | U0C1_1IC            | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| USIC0 Cannel 1, Request 2                     | U0C1_2IC            | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| USIC1 Cannel 0, Request 0                     | U1C0_0IC            | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| USIC1 Cannel 0, Request 1                     | U1C0_1IC            | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| USIC1 Cannel 0, Request 2                     | U1C0_2IC            | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

| USIC1 Cannel 1, Request 0                     | U1C1_0IC            | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| USIC1 Cannel 1, Request 1                     | U1C1_1IC            | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| USIC1 Cannel 1, Request 2                     | U1C1_2IC            | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| USIC2 Cannel 0, Request 0                     | U2C0_0IC            | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| USIC2 Cannel 0, Request 1                     | U2C0_1IC            | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| USIC2 Cannel 0, Request 2                     | U2C0_2IC            | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

The XE167 includes an excellent mechanism to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate non-maskable system reaction similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

**Table 7** shows all possible exceptions or error conditions that can arise during runtime:

Table 7 Trap Summary

| <b>Exception Condition</b>                                                                                                                 | Trap<br>Flag                              | Trap<br>Vector                            | Vector<br>Location <sup>1)</sup>                                                                                     | Trap<br>Number                                                           | Trap<br>Priority           |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|

| Reset Functions                                                                                                                            | _                                         | RESET                                     | xx'0000 <sub>H</sub>                                                                                                 | 00 <sub>H</sub>                                                          | Ш                          |

| Class A Hardware Traps:  System Request 0  Stack Overflow  Stack Underflow  Software Break                                                 | SR0<br>STKOF<br>STKUF<br>SOFTBRK          | SR0TRAP<br>STOTRAP<br>STUTRAP<br>SBRKTRAP | xx'0008 <sub>H</sub><br>xx'0010 <sub>H</sub><br>xx'0018 <sub>H</sub><br>xx'0020 <sub>H</sub>                         | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub><br>08 <sub>H</sub> |                            |

| Class B Hardware Traps:  System Request 1  Undefined Opcode  Memory Access Error  Protected Instruction Fault  Illegal Word Operand Access | SR1<br>UNDOPC<br>ACER<br>PRTFLT<br>ILLOPA | BTRAP<br>BTRAP<br>BTRAP<br>BTRAP<br>BTRAP | xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub> | 0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub> | <br>                       |

| Reserved                                                                                                                                   | _                                         | _                                         | [2C <sub>H</sub> - 3C <sub>H</sub> ]                                                                                 | [0B <sub>H</sub> - 0F <sub>H</sub> ]                                     | _                          |

| Software Traps: • TRAP Instruction                                                                                                         | _                                         | _                                         | Any<br>[xx'0000 <sub>H</sub> -<br>xx'01FC <sub>H</sub> ]<br>in steps of<br>4 <sub>H</sub>                            | Any<br>[00 <sub>H</sub> -<br>7F <sub>H</sub> ]                           | Current<br>CPU<br>Priority |

Register VECSEG defines the segment where the vector table is located to.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

Data Sheet 48 V2.1, 2008-08

### 3.8 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

Data Sheet 55 V2.1, 2008-08

#### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- maximum baud rate:  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- maximum baud rate:  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI/QSPI (synchronous serial channel with or without data buffer)

- maximum baud rate in slave mode:  $f_{SYS}$

- maximum baud rate in master mode:  $f_{\rm SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- maximum baud rate:  $f_{\rm SYS}$  / 2 for transmitter,  $f_{\rm SYS}$  for receiver

Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

Data Sheet 63 V2.1, 2008-08

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XE167 into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Table 20 Various System Parameters

| Parameter                                                 | Symbol                 |                         | Values   |                         |     | Values                                                |  |  | Note / |

|-----------------------------------------------------------|------------------------|-------------------------|----------|-------------------------|-----|-------------------------------------------------------|--|--|--------|

|                                                           |                        | Min.                    | Тур.     | Max.                    |     | Test Condition                                        |  |  |        |

| Supply watchdog (SWD) supervision level (see Table 21)    | V <sub>SWD</sub><br>CC | V <sub>LV</sub> - 0.150 | $V_{LV}$ | V <sub>LV</sub> + 0.100 | V   | $V_{\rm LV}$ = selected voltage in upper voltage area |  |  |        |

|                                                           |                        | V <sub>LV</sub> - 0.125 | $V_{LV}$ | V <sub>LV</sub> + 0.050 | V   | $V_{\rm LV}$ = selected voltage in lower voltage area |  |  |        |

| Core voltage (PVC)<br>supervision level<br>(see Table 22) | V <sub>PVC</sub> CC    | V <sub>LV</sub> - 0.070 | $V_{LV}$ | V <sub>LV</sub> + 0.030 | V   | $V_{\rm LV}$ = selected voltage                       |  |  |        |

| Current control limit                                     | $I_{\rm CC}$ CC        | 13                      | _        | 30                      | mA  | Power domain DMP_M                                    |  |  |        |

|                                                           |                        | 90                      | _        | 150                     | mA  | Power domain DMP_1                                    |  |  |        |

| Wakeup clock source frequency                             | $f_{WU}CC$             | 400                     | 500      | 600                     | kHz | FREQSEL<br>= 00 <sub>B</sub>                          |  |  |        |

| Internal clock source frequency                           | $f_{INT}CC$            | 4.8                     | 5.0      | 5.2                     | MHz |                                                       |  |  |        |

| Startup time from stopover mode                           | $t_{\rm SSO}$ CC       | 200                     | 260      | 320                     | μS  | User instruction from PSRAM                           |  |  |        |

## 4.6.2 Definition of Internal Timing

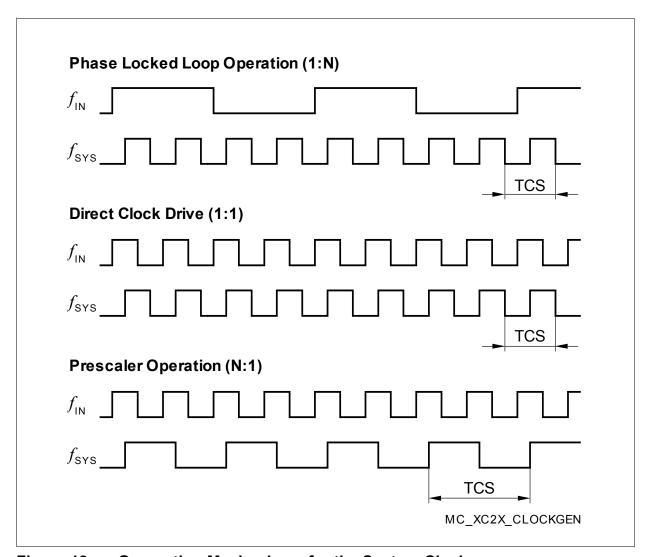

The internal operation of the XE167 is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE167.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

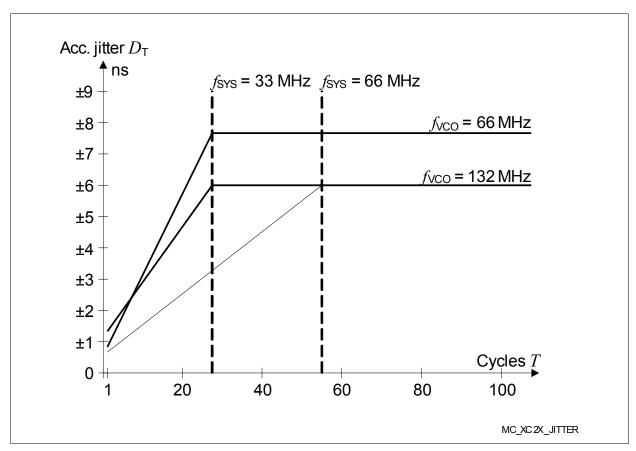

Figure 19 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_1$  = 20 pF (see **Table 12**).

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{\rm DDPB}$  pin 100/144 and  $V_{\rm SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{\rm PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

Table 25 VCO Bands for PLL Operation<sup>1)</sup>

| PLLCON0.VCOSEL | VCO Frequency Range | Base Frequency Range |

|----------------|---------------------|----------------------|

| 00             | 50 110 MHz          | 10 40 MHz            |

| 01             | 100 160 MHz         | 20 80 MHz            |

| 1X             | Reserved            |                      |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

Table 29 External Bus Cycle Timing for Upper Voltage Range (Operating Conditions apply)

| Parameter                                                       | Symbol                    | Limits |      |      | Unit | Note |

|-----------------------------------------------------------------|---------------------------|--------|------|------|------|------|

|                                                                 |                           | Min.   | Тур. | Max. |      |      |

| Output valid delay for:<br>RD, WR(L/H)                          | t <sub>10</sub> CC        | _      |      | 13   | ns   |      |

| Output valid delay for:<br>BHE, ALE                             | <i>t</i> <sub>11</sub> CC | _      |      | 13   | ns   |      |

| Output valid delay for:<br>A23 A16, A15 A0 (on P0/P1)           | <i>t</i> <sub>12</sub> CC | _      |      | 14   | ns   |      |

| Output valid delay for:<br>A15 A0 (on P2/P10)                   | <i>t</i> <sub>13</sub> CC | _      |      | 14   | ns   |      |

| Output valid delay for:<br>CS                                   | t <sub>14</sub> CC        | _      |      | 13   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, MUX-mode)        | t <sub>15</sub> CC        | _      |      | 14   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, DEMUX-<br>mode)  | t <sub>16</sub> CC        | _      |      | 14   | ns   |      |

| Output hold time for:<br>RD, WR(L/H)                            | t <sub>20</sub> CC        | 0      |      | 8    | ns   |      |

| Output hold time for:<br>BHE, ALE                               | t <sub>21</sub> CC        | 0      |      | 8    | ns   |      |

| Output hold time for:<br>A23 A16, A15 A0 (on P2/P10)            | <i>t</i> <sub>23</sub> CC | 0      |      | 8    | ns   |      |

| Output hold time for:<br>CS                                     | t <sub>24</sub> CC        | 0      |      | 8    | ns   |      |

| Output hold time for:<br>D15 D0 (write data)                    | t <sub>25</sub> CC        | 0      |      | 8    | ns   |      |

| Input setup time for:<br>READY, D15 D0 (read data)              | t <sub>30</sub> SR        | 18     |      | _    | ns   |      |

| Input hold time for:<br>READY, D15 D0 (read data) <sup>1)</sup> | t <sub>31</sub> SR        | -4     |      | _    | ns   |      |

<sup>1)</sup> Read data are latched with the same internal clock edge that triggers the address change and the rising edge of  $\overline{RD}$ . Address changes before the end of  $\overline{RD}$  have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of  $\overline{RD}$ .

#### **External Bus Arbitration**

If the arbitration signals are enabled, the XE167 makes its external resources available in response to an arbitration request.

Table 31 Bus Arbitration Timing for Upper Voltage Range (Operating Conditions apply)

| Parameter                                | Symbol             | Limits |      |      | Unit | Note |

|------------------------------------------|--------------------|--------|------|------|------|------|

|                                          |                    | Min.   | Тур. | Max. |      |      |

| Input setup time for: HOLD input         | t <sub>40</sub> SR | 18     |      | -    | ns   |      |

| Output delay rising edge for: HLDA, BREQ | t <sub>41</sub> CC | 0      |      | 13   | ns   |      |

| Output delay falling edge for: HLDA      | t <sub>42</sub> CC | 1      |      | 14   | ns   |      |

Table 32 Bus Arbitration Timing for Lower Voltage Range (Operating Conditions apply)

| Parameter                                | Symbol                    | Limits |      |      | Unit | Note |

|------------------------------------------|---------------------------|--------|------|------|------|------|

|                                          |                           | Min.   | Тур. | Max. |      |      |

| Input setup time for: HOLD input         | <i>t</i> <sub>40</sub> SR | 28     |      | _    | ns   |      |

| Output delay rising edge for: HLDA, BREQ | t <sub>41</sub> CC        | 0      |      | 19   | ns   |      |

| Output delay falling edge for: HLDA      | t <sub>42</sub> CC        | 1      |      | 21   | ns   |      |

Data Sheet 109 V2.1, 2008-08

## 4.6.5 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Table 33 SSC Master/Slave Mode Timing for Upper Voltage Range (Operating Conditions apply),  $C_1 = 50 \text{ pF}$

| Parameter                                                         | Symbol                    | Values                   |      |      | Unit | Note /          |

|-------------------------------------------------------------------|---------------------------|--------------------------|------|------|------|-----------------|

|                                                                   |                           | Min.                     | Тур. | Max. | 1    | Test Co ndition |

| Master Mode Timing                                                |                           | 1                        |      |      | •    |                 |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC         | 0                        | _    | 1)   | ns   | 2)              |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC         | $0.5 \times t_{\rm BIT}$ | _    | 3)   | ns   |                 |

| Transmit data output valid time                                   | t <sub>3</sub> CC         | -6                       | _    | 13   | ns   |                 |

| Receive data input setup time to SCLKOUT receive edge             | t <sub>4</sub> SR         | 31                       | _    | _    | ns   |                 |

| Data input DX0 hold time from SCLKOUT receive edge                | t <sub>5</sub> SR         | -7                       | _    | _    | ns   |                 |

| Slave Mode Timing                                                 | l                         | 1                        |      |      |      |                 |

| Select input DX2 setup to first clock input DX1 transmit edge     | <i>t</i> <sub>10</sub> SR | 7                        | _    | _    | ns   | 4)              |

| Select input DX2 hold after last clock input DX1 receive edge     | <i>t</i> <sub>11</sub> SR | 5                        | _    | _    | ns   | 7)              |

| Data input DX0 setup time to clock input DX1 receive edge         | <i>t</i> <sub>12</sub> SR | 7                        | _    | _    | ns   | 7)              |

| Data input DX0 hold time from clock input DX1 receive edge        | <i>t</i> <sub>13</sub> SR | 5                        | _    | _    | ns   | 7)              |

| Data output DOUT valid time                                       | t <sub>14</sub> CC        | 8                        | _    | 29   | ns   | 7)              |

<sup>1)</sup> The maximum value further depends on the settings for the slave select output leading delay.

Data Sheet 112 V2.1, 2008-08

<sup>2)</sup>  $t_{SYS} = 1/f_{SYS}$  (= 12.5 ns @ 80 MHz)

<sup>3)</sup> The maximum value depends on the settings for the slave select output trailing delay and for the shift clock output delay.

<sup>4)</sup> These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

## Package and Reliability

#### 5.2 Thermal Considerations

When operating the XE167 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 125 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{\text{INT}} + P_{\text{IOSTAT}} + P_{\text{IODYN}}) \times R_{\Theta,\text{JA}}$

The internal power consumption is defined as  $P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (see **Section 4.2.3**).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\mathsf{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\rm DDP}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

Data Sheet 119 V2.1, 2008-08