Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 118                                                                             |

| Program Memory Size        | 576KB (576K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 50K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-144-4                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe167f72f66lacfxqma1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

| Table 1 XE167 Derivative Synopsis |                    |                                 |                     |               |                            |                                |  |

|-----------------------------------|--------------------|---------------------------------|---------------------|---------------|----------------------------|--------------------------------|--|

| Derivative <sup>1)</sup>          | Temp.<br>Range     | Program<br>Memory <sup>2)</sup> | PSRAM <sup>3)</sup> | CCU6<br>Mod.  | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>       |  |

| SAF-XE167F-<br>48F66L             | -40 °C to<br>85 °C | 384 Kbytes<br>Flash             | 16 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | 5 CAN Nodes,<br>6 Serial Chan. |  |

| SAF-XE167F-<br>72F66L             | -40 °C to<br>85 °C | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | 5 CAN Nodes,<br>6 Serial Chan. |  |

| SAF-XE167F-<br>96FxxL             | -40 °C to<br>85 °C | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | 5 CAN Nodes,<br>6 Serial Chan. |  |

| SAF-XE167G-<br>48F66L             | -40 °C to<br>85 °C | 384 Kbytes<br>Flash             | 16 Kbytes           | 0, 1          | 8 + 8                      | 2 CAN Nodes,<br>4 Serial Chan. |  |

| SAF-XE167G-<br>72F66L             | -40 °C to<br>85 °C | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1          | 8 + 8                      | 2 CAN Nodes,<br>4 Serial Chan. |  |

| SAF-XE167G-<br>96F66L             | -40 °C to<br>85 °C | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1          | 8 + 8                      | 2 CAN Nodes,<br>4 Serial Chan. |  |

| SAF-XE167H-<br>48F66L             | -40 °C to<br>85 °C | 384 Kbytes<br>Flash             | 16 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | No CAN Node,<br>6 Serial Chan. |  |

| SAF-XE167H-<br>72F66L             | -40 °C to<br>85 °C | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | No CAN Node,<br>6 Serial Chan. |  |

| SAF-XE167H-<br>96F66L             | -40 °C to<br>85 °C | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1,<br>2, 3 | 16 + 8                     | No CAN Node,<br>6 Serial Chan. |  |

| SAF-XE167K-<br>48F66L             | -40 °C to<br>85 °C | 384 Kbytes<br>Flash             | 16 Kbytes           | 0, 1          | 8 + 8                      | No CAN Node,<br>4 Serial Chan. |  |

| SAF-XE167K-<br>72F66L             | -40 °C to<br>85 °C | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1          | 8 + 8                      | No CAN Node,<br>4 Serial Chan. |  |

| SAF-XE167K-<br>96F66L             | -40 °C to<br>85 °C | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1          | 8 + 8                      | No CAN Node,<br>4 Serial Chan. |  |

1) This Data Sheet is valid for devices starting with and including design step AC.

2) Specific inormation about the on-chip Flash memory in **Table 2**.

3) All derivatives additionally provide 1 Kbyte SBRAM, 2 Kbytes DPRAM, and 16 Kbytes DSRAM.

4) Specific information about the available channels in **Table 3**. Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin       | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3         | TESTM             | I      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pullup device will hold this pin highwhen nothing is driving it.                                                                                                                                                                   |

| 4         | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                     |

|           | TxDC4             | 02     | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                                                                                                                                                                                                 |

|           | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                          |

|           | TDI_C             | Ι      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |

| 5         | P8.4              | O0 / I | St/B | Bit 4 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | CCU60_<br>COUT61  | 01     | St/B | CCU60 Channel 1 Output                                                                                                                                                                                                                                                                                                                                          |

|           | TMS_D             | I      | St/B | JTAG Test Mode Selection Input                                                                                                                                                                                                                                                                                                                                  |

| 6         | TRST              |        | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE167's debug system. In<br>this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |

| 7         | P8.3              | O0 / I | St/B | Bit 3 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | CCU60_<br>COUT60  | 01     | St/B | CCU60 Channel 0 Output                                                                                                                                                                                                                                                                                                                                          |

| . <u></u> | TDI_D             | Ι      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |

#### Table 4Pin Definitions and Functions

| Table | Fable 4Pin Definitions and Functions (cont'd) |        |      |                                               |  |

|-------|-----------------------------------------------|--------|------|-----------------------------------------------|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                      |  |

| 79    | P0.1                                          | O0 / I | St/B | Bit 1 of Port 0, General Purpose Input/Output |  |

|       | U1C0_DOUT                                     | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |

|       | TxDC0                                         | 02     | St/B | CAN Node 0 Transmit Data Output               |  |

|       | CCU61_<br>CC61                                | O3 / I | St/B | CCU61 Channel 1 Input/Output                  |  |

|       | A1                                            | OH     | St/B | External Bus Interface Address Line 1         |  |

|       | U1C0_DX0B                                     | Ι      | St/B | USIC1 Channel 0 Shift Data Input              |  |

| _     | U1C0_DX1A                                     | 1      | St/B | USIC1 Channel 0 Shift Clock Input             |  |

| 80    | P2.8                                          | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output |  |

|       | U0C1_<br>SCLKOUT                              | O1     | DP/B | USIC0 Channel 1 Shift Clock Output            |  |

|       | EXTCLK                                        | O2     | DP/B | Programmable Clock Signal Output              |  |

|       | CC2_21                                        | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.     |  |

|       | A21                                           | OH     | DP/B | External Bus Interface Address Line 21        |  |

| _     | U0C1_DX1D                                     | 1      | DP/B | USIC0 Channel 1 Shift Clock Input             |  |

| 81    | P4.7                                          | O0 / I | St/B | Bit 7 of Port 4, General Purpose Input/Output |  |

|       | CC2_31                                        | O3 / I | St/B | CAPCOM2 CC31IO Capture Inp./ Compare Out.     |  |

| _     | T4EUD                                         | 1      | St/B | GPT1 Timer T4 External Up/Down Control Input  |  |

| 82    | P2.9                                          | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output             |  |

|       | TxDC1                                         | 02     | St/B | CAN Node 1 Transmit Data Output               |  |

|       | CC2_22                                        | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.     |  |

|       | A22                                           | OH     | St/B | External Bus Interface Address Line 22        |  |

|       | CLKIN1                                        | 1      | St/B | Clock Signal Input                            |  |

|       | TCK_A                                         | 1      | St/B | JTAG Clock Input                              |  |

| Tabl | Fable 4Pin Definitions and Functions (cont'd) |        |      |                                                |  |

|------|-----------------------------------------------|--------|------|------------------------------------------------|--|

| Pin  | Symbol                                        | Ctrl.  | Туре | Function                                       |  |

| 92   | TRef                                          | Ю      | Sp/1 | <b>Control Pin for Core Voltage Generation</b> |  |

| 93   | P3.2                                          | O0 / I | St/B | Bit 2 of Port 3, General Purpose Input/Output  |  |

|      | U2C0_<br>SCLKOUT                              | 01     | St/B | USIC2 Channel 0 Shift Clock Output             |  |

|      | TxDC3                                         | 02     | St/B | CAN Node 3 Transmit Data Output                |  |

|      | U2C0_DX1B                                     | I      | St/B | USIC2 Channel 0 Shift Clock Input              |  |

| _    | HOLD                                          | l      | St/B | External Bus Master Hold Request Input         |  |

| 94   | P2.10                                         | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |

|      | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |

|      | U0C0_<br>SELO3                                | 02     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |

|      | CC2_23                                        | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |

|      | A23                                           | OH     | St/B | External Bus Interface Address Line 23         |  |

|      | U0C1_DX0E                                     | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |

| _    | CAPIN                                         | l      | St/B | GPT2 Register CAPREL Capture Input             |  |

| 95   | P10.3                                         | O0 / I | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |

|      | CCU60_<br>COUT60                              | O2     | St/B | CCU60 Channel 0 Output                         |  |

|      | AD3                                           | OH/I   | St/B | External Bus Interface Address/Data Line 3     |  |

|      | U0C0_DX2A                                     | I      | St/B | USIC0 Channel 0 Shift Control Input            |  |

|      | U0C1_DX2A                                     | I      | St/B | USIC0 Channel 1 Shift Control Input            |  |

| 96   | P0.5                                          | O0 / I | St/B | Bit 5 of Port 0, General Purpose Input/Output  |  |

|      | U1C1_<br>SCLKOUT                              | 01     | St/B | USIC1 Channel 1 Shift Clock Output             |  |

|      | U1C0_<br>SELO2                                | 02     | St/B | USIC1 Channel 0 Select/Control 2 Output        |  |

|      | CCU61_<br>COUT62                              | O3     | St/B | CCU61 Channel 2 Output                         |  |

|      | A5                                            | OH     | St/B | External Bus Interface Address Line 5          |  |

|      | U1C1_DX1A                                     | I      | St/B | USIC1 Channel 1 Shift Clock Input              |  |

|      | U1C0_DX1C                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input              |  |

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |

|-------|-----------------------------------------------|--------|------|-------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                        |  |  |

| 115   | P10.9                                         | O0 / I | St/B | Bit 9 of Port 10, General Purpose Input/Output  |  |  |

|       | U0C0_<br>SELO4                                | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output         |  |  |

|       | U0C1_<br>MCLKOUT                              | O2     | St/B | USIC0 Channel 1 Master Clock Output             |  |  |

|       | AD9                                           | OH/I   | St/B | External Bus Interface Address/Data Line 9      |  |  |

|       | CCU60_<br>CCPOS2A                             | I      | St/B | CCU60 Position Input 2                          |  |  |

|       | TCK_B                                         | 1      | St/B | JTAG Clock Input                                |  |  |

| 116   | P1.1                                          | O0 / I | St/B | Bit 1 of Port 1, General Purpose Input/Output   |  |  |

|       | CCU62_<br>COUT62                              | O1     | St/B | CCU62 Channel 2 Output                          |  |  |

|       | U1C0_<br>SELO5                                | O2     | St/B | USIC1 Channel 0 Select/Control 5 Output         |  |  |

|       | U2C1_DOUT                                     | O3     | St/B | USIC2 Channel 1 Shift Data Output               |  |  |

|       | A9                                            | OH     | St/B | External Bus Interface Address Line 9           |  |  |

|       | ESR2_3                                        | 1      | St/B | ESR2 Trigger Input 3                            |  |  |

|       | EX1BINA                                       | 1      | St/B | External Interrupt Trigger Input                |  |  |

| _     | U2C1_DX0C                                     | 1      | St/B | USIC2 Channel 1 Shift Data Input                |  |  |

| 117   | P10.10                                        | O0 / I | St/B | Bit 10 of Port 10, General Purpose Input/Output |  |  |

|       | U0C0_<br>SELO0                                | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output         |  |  |

|       | CCU60_<br>COUT63                              | O2     | St/B | CCU60 Channel 3 Output                          |  |  |

|       | AD10                                          | OH/I   | St/B | External Bus Interface Address/Data Line 10     |  |  |

|       | U0C0_DX2C                                     | I      | St/B | USIC0 Channel 0 Shift Control Input             |  |  |

|       | TDI_B                                         | I      | St/B | JTAG Test Data Input                            |  |  |

|       | U0C1_DX1A                                     | Ι      | St/B | USIC0 Channel 1 Shift Clock Input               |  |  |

| Table | Fable 4Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |

|-------|-----------------------------------------------|--------|------|-------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                        |  |  |

| 118   | P10.11                                        | O0 / I | St/B | Bit 11 of Port 10, General Purpose Input/Output |  |  |

|       | U1C0_<br>SCLKOUT                              | O1     | St/B | USIC1 Channel 0 Shift Clock Output              |  |  |

|       | BRKOUT                                        | O2     | St/B | OCDS Break Signal Output                        |  |  |

|       | AD11                                          | OH/I   | St/B | External Bus Interface Address/Data Line 11     |  |  |

|       | U1C0_DX1D                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input               |  |  |

|       | RxDC2B                                        | 1      | St/B | CAN Node 2 Receive Data Input                   |  |  |

|       | TMS_B                                         | 1      | St/B | JTAG Test Mode Selection Input                  |  |  |

| 119   | P9.2                                          | O0 / I | St/B | Bit 2 of Port 9, General Purpose Input/Output   |  |  |

|       | CCU63_<br>CC62                                | O1 / I | St/B | CCU63 Channel 2 Input/Output                    |  |  |

| 120   | P1.2                                          | O0 / I | St/B | Bit 2 of Port 1, General Purpose Input/Output   |  |  |

|       | CCU62_<br>CC62                                | 01/1   | St/B | CCU62 Channel 2 Input/Output                    |  |  |

|       | U1C0_<br>SELO6                                | O2     | St/B | USIC1 Channel 0 Select/Control 6 Output         |  |  |

|       | U2C1_<br>SCLKOUT                              | O3     | St/B | USIC2 Channel 1 Shift Clock Output              |  |  |

|       | A10                                           | OH     | St/B | External Bus Interface Address Line 10          |  |  |

|       | ESR1_4                                        | 1      | St/B | ESR1 Trigger Input 4                            |  |  |

|       | CCU61_<br>T12HRB                              | 1      | St/B | External Run Control Input for T12 of CCU61     |  |  |

|       | EX2AINA                                       | I      | St/B | External Interrupt Trigger Input                |  |  |

|       | U2C1_DX0D                                     | I      | St/B | USIC2 Channel 1 Shift Data Input                |  |  |

|       | U2C1_DX1C                                     | I      | St/B | USIC2 Channel 1 Shift Clock Input               |  |  |

| 121   | P10.12                                        | O0 / I | St/B | Bit 12 of Port 10, General Purpose Input/Output |  |  |

|       | U1C0_DOUT                                     | 01     | St/B | USIC1 Channel 0 Shift Data Output               |  |  |

|       | TxDC2                                         | 02     | St/B | CAN Node 2 Transmit Data Output                 |  |  |

|       | TDO_B                                         | O3     | St/B | JTAG Test Data Output                           |  |  |

|       | AD12                                          | OH/I   | St/B | External Bus Interface Address/Data Line 12     |  |  |

|       | U1C0_DX0C                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                |  |  |

|       | U1C0_DX1E                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input               |  |  |

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |

|-------|-----------------------------------------------|--------|------|-----------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                      |  |  |

| 131   | P1.5                                          | O0 / I | St/B | Bit 5 of Port 1, General Purpose Input/Output |  |  |

|       | CCU62_<br>COUT60                              | 01     | St/B | CCU62 Channel 0 Output                        |  |  |

|       | U1C1_<br>SELO3                                | O2     | St/B | USIC1 Channel 1 Select/Control 3 Output       |  |  |

|       | BRKOUT                                        | O3     | St/B | OCDS Break Signal Output                      |  |  |

|       | A13                                           | OH     | St/B | External Bus Interface Address Line 13        |  |  |

|       | U2C0_DX0C                                     | I      | St/B | USIC2 Channel 0 Shift Data Input              |  |  |

| 132   | P9.6                                          | O0 / I | St/B | Bit 6 of Port 9, General Purpose Input/Output |  |  |

|       | CCU63_<br>COUT63                              | 01     | St/B | CCU63 Channel 3 Output                        |  |  |

|       | CCU63_<br>COUT62                              | O2     | St/B | CCU63 Channel 2 Output                        |  |  |

| _     | CCU63 _<br>CTRAPA                             | I      | St/B | CCU63 Emergency Trap Input                    |  |  |

|       | CCU60_<br>CCPOS1B                             | I      | St/B | CCU60 Position Input 1                        |  |  |

| 133   | P1.6                                          | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output |  |  |

|       | CCU62_<br>CC61                                | 01/1   | St/B | CCU62 Channel 1 Input/Output                  |  |  |

|       | U1C1_<br>SELO2                                | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output       |  |  |

|       | U2C0_DOUT                                     | O3     | St/B | USIC2 Channel 0 Shift Data Output             |  |  |

|       | A14                                           | OH     | St/B | External Bus Interface Address Line 14        |  |  |

|       | U2C0_DX0D                                     | I      | St/B | USIC2 Channel 0 Shift Data Input              |  |  |

| 134   | P9.7                                          | O0 / I | St/B | Bit 7 of Port 9, General Purpose Input/Output |  |  |

|       | CCU63_<br>CTRAPB                              | I      | St/B | CCU63 Emergency Trap Input                    |  |  |

|       | U2C0_DX1D                                     | I      | St/B | USIC2 Channel 0 Shift Clock Input             |  |  |

|       | CCU60_<br>CCPOS0B                             | I      | St/B | CCU60 Position Input 0                        |  |  |

The XE167 includes an excellent mechanism to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate non-maskable system reaction similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Table 7 shows all possible exceptions or error conditions that can arise during runtime:

| Exception Condition                                                                                                                                                                                            | Trap<br>Flag                              | Trap<br>Vector                            | Vector<br>Location <sup>1)</sup>                                                                                                             | Trap<br>Number                                                           | Trap<br>Priority           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|

| Reset Functions                                                                                                                                                                                                | _                                         | RESET                                     | xx'0000 <sub>H</sub>                                                                                                                         | 00 <sub>H</sub>                                                          | III                        |

| <ul> <li>Class A Hardware Traps:</li> <li>System Request 0</li> <li>Stack Overflow</li> <li>Stack Underflow</li> <li>Software Break</li> </ul>                                                                 | SR0<br>STKOF<br>STKUF<br>SOFTBRK          | SR0TRAP<br>STOTRAP<br>STUTRAP<br>SBRKTRAP | xx'0008 <sub>H</sub><br>xx'0010 <sub>H</sub><br>xx'0018 <sub>H</sub><br>xx'0020 <sub>H</sub>                                                 | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub><br>08 <sub>H</sub> | <br>  <br>                 |

| <ul> <li>Class B Hardware Traps:</li> <li>System Request 1</li> <li>Undefined Opcode</li> <li>Memory Access Error</li> <li>Protected Instruction<br/>Fault</li> <li>Illegal Word Operand<br/>Access</li> </ul> | SR1<br>UNDOPC<br>ACER<br>PRTFLT<br>ILLOPA | BTRAP<br>BTRAP<br>BTRAP<br>BTRAP<br>BTRAP | xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub> | 0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub> | <br> <br> <br>             |

| Reserved                                                                                                                                                                                                       | -                                         | -                                         | [2C <sub>H</sub> - 3C <sub>H</sub> ]                                                                                                         | [0B <sub>H</sub> -<br>0F <sub>H</sub> ]                                  | _                          |

| Software Traps: <ul> <li>TRAP Instruction</li> </ul>                                                                                                                                                           | _                                         | -                                         | Any<br>[xx'0000 <sub>H</sub> -<br>xx'01FC <sub>H</sub> ]<br>in steps of<br>4 <sub>H</sub>                                                    | Any<br>[00 <sub>н</sub> -<br>7F <sub>н</sub> ]                           | Current<br>CPU<br>Priority |

#### Table 7Trap Summary

1) Register VECSEG defines the segment where the vector table is located to.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

# 3.5 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XE167 provides a broad range of debug and emulation features. User software running on the XE167 can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This consists of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the debug interface, or via the external bus interface for increased performance.

The JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

#### 3.6 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to a number of prescaled values of the internal system clock. It may also be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range for the timer period and resolution while allowing precise adjustments for application-specific requirements. An external count input for CAPCOM2 timer T7 allows event scheduling for the capture/compare registers with respect to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers. Each may be individually allocated to either CAPCOM2 timer T7 or T8 and programmed for a capture or compare function.

Each register of the CAPCOM2 module has one port pin associated with it. This serves as an input pin to trigger the capture function or as an output pin to indicate the occurrence of a compare event.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible                                        |

| Mode 1                  | Pin toggles on each compare match;<br>Several compare events per timer period are possible                                      |

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

| Table 8 | <b>Compare Modes</b> | (CAPCOM2) |

|---------|----------------------|-----------|

|         |                      |           |

## 3.8 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XE167 to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

#### 4.2 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XE167 can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XE167 are designed to operate in various driver modes. The DC parameter specifications refer to the current limits in **Table 13**.

| Port Output Driver<br>Mode | Maximum Ou<br>(I <sub>OLmax</sub> , -I <sub>OHma</sub> | •                    | Nominal Output Current<br>(I <sub>OLnom</sub> , -I <sub>OHnom</sub> ) |                      |  |

|----------------------------|--------------------------------------------------------|----------------------|-----------------------------------------------------------------------|----------------------|--|

|                            | $V_{	t DDP} \ge$ 4.5 V                                 | $V_{ m DDP}$ < 4.5 V | $V_{	t DDP} \ge$ 4.5 V                                                | $V_{ m DDP}$ < 4.5 V |  |

| Strong driver              | 10 mA                                                  | 10 mA                | 2.5 mA                                                                | 2.5 mA               |  |

| Medium driver              | 4.0 mA                                                 | 2.5 mA               | 1.0 mA                                                                | 1.0 mA               |  |

| Weak driver                | 0.5 mA                                                 | 0.5 mA               | 0.1 mA                                                                | 0.1 mA               |  |

Table 13

Current Limits for Port Output Drivers

1) An output current above  $|I_{OXnom}|$  may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction ( $\Sigma I_{OL}$  and  $\Sigma I_{OH}$ ) must remain below 50 mA.

### 4.2.2 DC Parameters for Lower Voltage Area

These parameters apply to the lower IO voltage range, 3.0 V  $\leq V_{\text{DDP}} \leq$  4.5 V.

#### Note / Parameter Symbol Values Unit **Test Condition** Min. Тур. Max. V Input low voltage $V_{\parallel}$ SR -0.3 $0.3 \times$ \_ \_ (all except XTAL1) $V_{\rm DDP}$ $V_{\rm IH}\,{\rm SR}$ Input high voltage 0.7 × V $V_{\mathsf{DDP}}$ \_ \_ (all except XTAL1) + 0.3 $V_{\mathsf{DDP}}$ Input Hysteresis<sup>2)</sup> HYS CC 0.07 V $V_{\text{DDP}}$ in [V], \_ \_ Series $\times V_{\text{DDP}}$ resistance = $0 \Omega$ $I_{\rm OL} \leq I_{\rm OLmax}^{3)}$ $V_{OI}$ CC V Output low voltage 1.0 \_ \_ $I_{\rm OL} \leq I_{\rm OLnom}^{3)4)}$ V Output low voltage $V_{OI}$ CC 0.4 $I_{OH} \ge I_{OHmax}^{3)}$ Output high voltage<sup>5)</sup> $V_{OH} CC$ V $V_{\rm DDP}$ \_ - 1.0 $I_{\text{OH}} \ge I_{\text{OHnom}}^{3)4)}$ $V_{OH} CC$ Output high voltage<sup>5)</sup> $V_{\rm DDP}$ V \_ \_ - 0.4 $0 V < V_{IN} < V_{DDP}$ Input leakage current $I_{O71}$ CC \_ ±10 ±200 nA (Port 5, Port 15)<sup>6)</sup> $T_{\rm J} \le 110^{\circ} {\rm C},$ Input leakage current $I_{072}$ CC \_ $\pm 0.2$ $\pm 2.5$ μA (all other)<sup>6)7)</sup> $0.45 V < V_{INI}$ $< V_{\rm DDP}$ $V_{\mathsf{PIN}} \ge V_{\mathsf{IH}} \ (\mathsf{up})^{\mathsf{8}}$ Pull level keep current ±10 μA $I_{\mathsf{PLK}}$ \_ \_ $V_{\text{PIN}} \le V_{\text{IL}}$ (dn) $V_{\mathsf{PIN}} \le V_{\mathsf{IL}} \ (\mathsf{up})^{\mathsf{8}}$ Pull level force current $I_{\mathsf{PLF}}$ ±150 \_ \_ μA $V_{\text{PIN}} \ge V_{\text{IH}} (\text{dn})$ Pin capacitance<sup>9)</sup> $C_{\rm IO}$ CC 10 pF \_ \_ (digital inputs/outputs)

# Table 15DC Characteristics for Lower Voltage Range<br/>(Operating Conditions apply)<sup>1)</sup>

1) Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 13, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

Sample time and conversion time of the XE167's A/D converters are programmable. The timing above can be calculated using **Table 19**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{ADCI}$ | INPCRx.7-0<br>(STC) | Sample Time<br>$t_{s}$<br>$t_{ADCI} \times 2$ |  |

|-----------------------|------------------------------------------|---------------------|-----------------------------------------------|--|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                         | 00 <sub>H</sub>     |                                               |  |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                     | 01 <sub>H</sub>     | $t_{\sf ADCI} 	imes {f 3}$                    |  |

| 000010 <sub>B</sub>   | 00010 <sub>B</sub> f <sub>SYS</sub> / 3  |                     | $t_{ADCI} \times 4$                           |  |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                 | :                   | $t_{ADCI} \times (STC+2)$                     |  |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                    | FE <sub>H</sub>     | $t_{ADCI} \times 256$                         |  |

| 111111 <sub>B</sub>   | <i>f</i> <sub>SYS</sub> / 64             | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                      |  |

Table 19

A/D Converter Computation Table

#### **Converter Timing Example A:**

| Assumptions:          | $f_{\rm SYS}$           | = 80 MHz (i.e. <i>t</i> <sub>SYS</sub> = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub> |

|-----------------------|-------------------------|---------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                                |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                            |

| <b>Conversion 10-</b> | bit:                    |                                                                                                   |

|                       | <i>t</i> <sub>C10</sub> | = $13 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 13 × 50 ns + 2 × 12.5 ns = 0.675 µs                      |

| Conversion 8-b        | it:                     |                                                                                                   |

|                       | t <sub>C8</sub>         | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 50$ ns + $2 \times 12.5$ ns = 0.575 µs   |

|                       | <b>F</b>                |                                                                                                   |

#### **Converter Timing Example B:**

| Assumptions:   | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub>            |  |  |

|----------------|-------------------------|----------------------------------------------------------------------------------------------|--|--|

| Analog clock   | $f_{\rm ADCI}$          | = f <sub>SYS</sub> / 3 = 13.3 MHz, i.e. t <sub>ADCI</sub> = 75 ns                            |  |  |

| Sample time    | t <sub>S</sub>          | = $t_{ADCI} \times 5 = 375 \text{ ns}$                                                       |  |  |

| Conversion 10- | bit:                    | :                                                                                            |  |  |

|                | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = $16 \times 75$ ns + 2 × 25 ns = 1.25 µs             |  |  |

| Conversion 8-b | it:                     |                                                                                              |  |  |

|                | t <sub>C8</sub>         | = $14 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $14 \times 75$ ns + $2 \times 25$ ns = 1.10 µs |  |  |

| Table 21          | Coding of Bitfields LEVXV | colling of Bittleids LEVXV in Register SWDCONU |  |  |  |  |

|-------------------|---------------------------|------------------------------------------------|--|--|--|--|

| Code              | Default Voltage Level     | Notes <sup>1)</sup>                            |  |  |  |  |

| 0000 <sub>B</sub> | 2.9 V                     |                                                |  |  |  |  |

| 0001 <sub>B</sub> | 3.0 V                     | LEV1V: reset request                           |  |  |  |  |

| 0010 <sub>B</sub> | 3.1 V                     |                                                |  |  |  |  |

| 0011 <sub>B</sub> | 3.2 V                     |                                                |  |  |  |  |

| 0100 <sub>B</sub> | 3.3 V                     |                                                |  |  |  |  |

| 0101 <sub>B</sub> | 3.4 V                     |                                                |  |  |  |  |

| 0110 <sub>B</sub> | 3.6 V                     |                                                |  |  |  |  |

| 0111 <sub>B</sub> | 4.0 V                     |                                                |  |  |  |  |

| 1000 <sub>B</sub> | 4.2 V                     |                                                |  |  |  |  |

| 1001 <sub>B</sub> | 4.5 V                     | LEV2V: no request                              |  |  |  |  |

| 1010 <sub>B</sub> | 4.6 V                     |                                                |  |  |  |  |

| 1011 <sub>B</sub> | 4.7 V                     |                                                |  |  |  |  |

| 1100 <sub>B</sub> | 4.8 V                     |                                                |  |  |  |  |

| 1101 <sub>B</sub> | 4.9 V                     |                                                |  |  |  |  |

| 1110 <sub>B</sub> | 5.0 V                     |                                                |  |  |  |  |

| 1111 <sub>B</sub> | 5.5 V                     |                                                |  |  |  |  |

|                   |                           |                                                |  |  |  |  |

#### Table 21 Coding of Bitfields LEVxV in Register SWDCON0

1) The indicated default levels are selected automatically after a power reset.

#### Table 22 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>      |

|------------------|-----------------------|--------------------------|

| 000 <sub>B</sub> | 0.9 V                 |                          |

| 001 <sub>B</sub> | 1.0 V                 |                          |

| 010 <sub>B</sub> | 1.1 V                 |                          |

| 011 <sub>B</sub> | 1.2 V                 |                          |

| 100 <sub>B</sub> | 1.3 V                 | LEV1V: reset request     |

| 101 <sub>B</sub> | 1.4 V                 | LEV2V: interrupt request |

| 110 <sub>B</sub> | 1.5 V                 |                          |

| 111 <sub>B</sub> | 1.6 V                 |                          |

1) The indicated default levels are selected automatically after a power reset.

#### Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{\text{SYS}} = f_{\text{WU}}.$

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

#### Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bitfields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

### 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE167. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an **external clock signal**. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . In connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

| Parameter                                      | Symbol             | Limit Values               |      |           | Unit | Note / Test                                            |

|------------------------------------------------|--------------------|----------------------------|------|-----------|------|--------------------------------------------------------|

|                                                |                    | Min.                       | Тур. | Typ. Max. |      | Condition                                              |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR   | -1.7 +<br>V <sub>DDI</sub> | -    | 1.7       | V    | 1)                                                     |

| Input voltage (amplitude)<br>on XTAL1          | $V_{AX1}SR$        | $0.3 \times V_{ m DDI}$    | -    | -         | V    | Peak-to-peak<br>voltage <sup>2)</sup>                  |

| XTAL1 input current                            | I <sub>IL</sub> CC | _                          | -    | ±20       | μA   | $0 \vee \langle V_{\rm IN} \langle V_{\rm DI} \rangle$ |

| Oscillator frequency                           | $f_{\rm OSC}$ CC   | 4                          | -    | 40        | MHz  | Clock signal                                           |

|                                                |                    | 4                          | -    | 16        | MHz  | Crystal or<br>Resonator                                |

| High time                                      | $t_1$ SR           | 6                          | -    | -         | ns   |                                                        |

| Low time                                       | t <sub>2</sub> SR  | 6                          | -    | -         | ns   |                                                        |

| Rise time                                      | t <sub>3</sub> SR  | _                          | 8    | 8         | ns   |                                                        |

| Fall time                                      | t <sub>4</sub> SR  | _                          | 8    | 8         | ns   |                                                        |

# Table 26External Clock Input Characteristics<br/>(Operating Conditions apply)

1) Overload conditions must not occur on pin XTAL1.

2) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

## XE167x XE166 Family Derivatives

#### **Electrical Parameters**

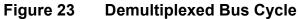

Figure 27 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.