Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                             |

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 118                                                                             |

| Program Memory Size        | 768KB (768K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 82K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-144-4                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe167f96f80lacfxuma1 |

Edition 2008-08

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2008 Infineon Technologies AG

#### **Legal Disclaimer**

All Rights Reserved.

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XE167

16-Bit Single-Chip Real Time Signal Controller

Microcontrollers

| 1                                                                                                                | Summary of Features 4                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1                                                                                                  | General Device Information       8         Pin Configuration and Definition       9                                                                                                                                                                                                                                                                                                                                              |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                         | Functional Description36Memory Subsystem and Organization37External Bus Controller40Central Processing Unit (CPU)41Interrupt System43On-Chip Debug Support (OCDS)49Capture/Compare Unit (CAPCOM2)50Capture/Compare Units CCU6x53General Purpose Timer (GPT12E) Unit55Real Time Clock59A/D Converters61Universal Serial Interface Channel Modules (USIC)62MultiCAN Module64                                                       |

| 3.13<br>3.14<br>3.15<br>3.16                                                                                     | Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.6.5<br>4.6.6 | Electrical Parameters72General Parameters72DC Parameters76DC Parameters for Upper Voltage Area78DC Parameters for Lower Voltage Area80Power Consumption82Analog/Digital Converter Parameters86System Parameters89Flash Memory Parameters91AC Parameters93Testing Waveforms93Definition of Internal Timing94External Clock Input Parameters99External Bus Timing101Synchronous Serial Interface Timing112JTAG Interface Timing115 |

| <b>5</b><br>5.1<br>5.2                                                                                           | Package and Reliability       117         Packaging       117         Thermal Considerations       118                                                                                                                                                                                                                                                                                                                           |

Data Sheet 3 V2.1, 2008-08

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                      |

|-----|-------------------|--------|------|-----------------------------------------------|

| 12  | P7.4              | O0 / I | St/B | Bit 4 of Port 7, General Purpose Input/Output |

|     | EMUX2             | 01     | St/B | External Analog MUX Control Output 2 (ADC1)   |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | U0C1_<br>SCLKOUT  | О3     | St/B | USIC0 Channel 1 Shift Clock Output            |

|     | CCU62_<br>CCPOS2A | I      | St/B | CCU62 Position Input 2                        |

|     | TCK_C             | I      | St/B | JTAG Clock Input                              |

|     | U0C0_DX0D         | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | U0C1_DX1E         | I      | St/B | USIC0 Channel 1 Shift Clock Input             |

| 13  | P8.1              | O0 / I | St/B | Bit 1 of Port 8, General Purpose Input/Output |

|     | CCU60_<br>CC61    | O1 / I | St/B | CCU60 Channel 1 Input/Output                  |

| 14  | P8.0              | O0 / I | St/B | Bit 0 of Port 8, General Purpose Input/Output |

|     | CCU60_<br>CC60    | 01/I   | St/B | CCU60 Channel 0 Input/Output                  |

| 16  | P6.0              | O0 / I | St/A | Bit 0 of Port 6, General Purpose Input/Output |

|     | EMUX0             | 01     | St/A | External Analog MUX Control Output 0 (ADC0)   |

|     | BRKOUT            | О3     | St/A | OCDS Break Signal Output                      |

|     | ADCx_<br>REQGTyC  | I      | St/A | External Request Gate Input for ADC0/1        |

|     | U1C1_DX0E         | I      | St/A | USIC1 Channel 1 Shift Data Input              |

| 17  | P6.1              | O0 / I | St/A | Bit 1 of Port 6, General Purpose Input/Output |

|     | EMUX1             | 01     | St/A | External Analog MUX Control Output 1 (ADC0)   |

|     | T3OUT             | O2     | St/A | GPT1 Timer T3 Toggle Latch Output             |

|     | U1C1_DOUT         | О3     | St/A | USIC1 Channel 1 Shift Data Output             |

|     | ADCx_<br>REQTRyC  | I      | St/A | External Request Trigger Input for ADC0/1     |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |

|-----|------------------|--------|------|-----------------------------------------------|

| 18  | P6.2             | O0 / I | St/A | Bit 2 of Port 6, General Purpose Input/Output |

|     | EMUX2            | 01     | St/A | External Analog MUX Control Output 2 (ADC0)   |

|     | T6OUT            | O2     | St/A | GPT2 Timer T6 Toggle Latch Output             |

|     | U1C1_<br>SCLKOUT | О3     | St/A | USIC1 Channel 1 Shift Clock Output            |

|     | U1C1_DX1C        | I      | St/A | USIC1 Channel 1 Shift Clock Input             |

| 19  | P6.3             | O0 / I | St/A | Bit 3 of Port 6, General Purpose Input/Output |

|     | T3OUT            | O2     | St/A | GPT1 Timer T3 Toggle Latch Output             |

|     | U1C1_<br>SELO0   | О3     | St/A | USIC1 Channel 1 Select/Control 0 Output       |

|     | U1C1_DX2D        | I      | St/A | USIC1 Channel 1 Shift Control Input           |

|     | ADCx_<br>REQTRyD | I      | St/A | External Request Trigger Input for ADC0/1     |

| 21  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input       |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1               |

| 22  | P15.1            |        | In/A | Bit 1 of Port 15, General Purpose Input       |

|     | ADC1_CH1         | l      | In/A | Analog Input Channel 1 for ADC1               |

| 23  | P15.2            | l      | In/A | Bit 2 of Port 15, General Purpose Input       |

|     | ADC1_CH2         | l      | In/A | Analog Input Channel 2 for ADC1               |

|     | T5IN             | l      | In/A | GPT2 Timer T5 Count/Gate Input                |

| 24  | P15.3            | l      | In/A | Bit 3 of Port 15, General Purpose Input       |

|     | ADC1_CH3         | l      | In/A | Analog Input Channel 3 for ADC1               |

|     | T5EUD            | I      | In/A | GPT2 Timer T5 External Up/Down Control Input  |

| 25  | P15.4            | I      | In/A | Bit 4 of Port 15, General Purpose Input       |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1               |

|     | T6IN             | I      | In/A | GPT2 Timer T6 Count/Gate Input                |

| 26  | P15.5            | I      | In/A | Bit 5 of Port 15, General Purpose Input       |

|     | ADC1_CH5         | I      | In/A | Analog Input Channel 5 for ADC1               |

|     | T6EUD            | I      | In/A | GPT2 Timer T6 External Up/Down Control Input  |

| 27  | P15.6            | I      | In/A | Bit 6 of Port 15, General Purpose Input       |

|     | ADC1_CH6         | I      | In/A | Analog Input Channel 6 for ADC1               |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Type | Function                                                                             |  |  |

|-----|------------------|--------|------|--------------------------------------------------------------------------------------|--|--|

| 87  | P0.3             | O0 / I | St/B | Bit 3 of Port 0, General Purpose Input/Output                                        |  |  |

|     | U1C0_<br>SELO0   | 01     | St/B | USIC1 Channel 0 Select/Control 0 Output                                              |  |  |

|     | U1C1_<br>SELO1   | O2     | St/B | USIC1 Channel 1 Select/Control 1 Output                                              |  |  |

|     | CCU61_<br>COUT60 | О3     | St/B | CCU61 Channel 0 Output                                                               |  |  |

|     | A3               | ОН     | St/B | External Bus Interface Address Line 3                                                |  |  |

|     | U1C0_DX2A        | I      | St/B | USIC1 Channel 0 Shift Control Input                                                  |  |  |

|     | RxDC0B           | I      | St/B | CAN Node 0 Receive Data Input                                                        |  |  |

| 88  | P3.1             | O0 / I | St/B | Bit 1 of Port 3, General Purpose Input/Output                                        |  |  |

|     | U2C0_DOUT        | 01     | St/B | USIC2 Channel 0 Shift Data Output                                                    |  |  |

|     | TxDC3            | O2     | St/B | CAN Node 3 Transmit Data Output                                                      |  |  |

|     | HLDA             | OH/I   | St/B | External Bus Hold Acknowledge Output/Inp Output in master mode, input in slave mode. |  |  |

|     | U2C0_DX0B        | I      | St/B | USIC2 Channel 0 Shift Data Input                                                     |  |  |

| 89  | P10.2            | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output                                       |  |  |

|     | U0C0_<br>SCLKOUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output                                                   |  |  |

|     | CCU60_<br>CC62   | O2 / I | St/B | CCU60 Channel 2 Input/Output                                                         |  |  |

|     | AD2              | OH/I   | St/B | External Bus Interface Address/Data Line 2                                           |  |  |

|     | U0C0_DX1B        | I      | St/B | USIC0 Channel 0 Shift Clock Input                                                    |  |  |

| 90  | P0.4             | O0 / I | St/B | Bit 4 of Port 0, General Purpose Input/Output                                        |  |  |

|     | U1C1_<br>SELO0   | 01     | St/B | USIC1 Channel 1 Select/Control 0 Output                                              |  |  |

|     | U1C0_<br>SELO1   | O2     | St/B | USIC1 Channel 0 Select/Control 1 Output                                              |  |  |

|     | CCU61_<br>COUT61 | О3     | St/B | CCU61 Channel 1 Output                                                               |  |  |

|     | A4               | ОН     | St/B | External Bus Interface Address Line 4                                                |  |  |

|     | U1C1_DX2A        | I      | St/B | USIC1 Channel 1 Shift Control Input                                                  |  |  |

|     | RxDC1B           | I      | St/B | CAN Node 1 Receive Data Input                                                        |  |  |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 104 | P3.6              | O0 / I | St/B | Bit 6 of Port 3, General Purpose Input/Output  |

|     | U2C1_DOUT         | 01     | St/B | USIC2 Channel 1 Shift Data Output              |

|     | TxDC4             | 02     | St/B | CAN Node 4 Transmit Data Output                |

|     | U0C0_<br>SELO6    | О3     | St/B | USIC0 Channel 0 Select/Control 6 Output        |

|     | U2C1_DX0A         | I      | St/B | USIC2 Channel 1 Shift Data Input               |

|     | U2C1_DX1B         | I      | St/B | USIC2 Channel 1 Shift Clock Input              |

| 105 | P10.7             | O0 / I | St/B | Bit 7 of Port 10, General Purpose Input/Output |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CCU60_<br>COUT63  | O2     | St/B | CCU60 Channel 3 Output                         |

|     | AD7               | OH/I   | St/B | External Bus Interface Address/Data Line 7     |

|     | U0C1_DX0B         | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CCU60_<br>CCPOS0A | I      | St/B | CCU60 Position Input 0                         |

|     | RxDC4C            | I      | St/B | CAN Node 4 Receive Data Input                  |

| 106 | P0.7              | O0 / I | St/B | Bit 7 of Port 0, General Purpose Input/Output  |

|     | U1C1_DOUT         | 01     | St/B | USIC1 Channel 1 Shift Data Output              |

|     | U1C0_<br>SELO3    | O2     | St/B | USIC1 Channel 0 Select/Control 3 Output        |

|     | A7                | ОН     | St/B | External Bus Interface Address Line 7          |

|     | U1C1_DX0B         | I      | St/B | USIC1 Channel 1 Shift Data Input               |

|     | CCU61_<br>CTRAPB  | I      | St/B | CCU61 Emergency Trap Input                     |

| 107 | P3.7              | O0 / I | St/B | Bit 7 of Port 3, General Purpose Input/Output  |

|     | U2C1_DOUT         | 01     | St/B | USIC2 Channel 1 Shift Data Output              |

|     | U2C0_<br>SELO3    | O2     | St/B | USIC2 Channel 0 Select/Control 3 Output        |

|     | U0C0_<br>SELO7    | О3     | St/B | USIC0 Channel 0 Select/Control 7 Output        |

|     | U2C1_DX0B         | I      | St/B | USIC2 Channel 1 Shift Data Input               |

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XE166 Family. In order to to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 5**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**Up to 768 Kbytes of on-chip Flash memory** store code, constant data, and control data. The on-chip Flash memory consists of up to three modules with a maximum capacity of 256 Kbytes each. Each module is organized in 4-Kbyte sectors.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen derivative (see **Table 1**).

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see **Section 4.5**.

Data Sheet 39 V2.1, 2008-08

<sup>1)</sup> To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

# XE167x XE166 Family Derivatives

# **Functional Description**

Table 6 XE167 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| A/D Converter Request 0                       | ADC_0IC             | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| A/D Converter Request 1                       | ADC_1IC             | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| A/D Converter Request 2                       | ADC_2IC             | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| A/D Converter Request 3                       | ADC_3IC             | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| A/D Converter Request 4                       | ADC_4IC             | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| A/D Converter Request 5                       | ADC_5IC             | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| A/D Converter Request 6                       | ADC_6IC             | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| A/D Converter Request 7                       | ADC_7IC             | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| CCU60 Request 0                               | CCU60_0IC           | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CCU60 Request 1                               | CCU60_1IC           | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CCU60 Request 2                               | CCU60_2IC           | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CCU60 Request 3                               | CCU60_3IC           | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CCU61 Request 0                               | CCU61_0IC           | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CCU61 Request 1                               | CCU61_1IC           | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CCU61 Request 2                               | CCU61_2IC           | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CCU61 Request 3                               | CCU61_3IC           | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CCU62 Request 0                               | CCU62_0IC           | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CCU62 Request 1                               | CCU62_1IC           | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CCU62 Request 2                               | CCU62_2IC           | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CCU62 Request 3                               | CCU62_3IC           | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CCU63 Request 0                               | CCU63_0IC           | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

| CCU63 Request 1                               | CCU63_1IC           | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CCU63 Request 2                               | CCU63_2IC           | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| CCU63 Request 3                               | CCU63_3IC           | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| CAN Request 0                                 | CAN_0IC             | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

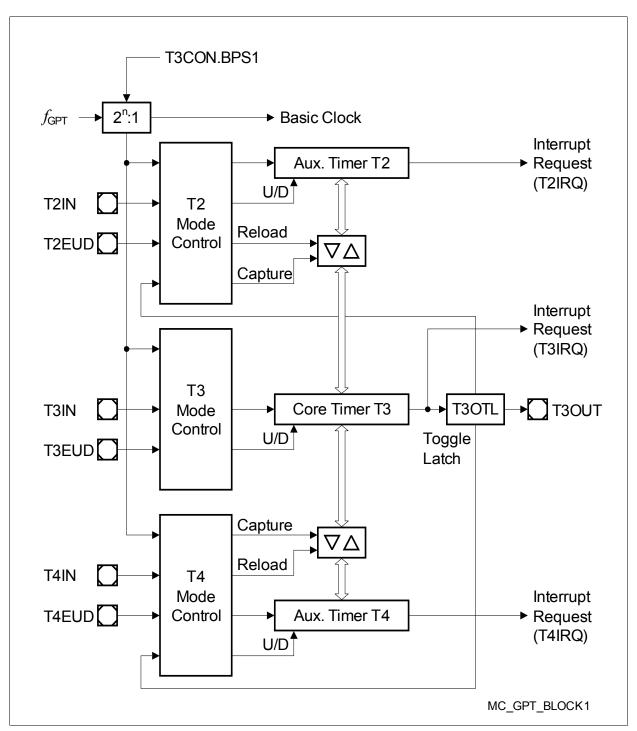

## 3.8 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

Data Sheet 55 V2.1, 2008-08

Figure 7 Block Diagram of GPT1

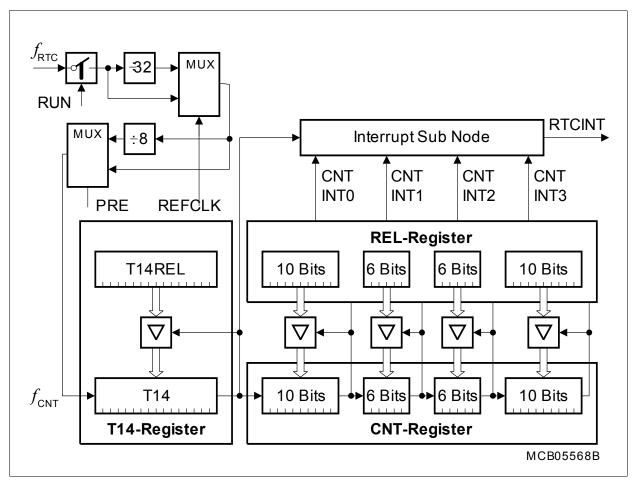

#### 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XE167 can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

Data Sheet 59 V2.1, 2008-08

#### 3.10 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 16 + 8 multiplexed input channels and a sample and hold circuit have been integrated on-chip. They use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically.

For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XE167 support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features, such as limit checking or result accumulation, reduce the number of required CPU access operations allowing the precise evaluation of analoginputs (high conversion rate) even at a low CPU speed.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages under software control. This can be selected for each pin separately with registers P5\_DIDIS and P15\_DIDIS (Port x Digital Input Disable).

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Data Sheet 61 V2.1, 2008-08

# **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XE167. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

**Table 12** Operating Condition Parameters

| Parameter                                                                      | Symbol                       |           | Values                    | 6                         | Unit | Note /                               |  |

|--------------------------------------------------------------------------------|------------------------------|-----------|---------------------------|---------------------------|------|--------------------------------------|--|

|                                                                                |                              | Min. Typ. |                           | Max.                      |      | Test Condition                       |  |

| Digital core supply voltage                                                    | $V_{DDI}$                    | 1.4       | _                         | 1.6                       | V    |                                      |  |

| Core Supply Voltage<br>Difference                                              | ΔVDDI                        | -10       | _                         | +10                       | mV   | $V_{\rm DDIM}$ - $V_{\rm DDI1}$      |  |

| Digital supply voltage for IO pads and voltage regulators, upper voltage range | $V_{ m DDPA}, \ V_{ m DDPB}$ | 4.5       | _                         | 5.5                       | V    | 2)                                   |  |

| Digital supply voltage for IO pads and voltage regulators, lower voltage range | $V_{ m DDPA}, \ V_{ m DDPB}$ | 3.0       | _                         | 4.5                       | V    | 2)                                   |  |

| Digital ground voltage                                                         | $V_{SS}$                     | 0         | _                         | 0                         | V    | Reference voltage                    |  |

| Overload current                                                               | $I_{OV}$                     | -5        | _                         | 5                         | mA   | Per IO pin <sup>3)4)</sup>           |  |

|                                                                                |                              | -2        | _                         | 5                         | mA   | Per analog input pin <sup>3)4)</sup> |  |

| Overload positive current coupling factor for analog inputs <sup>5)</sup>      | $K_{OVA}$                    | _         | 1.0 ×<br>10 <sup>-6</sup> | 1.0 ×<br>10 <sup>-4</sup> | _    | <i>I</i> <sub>OV</sub> > 0           |  |

| Overload negative current coupling factor for analog inputs <sup>5)</sup>      | $K_{OVA}$                    | _         | 2.5 × 10 <sup>-4</sup>    | 1.5 ×<br>10 <sup>-3</sup> | _    | <i>I</i> <sub>OV</sub> < 0           |  |

| Overload positive current coupling factor for digital I/O pins <sup>5)</sup>   | $K_{OVD}$                    | _         | 1.0 ×<br>10 <sup>-4</sup> | 5.0 ×<br>10 <sup>-3</sup> | _    | <i>I</i> <sub>OV</sub> > 0           |  |

| Overload negative current coupling factor for digital I/O pins <sup>5)</sup>   | $K_{OVD}$                    | _         | 1.0 ×<br>10 <sup>-2</sup> | 3.0 ×<br>10 <sup>-2</sup> | -    | <i>I</i> <sub>OV</sub> < 0           |  |

| Absolute sum of overload currents                                              | Σ ΙΟV                        | _         | _                         | 50                        | mA   | 4)                                   |  |

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and Figure 19).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$$D_{Tmax}$$

[ns] = ±(220 / (K2 ×  $f_{SYS}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$$\mathbf{D}_{\mathsf{T}}$$

[ns] =  $D_{\mathsf{Tmax}} \times [(1 - 0.058 \times \mathsf{K2}) \times (\mathsf{T} - 1) / (0.83 \times f_{\mathsf{SYS}} - 1) + 0.058 \times \mathsf{K2}]$

$f_{\text{SYS}}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max}$  = ±(220 / (4 × 33) + 4.3) = 5.97 ns (Not applicable directly in this case!)

$$D_3$$

= 5.97 × [(1 - 0.058 × 4) × (3 - 1) / (0.83 × 33 - 1) + 0.058 × 4] = 5.97 × [0.768 × 2 / 26.39 + 0.232] = 1.7 ns

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max}$  = ±(220 / (2 × 33) + 4.3) = 7.63 ns (Not applicable directly in this case!)

$$D_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 2]$$

=  $7.63 \times [0.884 \times 2 / 26.39 + 0.116]$

= 1.4 ns

Data Sheet 96 V2.1, 2008-08

#### 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE167. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an **external clock signal**. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . In connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Table 26 External Clock Input Characteristics (Operating Conditions apply)

| Parameter                                      | Symbol               | Limit Values                  |      |      | Unit | Note / Test                        |

|------------------------------------------------|----------------------|-------------------------------|------|------|------|------------------------------------|

|                                                |                      | Min.                          | Тур. | Max. |      | Condition                          |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}{ m SR}$ | -1.7 + V <sub>DDI</sub>       | _    | 1.7  | V    | 1)                                 |

| Input voltage (amplitude) on XTAL1             | $V_{AX1}SR$          | $0.3 \times V_{\mathrm{DDI}}$ | _    | _    | V    | Peak-to-peak voltage <sup>2)</sup> |

| XTAL1 input current                            | $I_{IL}$ CC          | _                             | _    | ±20  | μΑ   | $0 \ V < V_{IN} < V_{DD}$          |

| Oscillator frequency                           | $f_{\rm OSC}$ CC     | 4                             | _    | 40   | MHz  | Clock signal                       |

|                                                |                      | 4                             | _    | 16   | MHz  | Crystal or<br>Resonator            |

| High time                                      | t <sub>1</sub> SR    | 6                             | _    | _    | ns   |                                    |

| Low time                                       | t <sub>2</sub> SR    | 6                             | _    | _    | ns   |                                    |

| Rise time                                      | t <sub>3</sub> SR    | _                             | 8    | 8    | ns   |                                    |

| Fall time                                      | t <sub>4</sub> SR    | _                             | 8    | 8    | ns   |                                    |

<sup>1)</sup> Overload conditions must not occur on pin XTAL1.

Data Sheet 99 V2.1, 2008-08

<sup>2)</sup> The amplitude voltage  $V_{\text{AX1}}$  refers to the offset voltage  $V_{\text{OFF}}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{\text{IX1}}$ .

# XE167x XE166 Family Derivatives

#### **Electrical Parameters**

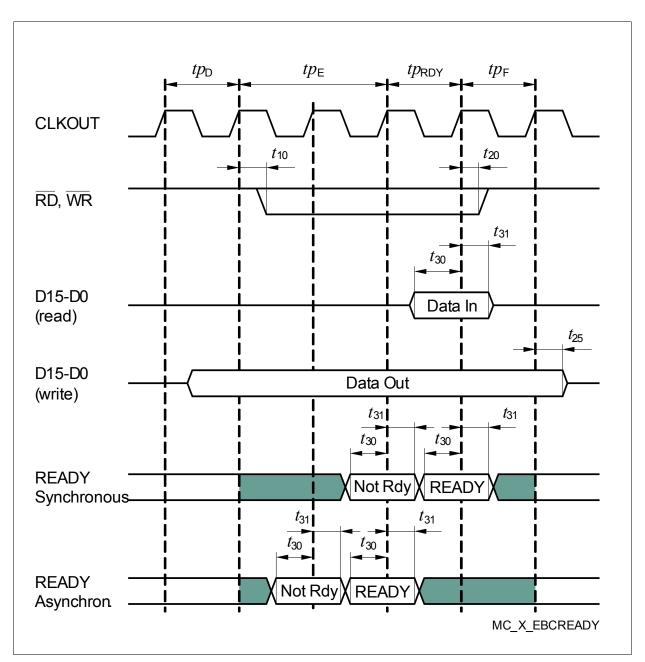

#### **Bus Cycle Control with the READY Input**

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command (RD or WR).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

Figure 24 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

## Package and Reliability

#### 5.2 Thermal Considerations

When operating the XE167 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 125 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta JA}$

The internal power consumption is defined as  $P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (see **Section 4.2.3**).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\rm DDP}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

Data Sheet 119 V2.1, 2008-08

www.infineon.com

Published by Infineon Technologies AG