Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 118                                                                             |

| Program Memory Size        | 576KB (576K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 50K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-144-4                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe167g72f66lacfxqma1 |

# XE167

16-Bit Single-Chip Real Time Signal Controller

Microcontrollers

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |

|-----|------------------|--------|------|-----------------------------------------------|

| 18  | P6.2             | O0 / I | St/A | Bit 2 of Port 6, General Purpose Input/Output |

|     | EMUX2            | 01     | St/A | External Analog MUX Control Output 2 (ADC0)   |

|     | T6OUT            | O2     | St/A | GPT2 Timer T6 Toggle Latch Output             |

|     | U1C1_<br>SCLKOUT | О3     | St/A | USIC1 Channel 1 Shift Clock Output            |

|     | U1C1_DX1C        | I      | St/A | USIC1 Channel 1 Shift Clock Input             |

| 19  | P6.3             | O0 / I | St/A | Bit 3 of Port 6, General Purpose Input/Output |

|     | T3OUT            | O2     | St/A | GPT1 Timer T3 Toggle Latch Output             |

|     | U1C1_<br>SELO0   | О3     | St/A | USIC1 Channel 1 Select/Control 0 Output       |

|     | U1C1_DX2D        | I      | St/A | USIC1 Channel 1 Shift Control Input           |

|     | ADCx_<br>REQTRyD | I      | St/A | External Request Trigger Input for ADC0/1     |

| 21  | P15.0            | I      | In/A | Bit 0 of Port 15, General Purpose Input       |

|     | ADC1_CH0         | I      | In/A | Analog Input Channel 0 for ADC1               |

| 22  | P15.1            |        | In/A | Bit 1 of Port 15, General Purpose Input       |

|     | ADC1_CH1         | l      | In/A | Analog Input Channel 1 for ADC1               |

| 23  | P15.2            | I      | In/A | Bit 2 of Port 15, General Purpose Input       |

|     | ADC1_CH2         | I      | In/A | Analog Input Channel 2 for ADC1               |

|     | T5IN             | I      | In/A | GPT2 Timer T5 Count/Gate Input                |

| 24  | P15.3            | I      | In/A | Bit 3 of Port 15, General Purpose Input       |

|     | ADC1_CH3         | I      | In/A | Analog Input Channel 3 for ADC1               |

|     | T5EUD            | I      | In/A | GPT2 Timer T5 External Up/Down Control Input  |

| 25  | P15.4            | 1      | In/A | Bit 4 of Port 15, General Purpose Input       |

|     | ADC1_CH4         | I      | In/A | Analog Input Channel 4 for ADC1               |

|     | T6IN             | I      | In/A | GPT2 Timer T6 Count/Gate Input                |

| 26  | P15.5            | I      | In/A | Bit 5 of Port 15, General Purpose Input       |

|     | ADC1_CH5         | 1      | In/A | Analog Input Channel 5 for ADC1               |

|     | T6EUD            | I      | In/A | GPT2 Timer T6 External Up/Down Control Input  |

| 27  | P15.6            | 1      | In/A | Bit 6 of Port 15, General Purpose Input       |

|     | ADC1_CH6         | 1      | In/A | Analog Input Channel 6 for ADC1               |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl. | Туре | Function                                                                |  |  |

|-----|------------------|-------|------|-------------------------------------------------------------------------|--|--|

| 28  | P15.7            | I     | In/A | Bit 7 of Port 15, General Purpose Input                                 |  |  |

|     | ADC1_CH7         | I     | In/A | Analog Input Channel 7 for ADC1                                         |  |  |

| 29  | $V_{AREF1}$      | -     | PS/A | Reference Voltage for A/D Converter ADC1                                |  |  |

| 30  | $V_{AREF0}$      | -     | PS/A | Reference Voltage for A/D Converter ADC0                                |  |  |

| 31  | $V_{AGND}$       | -     | PS/A | Reference Ground for A/D Converters ADC0/1                              |  |  |

| 32  | P5.0             | I     | In/A | Bit 0 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH0         | I     | In/A | Analog Input Channel 0 for ADC0  Bit 1 of Port 5. General Purpose Input |  |  |

| 33  | P5.1             | I     | In/A | Bit 1 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH1         | I     | In/A | Analog Input Channel 1 for ADC0                                         |  |  |

| 34  | P5.2             | I     | In/A | Bit 2 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH2         | I     | In/A | Analog Input Channel 2 for ADC0                                         |  |  |

|     | TDI_A            | I     | In/A | JTAG Test Data Input                                                    |  |  |

| 35  | P5.3             | I     | In/A | Bit 3 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH3         | I     | In/A | Analog Input Channel 3 for ADC0                                         |  |  |

|     | T3IN             | I     | In/A | GPT1 Timer T3 Count/Gate Input                                          |  |  |

| 39  | P5.4             | I     | In/A | Bit 4 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH4         | I     | In/A | Analog Input Channel 4 for ADC0                                         |  |  |

|     | CCU63_<br>T12HRB | I     | In/A | External Run Control Input for T12 of CCU63                             |  |  |

|     | T3EUD            | I     | In/A | GPT1 Timer T3 External Up/Down Control Input                            |  |  |

|     | TMS_A            | I     | In/A | JTAG Test Mode Selection Input                                          |  |  |

| 40  | P5.5             | l     | In/A | Bit 5 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH5         |       | In/A | Analog Input Channel 5 for ADC0                                         |  |  |

|     | CCU60_<br>T12HRB | I     | In/A | External Run Control Input for T12 of CCU60                             |  |  |

| 41  | P5.6             | I     | In/A | Bit 6 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH6         | I     | In/A | Analog Input Channel 6 for ADC0                                         |  |  |

| 42  | P5.7             | I     | In/A | Bit 7 of Port 5, General Purpose Input                                  |  |  |

|     | ADC0_CH7         | I     | In/A | Analog Input Channel 7 for ADC0                                         |  |  |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                                                               |

|-----|------------------|--------|------|----------------------------------------------------------------------------------------|

| 87  | P0.3             | O0 / I | St/B | Bit 3 of Port 0, General Purpose Input/Output                                          |

|     | U1C0_<br>SELO0   | 01     | St/B | USIC1 Channel 0 Select/Control 0 Output                                                |

|     | U1C1_<br>SELO1   | O2     | St/B | USIC1 Channel 1 Select/Control 1 Output                                                |

|     | CCU61_<br>COUT60 | О3     | St/B | CCU61 Channel 0 Output                                                                 |

|     | A3               | ОН     | St/B | External Bus Interface Address Line 3                                                  |

|     | U1C0_DX2A        | I      | St/B | USIC1 Channel 0 Shift Control Input                                                    |

|     | RxDC0B           | I      | St/B | CAN Node 0 Receive Data Input                                                          |

| 88  | P3.1             | O0 / I | St/B | Bit 1 of Port 3, General Purpose Input/Output                                          |

|     | U2C0_DOUT        | 01     | St/B | USIC2 Channel 0 Shift Data Output                                                      |

|     | TxDC3            | 02     | St/B | CAN Node 3 Transmit Data Output                                                        |

|     | HLDA             | OH/I   | St/B | External Bus Hold Acknowledge Output/Input Output in master mode, input in slave mode. |

|     | U2C0_DX0B        | I      | St/B | USIC2 Channel 0 Shift Data Input                                                       |

| 89  | P10.2            | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output                                         |

|     | U0C0_<br>SCLKOUT | 01     | St/B | USIC0 Channel 0 Shift Clock Output                                                     |

|     | CCU60_<br>CC62   | O2 / I | St/B | CCU60 Channel 2 Input/Output                                                           |

|     | AD2              | OH/I   | St/B | External Bus Interface Address/Data Line 2                                             |

|     | U0C0_DX1B        | I      | St/B | USIC0 Channel 0 Shift Clock Input                                                      |

| 90  | P0.4             | O0 / I | St/B | Bit 4 of Port 0, General Purpose Input/Output                                          |

|     | U1C1_<br>SELO0   | 01     | St/B | USIC1 Channel 1 Select/Control 0 Output                                                |

|     | U1C0_<br>SELO1   | O2     | St/B | USIC1 Channel 0 Select/Control 1 Output                                                |

|     | CCU61_<br>COUT61 | О3     | St/B | CCU61 Channel 1 Output                                                                 |

|     | A4               | ОН     | St/B | External Bus Interface Address Line 4                                                  |

|     | U1C1_DX2A        | I      | St/B | USIC1 Channel 1 Shift Control Input                                                    |

|     | RxDC1B           | I      | St/B | CAN Node 1 Receive Data Input                                                          |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Type | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 101 | P3.5             | O0 / I | St/B | Bit 5 of Port 3, General Purpose Input/Output  |

|     | U2C1_<br>SCLKOUT | O1     | St/B | USIC2 Channel 1 Shift Clock Output             |

|     | U2C0_<br>SELO2   | O2     | St/B | USIC2 Channel 0 Select/Control 2 Output        |

|     | U0C0_<br>SELO5   | О3     | St/B | USIC0 Channel 0 Select/Control 5 Output        |

|     | U2C1_DX1A        | I      | St/B | USIC2 Channel 1 Shift Clock Input              |

| 102 | P0.6             | O0 / I | St/B | Bit 6 of Port 0, General Purpose Input/Output  |

|     | U1C1_DOUT        | 01     | St/B | USIC1 Channel 1 Shift Data Output              |

|     | TxDC1            | 02     | St/B | CAN Node 1 Transmit Data Output                |

|     | CCU61_<br>COUT63 | О3     | St/B | CCU61 Channel 3 Output                         |

|     | A6               | ОН     | St/B | External Bus Interface Address Line 6          |

|     | U1C1_DX0A        | I      | St/B | USIC1 Channel 1 Shift Data Input               |

|     | CCU61_<br>CTRAPA | I      | St/B | CCU61 Emergency Trap Input                     |

|     | U1C1_DX1B        | I      | St/B | USIC1 Channel 1 Shift Clock Input              |

| 103 | P10.6            | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |

|     | TxDC4            | 02     | St/B | CAN Node 4 Transmit Data Output                |

|     | U1C0_<br>SELO0   | О3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | AD6              | OH/I   | St/B | External Bus Interface Address/Data Line 6     |

|     | U0C0_DX0C        | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U1C0_DX2D        | I      | St/B | USIC1 Channel 0 Shift Control Input            |

|     | CCU60_<br>CTRAPA | 1      | St/B | CCU60 Emergency Trap Input                     |

Table 4

Pin Definitions and Functions (cont'd)

| Pin               | Symbol           | Ctrl.  | Type | Function                                                                                                                                                                                                                                               |  |  |

|-------------------|------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 140               | ESR2             | O0 / I | St/B | External Service Request 2                                                                                                                                                                                                                             |  |  |

|                   | U1C1_DX0D        | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                       |  |  |

|                   | U1C1_DX2C        | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                    |  |  |

|                   | U2C1_DX0E        | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                       |  |  |

|                   | U2C1_DX2B        | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                    |  |  |

|                   | EX1AINB          | I      | St/B | External Interrupt Trigger Input                                                                                                                                                                                                                       |  |  |

| 141               | ESR0             | O0 / I | St/B | External Service Request 0                                                                                                                                                                                                                             |  |  |

|                   |                  |        |      | Note: After power-up, ESR0 operates as open drain bidirectional reset with a weak pull-up                                                                                                                                                              |  |  |

|                   | U1C0_DX0E        | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                       |  |  |

|                   | U1C0_DX2B        | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                    |  |  |

| 142               | P8.6             | O0 / I | St/B | Bit 6 of Port 8, General Purpose Input/Output                                                                                                                                                                                                          |  |  |

|                   | CCU60_<br>COUT63 | 01     | St/B | CCU60 Channel 3 Output                                                                                                                                                                                                                                 |  |  |

|                   | CCU60_<br>CTRAPB | I      | St/B | CCU60 Emergency Trap Input                                                                                                                                                                                                                             |  |  |

|                   | BRKIN_D          | I      | St/B | OCDS Break Signal Input                                                                                                                                                                                                                                |  |  |

| 143               | P8.5             | O0 / I | St/B | Bit 5 of Port 8, General Purpose Input/Output                                                                                                                                                                                                          |  |  |

|                   | CCU60_<br>COUT62 | 01     | St/B | CCU60 Channel 2 Output                                                                                                                                                                                                                                 |  |  |

|                   | TCK_D            | I      | St/B | JTAG Clock Input                                                                                                                                                                                                                                       |  |  |

| 15                | $V_{DDIM}$       | -      | PS/M | Digital Core Supply Voltage for Domain M Decouple with a ceramic capacitor, see Table 12 for details.                                                                                                                                                  |  |  |

| 54,<br>91,<br>127 | $V_{DDI1}$       | -      | PS/1 | Digital Core Supply Voltage for Domain 1 Decouple with a ceramic capacitor, see Table 12 for details. All $V_{\rm DDI1}$ pins must be connected to each other.                                                                                         |  |  |

| 20                | $V_{DDPA}$       | -      | PS/A | Digital Pad Supply Voltage for Domain A Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pins. Note: The A/D_Converters and ports P5, P6, and P15 are fed from supply voltage $V_{\rm DDPA}$ . |  |  |

# XE167x XE166 Family Derivatives

#### **Functional Description**

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 64 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the chosen derivative (see Table 1).

**16 Kbytes of on-chip Data SRAM (DSRAM)** are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**1 Kbyte of on-chip Stand-By SRAM (SBRAM)** provides storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

Data Sheet 38 V2.1, 2008-08

# XE167x XE166 Family Derivatives

# **Functional Description**

Table 6 XE167 Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAN Request 1                                 | CAN_1IC             | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| CAN Request 2                                 | CAN_2IC             | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

| CAN Request 3                                 | CAN_3IC             | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| CAN Request 4                                 | CAN_4IC             | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAN Request 5                                 | CAN_5IC             | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAN Request 6                                 | CAN_6IC             | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAN Request 7                                 | CAN_7IC             | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| CAN Request 8                                 | CAN_8IC             | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| CAN Request 9                                 | CAN_9IC             | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| CAN Request 10                                | CAN_10IC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

| CAN Request 11                                | CAN_11IC            | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| CAN Request 12                                | CAN_12IC            | xx'0130 <sub>H</sub>             | 4C <sub>H</sub> / 76 <sub>D</sub> |

| CAN Request 13                                | CAN_13IC            | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |

| CAN Request 14                                | CAN_14IC            | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAN Request 15                                | CAN_15IC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| USIC0 Cannel 0, Request 0                     | U0C0_0IC            | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| USIC0 Cannel 0, Request 1                     | U0C0_1IC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| USIC0 Cannel 0, Request 2                     | U0C0_2IC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| USIC0 Cannel 1, Request 0                     | U0C1_0IC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| USIC0 Cannel 1, Request 1                     | U0C1_1IC            | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| USIC0 Cannel 1, Request 2                     | U0C1_2IC            | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| USIC1 Cannel 0, Request 0                     | U1C0_0IC            | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| USIC1 Cannel 0, Request 1                     | U1C0_1IC            | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| USIC1 Cannel 0, Request 2                     | U1C0_2IC            | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

| USIC1 Cannel 1, Request 0                     | U1C1_0IC            | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| USIC1 Cannel 1, Request 1                     | U1C1_1IC            | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| USIC1 Cannel 1, Request 2                     | U1C1_2IC            | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| USIC2 Cannel 0, Request 0                     | U2C0_0IC            | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| USIC2 Cannel 0, Request 1                     | U2C0_1IC            | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| USIC2 Cannel 0, Request 2                     | U2C0_2IC            | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

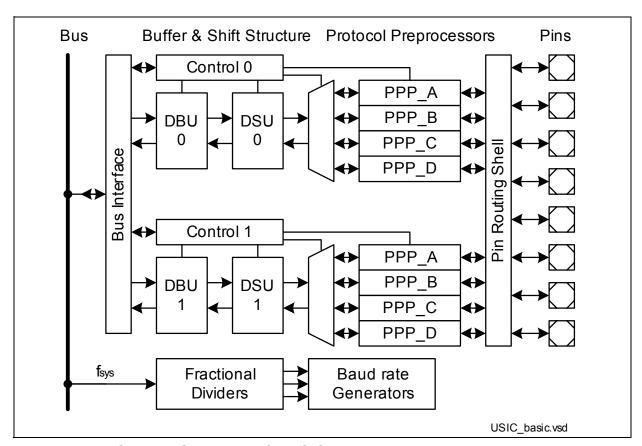

# 3.11 Universal Serial Interface Channel Modules (USIC)

The XE167 includes up to three USIC modules (USIC0, USIC1, USIC2), each providing two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

Figure 10 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

Data Sheet 62 V2.1, 2008-08

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- maximum baud rate:  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- maximum baud rate:  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI/QSPI (synchronous serial channel with or without data buffer)

- maximum baud rate in slave mode:  $f_{SYS}$

- maximum baud rate in master mode:  $f_{\rm SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- maximum baud rate:  $f_{\rm SYS}$  / 2 for transmitter,  $f_{\rm SYS}$  for receiver

Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

Data Sheet 63 V2.1, 2008-08

# 3.13 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

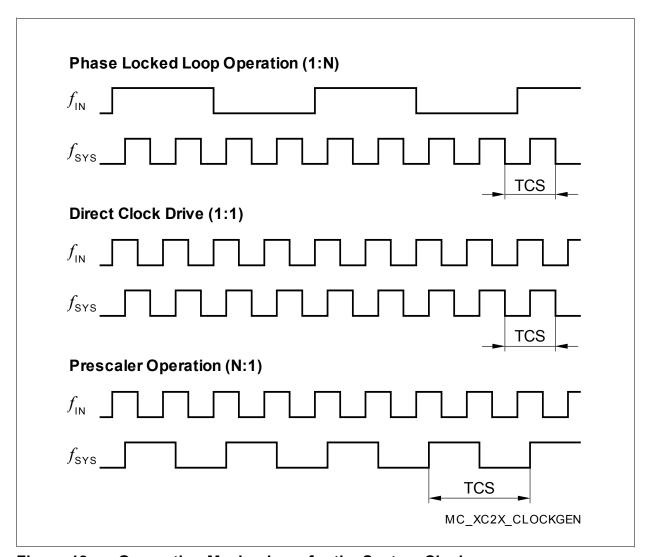

#### 3.14 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE167 from a number of external or internal clock sources:

- External clock signals with pad or core voltage levels

- External crystal using the on-chip oscillator

- On-chip clock source for operation without crystal

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

Data Sheet 66 V2.1, 2008-08

Table 9 Summary of the XE167's Parallel Ports (cont'd)

| Port    | Width | Alternate Functions                                                                                                                                      |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 5  | 16    | Analog input channels to ADC0, Input/Output lines for CCU6x, Timer control signals, JTAG, OCDS control, interrupts                                       |

| Port 6  | 4     | ADC control lines, Serial interface lines of USIC1, Timer control signals, OCDS control                                                                  |

| Port 7  | 5     | ADC control lines, Serial interface lines of USIC0 and CAN4, Input/Output lines for CCU62, Timer control signals, JTAG, OCDS control,system clock output |

| Port 8  | 7     | Input/Output lines for CCU60,<br>JTAG, OCDS control                                                                                                      |

| Port 9  | 8     | Serial interface lines of USIC2,<br>Input/Output lines for CCU60 and CCU63,<br>OCDS control                                                              |

| Port 10 | 16    | Address and/or data lines, bus control, Serial interface lines of USIC0, USIC1, CAN2, CAN3, and CAN4, Input/Output lines for CCU60, JTAG, OCDS control   |

| Port 11 | 6     | Input/Output lines for CCU63                                                                                                                             |

| Port 15 | 8     | Analog input channels to ADC1,<br>Timer control signals                                                                                                  |

# 4 Electrical Parameters

The operating range for the XE167 is defined by its electrical parameters. For proper operation the specified limits must be respected during system design.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

## 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

Table 11 Absolute Maximum Rating Parameters

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol                                   |      | Values | 5                      | Unit | Note /                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|--------|------------------------|------|-----------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          | Min. | Тур.   | Max.                   |      | Test Condition        |

| Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $T_{ST}$                                 | -65  | _      | 150                    | °C   | _                     |

| Junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $T_{J}$                                  | -40  | _      | 125                    | °C   | under bias            |

| $\begin{tabular}{lll} \hline & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$ | $V_{\mathrm{DDIM}}, \ V_{\mathrm{DDI1}}$ | -0.5 | -      | 1.65                   | V    | -                     |

| $\begin{tabular}{lll} \hline & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$ | $V_{ m DDPA}, \ V_{ m DDPB}$             | -0.5 | -      | 6.0                    | V    | -                     |

| Voltage on any pin with respect to ground $(V_{\rm SS})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_{IN}$                                 | -0.5 | _      | V <sub>DDP</sub> + 0.5 | V    | $V_{IN} < V_{DDPmax}$ |

| Input current on any pin during overload condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                        | -10  | _      | 10                     | mA   | -                     |

| Absolute sum of all input currents during overload condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                        | _    | _      | [100]                  | mA   | _                     |

| Output current on any pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $I_{\mathrm{OH}},I_{\mathrm{OL}}$        | _    | _      | 30                     | mA   | _                     |

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

# **Parameter Interpretation**

The parameters listed in the following include both the characteristics of the XE167 and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

## **CC** (Controller Characteristics):

The logic of the XE167 provides signals with the specified characteristics.

# **SR** (System Requirement):

The external system must provide signals with the specified characteristics to the XE167.

Data Sheet 75 V2.1, 2008-08

# 4.3 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance.

Table 18 A/D Converter Characteristics (Operating Conditions apply)

| Parameter                                       | Symbol             |    | Limit                               | Values                   | Unit | Test                            |

|-------------------------------------------------|--------------------|----|-------------------------------------|--------------------------|------|---------------------------------|

|                                                 |                    |    | Min.                                | Max.                     |      | Condition                       |

| Analog reference supply                         | $V_{AREF}$         | SR | V <sub>AGND</sub> + 1.0             | V <sub>DDPA</sub> + 0.05 | V    | 1)                              |

| Analog reference ground                         | $V_{AGND}$         | SR | V <sub>SS</sub> - 0.05              | V <sub>AREF</sub> - 1.0  | V    | _                               |

| Analog input voltage range                      | $V_{AIN}$          | SR | $V_{AGND}$                          | $V_{AREF}$               | V    | 2)                              |

| Analog clock frequency                          | $f_{ADCI}$         |    | 0.5                                 | 20                       | MHz  | 3)                              |

| Conversion time for 10-bit result <sup>4)</sup> | t <sub>C10</sub>   | CC | (13 + STC<br>+ 2 × t <sub>SYS</sub> | $(t) \times t_{ADCI}$    | -    | _                               |

| Conversion time for 8-bit result <sup>4)</sup>  | $t_{C8}$           | CC | (11 + STC<br>+ 2 × t <sub>SYS</sub> | $C) \times t_{ADCI}$     | -    | _                               |

| Wakeup time from analog powerdown, fast mode    | $t_{WAF}$          | CC | _                                   | 1                        | μS   | _                               |

| Wakeup time from analog powerdown, slow mode    | $t_{WAS}$          | CC | _                                   | 10                       | μS   | _                               |

| Total unadjusted error <sup>5)</sup>            | TUE                | CC | _                                   | ±2                       | LSB  | $V_{AREF} = 5.0 \text{ V}^{1)}$ |

| DNL error                                       | EA <sub>DNL</sub>  | CC | _                                   | ±1                       | LSB  |                                 |

| INL error                                       | EA <sub>INL</sub>  | CC | _                                   | ±1.2                     | LSB  |                                 |

| Gain error                                      | EA <sub>GAIN</sub> | CC | _                                   | ±0.8                     | LSB  |                                 |

| Offset error                                    | EA <sub>OFF</sub>  | CC | _                                   | ±0.8                     | LSB  |                                 |

| Total capacitance of an analog input            | $C_{AINT}$         | CC | _                                   | 10                       | pF   | 6)7)                            |

| Switched capacitance of an analog input         | $C_{AINS}$         | CC | _                                   | 4                        | pF   | 6)7)                            |

| Resistance of the analog input path             | $R_{AIN}$          | CC | _                                   | 1.5                      | kΩ   | 6)7)                            |

| Total capacitance of the reference input        | $C_{AREFT}$        | CC | _                                   | 15                       | pF   | 6)7)                            |

# 4.6.2 Definition of Internal Timing

The internal operation of the XE167 is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE167.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

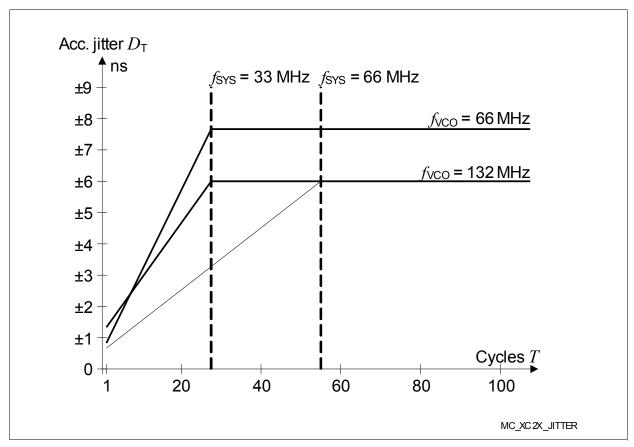

Figure 19 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_1$  = 20 pF (see **Table 12**).

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{\rm DDPB}$  pin 100/144 and  $V_{\rm SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{\rm PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

Table 25 VCO Bands for PLL Operation<sup>1)</sup>

| PLLCON0.VCOSEL | VCO Frequency Range | Base Frequency Range |

|----------------|---------------------|----------------------|

| 00             | 50 110 MHz          | 10 40 MHz            |

| 01             | 100 160 MHz         | 20 80 MHz            |

| 1X             | Reserved            |                      |

<sup>1)</sup> Not subject to production test - verified by design/characterization.

# 4.6.4 External Bus Timing

The following parameters specify the behavior of the XE167 bus interface.

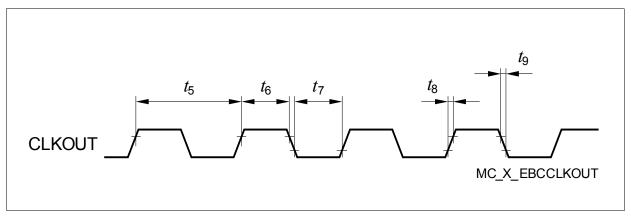

Table 27 CLKOUT Reference Signal

| Parameter         | Sym                   | Symbol |      | Limits                 | Unit | Note / Test |

|-------------------|-----------------------|--------|------|------------------------|------|-------------|

|                   |                       |        | Min. | Max.                   |      | Condition   |

| CLKOUT cycle time | $t_5$                 | CC     | 40   | /25/12.5 <sup>1)</sup> | ns   |             |

| CLKOUT high time  | <i>t</i> <sub>6</sub> | CC     | 3    | _                      | ns   |             |

| CLKOUT low time   | t <sub>7</sub>        | CC     | 3    | _                      | ns   |             |

| CLKOUT rise time  | <i>t</i> <sub>8</sub> | CC     | _    | 3                      | ns   |             |

| CLKOUT fall time  | $t_9$                 | CC     | _    | 3                      | ns   |             |

<sup>1)</sup> The CLKOUT cycle time is influenced by the PLL jitter (given values apply to  $f_{SYS}$  = 25/40/80 MHz). For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 21 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

Data Sheet 101 V2.1, 2008-08

# Package and Reliability

#### 5.2 Thermal Considerations

When operating the XE167 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta JA}$ " quantifies these parameters. The power dissipation must be limited so that the average junction temperature does not exceed 125 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{\text{INT}} + P_{\text{IOSTAT}} + P_{\text{IODYN}}) \times R_{\Theta,\text{JA}}$

The internal power consumption is defined as  $P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (see **Section 4.2.3**).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\mathsf{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

Data Sheet 119 V2.1, 2008-08

www.infineon.com

Published by Infineon Technologies AG