Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 66MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                    |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                 |

| Number of I/O              | 118                                                                             |

| Program Memory Size        | 384KB (384K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 34K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-144-4                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe167k48f66lacfxqma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin       | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3         | TESTM             | I      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pullup device will hold this pin highwhen nothing is driving it.                                                                                                                                                                   |

| 4         | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                     |

|           | TxDC4             | 02     | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                                                                                                                                                                                                 |

|           | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                          |

|           | TDI_C             | Ι      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |

| 5         | P8.4              | O0 / I | St/B | Bit 4 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | CCU60_<br>COUT61  | 01     | St/B | CCU60 Channel 1 Output                                                                                                                                                                                                                                                                                                                                          |

|           | TMS_D             | I      | St/B | JTAG Test Mode Selection Input                                                                                                                                                                                                                                                                                                                                  |

| 6         | TRST              |        | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XE167's debug system. In<br>this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |

| 7         | P8.3              | O0 / I | St/B | Bit 3 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |

|           | CCU60_<br>COUT60  | 01     | St/B | CCU60 Channel 0 Output                                                                                                                                                                                                                                                                                                                                          |

| . <u></u> | TDI_D             | Ι      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                            |

#### Table 4Pin Definitions and Functions

| Table | Fable 4Pin Definitions and Functions (cont'd) |        |      |                                               |  |

|-------|-----------------------------------------------|--------|------|-----------------------------------------------|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                      |  |

| 8     | P7.0                                          | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output |  |

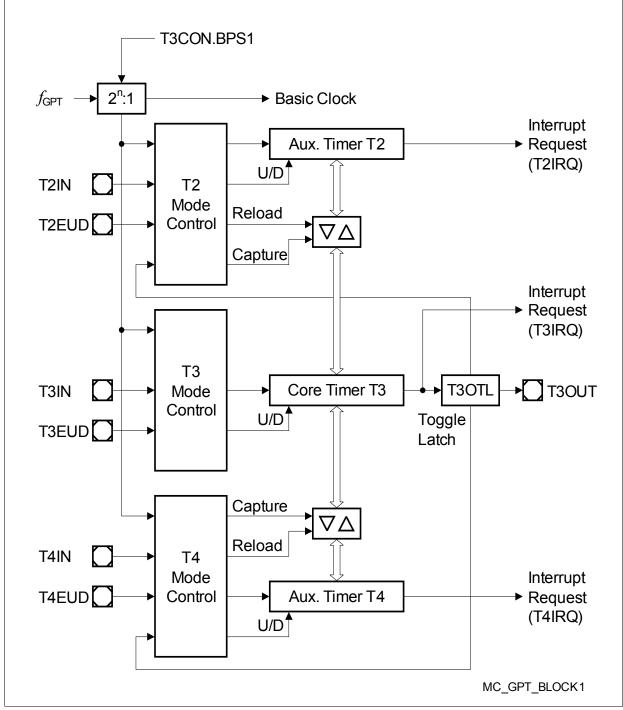

|       | T3OUT                                         | 01     | St/B | GPT1 Timer T3 Toggle Latch Output             |  |

|       | T6OUT                                         | O2     | St/B | GPT2 Timer T6 Toggle Latch Output             |  |

|       | TDO_A                                         | OH     | St/B | JTAG Test Data Output                         |  |

|       | ESR2_1                                        | I      | St/B | ESR2 Trigger Input 1                          |  |

|       | RxDC4B                                        | I      | St/B | CAN Node 4 Receive Data Input                 |  |

| 9     | P7.3                                          | O0 / I | St/B | Bit 3 of Port 7, General Purpose Input/Output |  |

|       | EMUX1                                         | 01     | St/B | External Analog MUX Control Output 1 (ADC1)   |  |

|       | U0C1_DOUT                                     | O2     | St/B | USIC0 Channel 1 Shift Data Output             |  |

|       | U0C0_DOUT                                     | O3     | St/B | USIC0 Channel 0 Shift Data Output             |  |

|       | CCU62_<br>CCPOS1A                             | I      | St/B | CCU62 Position Input 1                        |  |

|       | TMS_C                                         | I      | St/B | JTAG Test Mode Selection Input                |  |

|       | U0C1_DX0F                                     | I      | St/B | USIC0 Channel 1 Shift Data Input              |  |

| 10    | P8.2                                          | O0 / I | St/B | Bit 2 of Port 8, General Purpose Input/Output |  |

|       | CCU60_<br>CC62                                | 01 / I | St/B | CCU60 Channel 2 Input/Output                  |  |

| 11    | P7.1                                          | O0 / I | St/B | Bit 1 of Port 7, General Purpose Input/Output |  |

|       | EXTCLK                                        | 01     | St/B | Programmable Clock Signal Output              |  |

|       | TxDC4                                         | O2     | St/B | CAN Node 4 Transmit Data Output               |  |

|       | CCU62_<br>CTRAPA                              | I      | St/B | CCU62 Emergency Trap Input                    |  |

|       | BRKIN_C                                       | I      | St/B | OCDS Break Signal Input                       |  |

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 60  | P4.0              | O0 / I | St/B | Bit 0 of Port 4, General Purpose Input/Output  |

|     | CC2_24            | O3 / I | St/B | CAPCOM2 CC24IO Capture Inp./ Compare Out.      |

|     | CS0               | OH     | St/B | External Bus Interface Chip Select 0 Output    |

| 61  | P2.3              | O0 / I | St/B | Bit 3 of Port 2, General Purpose Input/Output  |

|     | U0C0_DOUT         | 01     | St/B | USIC0 Channel 0 Shift Data Output              |

|     | CCU63_<br>COUT63  | O2     | St/B | CCU63 Channel 3 Output                         |

|     | CC2_16            | O3 / I | St/B | CAPCOM2 CC16IO Capture Inp./ Compare Out.      |

|     | A16               | OH     | St/B | External Bus Interface Address Line 16         |

|     | ESR2_0            | I      | St/B | ESR2 Trigger Input 0                           |

|     | U0C0_DX0E         | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U0C1_DX0D         | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | RxDC0A            | I      | St/B | CAN Node 0 Receive Data Input                  |

| 62  | P11.2             | O0 / I | St/B | Bit 2 of Port 11, General Purpose Input/Output |

|     | CCU63_<br>CCPOS2A | I      | St/B | CCU63 Position Input 2                         |

| 63  | P4.1              | O0 / I | St/B | Bit 1 of Port 4, General Purpose Input/Output  |

|     | TxDC2             | 02     | St/B | CAN Node 2 Transmit Data Output                |

|     | CC2_25            | O3 / I | St/B | CAPCOM2 CC25IO Capture Inp./ Compare Out.      |

|     | CS1               | OH     | St/B | External Bus Interface Chip Select 1 Output    |

| 64  | P2.4              | O0 / I | St/B | Bit 4 of Port 2, General Purpose Input/Output  |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | TxDC0             | 02     | St/B | CAN Node 0 Transmit Data Output                |

|     | CC2_17            | O3 / I | St/B | CAPCOM2 CC17IO Capture Inp./ Compare Out.      |

|     | A17               | OH     | St/B | External Bus Interface Address Line 17         |

|     | ESR1_0            | I      | St/B | ESR1 Trigger Input 0                           |

|     | U0C0_DX0F         | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | RxDC1A            | I      | St/B | CAN Node 1 Receive Data Input                  |

| 65  | P11.1             | O0 / I | St/B | Bit 1 of Port 11, General Purpose Input/Output |

|     | CCU63_<br>CCPOS1A | I      | St/B | CCU63 Position Input 1                         |

| Tabl | e 4 Pin De       | finitior | ns and | Functions (cont'd)                                                                               |

|------|------------------|----------|--------|--------------------------------------------------------------------------------------------------|

| Pin  | Symbol           | Ctrl.    | Туре   | Function                                                                                         |

| 87   | P0.3             | O0 / I   | St/B   | Bit 3 of Port 0, General Purpose Input/Output                                                    |

|      | U1C0_<br>SELO0   | 01       | St/B   | USIC1 Channel 0 Select/Control 0 Output                                                          |

|      | U1C1_<br>SELO1   | O2       | St/B   | USIC1 Channel 1 Select/Control 1 Output                                                          |

|      | CCU61_<br>COUT60 | O3       | St/B   | CCU61 Channel 0 Output                                                                           |

|      | A3               | OH       | St/B   | External Bus Interface Address Line 3                                                            |

|      | U1C0_DX2A        | I        | St/B   | USIC1 Channel 0 Shift Control Input                                                              |

|      | RxDC0B           | I        | St/B   | CAN Node 0 Receive Data Input                                                                    |

| 88   | P3.1             | O0 / I   | St/B   | Bit 1 of Port 3, General Purpose Input/Output                                                    |

|      | U2C0_DOUT        | 01       | St/B   | USIC2 Channel 0 Shift Data Output                                                                |

|      | TxDC3            | 02       | St/B   | CAN Node 3 Transmit Data Output                                                                  |

|      | HLDA             | OH/I     | St/B   | <b>External Bus Hold Acknowledge Output/Input</b><br>Output in master mode, input in slave mode. |

|      | U2C0_DX0B        | I        | St/B   | USIC2 Channel 0 Shift Data Input                                                                 |

| 89   | P10.2            | O0 / I   | St/B   | Bit 2 of Port 10, General Purpose Input/Output                                                   |

|      | U0C0_<br>SCLKOUT | 01       | St/B   | USIC0 Channel 0 Shift Clock Output                                                               |

|      | CCU60_<br>CC62   | 02 / 1   | St/B   | CCU60 Channel 2 Input/Output                                                                     |

|      | AD2              | OH/I     | St/B   | External Bus Interface Address/Data Line 2                                                       |

|      | U0C0_DX1B        | I        | St/B   | USIC0 Channel 0 Shift Clock Input                                                                |

| 90   | P0.4             | O0 / I   | St/B   | Bit 4 of Port 0, General Purpose Input/Output                                                    |

|      | U1C1_<br>SELO0   | 01       | St/B   | USIC1 Channel 1 Select/Control 0 Output                                                          |

|      | U1C0_<br>SELO1   | O2       | St/B   | USIC1 Channel 0 Select/Control 1 Output                                                          |

|      | CCU61_<br>COUT61 | O3       | St/B   | CCU61 Channel 1 Output                                                                           |

|      | A4               | OH       | St/B   | External Bus Interface Address Line 4                                                            |

|      | U1C1_DX2A        | I        | St/B   | USIC1 Channel 1 Shift Control Input                                                              |

|      | RxDC1B           | I        | St/B   | CAN Node 1 Receive Data Input                                                                    |

| Table             | e 4 Pin De        | finitior | is and | Functions (cont'd)                                                                                                                                                                                                                                                                 |

|-------------------|-------------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin               | Symbol            | Ctrl.    | Туре   | Function                                                                                                                                                                                                                                                                           |

| 140               | ESR2              | O0 / I   | St/B   | External Service Request 2                                                                                                                                                                                                                                                         |

|                   | U1C1_DX0D         | I        | St/B   | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                   |

|                   | U1C1_DX2C         | I        | St/B   | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                |

|                   | U2C1_DX0E         | I        | St/B   | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                   |

|                   | U2C1_DX2B         | I        | St/B   | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                |

|                   | EX1AINB           | I        | St/B   | External Interrupt Trigger Input                                                                                                                                                                                                                                                   |

| 141               | ESR0              | O0 / I   | St/B   | External Service Request 0                                                                                                                                                                                                                                                         |

|                   |                   |          |        | Note: After power-up, ESR0 operates as open-<br>drain bidirectional reset with a weak pull-up.                                                                                                                                                                                     |

|                   | U1C0_DX0E         | I        | St/B   | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                   |

|                   | U1C0_DX2B         | I        | St/B   | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                |

| 142               | P8.6              | O0 / I   | St/B   | Bit 6 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                      |

|                   | CCU60_<br>COUT63  | 01       | St/B   | CCU60 Channel 3 Output                                                                                                                                                                                                                                                             |

|                   | CCU60_<br>CTRAPB  | I        | St/B   | CCU60 Emergency Trap Input                                                                                                                                                                                                                                                         |

|                   | BRKIN_D           | I        | St/B   | OCDS Break Signal Input                                                                                                                                                                                                                                                            |

| 143               | P8.5              | O0 / I   | St/B   | Bit 5 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                      |

|                   | CCU60_<br>COUT62  | 01       | St/B   | CCU60 Channel 2 Output                                                                                                                                                                                                                                                             |

|                   | TCK_D             | I        | St/B   | JTAG Clock Input                                                                                                                                                                                                                                                                   |

| 15                | V <sub>DDIM</sub> | -        | PS/M   | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see <b>Table 12</b><br>for details.                                                                                                                                                          |

| 54,<br>91,<br>127 | V <sub>DDI1</sub> | -        | PS/1   | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see <b>Table 12</b><br>for details.<br>All $V_{DDI1}$ pins must be connected to each other.                                                                                                  |

| 20                | V <sub>DDPA</sub> | -        | PS/A   | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6, and<br>P15 are fed from supply voltage $V_{\text{DDPA}}$ . |

| Pin                                                   | Symbol            | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------|-------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,<br>36,<br>38,<br>72,<br>74,<br>108,<br>110,<br>144 | V <sub>DDPB</sub> | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The on-chip voltage regulators and all ports<br>except P5, P6, and P15 are fed from supply<br>voltage $V_{\text{DDPB}}$ . |

| 1,<br>37,<br>73,<br>109                               | V <sub>SS</sub>   | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line<br>or ground-plane.<br><i>Note: Also the exposed pad is connected to</i> $V_{SS}$ .                                                                                                                                          |

|                                                       |                   |       |      | The respective board area must be connected to ground (if soldered) or left free.                                                                                                                                                                                                                            |

Table 4Pin Definitions and Functions (cont'd)

1) To generate the reference clock output for bus timing measurement,  $f_{SYS}$  must be selected as source for EXTCLK and P2.8 must be selected as output pin. Also the high-speed clock pad must be enabled. This configuration is referred to as reference clock output signal CLKOUT.

2) Pin TRef was used to control the core voltage generation in step AA. For that step, pin TRef must be connected to  $V_{\text{DDPB}}$ .

This connection is no more required from step AB on. For the current step, pin TRef is logically not connected. Future derivatives will feature an additional general purpose IO pin at this position.

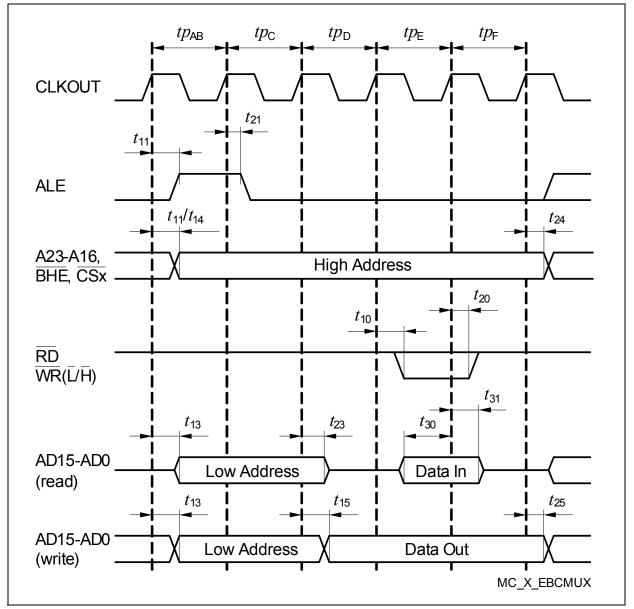

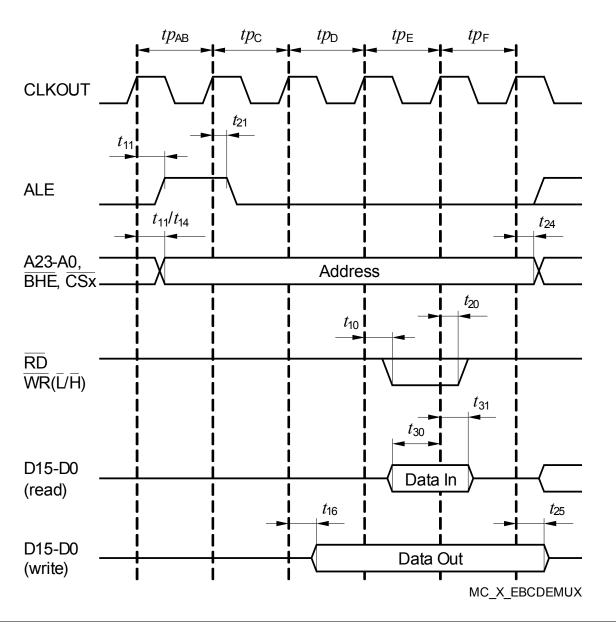

## 3.2 External Bus Controller

All external memory access operations are performed by a special on-chip External Bus Controller (EBC). The EBC also controls access to resources connected to the on-chip LXBus (MultiCAN and the USIC modules). The LXBus is an internal representation of the external bus that allows access to integrated peripherals and modules in the same way as to external components.

The EBC can be programmed either to Single Chip Mode, when no external memory is required, or to an external bus mode with the following selections<sup>1)</sup>:

- Address Bus Width with a range of 0 ... 24-bit

- Data Bus Width 8-bit or 16-bit

- Bus Operation Multiplexed or Demultiplexed

The bus interface uses Port 10 and Port 2 for addresses and data. In the demultiplexed bus modes, the lower addresses are output separately on Port 0 and Port 1. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines shall be assigned to Port 2.

Up to five external  $\overline{CS}$  signals (four windows plus default) can be generated and output on Port 4 in order to save external glue logic. External modules can be directly connected to the common address/data bus and their individual select lines.

A HOLD/HLDA protocol is available for bus arbitration; this allows the sharing of external resources with other bus masters. The bus arbitration is enabled by software, after which pins P3.0 ... P3.2 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. In Slave Mode pin HLDA is switched to be an input. This allows the direct connection of the slave controller to another master controller without glue logic.

Important timing characteristics of the external bus interface are programmable (with registers TCONCSx/FCONCSx) to allow the user to adapt it to a wide range of different types of memories and external peripherals.

Access to very slow memories or modules with varying access times is supported by a special 'Ready' function. The active level of the control input signal is selectable.

In addition, up to four independent address windows may be defined (using registers ADDRSELx) to control access to resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these four address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is based on the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

| Table 6 XE167 Interrupt N                     | lodes (cont'd)      |                                  |                                    |

|-----------------------------------------------|---------------------|----------------------------------|------------------------------------|

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                     |

| USIC2 Cannel 1, Request 0                     | U2C1_0IC            | xx'017C <sub>H</sub>             | 5F <sub>H</sub> / 95 <sub>D</sub>  |

| USIC2 Cannel 1, Request 1                     | U2C1_1IC            | xx'0180 <sub>H</sub>             | 60 <sub>H</sub> / 96 <sub>D</sub>  |

| USIC2 Cannel 1, Request 2                     | U2C1_2IC            | xx'0184 <sub>H</sub>             | 61 <sub>H</sub> / 97 <sub>D</sub>  |

| Unassigned node                               | _                   | xx'0188 <sub>H</sub>             | 62 <sub>H</sub> / 98 <sub>D</sub>  |

| Unassigned node                               | _                   | xx'018C <sub>H</sub>             | 63 <sub>H</sub> / 99 <sub>D</sub>  |

| Unassigned node                               | -                   | xx'0190 <sub>H</sub>             | 64 <sub>H</sub> / 100 <sub>D</sub> |

| Unassigned node                               | _                   | xx'0194 <sub>H</sub>             | 65 <sub>H</sub> / 101 <sub>D</sub> |

| Unassigned node                               | _                   | xx'0198 <sub>H</sub>             | 66 <sub>H</sub> / 102 <sub>D</sub> |

| Unassigned node                               | _                   | xx'019C <sub>H</sub>             | 67 <sub>H</sub> / 103 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A0 <sub>H</sub>             | 68 <sub>H</sub> / 104 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A4 <sub>H</sub>             | 69 <sub>H</sub> / 105 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A8 <sub>H</sub>             | 6A <sub>H</sub> / 106 <sub>D</sub> |

| SCU Request 1                                 | SCU_1IC             | xx'01AC <sub>H</sub>             | 6B <sub>H</sub> / 107 <sub>D</sub> |

| SCU Request 0                                 | SCU_0IC             | xx'01B0 <sub>H</sub>             | 6C <sub>H</sub> / 108 <sub>D</sub> |

| Program Flash Modules                         | PFM_IC              | xx'01B4 <sub>H</sub>             | 6D <sub>H</sub> / 109 <sub>D</sub> |

| RTC                                           | RTC_IC              | xx'01B8 <sub>H</sub>             | 6E <sub>H</sub> / 110 <sub>D</sub> |

| End of PEC Subchannel                         | EOPIC               | xx'01BC <sub>H</sub>             | 6F <sub>H</sub> / 111 <sub>D</sub> |

1) Register VECSEG defines the segment where the vector table is located.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting with a distance of 4 (two words) between two vectors.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

| Table 10Instruction Set Summary (cont'd) |                                     |       |  |  |  |

|------------------------------------------|-------------------------------------|-------|--|--|--|

| Mnemonic                                 | Description                         | Bytes |  |  |  |

| NOP                                      | Null operation                      | 2     |  |  |  |

| CoMUL/CoMAC                              | Multiply (and accumulate)           | 4     |  |  |  |

| CoADD/CoSUB                              | Add/Subtract                        | 4     |  |  |  |

| Co(A)SHR                                 | (Arithmetic) Shift right            | 4     |  |  |  |

| CoSHL                                    | Shift left                          | 4     |  |  |  |

| CoLOAD/STORE                             | Load accumulator/Store MAC register | 4     |  |  |  |

| CoCMP                                    | Compare                             | 4     |  |  |  |

| CoMAX/MIN                                | Maximum/Minimum                     | 4     |  |  |  |

| CoABS/CoRND                              | Absolute value/Round accumulator    | 4     |  |  |  |

| CoMOV                                    | Data move                           | 4     |  |  |  |

| CoNEG/NOP                                | Negate accumulator/Null operation   | 4     |  |  |  |

1) The Enter Power Down Mode instruction is not used in the XE167, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

| Parameter                                         | Symbol         | Values |      |      | Unit | Note /                                           |

|---------------------------------------------------|----------------|--------|------|------|------|--------------------------------------------------|

|                                                   |                | Min.   | Тур. | Max. |      | Test Condition                                   |

| External Pin Load<br>Capacitance                  | CL             | -      | 20   | -    | pF   | Pin drivers in <b>default</b> mode <sup>6)</sup> |

| Voltage Regulator Buffer<br>Capacitance for DMP_M | $C_{\rm EVRM}$ | 1.0    | -    | 4.7  | μF   | 7)                                               |

| Voltage Regulator Buffer<br>Capacitance for DMP_1 | $C_{\rm EVR1}$ | 0.47   | -    | 2.2  | μF   | One for each supply pin <sup>7)</sup>            |

| Operating frequency                               | $f_{\rm SYS}$  | -      | -    | 80   | MHz  | 8)                                               |

| Ambient temperature                               | T <sub>A</sub> | _      | _    | _    | °C   | See Table 1                                      |

#### Table 12Operating Condition Parameters (cont'd)

If both core power domains are clocked, the difference between the power supply voltages must be less than 10 mV. This condition imposes additional constraints when using external power supplies. Do not combine internal and external supply of different core power domains.

Do not supply the core power domains with two independent external voltage regulators. The simplest method

Do not supply the core power domains with two independent external voltage regulators. The simplest method is to supply both power domains directly via a single external power supply.

Performance of pad drivers, A/D Converter, and Flash module depends on V<sub>DDP</sub>.

If the external supply voltage V<sub>DDP</sub> becomes lower than the specified operating range, a power reset must be generated. Otherwise, the core supply voltage V<sub>DDI</sub> may rise above its specified operating range due to parasitic effects.

This power reset can be generated by the on-chip SWD. If the SWD is disabled the power reset must be generated by activating the PORST input.

- 3) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{OV} > V_{IHmax}$  ( $I_{OV} > 0$ ) or  $V_{OV} < V_{ILmin}$  ( $I_{OV} < 0$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by  $V_{DDI}$ ).

- 4) Not subject to production test verified by design/characterization.

- 5) An overload current ( $I_{OV}$ ) through a pin injects an error current ( $I_{INJ}$ ) into the adjacent pins. This error current adds to that pin's leakage current ( $I_{OZ}$ ). The value of the error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is reversed from the polarity of the overload current that produces it.

The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 6) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability ( $C_L$ ).

- 7) To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each  $V_{\text{DDI}}$  pin to keep the resistance of the board tracks below 2  $\Omega$ . Connect all  $V_{\text{DDI1}}$  pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 8) The operating frequency range may be reduced for specific types of the XE167. This is indicated in the device designation (...FxxL). 80-MHz devices are marked ...F80L.

## 4.2.2 DC Parameters for Lower Voltage Area

These parameters apply to the lower IO voltage range, 3.0 V  $\leq V_{\text{DDP}} \leq$  4.5 V.

#### Note / Parameter Symbol Values Unit **Test Condition** Min. Тур. Max. V Input low voltage $V_{\parallel}$ SR -0.3 $0.3 \times$ \_ \_ (all except XTAL1) $V_{\rm DDP}$ $V_{\rm IH}\,{\rm SR}$ Input high voltage 0.7 × V $V_{\mathsf{DDP}}$ \_ \_ (all except XTAL1) + 0.3 $V_{\mathsf{DDP}}$ Input Hysteresis<sup>2)</sup> HYS CC 0.07 V $V_{\text{DDP}}$ in [V], \_ \_ Series $\times V_{\text{DDP}}$ resistance = $0 \Omega$ $I_{\rm OL} \leq I_{\rm OLmax}^{3)}$ $V_{OI}$ CC V Output low voltage 1.0 \_ \_ $I_{\rm OL} \leq I_{\rm OLnom}^{3)4)}$ V Output low voltage $V_{OI}$ CC 0.4 $I_{OH} \ge I_{OHmax}^{3)}$ Output high voltage<sup>5)</sup> $V_{OH} CC$ V $V_{\rm DDP}$ \_ - 1.0 $I_{\text{OH}} \ge I_{\text{OHnom}}^{3)4)}$ $V_{OH} CC$ Output high voltage<sup>5)</sup> $V_{\rm DDP}$ V \_ \_ - 0.4 $0 V < V_{IN} < V_{DDP}$ Input leakage current $I_{O71}$ CC \_ ±10 ±200 nA (Port 5, Port 15)<sup>6)</sup> $T_{\rm J} \le 110^{\circ} {\rm C},$ Input leakage current $I_{072}$ CC \_ $\pm 0.2$ $\pm 2.5$ μA (all other)<sup>6)7)</sup> $0.45 V < V_{INI}$ $< V_{\rm DDP}$ $V_{\mathsf{PIN}} \ge V_{\mathsf{IH}} \ (\mathsf{up})^{\mathsf{8}}$ Pull level keep current ±10 μA $I_{\mathsf{PLK}}$ \_ \_ $V_{\text{PIN}} \le V_{\text{IL}}$ (dn) $V_{\mathsf{PIN}} \le V_{\mathsf{IL}} \ (\mathsf{up})^{\mathsf{8}}$ Pull level force current $I_{\mathsf{PLF}}$ ±150 \_ \_ μA $V_{\text{PIN}} \ge V_{\text{IH}} (\text{dn})$ Pin capacitance<sup>9)</sup> $C_{\rm IO}$ CC 10 pF \_ \_ (digital inputs/outputs)

## Table 15DC Characteristics for Lower Voltage Range<br/>(Operating Conditions apply)<sup>1)</sup>

1) Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 13, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

## 4.2.3 Power Consumption

The power consumed by the XE167 depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current  $I_{\rm LK}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  (**Table 16**) and leakage current  $I_{\rm LK}$  (**Table 17**) must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{DDI}$  are charged with the maximum possible current, see parameter  $I_{CC}$  in **Table 20**.

For additional information, please refer to Section 5.2, Thermal Considerations.

# Table 16Switching Power Consumption XE167<br/>(Operating Conditions apply)

| Parameter                                                                    | Sym-              |      | Values                       | 3                            | Unit | Note /                                                |

|------------------------------------------------------------------------------|-------------------|------|------------------------------|------------------------------|------|-------------------------------------------------------|

|                                                                              | bol               | Min. | Тур.                         | Max.                         |      | Test Condition                                        |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub> | -    | 10 +<br>0.6×f <sub>SYS</sub> | 10 +<br>1.0×f <sub>SYS</sub> | mA   | Active mode <sup>1)2)</sup><br>$f_{\rm SYS}$ in [MHz] |

| Power supply current<br>in stopover mode,<br>EVVRs on                        | I <sub>SSO</sub>  | -    | 1.0                          | 2.0                          | mA   | Stopover Mode <sup>2)</sup>                           |

1) The pad supply voltage pins ( $V_{\text{DDPB}}$ ) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers' input stages are switched.

2) The pad supply voltage has only a minor influence on this parameter.

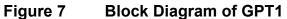

Figure 19 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L$  = 20 pF (see **Table 12**).

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{DDPB}$  pin 100/144 and  $V_{SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| PLLCON0.VCOSEL | VCO Frequency Range | Base Frequency Range |

|----------------|---------------------|----------------------|

| 00             | 50 110 MHz          | 10 40 MHz            |

| 01             | 100 160 MHz         | 20 80 MHz            |

| 1X             | Reserved            |                      |

| Table 25 VCO Bands for PLL Operation <sup>1)</sup> |

|----------------------------------------------------|

|----------------------------------------------------|

1) Not subject to production test - verified by design/characterization.

## 4.6.4 External Bus Timing

The following parameters specify the behavior of the XE167 bus interface.

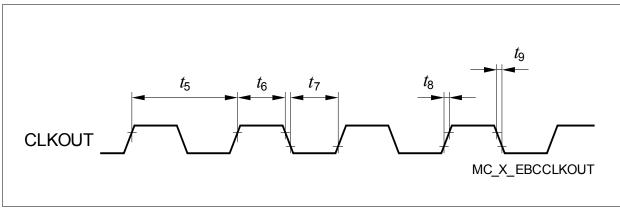

## Table 27 CLKOUT Reference Signal

| Parameter         | Symbol                |    | Limits |                        | Unit | Note / Test |

|-------------------|-----------------------|----|--------|------------------------|------|-------------|

|                   |                       |    | Min.   | Max.                   |      | Condition   |

| CLKOUT cycle time | <i>t</i> <sub>5</sub> | CC | 40     | /25/12.5 <sup>1)</sup> | ns   |             |

| CLKOUT high time  | t <sub>6</sub>        | CC | 3      | _                      | ns   |             |

| CLKOUT low time   | <i>t</i> <sub>7</sub> | CC | 3      | _                      | ns   |             |

| CLKOUT rise time  | <i>t</i> <sub>8</sub> | CC | _      | 3                      | ns   |             |

| CLKOUT fall time  | t <sub>9</sub>        | CC | _      | 3                      | ns   |             |

1) The CLKOUT cycle time is influenced by the PLL jitter (given values apply to  $f_{SYS}$  = 25/40/80 MHz). For longer periods the relative deviation decreases (see PLL deviation formula).

#### Figure 21 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

## XE167x XE166 Family Derivatives

## **Electrical Parameters**

Figure 22 Multiplexed Bus Cycle

## XE167x XE166 Family Derivatives

## **Electrical Parameters**

### Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.