Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M7                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 300MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, SSC, UART/USART     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 44                                                                         |

| Program Memory Size        | 2MB (2M × 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 384K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 5x12b; D/A 1x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70j21a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Bus Matrix (MATRIX)

| Offset | Name          | Bit Pos.       |  |                 |        |           |            |

|--------|---------------|----------------|--|-----------------|--------|-----------|------------|

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  |                 |        | ULBT[2:0] |            |

| 0x2C   | MATRIX_MCFG11 | 15:8           |  |                 |        |           |            |

| 0/120  |               | 23:16          |  |                 |        |           |            |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  |                 |        | ULBT[2:0] |            |

| 0x30   | MATRIX_MCFG12 | 15:8           |  |                 |        |           |            |

|        |               | 23:16          |  |                 |        |           |            |

|        |               | 31:24          |  |                 |        |           |            |

| 0x34   |               |                |  |                 |        |           |            |

|        | Reserved      |                |  |                 |        |           |            |

| 0x3F   |               |                |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x40   | MATRIX_SCFG0  | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x44   | MATRIX_SCFG1  | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x48   | MATRIX_SCFG2  | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        | _             | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        | 0.07.0    |            |

| 0x4C   | MATRIX_SCFG3  | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x50   | MATRIX_SCFG4  | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x54   | MATRIX_SCFG5  | 15:8           |  |                 | D[2,0] |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFINISTR | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        | SLOT C    |            |

| 0x58   | MATRIX_SCFG6  | 15:8           |  | FIXED_DEFMST    | D[3:0] |           | YCLE[8:7]  |

|        |               | 23:16<br>31:24 |  | FIXED_DEFINST   | N[0.0] | DEFINISTR | _TYPE[1:0] |

|        |               | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

|        |               | 15:8           |  |                 |        | SLOT O    |            |

| 0x5C   | MATRIX_SCFG7  |                |  |                 | P[3:0] |           | YCLE[8:7]  |

|        |               | 23:16          |  | FIXED_DEFMST    | N[J.U] | DELINGIK  | _TYPE[1:0] |

|        |               | 31:24          |  |                 |        |           |            |

| 0x60   | MATRIX_SCFG8  | 7:0            |  | SLOT_CYCLE[6:0] |        | SLOT O    |            |

|        |               | 15:8           |  |                 |        | SLUI_C    | YCLE[8:7]  |

## Enhanced Embedded Flash Controller (EEFC)

Bit 16 - UECCELSB Unique ECC Error on LSB Part of the Memory Flash Data Bus (cleared on read)

| Value | Description                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------|

| 0     | No unique error detected on 64 LSB data bus of the Flash memory since the last read of EEFC_FSR.                |

| 1     | One unique error detected but corrected on 64 LSB data bus of the Flash memory since the last read of EEFC_FSR. |

**Bit 3 – FLERR** Flash Error Status (cleared when a programming operation starts)

| Value | Description                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------|

| 0     | No Flash memory error occurred at the end of programming (EraseVerify or WriteVerify test has passed). |

| 1     | A Flash memory error occurred at the end of programming (EraseVerify or WriteVerify test has failed).  |

**Bit 2 – FLOCKE** Flash Lock Error Status (cleared on read)

This flag is automatically cleared when EEFC\_FSR is read or EEFC\_FCR is written.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | No programming/erase of at least one locked region has happened since the last read of |

|       | EEFC_FSR.                                                                              |

| 1     | Programming/erase of at least one locked region has happened since the last read of    |

|       | EEFC_FSR.                                                                              |

**Bit 1 – FCMDE** Flash Command Error Status (cleared on read or by writing EEFC\_FCR)

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | No invalid commands and no bad keywords were written in EEFC_FMR.     |

| 1     | An invalid command and/or a bad keyword was/were written in EEFC_FMR. |

**Bit 0 – FRDY** Flash Ready Status (cleared when Flash is busy)

When set, this flag triggers an interrupt if the FRDY flag is set in EEFC\_FMR.

This flag is automatically cleared when the EEFC is busy.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The EEFC is busy.                         |

| 1     | The EEFC is ready to start a new command. |

#### 23.5.5 Supply Controller Wakeup Inputs Register

| Name:     | SUPC_WUIR  |  |  |  |  |

|-----------|------------|--|--|--|--|

| Offset:   | 0x10       |  |  |  |  |

| Reset:    | 0x00000000 |  |  |  |  |

| Property: | Read/Write |  |  |  |  |

This register is located in the VDDIO domain. This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

| Bit    | 31  | 30  | 29  | 28          | 27      | 26       | 25  | 24  |  |  |  |

|--------|-----|-----|-----|-------------|---------|----------|-----|-----|--|--|--|

|        |     |     |     | WKUPT[13:8] |         |          |     |     |  |  |  |

| Access | L   | •   | R/W | R/W         | R/W     | R/W      | R/W | R/W |  |  |  |

| Reset  |     |     | 0   | 0           | 0       | 0        | 0   | 0   |  |  |  |

|        |     |     |     |             |         |          |     |     |  |  |  |

| Bit    | 23  | 22  | 21  | 20          | 19      | 18       | 17  | 16  |  |  |  |

|        |     |     |     | WKUF        | PT[7:0] |          |     |     |  |  |  |

| Access | R/W | R/W | R/W | R/W         | R/W     | R/W      | R/W | R/W |  |  |  |

| Reset  | 0   | 0   | 0   | 0           | 0       | 0        | 0   | _   |  |  |  |

|        |     |     |     |             |         |          |     |     |  |  |  |

| Bit    | 15  | 14  | 13  | 12          | 11      | 10       | 9   | 8   |  |  |  |

|        |     |     |     |             | WKUPE   | EN[13:8] |     |     |  |  |  |

| Access |     |     | R/W | R/W         | R/W     | R/W      | R/W | R/W |  |  |  |

| Reset  |     |     | 0   | 0           | 0       | 0        | 0   | 0   |  |  |  |

|        |     |     |     |             |         |          |     |     |  |  |  |

| Bit    | 7   | 6   | 5   | 4           | 3       | 2        | 1   | 0   |  |  |  |

|        |     |     |     | WKUP        | EN[7:0] |          |     |     |  |  |  |

| Access | R/W | R/W | R/W | R/W         | R/W     | R/W      | R/W | R/W |  |  |  |

| Reset  | 0   | 0   | 0   | 0           | 0       | 0        | 0   | _   |  |  |  |

|        |     |     |     |             |         |          |     |     |  |  |  |

Bits 29:16 – WKUPT[13:0] Wakeup Input Type ('x' = 0-13)

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | (LOW): A falling edge followed by a low level for a period defined by WKUPDBC on the  |

|       | corresponding wakeup input forces the wakeup of the core power supply.                |

| 1     | (HIGH): A rising edge followed by a high level for a period defined by WKUPDBC on the |

|       | corresponding wakeup input forces the wakeup of the core power supply.                |

#### Bits 13:0 – WKUPEN[13:0] Wakeup Input Enablex ('x' = 0-13)

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | (DISABLE): The corresponding wakeup input has no wakeup effect.                    |

| 1     | (ENABLE): The corresponding wakeup input is enabled for a wakeup of the core power |

|       | supply.                                                                            |

## Parallel Input/Output Controller (PIO)

## 32.6 Register Summary

| Offset | Name     | Bit Pos. |     |      |      |      |      |     |     |       |

|--------|----------|----------|-----|------|------|------|------|-----|-----|-------|

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

| 0x00   |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

|        | PIO_PER  | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

| 004    |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x04   | PIO_PDR  | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x08   | PIO_PSR  | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

| 0x0C   |          |          |     |      |      |      |      |     |     |       |

|        | Reserved |          |     |      |      |      |      |     |     |       |

| 0x0F   |          |          |     |      |      |      |      |     |     |       |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x10   | PIO_OER  | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        | PIO_ODR  | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x14   |          | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x18   | PIO_OSR  | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

| 0x1C   |          |          | -   |      |      |      |      | -   |     |       |

|        | Reserved |          |     |      |      |      |      |     |     |       |

| 0x1F   |          |          |     |      |      |      |      |     |     |       |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x20   | PIO_IFER | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x24   | PIO_IFDR | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P27  | P26 | P25 | P24   |

|        |          | 7:0      | P7  | P6   | P5   | P4   | P3   | P2  | P1  | P0    |

|        |          | 15:8     | P15 | P14  | P13  | P12  | P11  | P10 | P9  | P8    |

| 0x28   | PIO_IFSR | 23:16    | P23 | P22  | P21  | P20  | P19  | P18 | P17 | P16   |

|        |          | 31:24    | P31 | P30  | P29  | P28  | P19  | P16 | P25 | P10   |

|        |          | 01.24    | 101 | 1.50 | 1 23 | 1 20 | 1 21 | 120 | 120 | 1.774 |

### **DMA Controller (XDMAC)**

| Value | Name           | Description                                                          |

|-------|----------------|----------------------------------------------------------------------|

| 0     | FIXED_AM       | The address remains unchanged.                                       |

| 1     | INCREMENTED_AM | The addressing mode is incremented (the increment size is set to the |

|       |                | data size).                                                          |

| 2     | UBS_AM         | The microblock stride is added at the microblock boundary.           |

| 3     | UBS_DS_AM      | The microblock stride is added at the microblock boundary; the data  |

|       |                | stride is added at the data boundary.                                |

#### Bits 17:16 - SAM[1:0] Channel x Source Addressing Mode

| Value | Name           | Description                                                                                               |

|-------|----------------|-----------------------------------------------------------------------------------------------------------|

| 0     | FIXED_AM       | The address remains unchanged.                                                                            |

| 1     | INCREMENTED_AM | The addressing mode is incremented (the increment size is set to the data size).                          |

| 2     | UBS_AM         | The microblock stride is added at the microblock boundary.                                                |

| 3     | UBS_DS_AM      | The microblock stride is added at the microblock boundary, the data stride is added at the data boundary. |

Bit 14 – DIF Channel x Destination Interface Identifier

0 (AHB\_IF0): The data is written through system bus interface 0.

1 (AHB\_IF1): The data is written though system bus interface 1.

#### Bit 13 – SIF Channel x Source Interface Identifier

0 (AHB\_IF0): The data is read through system bus interface 0.

1 (AHB\_IF1): The data is read through system bus interface 1.

#### Bits 12:11 – DWIDTH[1:0] Channel x Data Width

| Value | Name     | Description                     |

|-------|----------|---------------------------------|

| 0     | BYTE     | The data size is set to 8 bits  |

| 1     | HALFWORD | The data size is set to 16 bits |

| 2     | WORD     | The data size is set to 32 bits |

#### Bits 10:8 – CSIZE[2:0] Channel x Chunk Size

| Value | Name   | Description         |

|-------|--------|---------------------|

| 0     | CHK_1  | 1 data transferred  |

| 1     | CHK_2  | 2 data transferred  |

| 2     | CHK_4  | 4 data transferred  |

| 3     | CHK_8  | 8 data transferred  |

| 4     | CHK_16 | 16 data transferred |

#### Bit 7 - MEMSET Channel x Fill Block of Memory

0 (NORMAL\_MODE): Memset is not activated.

1 (HW\_MODE): Sets the block of memory pointed by DA field to the specified value. This operation is performed on 8-, 16- or 32-bit basis.

#### **Bit 6 – SWREQ** Channel x Software Request Trigger

0 (HWR\_CONNECTED): Hardware request line is connected to the peripheral request line.

© 2018 Microchip Technology Inc.

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TPFC<br>0x0C4<br>0x00000000<br>- | P   |     |        |     |     |     |

|--------|-----------------------------------------|---------------------------------------|-----|-----|--------|-----|-----|-----|

| Bit    | 31                                      | 30                                    | 29  | 28  | 27     | 26  | 25  | 24  |

|        |                                         |                                       |     |     |        |     |     |     |

| Access |                                         |                                       |     |     |        |     |     |     |

| Reset  |                                         |                                       |     |     |        |     |     |     |

| Bit    | 23                                      | 22                                    | 21  | 20  | 19     | 18  | 17  | 16  |

|        |                                         |                                       |     |     |        |     |     |     |

| Access |                                         |                                       |     |     | 1      |     |     |     |

| Reset  |                                         |                                       |     |     |        |     |     |     |

| Bit    | 15                                      | 14                                    | 13  | 12  | 11     | 10  | 9   | 8   |

|        |                                         | PQ[7:0]                               |     |     |        |     |     |     |

| Access | R/W                                     | R/W                                   | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                     | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                       |     |     |        |     |     |     |

| Bit    | 7                                       | 6                                     | 5   | 4   | 3      | 2   | 1   | 0   |

|        |                                         |                                       |     |     | ([7:0] |     |     |     |

| Access |                                         | R/W                                   | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                     | 0   | 0   | 0      | 0   | 0   | 0   |

#### 38.8.28 GMAC Transmit PFC Pause Register

#### Bits 15:8 – PQ[7:0] Pause Quantum

When the Remove FCS bit in the GMAC Network Configuration register (GMAC\_NCFGR.RFCS) is written to '1', and one or more bits in this bit field are written to '0', the associated PFC pause frame's pause quantum field value is taken from the Transmit Pause Quantum register (GMAC\_TPQ).

For each entry equal to '1' in this bit field, the pause quantum associated with that entry will be zero.

#### Bits 7:0 – PEV[7:0] Priority Enable Vector

When the Remove FCS bit in the GMAC Network Configuration register (GMAC\_NCFGR.RFCS) is written to '1', the priority enable vector of the PFC priority-based pause frame is set to the value stored in this bit field.

## **USB High-Speed Interface (USBHS)**

- The host starts a SETUP transaction with a SET\_ADDRESS (addr) request.

- The user writes this address to the USB Address (USBHS\_DEVCTRL.UADD) field, and writes a zero to the Address Enable (USBHS\_DEVCTRL.ADDEN) bit, so the actual address is still 0.

- The user sends a zero-length IN packet from the control endpoint.

- The user enables the recorded USB device address by writing a one to USBHS\_DEVCTRL.ADDEN.

Once the USB device address is configured, the controller filters the packets to accept only those targeting the address stored in USBHS\_DEVCTRL.UADD.

USBHS\_DEVCTRL.UADD and USBHS\_DEVCTRL.ADDEN must not be written all at once.

USBHS\_DEVCTRL.UADD and USBHS\_DEVCTRL.ADDEN are cleared:

- on a hardware reset,

- when the USBHS is disabled (USBHS\_CTRL.USBE = 0),

- when a USB reset is detected.

When USBHS\_DEVCTRL.UADD or USBHS\_DEVCTRL.ADDEN is cleared, the default device address 0 is used.

#### 39.5.2.7 Suspend and Wakeup

When an idle USB bus state has been detected for 3 ms, the controller sets the Suspend (USBHS\_DEVISR.SUSP) interrupt bit. The user may then write a one to the USBHS\_CTRL.FRZCLK bit to reduce power consumption.

To recover from the Suspend mode, the user should wait for the Wakeup (USBHS\_DEVISR.WAKEUP) interrupt bit, which is set when a non-idle event is detected, then write a zero to USBHS\_CTRL.FRZCLK.

As the USBHS\_DEVISR.WAKEUP interrupt bit is set when a non-idle event is detected, it can occur whether the controller is in the Suspend mode or not. The USBHS\_DEVISR.SUSP and USBHS\_DEVISR.WAKEUP interrupts are thus independent, except that one bit is cleared when the other is set.

#### 39.5.2.8 Detach

The reset value of the USBHS\_DEVCTRL.DETACH bit is one.

It is possible to initiate a device re-enumeration by simply writing a one, and then a zero, to USBHS\_DEVCTRL.DETACH.

USBHS\_DEVCTRL.DETACH acts on the pull-up connections of the D+ and D- pads. See "Device Mode" for further details.

#### 39.5.2.9 Remote Wakeup

The Remote Wakeup request (also known as Upstream Resume) is the only one the device may send without a host invitation, assuming a host command allowing the device to send such a request was previously issued. The sequence is the following:

- 1. The USBHS must have detected a "Suspend" state on the bus, i.e., the Remote Wakeup request can only be sent after a USBHS\_DEVISR.SUSP interrupt has been set.

- 2. The user writes a one to the Remote Wakeup (USBHS\_DEVCTRL.RMWKUP) bit to send an upstream resume to the host for a remote wakeup. This will automatically be done by the controller after 5 ms of inactivity on the USB bus.

- 3. When the controller sends the upstream resume, the Upstream Resume (USBHS\_DEVISR.UPRSM) interrupt is set and USBHS\_DEVISR.SUSP is cleared.

### **USB High-Speed Interface (USBHS)**

#### 39.6.26 Device Endpoint Interrupt Enable Register (Isochronous Endpoints)

Name:

USBHS\_DEVEPTIERx (ISOENPT)

Offset:

0x01F0 + x\*0x04 [x=0..9]

Reset:

0

Property:

Read/Write

This register view is relevant only if EPTYPE = 0x1 in "Device Endpoint x Configuration Register".

For additional information, see "Device Endpoint x Mask Register (Isochronous Endpoints)".

This register always reads as zero.

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Clears the corresponding bit in USBHS\_DEVEPTIMRx.

| Bit    | 31         | 30       | 29      | 28          | 27          | 26         | 25      | 24         |

|--------|------------|----------|---------|-------------|-------------|------------|---------|------------|

|        |            |          |         |             |             |            |         |            |

| Access |            |          |         |             |             |            |         |            |

| Reset  |            |          |         |             |             |            |         |            |

|        |            |          |         |             |             |            |         |            |

| Bit    | 23         | 22       | 21      | 20          | 19          | 18         | 17      | 16         |

|        |            |          |         |             |             | RSTDTS     |         | EPDISHDMAS |

| Access |            |          |         |             |             |            |         |            |

| Reset  |            |          |         |             |             | 0          |         | 0          |

|        |            |          |         |             |             |            |         |            |

| Bit    | 15         | 14       | 13      | 12          | 11          | 10         | 9       | 8          |

|        |            | FIFOCONS | KILLBKS | NBUSYBKES   |             | ERRORTRANS | DATAXES | MDATAES    |

|        |            |          |         |             |             | ES         |         |            |

| Access |            |          |         |             |             |            |         |            |

| Reset  |            | 0        | 0       | 0           |             | 0          | 0       | 0          |

|        |            |          |         |             |             |            |         |            |

| Bit    | 7          | 6        | 5       | 4           | 3           | 2          | 1       | 0          |

|        | SHORTPACKE | CRCERRES | OVERFES | HBISOFLUSHE | HBISOINERRE | UNDERFES   | RXOUTES | TXINES     |

|        | TES        |          |         | S           | S           |            |         |            |

| Access |            |          |         |             |             |            |         |            |

| Reset  | 0          | 0        | 0       | 0           | 0           | 0          | 0       | 0          |

Bit 18 – RSTDTS Reset Data Toggle Enable

Bit 16 - EPDISHDMAS Endpoint Interrupts Disable HDMA Request Enable

Bit 14 – FIFOCONS FIFO Control

Bit 13 - KILLBKS Kill IN Bank

Bit 12 – NBUSYBKES Number of Busy Banks Interrupt Enable

**Bit 10 – ERRORTRANSES** Transaction Error Interrupt Enable

## **USB High-Speed Interface (USBHS)**

#### 39.6.32 Host Global Interrupt Status Register

| Name:<br>Offset:<br>Reset:<br>Property: |       | USBHS_HST<br>0x0404<br>0x00000000<br>Read-only | ISR   |        |        |       |        |        |

|-----------------------------------------|-------|------------------------------------------------|-------|--------|--------|-------|--------|--------|

| Bit                                     | 31    | 30                                             | 29    | 28     | 27     | 26    | 25     | 24     |

|                                         | DMA_6 | DMA_5                                          | DMA_4 | DMA_3  | DMA_2  | DMA_1 | DMA_0  |        |

| Access                                  |       | -                                              |       |        |        |       |        |        |

| Reset                                   | 0     | 0                                              | 0     | 0      | 0      | 0     | 0      |        |

|                                         |       |                                                |       |        |        |       |        |        |

| Bit                                     | 23    | 22                                             | 21    | 20     | 19     | 18    | 17     | 16     |

|                                         |       |                                                |       |        |        |       | PEP_9  | PEP_8  |

| Access                                  |       |                                                |       |        |        |       |        |        |

| Reset                                   |       |                                                |       |        |        |       | 0      | 0      |

|                                         |       |                                                |       |        |        |       |        |        |

| Bit                                     | [     | 14                                             | 13    | 12     | 11     | 10    | 9      | 8      |

|                                         | PEP_7 | PEP_6                                          | PEP_5 | PEP_4  | PEP_3  | PEP_2 | PEP_1  | PEP_0  |

| Access                                  |       |                                                |       |        |        |       |        |        |

| Reset                                   | 0     | 0                                              | 0     | 0      | 0      | 0     | 0      | 0      |

| D:4                                     | 7     | 6                                              | -     | 4      | 2      | 2     | 4      | 0      |

| Bit                                     | 7     | 6                                              | 5     | 4      | 3      | 2     | 1      | 0      |

|                                         |       | HWUPI                                          | HSOFI | RXRSMI | RSMEDI | RSTI  | DDISCI | DCONNI |

| Access                                  |       |                                                |       |        |        |       |        |        |

| Reset                                   |       | 0                                              | 0     | 0      | 0      | 0     | 0      | 0      |

#### Bits 25, 26, 27, 28, 29, 30, 31 - DMA\_ DMA Channel x Interrupt

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Cleared when the USBHS_HSTDMASTATUSx interrupt source is cleared.                                                                    |

| 1     | Set when an interrupt is triggered by the DMA channel x. This triggers a USB interrupt if the corresponding bit in USBHS_HSTIMR = 1. |

#### Bits 8, 9, 10, 11, 12, 13, 14, 15, 16, 17 – PEP\_ Pipe x Interrupt

| Value | Description                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Cleared when the interrupt source is served.                                                                                                 |

| 1     | Set when an interrupt is triggered by pipe x (USBHS_HSTPIPISRx). This triggers a USB interrupt if the corresponding bit in USBHS_HSTIMR = 1. |

#### Bit 6 – HWUPI Host Wakeup Interrupt

This bit is set when the host controller is in Suspend mode (SOFE = 0) and an upstream resume from the peripheral is detected.

This bit is set when the host controller is in Suspend mode (SOFE = 0) and a peripheral disconnection is detected.

This interrupt is generated even if the clock is frozen by the USBHS\_CTRL.FRZCLK bit.

© 2018 Microchip Technology Inc.

### **USB High-Speed Interface (USBHS)**

Value Description

• (INRQ+1) in requests have been processed.

• A Pipe Reset (USBHS\_HSTPIP.PRSTx rising) has occurred.

• A Pipe Enable (USBHS\_HSTPIP.PEN rising) has occurred.

**Bit 16 – PDISHDMA** Pipe Interrupts Disable HDMA Request Enable See the USBHS\_DEVEPTIMR.EPDISHDMA bit description.

## Bit 14 – FIFOCON FIFO Control

For OUT and SETUP pipes:

0: Cleared when USBHS\_HSTPIPIDR.FIFOCONC = 1. This sends the FIFO data and switches the bank.

1: Set when the current bank is free, at the same time as USBHS\_HSTPIPISR.TXOUTI or TXSTPI.

For IN pipes:

0: Cleared when USBHS\_HSTPIPIDR.FIFOCONC = 1. This frees the current bank and switches to the next bank.

1: Set when a new IN message is stored in the current bank, at the same time as USBHS\_HSTPIPISR.RXINI.

#### Bit 12 – NBUSYBKE Number of Busy Banks Interrupt Enable

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.NBUSYBKEC = 1. This disables the Transmitted IN |

|       | Data interrupt (USBHS_HSTPIPIMR.NBUSYBKE).                                   |

| 1     | Set when USBHS_HSTPIPIER.NBUSYBKES = 1. This enables the Transmitted IN Data |

|       | interrupt (USBHS_HSTPIPIMR.NBUSYBKE).                                        |

#### Bit 7 – SHORTPACKETIE Short Packet Interrupt Enable

If this bit is set for non-control OUT pipes, a short packet transmission is guaranteed upon ending a DMA transfer, thus signaling an end of transfer, provided that the End of DMA Buffer Output Enable (USBHS\_HSTDMACONTROL.END\_B\_EN) bit and the Automatic Switch (USBHS\_HSTPIPCFG.AUTOSW) bit = 1.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.SHORTPACKETEC = 1. This disables the Transmitted |

|       | IN Data interrupt (USBHS_HSTPIPIMR.SHORTPACKETE).                             |

| 1     | Set when USBHS_HSTPIPIER.SHORTPACKETIES = 1. This enables the Transmitted IN  |

|       | Data interrupt (USBHS_HSTPIPIMR.SHORTPACKETIE).                               |

#### **Bit 6 – RXSTALLDE** Received STALLed Interrupt Enable

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.RXSTALLDEC = 1. This disables the Transmitted IN |

|       | Data interrupt (USBHS_HSTPIPIMR.RXSTALLDE).                                   |

| 1     | Set when USBHS_HSTPIPIER.RXSTALLDES= 1. This enables the Transmitted IN Data  |

|       | interrupt (USBHS_HSTPIPIMR.RXSTALLDE).                                        |

Bit 5 – OVERFIE Overflow Interrupt Enable

## Serial Peripheral Interface (SPI)

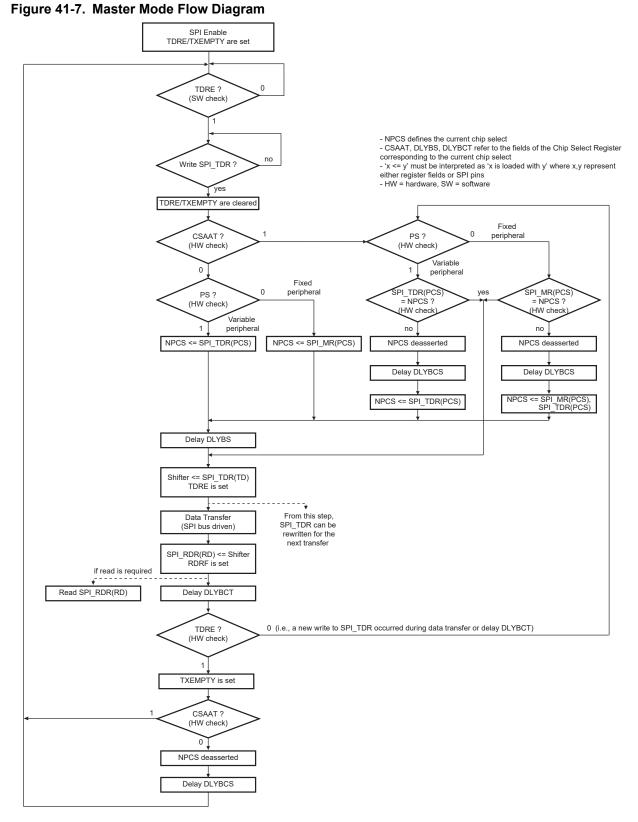

### 41.7.3.2 Master Mode Flow Diagram

## Serial Peripheral Interface (SPI)

#### 41.8.3 SPI Receive Data Register

| Name:     | SPI_RDR   |

|-----------|-----------|

| Offset:   | 0x08      |

| Reset:    | 0x0       |

| Property: | Read-only |

| Bit    | 31 | 30 | 29 | 28               | 27    | 26  | 25    | 24 |

|--------|----|----|----|------------------|-------|-----|-------|----|

|        |    |    |    |                  |       |     |       |    |

| Access |    |    |    |                  |       |     |       |    |

| Reset  |    |    |    |                  |       |     |       |    |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 23 | 22 | 21 | 20               | 19    | 18  | 17    | 16 |

|        |    |    |    |                  |       | PCS | [3:0] |    |

| Access |    |    |    |                  | R     | R   | R     | R  |

| Reset  |    |    |    |                  | 0     | 0   | 0     | 0  |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 15 | 14 | 13 | 12               | 11    | 10  | 9     | 8  |

|        |    |    |    | RD[ <sup>2</sup> | 15:8] |     |       |    |

| Access | R  | R  | R  | R                | R     | R   | R     | R  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 7  | 6  | 5  | 4                | 3     | 2   | 1     | 0  |

|        |    |    |    | RD[              | [7:0] |     |       |    |

| Access | R  | R  | R  | R                | R     | R   | R     | R  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

#### Bits 19:16 – PCS[3:0] Peripheral Chip Select

In Master mode only, these bits indicate the value on the NPCS pins at the end of a transfer. Otherwise, these bits are read as zero.

When using Variable Peripheral Select mode (PS = 1 in SPI\_MR), it is mandatory to set SPI\_MR.WDRBT bit if the PCS field must be processed in SPI\_RDR.

#### Bits 15:0 - RD[15:0] Receive Data

Data received by the SPI Interface is stored in this register in a right-justified format. Unused bits are read as zero.

## Media Local Bus (MLB)

| Value | e Description                                             |

|-------|-----------------------------------------------------------|

| 0     | Hardware clears interrupt after a MLB_ACSRn register read |

| 1     | Software writes a '1' to clear                            |

## **Controller Area Network (MCAN)**

#### 49.6.9 MCAN Timestamp Counter Configuration Register

| Name:     | MCAN_TSCC  |  |  |

|-----------|------------|--|--|

| Offset:   | 0x20       |  |  |

| Reset:    | 0x00000000 |  |  |

| Property: | Read/Write |  |  |

For a description of the Timestamp Counter see Timestamp Generation.

With CAN FD, an external counter is required for timestamp generation (TSS = 2).

| Bit    | 31 | 30 | 29 | 28 | 27  | 26  | 25    | 24    |

|--------|----|----|----|----|-----|-----|-------|-------|

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19  | 18  | 17    | 16    |

|        |    |    |    |    |     | TCP | [3:0] |       |

| Access |    |    |    |    | R/W | R/W | R/W   | R/W   |

| Reset  |    |    |    |    | 0   | 0   | 0     | 0     |

|        |    |    |    |    |     |     |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11  | 10  | 9     | 8     |

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3   | 2   | 1     | 0     |

|        |    |    |    |    |     |     |       | [1:0] |

| Access |    |    |    |    |     |     | R/W   | R/W   |

| Reset  |    |    |    |    |     |     | 0     | 0     |

#### Bits 19:16 – TCP[3:0] Timestamp Counter Prescaler

Configures the timestamp and timeout counters time unit in multiples of CAN bit times [1...16]. The actual interpretation by the hardware of this value is such that one more than the value programmed here is used.

| Bits 1:0 - TSS[ | 1:0] Timest | amp Select |

|-----------------|-------------|------------|

|-----------------|-------------|------------|

| Value | Name          | Description                                          |

|-------|---------------|------------------------------------------------------|

| 0     | ALWAYS_0      | Timestamp counter value always 0x0000                |

| 1     | TCP_INC       | Timestamp counter value incremented according to TCP |

| 2     | EXT_TIMESTAMP | External timestamp counter value used                |

| 3     | ALWAYS_0      | Timestamp counter value always 0x0000                |

#### 50.6 Functional Description

#### 50.6.1 Description

All channels of the Timer Counter are independent and identical in operation except when the QDEC is enabled. The registers for channel programming are listed in 50.7 Register Summary.

#### 50.6.2 16-bit Counter

Each 16-bit channel is organized around a 16-bit counter. The value of the counter is incremented at each positive edge of the selected clock. When the counter has reached the value 2<sup>16</sup>-1 and passes to zero, an overflow occurs and the COVFS bit in the Interrupt Status register (TC\_SR) is set.

The current value of the counter is accessible in real time by reading the Counter Value register (TC\_CV). The counter can be reset by a trigger. In this case, the counter value passes to zero on the next valid edge of the selected clock.

#### 50.6.3 Clock Selection

At block level, input clock signals of each channel can be connected either to the external inputs TCLKx, or to the internal I/O signals TIOAx for chaining<sup>(1)</sup> by programming the Block Mode register (TC\_BMR). See Clock Chaining Selection.

Each channel can independently select an internal or external clock source for its counter<sup>(2)</sup>:

- External clock signals: XC0, XC1 or XC2

- Internal clock signals: PCK6 or PCK7 (TC0 only), MCK/8, MCK/32, MCK/128, SLCK

This selection is made by the TCCLKS bits in the Channel Mode register (TC\_CMRx).

The selected clock can be inverted with TC\_CMRx.CLKI. This allows counting on the opposite edges of the clock.

The burst function allows the clock to be validated when an external signal is high. The BURST parameter in the TC\_CMRx defines this signal (none, XC0, XC1, XC2). See Clock Selection.

#### Note:

- 1. In Waveform mode, to chain two timers, it is mandatory to initialize some parameters:

- Configure TIOx outputs to 1 or 0 by writing the required value to TC\_CMRx.ASWTRG.

- Bit TC\_BCR.SYNC must be written to 1 to start the channels at the same time.

- 2. In all cases, if an external clock or asynchronous internal clock PCK6 or PCK7 (TC0 only) is used, the duration of each of its levels must be longer than the peripheral clock period, so the clock frequency will be at least 2.5 times lower than the peripheral clock.

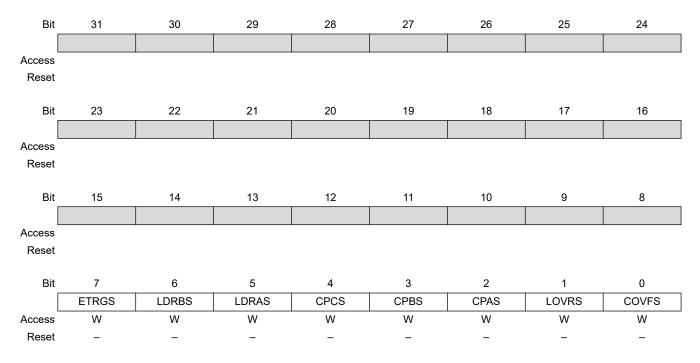

#### 50.7.11 TC Interrupt Enable Register

Name:

TC\_IERx

Offset:

0x24 + x\*0x40 [x=0..2]

Reset:

Property:

Write-only

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

Bit 7 – ETRGS External Trigger

Bit 6 - LDRBS RB Loading

Bit 5 - LDRAS RA Loading

Bit 4 – CPCS RC Compare

Bit 3 – CPBS RB Compare

Bit 2 – CPAS RA Compare

Bit 1 – LOVRS Load Overrun

Bit 0 - COVFS Counter Overflow

## **Advanced Encryption Standard (AES)**

#### 57.5.9 AES Output Data Register x

| Name:     | AES_ODATARx          |

|-----------|----------------------|

| Offset:   | 0x50 + x*0x04 [x=03] |

| Reset:    | 0x0000000            |

| Property: | Read-only            |

| Bit    | 31           | 30 | 29 | 28    | 27      | 26 | 25 | 24 |  |

|--------|--------------|----|----|-------|---------|----|----|----|--|

|        | ODATA[31:24] |    |    |       |         |    |    |    |  |

| Access | R            | R  | R  | R     | R       | R  | R  | R  |  |

| Reset  | 0            | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |

|        |              |    |    |       |         |    |    |    |  |

| Bit    | 23           | 22 | 21 | 20    | 19      | 18 | 17 | 16 |  |

|        |              |    |    | ODATA | [23:16] |    |    |    |  |

| Access | R            | R  | R  | R     | R       | R  | R  | R  |  |

| Reset  | 0            | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |

|        |              |    |    |       |         |    |    |    |  |

| Bit    | 15           | 14 | 13 | 12    | 11      | 10 | 9  | 8  |  |

|        |              |    |    | ODAT  | A[15:8] |    |    |    |  |

| Access | R            | R  | R  | R     | R       | R  | R  | R  |  |

| Reset  | 0            | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |

|        |              |    |    |       |         |    |    |    |  |

| Bit    | 7            | 6  | 5  | 4     | 3       | 2  | 1  | 0  |  |

|        |              |    |    | ODAT  | A[7:0]  |    |    |    |  |

| Access | R            | R  | R  | R     | R       | R  | R  | R  |  |

| Reset  | 0            | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |

|        |              |    |    |       |         |    |    |    |  |

#### Bits 31:0 - ODATA[31:0] Output Data

The four 32-bit Output Data registers contain the 128-bit data block that has been encrypted/decrypted. AES\_ODATAR0 corresponds to the first word, AES\_ODATAR3 to the last one.

## **Electrical Characteristics for SAM E70/S70**

| Symbol            | VDDIO Supply                                                                              | 1.8V Domain | 3.3V Domain | 1.8V<br>Domain | 3.3V<br>Domain | Unit |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------|-------------|----------------|----------------|------|--|

|                   | Parameter                                                                                 | Min         |             | Мах            |                |      |  |

| NO HOL            | NO HOLD Settings (NWE_HOLD = 0)                                                           |             |             |                |                |      |  |

| SMC <sub>21</sub> | NWE High to<br>Data OUT,<br>NBS0/A0<br>NBS1, A1, A2–<br>A25, NCS<br>change <sup>(1)</sup> | 2.1         | 1.5         | -              | -              | ns   |  |

Note:

Hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "NCS\_WR\_HOLD length" or "NWE\_HOLD length"

| Symbol            | ymbol VDDIO Supply 1.8V Domain 3.3V Domain  |                                                                  | 3.3V Domain                                                             | 1.8V<br>Domain | 3.3V<br>Domain | Unit |

|-------------------|---------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|----------------|------|

|                   | Parameter                                   | Min                                                              |                                                                         | Мах            |                |      |

| SMC <sub>22</sub> | Data Out Valid<br>before NCS<br>High        | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 2.8                       | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 3.9                              | _              |                | ns   |

| SMC <sub>23</sub> | NCS Pulse<br>Width                          | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 0.9                       | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 0.2                              | —              | —              | ns   |

| SMC <sub>24</sub> | A0–A22 valid<br>before NCS<br>low           | NCS_WR_SETUP ×<br>t <sub>CPMCK</sub> - 4.0                       | NCS_WR_SETUP ×<br>t <sub>CPMCK</sub> - 4.6                              |                |                | ns   |

| SMC <sub>25</sub> | NWE low<br>before NCS<br>high               | (NCS_WR_SETUP -<br>NWE_SETUP + NCS<br>pulse) × $t_{CPMCK}$ - 4.6 | (NCS_WR_SETUP -<br>NWE_SETUP + NCS<br>pulse) × t <sub>CPMCK</sub> - 4.6 |                |                | ns   |

| SMC <sub>26</sub> | NCS High to<br>Data Out, A0–<br>A25, change | NCS_WR_HOLD ×<br>t <sub>CPMCK</sub> - 4.4                        | NCS_WR_HOLD ×<br>t <sub>CPMCK</sub> - 3.4                               |                |                | ns   |

| SMC <sub>27</sub> | NCS High to<br>NWE Inactive                 | (NCS_WR_HOLD -<br>NWE_HOLD) × t <sub>CPMCK</sub><br>- 2.8        | (NCS_WR_HOLD -<br>NWE_HOLD) × t <sub>CPMCK</sub><br>- 2.4               |                |                | ns   |

#### Table 59-63. SMC Write NCS Controlled (WRITE\_MODE = 0)

Timings are given in the 3.3V domain, with VDDIO from 2.85V to 3.6V, maximum external capacitor = 50 pF.

Timings are given assuming a capacitance load on data, control and address pads.

In the tables that follow,  $t_{CPMCK}$  is MCK period.

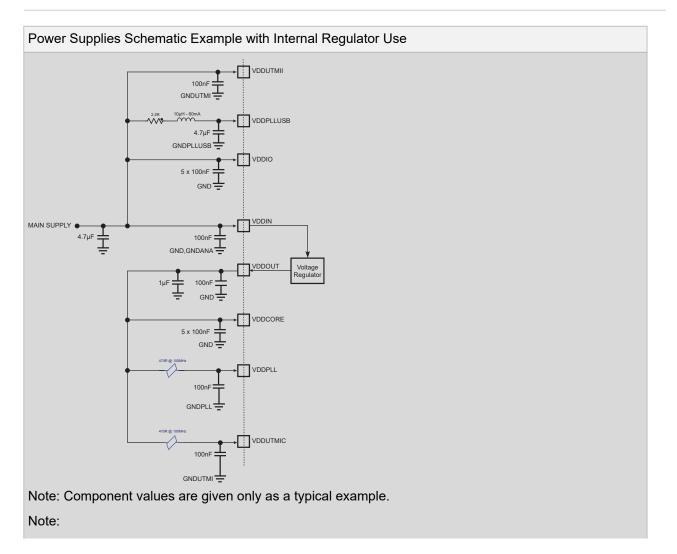

## 60. Schematic Checklist

The schematic checklist provides the user with the requirements regarding the different pin connections that must be considered before starting any new board design. It also provides information on the minimum hardware resources required to quickly develop an application with the SAM E70/S70/V70/V71 device. It does not consider PCB layout constraints.

This information is not intended to be exhaustive. Its objective is to cover as many configurations of use as possible. The checklist contains a column for use by designers, making it easy to track and verify each line item.

### 60.1 **Power Supplies**

#### 60.1.1 Supplying the Device With Only One Supply

$\triangle$  CAUTION To guarantee reliable operation of the device, the board design must comply with powerup and powerdown sequence guidelines provided in the "Power Considerations" chapter.

© 2017, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-2900-5

## Quality Management System Certified by DNV

#### ISO/TS 16949

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.