#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 300MHz                                                                                    |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                              |

| Number of I/O              | 75                                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                |                                                                                           |

| RAM Size                   | 256K × 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-TFBGA                                                                                 |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70n19a-cnt                |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Power Management Controller (PMC)**

# 31.20.24 PMC Peripheral Clock Disable Register 1

| Name:     | PMC_PCDR1  |

|-----------|------------|

| Offset:   | 0x104      |

| Property: | Write-only |

This register can only be written if the WPEN bit is cleared in the PCM Write Protection Mode Register

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| [      |       | PID62 |       | PID60 | PID59 | PID58 | PID57 | PID56 |

| Access |       |       |       |       | •     |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| [      |       |       | PID53 | PID52 | PID51 | PID50 | PID49 | PID48 |

| Access |       | •     |       |       | •     |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| [      | PID47 | PID46 | PID45 | PID44 | PID43 | PID42 | PID41 | PID40 |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        | PID39 |       | PID37 |       | PID35 | PID34 | PID33 | PID32 |

| Access |       |       |       |       | •     |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

### Bits 0:3,5,7:28,30 - PID Peripheral Clock x Disable

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | No effect.                                   |

| 1     | Disables the corresponding peripheral clock. |

Note: "PIDx" refers to identifiers as defined in the section "Peripheral Identifiers".

# Parallel Input/Output Controller (PIO)

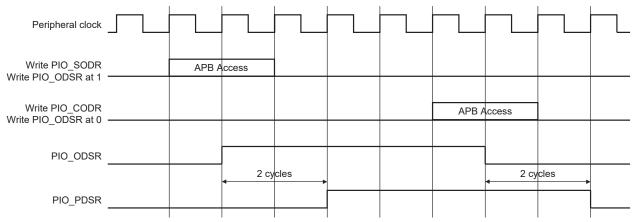

### Figure 32-3. Output Line Timings

## 32.5.8 Inputs

The level on each I/O line can be read through PIO\_PDSR. This register indicates the level of the I/O lines regardless of their configuration, whether uniquely as an input, or driven by the PIO Controller, or driven by a peripheral.

Reading the I/O line levels requires the clock of the PIO Controller to be enabled, otherwise PIO\_PDSR reads the levels present on the I/O line at the time the clock was disabled.

## 32.5.9 Input Glitch and Debouncing Filters

Optional input glitch and debouncing filters are independently programmable on each I/O line.

The glitch filter can filter a glitch with a duration of less than 1/2 peripheral clock and the debouncing filter can filter a pulse of less than 1/2 period of a programmable divided slow clock.

The selection between glitch filtering or debounce filtering is done by writing in the PIO Input Filter Slow Clock Disable Register (PIO\_IFSCDR) and the PIO Input Filter Slow Clock Enable Register (PIO\_IFSCER). Writing PIO\_IFSCDR and PIO\_IFSCER, respectively, sets and clears bits in the Input Filter Slow Clock Status Register (PIO\_IFSCSR).

The current selection status can be checked by reading the PIO\_IFSCSR.

- If PIO\_IFSCSR[i] = 0: The glitch filter can filter a glitch with a duration of less than 1/2 master clock period.

- If PIO\_IFSCSR[i] = 1: The debouncing filter can filter a pulse with a duration of less than 1/2 programmable divided slow clock period.

For the debouncing filter, the period of the divided slow clock is defined by writing in the DIV field of the Slow Clock Divider Debouncing Register (PIO\_SCDR):

$t_{div\_slck} = ((DIV + 1) \times 2) \times t_{slck}$

When the glitch or debouncing filter is enabled, a glitch or pulse with a duration of less than 1/2 selected clock cycle (selected clock represents peripheral clock or divided slow clock depending on PIO\_IFSCDR and PIO\_IFSCER programming) is automatically rejected, while a pulse with a duration of one selected clock (peripheral clock or divided slow clock) cycle or more is accepted. For pulse durations between 1/2 selected clock cycle and one selected clock cycle, the pulse may or may not be taken into account, depending on the precise timing of its occurrence. Thus for a pulse to be visible, it must exceed one selected clock cycle, whereas for a glitch to be reliably filtered out, its duration must not exceed 1/2 selected clock cycle.

© 2018 Microchip Technology Inc.

- 2. Allocate an area 8N bytes for the transmit buffer descriptor list in system memory and create N entries in this list. Mark all entries in this list as owned by GMAC, i.e., bit 31 of word 1 set to 0.

- 3. Mark the last descriptor in the queue with the wrap bit (bit 30 in word 1 set to 1).

- 4. Write address of transmit buffer descriptor list and control information to GMAC register transmit buffer queue pointer.

- 5. The transmit circuits can then be enabled by writing to the Network Control register.

**Note:** The queue pointers must be initialized and point to USED descriptors for all queues including those not intended for use.

#### 38.7.1.4 Address Matching

The GMAC Hash register pair and the four Specific Address register pairs must be written with the required values. Each register pair comprises of a bottom register and top register, with the bottom register being written first. The address matching is disabled for a particular register pair after the bottom register has been written and re-enabled when the top register is written. Each register pair may be written at any time, regardless of whether the receive circuits are enabled or disabled.

As an example, to set Specific Address register 1 to recognize destination address 21:43:65:87:A9:CB, the following values are written to Specific Address register 1 bottom and Specific Address register 1 top:

- Specific Address register 1 bottom bits 31:0 (0x98): 0x8765\_4321.

- Specific Address register 1 top bits 31:0 (0x9C): 0x0000\_CBA9.

Note: The address matching is the first level of filtering. If there is a match, the screeners are the next level of filtering for routing the data to the appropriate queue. See Priority Queueing in the DMA for more details.

## 38.7.1.5 PHY Maintenance

The PHY Maintenance register is implemented as a shift register. Writing to the register starts a shift operation which is signalled as complete when bit two is set in the Network Status register (about 2000 MCK cycles later when bits 18:16 are set to 010 in the Network Configuration register). An interrupt is generated as this bit is set.

During this time, the MSB of the register is output on the MDIO pin and the LSB updated from the MDIO pin with each Management Data Clock (MDC) cycle. This causes the transmission of a PHY management frame on MDIO. See section 22.2.4.5 of the IEEE 802.3 standard.

Reading during the shift operation will return the current contents of the shift register. At the end of the management operation the bits will have shifted back to their original locations. For a read operation the data bits are updated with data read from the PHY. It is important to write the correct values to the register to ensure a valid PHY management frame is produced.

The Management Data Clock (MDC) should not toggle faster than 2.5 MHz (minimum period of 400 ns), as defined by the IEEE 802.3 standard. MDC is generated by dividing down MCK. Three bits in the Network Configuration register determine by how much MCK should be divided to produce MDC.

#### 38.7.1.6 Interrupts

There are 18 interrupt conditions that are detected within the GMAC. The conditions are ORed to make multiple interrupts. Depending on the overall system design this may be passed through a further level of interrupt collection (interrupt controller). On receipt of the interrupt signal, the CPU enters the interrupt handler. Refer to the device interrupt controller documentation to identify that it is the GMAC that is generating the interrupt. To ascertain which interrupt, read the Interrupt Status register. Note that in the default configuration this register will clear itself after being read, though this may be configured to be write-one-to-clear if desired.

# **GMAC - Ethernet MAC**

| Bit    | 31        | 30    | 29  | 28        | 27     | 26  | 25     | 24     |

|--------|-----------|-------|-----|-----------|--------|-----|--------|--------|

|        | WZO       | CLTTO | OP  | [1:0]     |        | PHY | 4[4:1] |        |

| Access | R/W       | R/W   | R/W | R/W       | R/W    | R/W | R/W    | R/W    |

| Reset  | 0         | 0     | 0   | 0         | 0      | 0   | 0      | 0      |

|        |           |       |     |           |        |     |        |        |

| Bit    | 23        | 22    | 21  | 20        | 19     | 18  | 17     | 16     |

|        | PHYA[0:0] |       |     | REGA[4:0] |        |     | WTN    | I[1:0] |

| Access | R/W       | R/W   | R/W | R/W       | R/W    | R/W | R/W    | R/W    |

| Reset  | 0         | 0     | 0   | 0         | 0      | 0   | 0      | 0      |

|        |           |       |     |           |        |     |        |        |

| Bit    | 15        | 14    | 13  | 12        | 11     | 10  | 9      | 8      |

|        |           |       |     | DATA      | [15:8] |     |        |        |

| Access | R/W       | R/W   | R/W | R/W       | R/W    | R/W | R/W    | R/W    |

| Reset  | 0         | 0     | 0   | 0         | 0      | 0   | 0      | 0      |

|        |           |       |     |           |        |     |        |        |

| Bit    | 7         | 6     | 5   | 4         | 3      | 2   | 1      | 0      |

|        | DATA[7:0] |       |     |           |        |     |        |        |

| Access | R/W       | R/W   | R/W | R/W       | R/W    | R/W | R/W    | R/W    |

| Reset  | 0         | 0     | 0   | 0         | 0      | 0   | 0      | 0      |

|        |           |       |     |           |        |     |        |        |

#### Bit 31 – WZO Write ZERO

Must be written to '0'.

| Value | Description |

|-------|-------------|

| 0     | Mandatory   |

| 1     | Reserved    |

# Bit 30 – CLTTO Clause 22 Operation

| Value | Description         |

|-------|---------------------|

| 0     | Clause 45 operation |

| 1     | Clause 22 operation |

# Bits 29:28 - OP[1:0] Operation

| Value | Description |

|-------|-------------|

| 01    | Write       |

| 10    | Read        |

| Other | Reseved     |

# Bits 27:23 - PHYA[4:0] PHY Address

**Bits 22:18 – REGA[4:0]** Register Address Specifies the register in the PHY to access.

Bits 17:16 – WTN[1:0] Write Ten Must be written to '10'.

| Value | Description |

|-------|-------------|

| 10    | Mandatory   |

| Other | Reserved    |

© 2018 Microchip Technology Inc.

# USB High-Speed Interface (USBHS)

## 39.6.16 Device Endpoint Interrupt Status Register (Isochronous Endpoints)

| Name:     | USBHS_DEVEPTISRx (ISOENPT) |

|-----------|----------------------------|

| Offset:   | 0x0130 + x*0x04 [x=09]     |

| Reset:    | 0                          |

| Property: | Read/Write                 |

This register view is relevant only if EPTYPE = 0x1 in the "Device Endpoint x Configuration Register".

| Bit    | 31         | 30         | 29     | 28          | 27          | 26         | 25     | 24     |  |

|--------|------------|------------|--------|-------------|-------------|------------|--------|--------|--|

|        |            | BYCT[10:4] |        |             |             |            |        |        |  |

| Access |            |            |        |             |             |            |        |        |  |

| Reset  |            | 0          | 0      | 0           | 0           | 0          | 0      | 0      |  |

|        |            |            |        |             |             |            |        |        |  |

| Bit    | 23         | 22         | 21     | 20          | 19          | 18         | 17     | 16     |  |

|        |            | BYC        | Г[3:0] |             |             | CFGOK      |        | RWALL  |  |

| Access |            |            |        |             |             |            |        |        |  |

| Reset  | 0          | 0          | 0      | 0           |             | 0          |        | 0      |  |

|        |            |            |        |             |             |            |        |        |  |

| Bit    | 15         | 14         | 13     | 12          | 11          | 10         | 9      | 8      |  |

|        | CURRE      | 3K[1:0]    | NBUSY  | /BK[1:0]    |             | ERRORTRANS | DTSE   | Q[1:0] |  |

| Access |            |            |        |             |             |            |        |        |  |

| Reset  | 0          | 0          | 0      | 0           |             | 0          | 0      | 0      |  |

|        |            |            |        |             |             |            |        |        |  |

| Bit    | 7          | 6          | 5      | 4           | 3           | 2          | 1      | 0      |  |

|        | SHORTPACKE | CRCERRI    | OVERFI | HBISOFLUSHI | HBISOINERRI | UNDERFI    | RXOUTI | TXINI  |  |

|        | т          |            |        |             |             |            |        |        |  |

| Access | I          |            |        |             |             |            |        |        |  |

| Reset  | 0          | 0          | 0      |             |             |            |        |        |  |

#### Bits 30:20 - BYCT[10:0] Byte Count

This field is set with the byte count of the FIFO.

For IN endpoints, the field is incremented after each byte written by the software into the endpoint and decremented after each byte sent to the host.

For OUT endpoints, the field is incremented after each byte received from the host and decremented after each byte read by the software from the endpoint.

This field may be updated one clock cycle after the RWALL bit changes, so the user should not poll this field as an interrupt bit.

Bit 18 – CFGOK Configuration OK Status

This bit is updated when USBHS\_DEVEPTCFGx.ALLOC = 1.

This bit is set if the endpoint x number of banks (USBHS\_DEVEPTCFGx.EPBK) and size (USBHS\_DEVEPTCFGx.EPSIZE) are correct compared to the maximal allowed number of banks and size for this endpoint and to the maximal FIFO size (i.e., the DPRAM size).

If this bit is cleared, the user should rewrite correct values to the USBHS\_DEVEPTCFGx.EPBK and USBHS\_DEVEPTCFGx.EPSIZE fields.

© 2018 Microchip Technology Inc.

$\triangle$  WARNING In SDIO Byte and Block modes (TRTYP = 4 or 5), writing the 7 last bits of BCNT field with a value which differs from 0 is forbidden and may lead to unpredictable results.

# **Quad Serial Peripheral Interface (QSPI)**

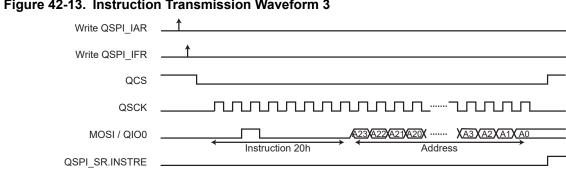

# Figure 42-13. Instruction Transmission Waveform 3

# Example 4:

Instruction in Single-bit SPI, without address, without option, with data write in Single-bit SPI.

Command: SET BURST (77h)

- Write 0x0000 0077 in QSPI ICR.

- Write 0x0000 2090 in QSPI IFR.

- Read QSPI\_IFR (dummy read) to synchronize system bus accesses.

- Write data in the system bus memory space (0x8000000). The address of system bus write accesses is not used.

- Write a '1' to QSPI CR.LASTXFR.

- Wait for QSPI SR.INSTRE to rise.

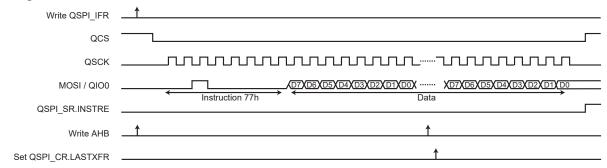

## Figure 42-14. Instruction Transmission Waveform 4

#### Example 5:

Instruction in Single-bit SPI, with address in Dual SPI, without option, with data write in Dual SPI.

# Command: BYTE/PAGE PROGRAM (02h)

- Write 0x0000 0002 in QSPI ICR.

- Write 0x0000 30B3 in QSPI IFR.

- Read QSPI IFR (dummy read) to synchronize system bus accesses.

- Write data in the QSPI system bus memory space (0x8000000). The address of the first system bus write access is sent in the instruction frame. The address of the next system bus write accesses is not used.

- Write a '1' to QSPI CR.LASTXFR.

- Wait for QSPI\_SR.INSTRE to rise.

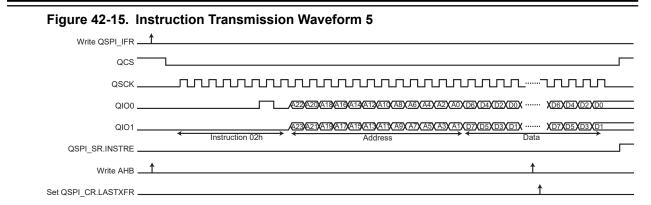

# **Quad Serial Peripheral Interface (QSPI)**

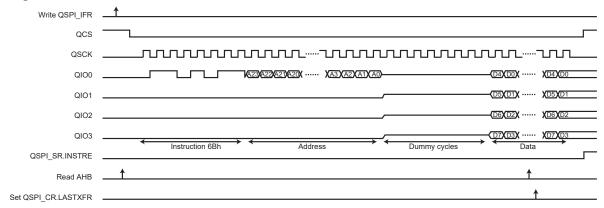

# Example 6:

Instruction in Single-bit SPI, with address in Single-bit SPI, without option, with data read in Quad SPI, with eight dummy cycles.

Command: QUAD\_OUTPUT READ ARRAY (6Bh)

- Write 0x0000\_006B in QSPI\_ICR.

- Write 0x0008\_10B2 in QSPI\_IFR.

- Read QSPI\_IR (dummy read) to synchronize system bus accesses.

- Read data in the QSPI system bus memory space (0x80000000).

The address of the first system bus read access is sent in the instruction frame.

The address of the next system bus read accesses is not used.

- Write a '1' to QSPI\_CR.LASTXFR.

- Wait for QSPI\_SR.INSTRE to rise.

# Figure 42-16. Instruction Transmission Waveform 6

# Example 7:

Instruction in Single-bit SPI, with address and option in Quad SPI, with data read in Quad SPI, with four dummy cycles, with fetch and continuous read.

Command: FAST READ QUAD I/O (EBh) - 8-BIT OPTION (0x30h)

- Write 0x0030\_00EB in QSPI\_ICR.

- Write 0x0004\_33F4 in QSPI\_IFR.

- Read QSPI\_IFR (dummy read) to synchronize system bus accesses.

- Read data in the QSPI system bus memory space (0x8000000). Fetch is enabled, the address of the system bus read accesses is always used.

Arbitration starts as soon as two or more masters place information on the bus at the same time, and stops (arbitration is lost) for the master that intends to send a logical one while the other master sends a logical zero.

As soon as arbitration is lost by a master, it stops sending data and listens to the bus in order to detect a stop. When the stop is detected, the master that has lost arbitration may put its data on the bus by respecting arbitration.

Arbitration is illustrated in Arbitration Cases.

### 43.6.4.2 Different Multimaster Modes

Two Multimaster modes may be distinguished:

- 1. The TWIHS is considered as a master only and is never addressed.

- 2. The TWIHS may be either a master or a slave and may be addressed.

Note: Arbitration in supported in both Multimaster modes.

#### 43.6.4.2.1 TWIHS as Master Only

In this mode, the TWIHS is considered as a master only (MSEN is always at one) and must be driven like a master with the ARBLST (Arbitration Lost) flag in addition.

If arbitration is lost (ARBLST = 1), the user must reinitiate the data transfer.

If starting a transfer (ex.: DADR + START + W + Write in THR) and if the bus is busy, the TWIHS automatically waits for a STOP condition on the bus to initiate the transfer (see User Sends Data While the Bus is Busy).

**Note:** The state of the bus (busy or free) is not indicated in the user interface.

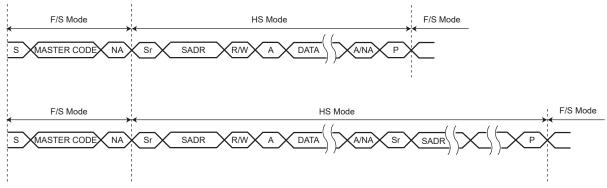

### 43.6.4.2.2 TWIHS as Master or Slave

The automatic reversal from master to slave is not supported in case of a lost arbitration.

Then, in the case where TWIHS may be either a master or a slave, the user must manage the pseudo Multimaster mode described in the steps below:

- 1. Program the TWIHS in Slave mode (SADR + MSDIS + SVEN) and perform a slave access (if TWIHS is addressed).

- 2. If the TWIHS has to be set in Master mode, wait until TXCOMP flag is at 1.

- 3. Program the Master mode (DADR + SVDIS + MSEN) and start the transfer (ex: START + Write in THR).

- 4. As soon as the Master mode is enabled, the TWIHS scans the bus in order to detect if it is busy or free. When the bus is considered free, the TWIHS initiates the transfer.

- 5. As soon as the transfer is initiated and until a STOP condition is sent, the arbitration becomes relevant and the user must monitor the ARBLST flag.

- 6. If the arbitration is lost (ARBLST is set to 1), the user must program the TWIHS in Slave mode in case the master that won the arbitration needs to access the TWIHS.

- 7. If the TWIHS has to be set in Slave mode, wait until the TXCOMP flag is at 1 and then program the Slave mode.

**Note:** If the arbitration is lost and the TWIHS is addressed, the TWIHS does not acknowledge, even if it is programmed in Slave mode as soon as ARBLST is set to 1. Then the master must repeat SADR.

# Two-wire Interface (TWIHS)

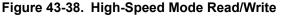

# 43.6.5.7 High-Speed Slave Mode

High-speed mode is enabled when a one is written to TWIHS\_CR.HSEN. Furthermore, the analog pad filter must be enabled, a one must be written to TWIHS\_FILTR.PADFEN and the FILT bit must be cleared. TWIHS High-speed mode operation is similar to TWIHS operation with the following exceptions:

- 1. A master code is received first at normal speed before entering High-speed mode period.

- 2. When TWIHS High-speed mode is active, clock stretching is only allowed after acknowledge (ACK), not-acknowledge (NACK), START (S) or REPEATED START (Sr) (as consequence OVF may happen).

TWIHS High-speed mode allows transfers of up to 3.4 Mbit/s.

The TWIHS slave in High-speed mode requires that slave clock stretching is disabled (SCLWSDIS bit at '1'). The peripheral clock must run at a minimum of 11 MHz (assuming the system has no latency).

**Note:** When slave clock stretching is disabled, the TWIHS\_RHR must always be read before receiving the next data (MASTER write frame). It is strongly recommended to use either the polling method on the RXRDY flag in TWIHS\_SR, or the DMA. If the receive is managed by an interrupt, the TWIHS interrupt priority must be set to the right level and its latency minimized to avoid receive overrun.

**Note:** When slave clock stretching is disabled, the TWIHS\_THR must be filled with the first data to send before the beginning of the frame (MASTER read frame). It is strongly recommended to use either the polling method on the TXRDY flag in TWIHS\_SR, or the DMA. If the transmit is managed by an interrupt, the TWIHS interrupt priority must be set to the right level and its latency minimized to avoid transmit underrun.

#### 43.6.5.7.1 Read/Write Operation

A TWIHS high-speed frame always begins with the following sequence:

- 1. START condition (S)

- 2. Master Code (0000 1XXX)

- 3. Not-acknowledge (NACK)

When the TWIHS is programmed in Slave mode and TWIHS High-speed mode is activated, master code matching is activated and internal timings are set to match the TWIHS High-speed mode requirements.

#### 43.6.5.7.2 Usage

TWIHS High-speed mode usage is the same as the standard TWIHS (See Read/Write Flowcharts).

# **Two-wire Interface (TWIHS)**

Universal Synchronous Asynchronous Receiver Transc...

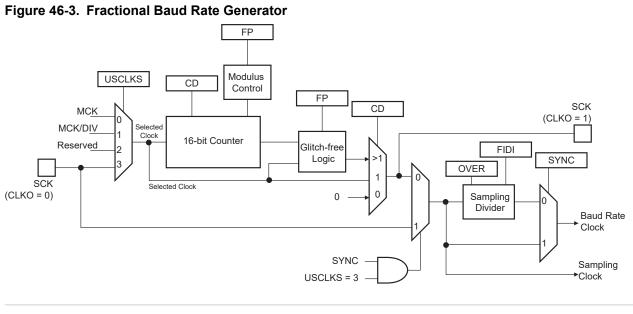

▲ WARNING When the value of US\_BRGR.FP is greater than '0', the SCK (oversampling clock) generates non-constant duty cycles. The SCK high duration is increased by "selected clock" period from time to time. The duty cycle depends on the value of USART\_BRGR.CD.

# 46.6.1.3 Baud Rate in Synchronous Mode or SPI Mode

If the USART is programmed to operate in Synchronous mode, the selected clock is divided by the value of US\_BRGR.CD.

Baud Rate =  $\frac{\text{Selected Clock}}{\text{CD}}$

In Synchronous mode, if the external clock is selected (USCLKS = 3), the clock is provided directly by the signal on the USART SCK pin. No division is active. The value written in US\_BRGR has no effect. The external clock frequency must be at least 3 times lower than the system clock. In Master mode, Synchronous mode (USCLKS = 0 or 1, CLKO set to 1), the receive part limits the SCK maximum frequency to Selected Clock/3 in USART mode, or Selected Clock/6 in SPI mode.

When either the external clock SCK or the internal clock divided (peripheral clock/DIV) is selected, the value of CD must be even if the user has to ensure a 50:50 mark/space ratio on the SCK pin. When the peripheral clock is selected, the baud rate generator ensures a 50:50 duty cycle on the SCK pin, even if the value of CD is odd.

# 46.6.1.4 Baud Rate in ISO 7816 Mode

The ISO7816 specification defines the bit rate with the following formula:

$$B = \frac{\mathrm{Di}}{\mathrm{Fi}} \times f$$

where:

- B is the bit rate

- Di is the bit-rate adjustment factor

- Fi is the clock frequency division factor

- f is the ISO7816 clock frequency (Hz)

# Media Local Bus (MLB)

- 4. Program the CAT for the inbound DMA

- 4.1. For Tx channels (to MediaLB) HBI is the inbound DMA

- 4.2. For Rx channels (from MediaLB) MediaLB is the inbound DMA

- 4.3. Set the channel direction: RNW = 0

- 4.4. Set the channel type: CT[2:0] = 010 (asynchronous), 001 (control), 011 (isochronous), or 000 (synchronous)

- 4.5. Set the connection label: CL[5:0] = N

- 4.6. If CT[2:0] = 000 (synchronous), set the mute bit (MT = 1)

- 4.7. Set the channel enable: CE = 1

- 4.8. Set all other bits of the CAT to '0'

- 5. Program the CAT for the outbound DMA

- 5.1. For Tx channels (to MediaLB) MediaLB is the outbound DMA

- 5.2. For Rx channels (from MediaLB) HBI is the outbound DMA

- 5.3. Set the channel direction: RNW = 1

- 5.4. Set the channel type: CT[2:0] = 010 (asynchronous), 001 (control), 011 (isochronous), or 000 (synchronous)

- 5.5. Set the channel label: CL[5:0] = N

- 5.6. If CT[2:0] = 000 (synchronous), set the mute bit (MT = 1)

- 5.7. Set the channel enable: CE = 1

- 5.8. Set all other bits of the CAT to '0'

- 6. Repeat steps 2–5 to initialize all logical channels

# Program the AHB Block DMAs

The ADT resides in the external CTR and is programmed indirectly via APB reads and writes to the MIF.

- 1. Initialize all bits of the ADT to '0'

- 2. Select a logical channel: N = 0-63

- 3. Program the AHB block ping page for channel N

- 3.1. Set the 32-bit base address (BA1)

- 3.2. Set the 11-bit buffer depth (BD1): BD1 = buffer depth in bytes 1

- 3.2.1. For synchronous channels: (BD1 + 1) = n x frames per sub-buffer (m) x bytesper-frame (bpf)

- 3.2.2. For isochronous channels: (BD1 + 1) mod (BS + 1) = 0

- 3.2.3. For asynchronous channels:  $5 \le (BD1 + 1) \le 4096$  (max packet length)

- 3.2.4. For control channels:  $5 \le (BD1 + 1) \le 4096$  (max packet length)

- 3.3. For asynchronous and control Tx channels set the packet start bit (PS1) iff the page contains the start of the packet

- 3.4. Clear the page done bit (DNE1)

- 3.5. Clear the error bit (ERR1)

- 3.6. Set the page ready bit (RDY1)

- 4. Program the AHB block pong page for channel N

- 4.1. Set the 32-bit base address (BA2)

- 4.2. Set the 11-bit buffer depth (BD2): BD2 = buffer depth in bytes 1

- 4.2.1. For synchronous channels: (BD2 +1) = n x frames per sub-buffer (m) x bytesper-frame (bpf)

# **Controller Area Network (MCAN)**

| Filter<br>Element | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |  |  |  |  |

|-------------------|----------------------------|----------------------------|--------------------------|--|--|--|--|

| 0                 | ID debug message A         | 1                          | 11 1101                  |  |  |  |  |

| 1                 | ID debug message B         | 2                          | 11 1110                  |  |  |  |  |

| 2                 | ID debug message C         | 3                          | 11 1111                  |  |  |  |  |

#### 49.5.4.4.2 Debug Message Handling

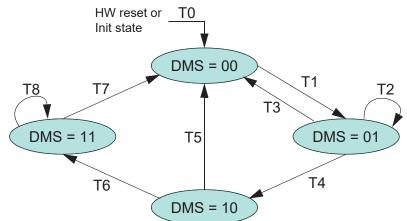

The debug message handling state machine ensures that debug messages are stored to three consecutive Rx Buffers in the correct order. If some messages are missing, the process is restarted. The DMA request is activated only when all three debug messages A, B, C have been received in the correct order.

The status of the debug message handling state machine is signalled via MCAN\_RXF1S.DMS.

# Figure 49-9. Debug Message Handling State Machine

Table 49-4 Example Filter Configuration for Debug Messages

T0: reset m\_can\_dma\_req output, enable reception of debug messages A, B, and C

- T1: reception of debug message A

- T2: reception of debug message A

- T3: reception of debug message C

- T4: reception of debug message B

- T5: reception of debug messages A, B

- T6: reception of debug message C

- T7: DMA transfer completed

- T8: reception of debug message A,B,C (message rejected)

# 49.5.5 Tx Handling

The Tx Handler handles transmission requests for the dedicated Tx Buffers, the Tx FIFO, and the Tx Queue. It controls the transfer of transmit messages to the CAN Core, the Put and Get Indices, and the Tx Event FIFO. Up to 32 Tx Buffers can be set up for message transmission. The CAN mode for transmission (Classic CAN or CAN FD) can be configured separately for each Tx Buffer element. The Tx

# Controller Area Network (MCAN)

#### 49.6.6 MCAN RAM Watchdog Register

| Name:     | MCAN_RWD   |

|-----------|------------|

| Offset:   | 0x14       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

The RAM Watchdog monitors the Message RAM response time. A Message RAM access via the MCAN's Generic Master Interface starts the Message RAM Watchdog Counter with the value configured by MCAN\_RWD.WDC. The counter is reloaded with MCAN\_RWD.WDC when the Message RAM signals successful completion by activating its READY output. In case there is no response from the Message RAM until the counter has counted down to zero, the counter stops and interrupt flag MCAN\_IR.WDI is set. The RAM Watchdog Counter is clocked by the system bus clock (peripheral clock).

| Bit    | 31       | 30  | 29  | 28  | 27     | 26  | 25  | 24  |

|--------|----------|-----|-----|-----|--------|-----|-----|-----|

|        |          |     |     |     |        |     |     |     |

| Access |          |     |     |     |        |     |     |     |

| Reset  |          |     |     |     |        |     |     |     |

|        |          |     |     |     |        |     |     |     |

| Bit    | 23       | 22  | 21  | 20  | 19     | 18  | 17  | 16  |

|        |          |     |     |     |        |     |     |     |

| Access |          |     |     |     |        | -   |     |     |

| Reset  |          |     |     |     |        |     |     |     |

|        |          |     |     |     |        |     |     |     |

| Bit    | 15       | 14  | 13  | 12  | 11     | 10  | 9   | 8   |

|        |          |     |     | WDV | /[7:0] |     |     |     |

| Access | R        | R   | R   | R   | R      | R   | R   | R   |

| Reset  | 0        | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |          |     |     |     |        |     |     |     |

| Bit    | 7        | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|        | WDC[7:0] |     |     |     |        |     |     |     |

| Access | R/W      | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0        | 0   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |          |     |     |     |        |     |     |     |

Bits 15:8 – WDV[7:0] Watchdog Value (read-only)

Watchdog Counter Value for the current message located in RAM.

Bits 7:0 – WDC[7:0] Watchdog Configuration (read/write)

Start value of the Message RAM Watchdog Counter. The counter is disabled when WDC is cleared.

# Controller Area Network (MCAN)

#### 49.6.40 MCAN Transmit Buffer Cancellation Request

|        | Name:<br>Offset:<br>Reset:<br>Property: | MCAN_TXBCF<br>0xD4<br>0x00000000<br>Read/Write | 3    |      |      |      |      |      |

|--------|-----------------------------------------|------------------------------------------------|------|------|------|------|------|------|

| Bit    | 31                                      | 30                                             | 29   | 28   | 27   | 26   | 25   | 24   |

|        | CR31                                    | CR30                                           | CR29 | CR28 | CR27 | CR26 | CR25 | CR24 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 23                                      | 22                                             | 21   | 20   | 19   | 18   | 17   | 16   |

|        | CR23                                    | CR22                                           | CR21 | CR20 | CR19 | CR18 | CR17 | CR16 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 15                                      | 14                                             | 13   | 12   | 11   | 10   | 9    | 8    |

|        | CR15                                    | CR14                                           | CR13 | CR12 | CR11 | CR10 | CR9  | CR8  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 7                                       | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |

|        | CR7                                     | CR6                                            | CR5  | CR4  | CR3  | CR2  | CR1  | CR0  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – CRx Cancellation Request for Transmit Buffer x

Each Transmit Buffer has its own Cancellation Request bit. Writing a '1' will set the corresponding Cancellation Request bit; writing a '0' has no impact. This enables the processor to set cancellation requests for multiple Transmit Buffers with one write to MCAN\_TXBCR. MCAN\_TXBCR bits are set only for those Transmit Buffers configured via TXBC. The bits remain set until the corresponding bit of MCAN\_TXBRP is reset.

| Valu | e Description            |  |

|------|--------------------------|--|

| 0    | No cancellation pending. |  |

| 1    | Cancellation pending.    |  |

# Pulse Width Modulation Controller (PWM)

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | Leading-edge blanking is disabled on PWMLx output falling edge. |

| 1     | Leading-edge blanking is enabled on PWMLx output falling edge.  |

# Bits 6:0 – LEBDELAY[6:0] Leading-Edge Blanking Delay for TRGINx

Leading-edge blanking duration for external trigger x input. The delay is calculated according to the following formula:

$LEBDELAY = (f_{peripheral clock} \times Delay) + 1$

# Electrical Characteristics for SAM ...

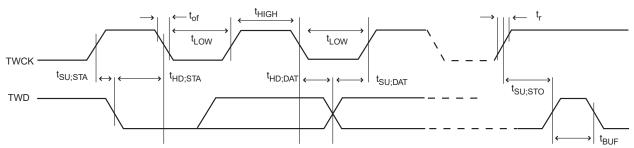

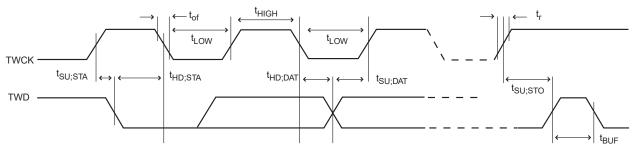

### Figure 58-29. Two-wire Serial Bus Timing

## 58.13.1.13 GMAC Characteristics

## 58.13.1.13.1 Timing Conditions

## Table 58-69. Load Capacitance on Data, Clock Pads

| Supply | CL    |      |  |

|--------|-------|------|--|

|        | Max   | Min  |  |

| 3.3V   | 20 pF | 0 pF |  |

# 58.13.1.13.2 Timing Constraints

The GMAC must be constrained so as to satisfy the timings of standards shown below and in 58.13.1.13.3 MII Mode, in MAX corner.

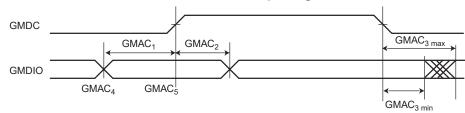

## Table 58-70. GMAC Signals Relative to GMDC

| Symbol            | Parameter                        | Min  | Max               | Unit |

|-------------------|----------------------------------|------|-------------------|------|

| GMAC <sub>1</sub> | Setup for GMDIO from GMDC rising | 10   | -                 | ns   |

| GMAC <sub>2</sub> | Hold for GMDIO from GMDC rising  | 10   | -                 |      |

| GMAC <sub>3</sub> | GMDIO toggling from GMDC falling | 0(1) | 10 <sup>(1)</sup> |      |

Note: 1. For GMAC output signals, min and max access time are defined. The min access time is the time between the GMDC falling edge and the signal change. The max access timing is the time between the GMDC falling edge and the signal stabilizes. The figure below illustrates min and max accesses for GMAC<sub>3</sub>.

#### Figure 58-30. Min and Max Access Time of GMAC Output Signals

# **Electrical Characteristics for SAM E70/S70**

## 5. $t_{CPMCK}$ = MCK bus period

Figure 59-29. Two-wire Serial Bus Timing

## 59.13.1.13 GMAC Characteristics

#### 59.13.1.13.1 Timing Conditions

## Table 59-69. Load Capacitance on Data, Clock Pads

| Supply | CL    |      |  |

|--------|-------|------|--|

|        | Max   | Min  |  |

| 3.3V   | 20 pF | 0 pF |  |

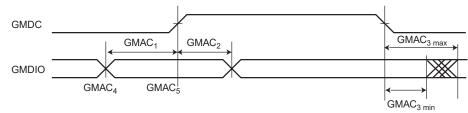

## 59.13.1.13.2 Timing Constraints

The GMAC must be constrained so as to satisfy the timings of standards shown below and in 58.13.1.13.3 MII Mode, in MAX corner.

#### Table 59-70. GMAC Signals Relative to GMDC

| Symbol            | Parameter                        | Min              | Мах               | Unit |

|-------------------|----------------------------------|------------------|-------------------|------|

| GMAC <sub>1</sub> | Setup for GMDIO from GMDC rising | 10               | _                 | ns   |

| GMAC <sub>2</sub> | Hold for GMDIO from GMDC rising  | 10               | _                 |      |

| GMAC <sub>3</sub> | GMDIO toggling from GMDC falling | 0 <sup>(1)</sup> | 10 <sup>(1)</sup> |      |

Note: 1. For GMAC output signals, min and max access time are defined. The min access time is the time between the GMDC falling edge and the signal change. The max access timing is the time between the GMDC falling edge and the signal stabilizes. The figure below illustrates min and max accesses for GMAC<sub>3</sub>.

## Figure 59-30. Min and Max Access Time of GMAC Output Signals

# **Schematic Checklist**

| Signal<br>Name | Recommended Pin<br>Connection | Description                                                                                          |

|----------------|-------------------------------|------------------------------------------------------------------------------------------------------|

| PCx<br>PDx     |                               | Refer to the column "Reset State" of the pin description tables in the section "Package and Pinout". |

| PEx            |                               | Schmitt trigger on all inputs.<br>To reduce power consumption if not used, the concerned PIO         |

|                |                               | can be configured as an output, driven at '0' with internal pullup disabled.                         |

# **Related Links**

6. Package and Pinout

# 60.2.6 Parallel Capture Mode

| Signal Name | Recommended Pin Connection                  | Description                                                                                    |

|-------------|---------------------------------------------|------------------------------------------------------------------------------------------------|

| PIODC0-7    | Application dependent.<br>(Pullup at VDDIO) | Parallel mode capture data<br>All are pulled-up inputs (100 kOhm) to VDDIO at<br>reset.        |

| PIODCCLK    | Application dependent.<br>(Pullup at VDDIO) | Parallel mode capture clock<br>Pulled-up input (100 kOhm) to VDDIO at reset.                   |

| PIODCEN1-2  | Application dependent.<br>(Pullup at VDDIO) | Parallel mode capture mode enable<br>All are pulled-up inputs (100 kOhm) to VDDIO at<br>reset. |

# 60.2.7 Analog Reference, Analog Front-End and DAC

| Signal Name            | Recommended Pin<br>Connection           | Description                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Analog Voltage Refere  | nces                                    |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VREFP                  | 1.7V to VDDIN<br>LC Filter is required. | <ul> <li>Positive reference voltage.</li> <li>VREFP is a pure analog input.</li> <li>VREFP is the voltage reference for the AFEC (ADC, PGA DAC and Analog Comparator).</li> <li>To reduce power consumption, if analog features are not used, connect VREFP to GND.</li> <li>Noise must be lower than 100 μVrms</li> </ul> |  |  |  |  |

| VREFN                  | Analog Negative Reference               | AFE, DAC and Analog Comparator negative<br>reference<br>VREFN must be connected to GND or GNDANA.                                                                                                                                                                                                                          |  |  |  |  |

| 12-bit Analog Front-En | 12-bit Analog Front-End                 |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |