#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 300MHz                                                                                    |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                              |

| Number of I/O              | 75                                                                                        |

| Program Memory Size        | 2MB (2M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                |                                                                                           |

| RAM Size                   | 384K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-TFBGA                                                                                 |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70n21a-cn                 |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 23.5.6 Supply Controller Status Register

| Name:     | SUPC_SR    |

|-----------|------------|

| Offset:   | 0x14       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

**Note:** Because of the asynchronism between the Slow Clock (SLCK) and the System Clock (MCK), the status register flag reset is taken into account only 2 slow clock cycles after the read of the SUPC\_SR.

| Bit    | 31     | 30      | 29      | 28     | 27       | 26      | 25    | 24 |

|--------|--------|---------|---------|--------|----------|---------|-------|----|

|        |        |         |         |        | WKUPI    | S[13:8] |       |    |

| Access |        |         | R       | R      | R        | R       | R     | R  |

| Reset  |        |         | 0       | 0      | 0        | 0       | 0     | 0  |

|        |        |         |         |        |          |         |       |    |

| Bit    | 23     | 22      | 21      | 20     | 19       | 18      | 17    | 16 |

|        |        |         |         | WKUP   | PIS[7:0] |         |       |    |

| Access | R      | R       | R       | R      | R        | R       | R     | R  |

| Reset  | 0      | 0       | 0       | 0      | 0        | 0       | 0     | 0  |

|        |        |         |         |        |          |         |       |    |

| Bit    | 15     | 14      | 13      | 12     | 11       | 10      | 9     | 8  |

|        |        | LPDBCS1 | LPDBCS0 |        |          |         |       |    |

| Access |        | R       | R       |        |          |         |       |    |

| Reset  |        | 0       | 0       |        |          |         |       |    |

|        |        |         |         |        |          |         |       |    |

| Bit    | 7      | 6       | 5       | 4      | 3        | 2       | 1     | 0  |

|        | OSCSEL | SMOS    | SMS     | SMRSTS | BODRSTS  | SMWS    | WKUPS |    |

| Access | R      | R       | R       | R      | R        | R       | R     |    |

| Reset  | 0      | 0       | 0       | 0      | 0        | 0       | 0     |    |

|        |        |         |         |        |          |         |       |    |

This register is located in the VDDIO domain.

Bits 29:16 – WKUPIS[13:0] WKUPx ('x' = 0-13) Input Status (cleared on read)

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | (DIS): The corresponding wakeup input is disabled, or was inactive at the time the    |

|       | debouncer triggered a wakeup event.                                                   |

| 1     | (EN): The corresponding wakeup input was active at the time the debouncer triggered a |

|       | wakeup event since the last read of SUPC_SR.                                          |

#### Bit 14 – LPDBCS1 Low-power Debouncer Wakeup Status on WKUP1 (cleared on read)

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | (NO): No wakeup due to the assertion of the WKUP1 pin has occurred since the last read of |

|       | SUPC_SR.                                                                                  |

| 1     | (PRESENT): At least one wakeup due to the assertion of the WKUP1 pin has occurred since   |

|       | the last read of SUPC_SR.                                                                 |

Bit 13 – LPDBCS0 Low-power Debouncer Wakeup Status on WKUP0 (cleared on read)

## **Power Management Controller (PMC)**

### 31.20.17 PMC Interrupt Mask Register

| Name:     | PMC_IMR    |

|-----------|------------|

| Offset:   | 0x006C     |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

| Bit    | 31 | 30      | 29       | 28      | 27      | 26      | 25      | 24       |

|--------|----|---------|----------|---------|---------|---------|---------|----------|

|        |    |         |          |         |         |         |         |          |

| Access |    |         |          |         |         |         |         |          |

| Reset  |    |         |          |         |         |         |         |          |

|        |    |         |          |         |         |         |         |          |

| Bit    | 23 | 22      | 21       | 20      | 19      | 18      | 17      | 16       |

|        |    |         | XT32KERR |         |         | CFDEV   | MOSCRCS | MOSCSELS |

| Access |    |         |          |         |         |         |         |          |

| Reset  |    |         | 0        |         |         | 0       | 0       | 0        |

|        |    |         |          |         |         |         |         |          |

| Bit    | 15 | 14      | 13       | 12      | 11      | 10      | 9       | 8        |

|        |    | PCKRDY6 | PCKRDY5  | PCKRDY4 | PCKRDY3 | PCKRDY2 | PCKRDY1 | PCKRDY0  |

| Access |    |         |          |         |         |         |         |          |

| Reset  |    | 0       | 0        | 0       | 0       | 0       | 0       | 0        |

|        |    |         |          |         |         |         |         |          |

| Bit    | 7  | 6       | 5        | 4       | 3       | 2       | 1       | 0        |

|        |    | LOCKU   |          |         | MCKRDY  |         | LOCKA   | MOSCXTS  |

| Access |    |         |          |         |         |         |         |          |

| Reset  |    | 0       |          |         | 0       |         | 0       | 0        |

Bit 21 – XT32KERR 32.768 kHz Crystal Oscillator Error Interrupt Mask

- Bit 18 CFDEV Clock Failure Detector Event Interrupt Mask

- Bit 17 MOSCRCS Main RC Status Interrupt Mask

- Bit 16 MOSCSELS Main Clock Source Oscillator Selection Status Interrupt Mask

Bits 8, 9, 10, 11, 12, 13, 14 – PCKRDY Programmable Clock Ready x Interrupt Mask

- Bit 6 LOCKU UTMI PLL Lock Interrupt Mask

- **Bit 3 MCKRDY** Master Clock Ready Interrupt Mask

- Bit 1 LOCKA PLLA Lock Interrupt Mask

- **Bit 0 MOSCXTS** Main Crystal Oscillator Status Interrupt Mask

## Parallel Input/Output Controller (PIO)

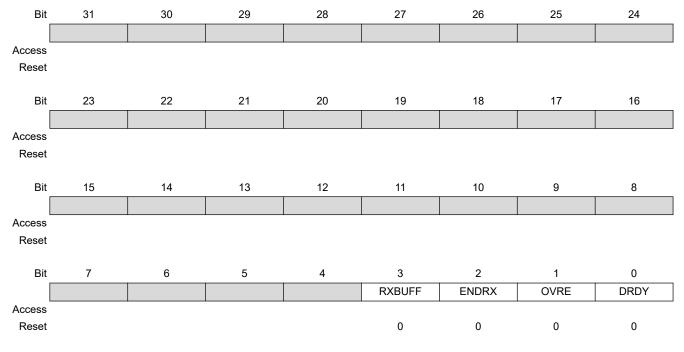

### 32.6.1.53 PIO Parallel Capture Interrupt Mask Register

| Name:     | PIO_PCIMR  |

|-----------|------------|

| Offset:   | 0x015C     |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

The following configuration values are valid for all listed bit names of this register:

- 0: Corresponding interrupt is not enabled.

- 1: Corresponding interrupt is enabled.

Bit 3 - RXBUFF Reception Buffer Full Interrupt Mask

- **Bit 2 ENDRX** End of Reception Transfer Interrupt Mask

- Bit 1 OVRE Parallel Capture Mode Overrun Error Interrupt Mask

- Bit 0 DRDY Parallel Capture Mode Data Ready Interrupt Mask

# SDRAM Controller (SDRAMC)

| Offset | Name              | Bit Pos. |             |            |  |      |         |  |  |        |

|--------|-------------------|----------|-------------|------------|--|------|---------|--|--|--------|

|        |                   | 7:0      |             |            |  |      |         |  |  | SDR_SE |

| 0x2C   | SDRAMC_OCMS       | 15:8     |             |            |  |      |         |  |  |        |

| 0,20   | SDRAIVIC_OCIVIS   | 23:16    |             |            |  |      |         |  |  |        |

|        |                   | 31:24    |             |            |  |      |         |  |  |        |

|        |                   | 7:0      |             | KEY1[7:0]  |  |      |         |  |  |        |

| 0x30   | SDRAMC_OCMS_K     | 15:8     |             | KEY1[15:8] |  |      |         |  |  |        |

| 0x30   | EY1               | 23:16    | KEY1[23:16] |            |  |      |         |  |  |        |

|        |                   | 31:24    |             |            |  | KEY1 | [31:24] |  |  |        |

|        |                   | 7:0      |             | KEY2[7:0]  |  |      |         |  |  |        |

| 0x34   | SDRAMC_OCMS_K     | 15:8     | KEY2[15:8]  |            |  |      |         |  |  |        |

| 0x34   | EY2               | 23:16    |             |            |  | KEY2 | [23:16] |  |  |        |

|        | 31:24 KEY2[31:24] |          |             |            |  |      |         |  |  |        |

## Static Memory Controller (SMC)

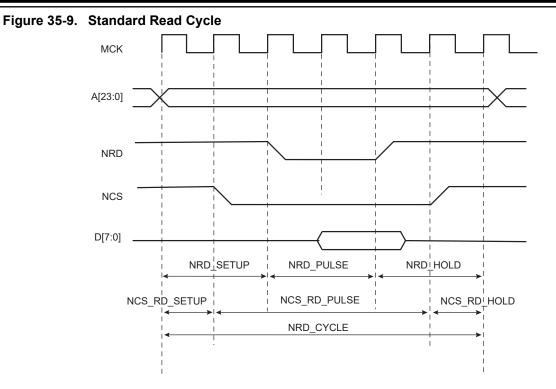

## 35.9.1.1 NRD Waveform

The NRD signal is characterized by a setup timing, a pulse width and a hold timing.

- nrd\_setup— NRD setup time is defined as the setup of address before the NRD falling edge;

- nrd\_pulse—NRD pulse length is the time between NRD falling edge and NRD rising edge;

- nrd\_hold—NRD hold time is defined as the hold time of address after the NRD rising edge.

## 35.9.1.2 NCS Waveform

The NCS signal can be divided into a setup time, pulse length and hold time:

- ncs\_rd\_setup—NCS setup time is defined as the setup time of address before the NCS falling edge.

- ncs\_rd\_pulse—NCS pulse length is the time between NCS falling edge and NCS rising edge;

- ncs\_rd\_hold—NCS hold time is defined as the hold time of address after the NCS rising edge.

## 35.9.1.3 Read Cycle

The NRD\_CYCLE time is defined as the total duration of the read cycle, i.e., from the time where address is set on the address bus to the point where address may change. The total read cycle time is defined as:

NRD\_CYCLE = NRD\_SETUP + NRD\_PULSE + NRD\_HOLD,

as well as

NRD\_CYCLE = NCS\_RD\_SETUP + NCS\_RD\_PULSE + NCS\_RD\_HOLD

All NRD and NCS timings are defined separately for each chip select as an integer number of Master Clock cycles. The NRD\_CYCLE field is common to both the NRD and NCS signals, thus the timing period is of the same duration.

NRD\_CYCLE, NRD\_SETUP, and NRD\_PULSE implicitly define the NRD\_HOLD value as:

NRD\_HOLD = NRD\_CYCLE - NRD SETUP - NRD PULSE

# **GMAC** - Ethernet MAC

| Offset | Name        | Bit Pos. |             |              |  |  |  |  |  |  |

|--------|-------------|----------|-------------|--------------|--|--|--|--|--|--|

|        |             | 23:16    | NFRX[23:16] |              |  |  |  |  |  |  |

|        |             | 31:24    | NFRX[31:24] |              |  |  |  |  |  |  |

|        |             | 7:0      | NFRX[7:0]   |              |  |  |  |  |  |  |

| 00400  |             | 15:8     | NFRX[15:8]  |              |  |  |  |  |  |  |

| 0x0180 | GMAC_TMXBFR | 23:16    | NFRX[23:16] |              |  |  |  |  |  |  |

|        |             | 31:24    | NFRX[31:24] |              |  |  |  |  |  |  |

|        |             | 7:0      | UFRX[7:0]   |              |  |  |  |  |  |  |

| 0x0184 | GMAC_UFR    | 15:8     |             | UFRX[9:8]    |  |  |  |  |  |  |

| 0X0104 | GWAC_OFK    | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | OFRX[7:0]   |              |  |  |  |  |  |  |

| 0x0188 | GMAC_OFR    | 15:8     |             | OFRX[9:8]    |  |  |  |  |  |  |

| 080100 | GWAC_OFK    | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | JRX[7:0]    |              |  |  |  |  |  |  |

| 0x018C | GMAC_JR     | 15:8     |             | JRX[9:8]     |  |  |  |  |  |  |

| 0.0100 | GINAC_JIC   | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | FCKR[7:0]   |              |  |  |  |  |  |  |

| 0x0190 | GMAC_FCSE   | 15:8     |             | FCKR[9:8]    |  |  |  |  |  |  |

| 0,0190 | GWAC_I COL  | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | LFER[7:0]   |              |  |  |  |  |  |  |

| 0x0194 | GMAC_LFFE   | 15:8     |             | LFER[9:8]    |  |  |  |  |  |  |

| 070134 |             | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | RXSE[7:0]   |              |  |  |  |  |  |  |

| 0x0198 | GMAC_RSE    | 15:8     |             | RXSE[9:8]    |  |  |  |  |  |  |

| 0.0130 |             | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | AER[7:0]    |              |  |  |  |  |  |  |

| 0x019C | GMAC_AE     | 15:8     |             | AER[9:8]     |  |  |  |  |  |  |

| 0,0100 |             | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | RXRER[7:0]  |              |  |  |  |  |  |  |

| 0x01A0 | GMAC_RRE    | 15:8     | RXRER[15:8] |              |  |  |  |  |  |  |

| UXUTAU |             | 23:16    |             | RXRER[17:16] |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | RXOVR[7:0]  |              |  |  |  |  |  |  |

| 0x01A4 | GMAC_ROE    | 15:8     |             | RXOVR[9:8]   |  |  |  |  |  |  |

|        |             | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|        |             | 7:0      | HCKER[7:0]  |              |  |  |  |  |  |  |

| 0x01A8 | GMAC_IHCE   | 15:8     |             |              |  |  |  |  |  |  |

|        |             | 23:16    |             |              |  |  |  |  |  |  |

|        |             | 31:24    |             |              |  |  |  |  |  |  |

|                 | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_CSE<br>0x14C<br>0x00000000<br>Read-only |    |    |       |    |    |    |

|-----------------|-----------------------------------------|----------------------------------------------|----|----|-------|----|----|----|

| Bit             | 31                                      | 30                                           | 29 | 28 | 27    | 26 | 25 | 24 |

| Access<br>Reset |                                         |                                              |    |    |       |    |    |    |

| Bit             | 23                                      | 22                                           | 21 | 20 | 19    | 18 | 17 | 16 |

| Access<br>Reset |                                         |                                              |    |    |       |    |    |    |

| Bit             | 15                                      | 14                                           | 13 | 12 | 11    | 10 | 9  | 8  |

| Access          |                                         |                                              |    |    |       |    | R  | R  |

| Reset           |                                         |                                              |    |    |       |    | 0  | 0  |

| Bit             | 7                                       | 6                                            | 5  | 4  | 3     | 2  | 1  | 0  |

| _               |                                         |                                              |    |    | [7:0] |    |    |    |

| Access          | R                                       | R                                            | R  | R  | R     | R  | R  | R  |

| Reset           | 0                                       | 0                                            | 0  | 0  | 0     | 0  | 0  | 0  |

### 38.8.57 GMAC Carrier Sense Errors Register

## Bits 9:0 - CSR[9:0] Carrier Sense Error

This register counts the number of frames transmitted with carrier sense was not seen during transmission or where carrier sense was de-asserted after being asserted in a transmit frame without collision (no underrun). Only incremented in half duplex mode. The only effect of a carrier sense error is to increment this register. The behavior of the other statistics registers is unaffected by the detection of a carrier sense error.

1: Set when the current bank is ready to accept a new IN packet. This triggers a PEP\_x interrupt if TXINE = 1.

For IN endpoints:

0: Cleared when TXINIC = 1. This acknowledges the interrupt, which has no effect on the endpoint FIFO. USBHS\_DEVEPTISRx.TXINI shall always be cleared before clearing USBHS\_DEVEPTIMRx.FIFOCON.

1: Set at the same time as USBHS\_DEVEPTIMRx.FIFOCON when the current bank is free. This triggers a PEP\_x interrupt if TXINE = 1.

The user writes into the FIFO and clears the USBHS\_DEVEPTIMRx.FIFOCON bit to allow the USBHS to send the data. If the IN endpoint is composed of multiple banks, this also switches to the next bank. The USBHS\_DEVEPTISRx.TXINI and USBHS\_DEVEPTIMRx.FIFOCON bits are set/cleared in accordance with the status of the next bank.

This bit is inactive (cleared) for OUT endpoints.

## **USB High-Speed Interface (USBHS)**

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.OVERFIEC = 1. This disables the Transmitted IN Data |

|       | interrupt (USBHS_HSTPIPIMR.OVERFIE).                                             |

| 1     | Set when USBHS_HSTPIPIER.OVERFIES = 1. This enables the Transmitted IN Data      |

|       | interrupt (USBHS_HSTPIPIMR.OVERFIE).                                             |

## Bit 4 – NAKEDE NAKed Interrupt Enable

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.NAKEDEC = 1. This disables the Transmitted IN Data |

|       | interrupt (USBHS_HSTPIPIMR.NAKEDE).                                             |

| 1     | Set when USBHS_HSTPIPIER.NAKEDES = 1. This enables the Transmitted IN Data      |

|       | interrupt (USBHS_HSTPIPIMR.NAKEDE).                                             |

## Bit 3 – PERRE Pipe Error Interrupt Enable

| Value | Description                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.PERREC = 1. This disables the Transmitted IN Data                               |

|       | interrupt (USBHS_HSTPIPIMR.PERRE).                                                                           |

| 1     | Set when USBHS_HSTPIPIER.PERRES = 1. This enables the Transmitted IN Data interrupt (USBHS_HSTPIPIMR.PERRE). |

## Bit 2 – TXSTPE Transmitted SETUP Interrupt Enable

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.TXSTPEC = 1. This disables the Transmitted IN Data |

|       | interrupt (USBHS_HSTPIPIMR.TXSTPE).                                             |

| 1     | Set when USBHS_HSTPIPIER.TXSTPES = 1. This enables the Transmitted IN Data      |

|       | interrupt (USBHS_HSTPIPIMR.TXSTPE).                                             |

## **Bit 1 – TXOUTE** Transmitted OUT Data Interrupt Enable

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.TXOUTEC = 1. This disables the Transmitted IN Data |

|       | interrupt (USBHS_HSTPIPIMR.TXOUTE).                                             |

| 1     | Set when USBHS_HSTPIPIER.TXOUTES = 1. This enables the Transmitted IN Data      |

|       | interrupt (USBHS_HSTPIPIMR.TXOUTE).                                             |

## Bit 0 – RXINE Received IN Data Interrupt Enable

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.RXINEC = 1. This disables the Transmitted IN Data      |

|       | interrupt (USBHS_HSTPIPIMR.RXINE).                                                  |

| 1     | Set when USBHS_HSTPIPIER.RXINES = 1. This enables the Transmitted IN Data interrupt |

|       | (USBHS_HSTPIPIMR.RXINE).                                                            |

## **Quad Serial Peripheral Interface (QSPI)**

## 42.7.7 QSPI Interrupt Disable Register

Name:QSPI\_IDROffset:0x18Reset:-Property:Write-only

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Disables the corresponding interrupt.

| Bit    | 31 | 30 | 29 | 28 | 27    | 26      | 25   | 24   |

|--------|----|----|----|----|-------|---------|------|------|

|        |    |    |    |    |       |         |      |      |

| Access |    |    |    |    |       |         |      |      |

| Reset  |    |    |    |    |       |         |      |      |

|        |    |    |    |    |       |         |      |      |

| Bit    | 23 | 22 | 21 | 20 | 19    | 18      | 17   | 16   |

|        |    |    |    |    |       |         |      |      |

| Access |    |    |    |    |       |         |      |      |

| Reset  |    |    |    |    |       |         |      |      |

| D:4    | 45 |    | 10 | 10 | 44    | 10      | 0    | 0    |

| Bit    | 15 | 14 | 13 | 12 | 11    | 10      | 9    | 8    |

|        |    |    |    |    |       | INSTRE  | CSS  | CSR  |

| Access |    |    |    |    |       | W       | W    | W    |

| Reset  |    |    |    |    |       | -       | _    | _    |

|        |    |    |    |    |       |         |      |      |

| Bit    | 7  | 6  | 5  | 4  | 3     | 2       | 1    | 0    |

|        |    |    |    |    | OVRES | TXEMPTY | TDRE | RDRF |

| Access |    |    |    |    | W     | W       | W    | W    |

| Reset  |    |    |    |    | _     | -       | -    | _    |

Bit 10 – INSTRE Instruction End Interrupt Disable

Bit 9 – CSS Chip Select Status Interrupt Disable

Bit 8 – CSR Chip Select Rise Interrupt Disable

Bit 3 – OVRES Overrun Error Interrupt Disable

Bit 2 – TXEMPTY Transmission Registers Empty Disable

**Bit 1 – TDRE** Transmit Data Register Empty Interrupt Disable

Bit 0 - RDRF Receive Data Register Full Interrupt Disable

## **Quad Serial Peripheral Interface (QSPI)**

## 42.7.13 QSPI Scrambling Mode Register

| Name:     | QSPI_SMR   |

|-----------|------------|

| Offset:   | 0x40       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if bit WPEN is cleared in the QSPI Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28 | 27 | 26          | 25    | 24    |

|--------|----|----|----|----|----|-------------|-------|-------|

|        |    |    |    |    |    |             |       |       |

| Access |    |    |    |    |    |             |       |       |

| Reset  |    |    |    |    |    |             |       |       |

|        |    |    |    |    |    |             |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18          | 17    | 16    |

|        |    |    |    |    |    |             |       |       |

| Access |    |    |    |    |    |             |       |       |

| Reset  |    |    |    |    |    |             |       |       |

|        |    |    |    |    |    |             |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10          | 9     | 8     |

|        |    |    |    |    |    |             |       |       |

| Access |    |    |    |    |    |             |       |       |

| Reset  |    |    |    |    |    |             |       |       |

|        |    |    |    |    |    |             |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2           | 1     | 0     |

|        |    |    |    |    |    |             | RVDIS | SCREN |

| Access |    |    |    |    |    | · · · · · · | R/W   | R/W   |

| Reset  |    |    |    |    |    |             | 0     | 0     |

|        |    |    |    |    |    |             |       |       |

## **Bit 1 – RVDIS** Scrambling/Unscrambling Random Value Disable

| Value | Description                                                                          |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | The scrambling/unscrambling algorithm includes the user scrambling key plus a random |  |  |  |  |  |

|       | value that may differ between devices.                                               |  |  |  |  |  |

| 1     | The scrambling/unscrambling algorithm includes only the user scrambling key.         |  |  |  |  |  |

Bit 0 – SCREN Scrambling/Unscrambling Enable

0 (DISABLED): The scrambling/unscrambling is disabled.

1 (ENABLED): The scrambling/unscrambling is enabled.

Before using the SSC transmitter, the PIO controller must be configured to dedicate the SSC transmitter I/O lines to the SSC Peripheral mode.

## 44.7.2 Power Management

The SSC is not continuously clocked. The SSC interface may be clocked through the Power Management Controller (PMC), therefore the programmer must first configure the PMC to enable the SSC clock.

## 44.7.3 Interrupt

The SSC interface has an interrupt line connected to the interrupt controller. Handling interrupts requires programming the interrupt controller before configuring the SSC.

All SSC interrupts can be enabled/disabled configuring the SSC Interrupt Mask Register. Each pending and unmasked SSC interrupt asserts the SSC interrupt line. The SSC interrupt service routine can get the interrupt origin by reading the SSC Interrupt Status Register.

## 44.8 Functional Description

This section contains the functional description of the following: SSC Functional Block, Clock Management, Data Format, Start, Transmit, Receive and Frame Synchronization.

The receiver and transmitter operate separately. However, they can work synchronously by programming the receiver to use the transmit clock and/or to start a data transfer when transmission starts. Alternatively, this can be done by programming the transmitter to use the receive clock and/or to start a data transfer when reception starts. The transmitter and the receiver can be programmed to operate with the clock signals provided on either the TK or RK pins. This allows the SSC to support many Slave mode data transfers. The maximum clock speed allowed on the TK and RK pins is the peripheral clock divided by 2.

Universal Synchronous Asynchronous Receiver Transc...

## 46.7.37 USART LON Data Length Register

| Name:     | US_LONDL   |  |  |  |

|-----------|------------|--|--|--|

| Offset:   | 0x0068     |  |  |  |

| Reset:    | 0x0        |  |  |  |

| Property: | Read/Write |  |  |  |

This register is relevant only if USART\_MODE = 0x9 in the USART Mode Register.

| Bit    | 31       | 30 | 29 | 28   | 27      | 26 | 25 | 24 |

|--------|----------|----|----|------|---------|----|----|----|

|        |          |    |    |      |         |    |    |    |

| Access | <b>L</b> | •  | •  |      |         | •  | •  |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 23       | 22 | 21 | 20   | 19      | 18 | 17 | 16 |

|        |          |    |    |      |         |    |    |    |

| Access |          | 1  |    |      |         |    |    |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 15       | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|        |          |    |    |      |         |    |    |    |

| Access |          |    |    |      |         |    |    |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 7        | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        |          |    |    | LOND | DL[7:0] |    |    |    |

| Access |          |    |    |      |         |    |    |    |

| Reset  | 0        | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |          |    |    |      |         |    |    |    |

## Bits 7:0 - LONDL[7:0] LON Data Length

| Value | Description                       |

|-------|-----------------------------------|

| 0-255 | LON data length is LONDL+1 bytes. |

## **Controller Area Network (MCAN)**

| Filter<br>Element | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |

|-------------------|----------------------------|----------------------------|--------------------------|

| 0                 | ID debug message A         | 1                          | 11 1101                  |

| 1                 | ID debug message B         | 2                          | 11 1110                  |

| 2                 | ID debug message C         | 3                          | 11 1111                  |

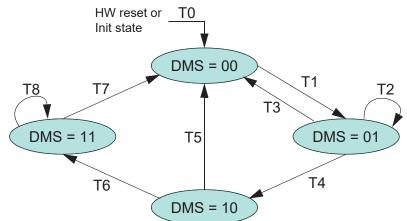

#### 49.5.4.4.2 Debug Message Handling

The debug message handling state machine ensures that debug messages are stored to three consecutive Rx Buffers in the correct order. If some messages are missing, the process is restarted. The DMA request is activated only when all three debug messages A, B, C have been received in the correct order.

The status of the debug message handling state machine is signalled via MCAN\_RXF1S.DMS.

## Figure 49-9. Debug Message Handling State Machine

Table 49-4 Example Filter Configuration for Debug Messages

T0: reset m\_can\_dma\_req output, enable reception of debug messages A, B, and C

- T1: reception of debug message A

- T2: reception of debug message A

- T3: reception of debug message C

- T4: reception of debug message B

- T5: reception of debug messages A, B

- T6: reception of debug message C

- T7: DMA transfer completed

- T8: reception of debug message A,B,C (message rejected)

## 49.5.5 Tx Handling

The Tx Handler handles transmission requests for the dedicated Tx Buffers, the Tx FIFO, and the Tx Queue. It controls the transfer of transmit messages to the CAN Core, the Put and Get Indices, and the Tx Event FIFO. Up to 32 Tx Buffers can be set up for message transmission. The CAN mode for transmission (Classic CAN or CAN FD) can be configured separately for each Tx Buffer element. The Tx

## **Timer Counter (TC)**

| Value | Name      | Description                                         |

|-------|-----------|-----------------------------------------------------|

| 0     | UP        | UP mode without automatic trigger on RC Compare     |

| 1     | UPDOWN    | UPDOWN mode without automatic trigger on RC Compare |

| 2     | UP_RC     | UP mode with automatic trigger on RC Compare        |

| 3     | UPDOWN_RC | UPDOWN mode with automatic trigger on RC Compare    |

## Bit 12 – ENETRG External Event Trigger Enable

Whatever the value programmed in ENETRG, the selected external event only controls the TIOAx output and TIOBx if not used as input (trigger event input or other input used).

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The external event has no effect on the counter and its clock.      |

| 1     | The external event resets the counter and starts the counter clock. |

## Bits 11:10 – EEVT[1:0] External Event Selection

Signal selected as external event.

| Value | Name | Description | TIOB Direction |

|-------|------|-------------|----------------|

| 0     | TIOB | TIOB        | Input          |

| 1     | XC0  | XC0         | Output         |

| 2     | XC1  | XC1         | Output         |

| 3     | XC2  | XC2         | Output         |

**Note:** If TIOB is chosen as the external event signal, it is configured as an input and no longer generates waveforms and subsequently no IRQs.

## Bits 9:8 – EEVTEDG[1:0] External Event Edge Selection

| Value | Name    | Description  |

|-------|---------|--------------|

| 0     | NONE    | None         |

| 1     | RISING  | Rising edge  |

| 2     | FALLING | Falling edge |

| 3     | EDGE    | Each edge    |

**Bit 7 – CPCDIS** Counter Clock Disable with RC Compare

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Counter clock is not disabled when counter reaches RC. |

| 1     | Counter clock is disabled when counter reaches RC.     |

## **Bit 6 – CPCSTOP** Counter Clock Stopped with RC Compare

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Counter clock is not stopped when counter reaches RC. |

| 1     | Counter clock is stopped when counter reaches RC.     |

Bits 5:4 – BURST[1:0] Burst Signal Selection

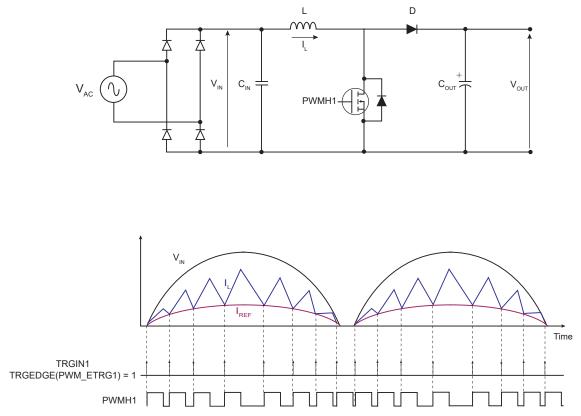

### 51.6.5.1.1 Application Example

The external PWM Reset mode can be used in power factor correction applications.

In the example below, the external trigger input is the PWMEXTRG1 (therefore the PWM channel used for regulation is the channel 1). The PWM channel 1 period (CPRD in the PWM Channel Period Register of the channel 1) must be programmed so that the TRGIN1 event always triggers before the PWM channel 1 period elapses.

In the figure below, an external circuit (not shown) is required to sense the inductor current  $I_L$ . The internal PWM counter of the channel 1 is cleared when the inductor current falls below a specific threshold ( $I_{REF}$ ). This starts a new PWM period and increases the inductor current.

## Figure 51-28. External PWM Reset Mode: Power Factor Correction Application

#### 51.6.5.2 External PWM Start Mode

External PWM Start mode is selected by programming TRGMODE = 2 in the PWM\_ETRGx register.

In this mode, the internal PWM counter can only be reset once it has reached the CPRD value in the PWM Channel Period Register and when the correct level is detected on the corresponding external trigger input. Both conditions have to be met to start a new PWM period. The active detection level is defined by the bit TRGEDGE of the PWM\_ETRGx register.

Note that this mode guarantees a constant  $t_{ON}$  time and a minimum  $t_{OFF}$  time.

## 51.7.10 PWM DMA Register

| Name:     | PWM_DMAR   |

|-----------|------------|

| Offset:   | 0x24       |

| Reset:    | -          |

| Property: | Write-only |

Only the first 16 bits (channel counter size) are significant.

| 16           |  |  |  |

|--------------|--|--|--|

|              |  |  |  |

| W            |  |  |  |

| 0            |  |  |  |

|              |  |  |  |

| 8            |  |  |  |

|              |  |  |  |

| W            |  |  |  |

| 0            |  |  |  |

|              |  |  |  |

| 0            |  |  |  |

| DMADUTY[7:0] |  |  |  |

| W            |  |  |  |

|              |  |  |  |

|              |  |  |  |

## Bits 23:0 – DMADUTY[23:0] Duty-Cycle Holding Register for DMA Access

Each write access to PWM\_DMAR sequentially updates PWM\_CDTYUPDx.CDTYUPD with DMADUTY (only for channel configured as synchronous). See "Method 3: Automatic write of duty-cycle values and automatic trigger of the update".

## Integrity Check Monitor (ICM)

## Bits 11:8 – RBE[3:0] Region Bus Error Interrupt Enable

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | No effect.                                                              |

| 1     | When RBE[i] is set to one, the Region i Bus Error interrupt is enabled. |

## Bits 7:4 – RDM[3:0] Region Digest Mismatch Interrupt Enable

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | No effect.                                                                    |

| 1     | When RDM[i] is set to one, the Region i Digest Mismatch interrupt is enabled. |

## Bits 3:0 – RHC[3:0] Region Hash Completed Interrupt Enable

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | No effect.                                                                   |

| 1     | When RHC[i] is set to one, the Region i Hash Completed interrupt is enabled. |

## **Advanced Encryption Standard (AES)**

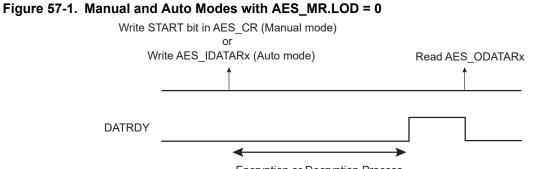

Encryption or Decryption Process

If the user does not want to read AES\_ODATARx between each encryption/decryption, the DATRDY flag will not be cleared. If the DATRDY flag is not cleared, the user cannot know the end of the following encryptions/decryptions.

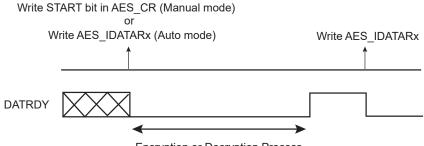

## 57.4.3.1.2 If AES\_MR.LOD = 1

This mode is optimized to process AES CBC-MAC operating mode.

The DATRDY flag is cleared when at least one AES\_IDATAR is written (see the figure below). No additional AES\_ODATAR reads are necessary between consecutive encryptions/decryptions.

## Figure 57-2. Manual and Auto Modes with AES\_MR.LOD = 1

Encryption or Decryption Process

#### 57.4.3.2 DMA Mode

#### 57.4.3.2.1 If AES\_MR.LOD = 0

This mode may be used for all AES operating modes except CBC-MAC where AES\_MR.LOD = 1 mode is recommended.

The end of the encryption/decryption is indicated by the end of DMA transfer associated to AES\_ODATARx (see the figure below). Two DMA channels are required: one for writing message blocks to AES\_IDATARx and one to obtain the result from AES\_ODATARx.

## Figure 57-3. DMA Transfer with AES\_MR.LOD = 0

Enable DMA Channels associated to AES\_IDATARx and AES\_ODATARx

Multiple Encryption or Decryption Processes

Multiple Encryption or Decryption Processes

Write accesses into AES\_IDATARx

Write accesses into AES\_IDATARx

Message fully processed

(cipher or decipher) last

block can be read

# **Advanced Encryption Standard (AES)**

### Bit 15 – LOD Last Output Data Mode

Awarning In DMA mode, reading to the Output Data registers before the last data encryption/decryption process may lead to unpredictable results.

| Value | Description                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No effect.                                                                                                                                                                                                             |

|       | After each end of encryption/decryption, the output data are available either on the output data registers (Manual and Auto modes) or at the address specified in the Channel Buffer Transfer Descriptor for DMA mode. |

|       | In Manual and Auto modes, the DATRDY flag is cleared when at least one of the Output Data registers is read.                                                                                                           |

| 1     | The DATRDY flag is cleared when at least one of the Input Data Registers is written.<br>No more Output Data Register reads are necessary between consecutive encryptions/<br>decryptions (see Last Output Data Mode).  |

### Bits 14:12 – OPMOD[2:0] Operating Mode

For CBC-MAC operating mode, set OPMOD to CBC and LOD to 1.

| Value | Name | Description                                 |

|-------|------|---------------------------------------------|

| 0     | ECB  | ECB: Electronic Codebook mode               |

| 1     | CBC  | CBC: Cipher Block Chaining mode             |

| 2     | OFB  | OFB: Output Feedback mode                   |

| 3     | CFB  | CFB: Cipher Feedback mode                   |

| 4     | CTR  | CTR: Counter mode (16-bit internal counter) |

| 5     | GCM  | GCM: Galois/Counter mode                    |

## Bits 11:10 - KEYSIZE[1:0] Key Size

| Value | Name   | Description              |

|-------|--------|--------------------------|

| 0     | AES128 | AES Key Size is 128 bits |

| 1     | AES192 | AES Key Size is 192 bits |

| 2     | AES256 | AES Key Size is 256 bits |

## Bits 9:8 - SMOD[1:0] Start Mode

If a DMA transfer is used, configure SMOD to 2. See DMA Mode for more details.

| Value | Name          | Description                             |

|-------|---------------|-----------------------------------------|

| 0     | MANUAL_START  | Manual Mode                             |

| 1     | AUTO_START    | Auto Mode                               |

| 2     | IDATAR0_START | AES_IDATAR0 access only Auto Mode (DMA) |

# Bits 7:4 – PROCDLY[3:0] Processing Delay

Processing Time =  $N \times (PROCDLY + 1)$

## where

• N = 10 when KEYSIZE = 0