Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                    |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                             |

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                                   |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                | -                                                                                                  |

| RAM Size                   | 256K x 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-LQFP                                                                                           |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q19a-an                          |

|     | 32.6.  | Register Summary                                       | 362 |

|-----|--------|--------------------------------------------------------|-----|

| 33. | Exter  | nal Bus Interface (EBI)                                | 424 |

|     |        | Description                                            |     |

|     |        | Embedded Characteristics                               |     |

|     | 33.3.  | EBI Block Diagram                                      | 425 |

|     |        | I/O Lines Description                                  |     |

|     | 33.5.  | Application Example                                    | 427 |

| 34. | SDR    | AM Controller (SDRAMC)                                 | 431 |

|     | 34.1.  | Description                                            | 431 |

|     |        | Embedded Characteristics                               |     |

|     | 34.3.  | Signal Description                                     | 432 |

|     | 34.4.  | Software Interface/SDRAM Organization, Address Mapping | 432 |

|     | 34.5.  | Product Dependencies                                   | 433 |

|     | 34.6.  | Functional Description                                 | 435 |

|     | 34.7.  | Register Summary                                       | 442 |

| 35. | Statio | Memory Controller (SMC)                                | 461 |

|     | 35.1.  | Description                                            | 461 |

|     | 35.2.  | Embedded Characteristics                               | 461 |

|     | 35.3.  | I/O Lines Description                                  | 461 |

|     | 35.4.  | Multiplexed Signals                                    | 462 |

|     | 35.5.  | Product Dependencies                                   | 462 |

|     | 35.6.  | External Memory Mapping                                | 463 |

|     | 35.7.  | Connection to External Devices                         | 463 |

|     | 35.8.  | Application Example                                    | 467 |

|     | 35.9.  | Standard Read and Write Protocols                      | 469 |

|     | 35.10. | Scrambling/Unscrambling Function                       | 477 |

|     | 35.11. | Automatic Wait States                                  | 478 |

|     | 35.12. | Data Float Wait States                                 | 481 |

|     | 35.13. | External Wait                                          | 485 |

|     | 35.14. | Slow Clock Mode                                        | 489 |

|     | 35.15. | Asynchronous Page Mode                                 | 491 |

|     | 35.16. | Register Summary                                       | 494 |

| 36. | DMA    | Controller (XDMAC)                                     | 508 |

|     | 36.1.  | Description                                            | 508 |

|     | 36.2.  | Embedded Characteristics                               | 508 |

|     | 36.3.  | Block Diagram                                          | 509 |

|     | 36.4.  | DMA Controller Peripheral Connections                  | 509 |

|     | 36.5.  | Functional Description                                 | 511 |

|     | 36.6.  | Linked List Descriptor Operation                       | 515 |

|     | 36.7.  | XDMAC Maintenance Software Operations                  | 517 |

|     | 36.8.  | XDMAC Software Requirements                            | 518 |

|     |        | Register Summary                                       |     |

| 37. | Imag   | e Sensor Interface (ISI)                               | 590 |

**USB Transmitter Macrocell Interface (UTMI)**

# 20.3.1 OHCI Interrupt Configuration Register

Name: UTMI\_OHCIICR

**Offset**: 0x10 **Reset**: 0x0

Property: Read/Write

| Bit    | 31       | 30 | 29       | 28   | 27 | 26 | 25 | 24   |

|--------|----------|----|----------|------|----|----|----|------|

|        |          |    |          |      |    |    |    |      |

| Access |          |    |          |      |    |    |    |      |

| Reset  |          |    |          |      |    |    |    |      |

|        |          |    |          |      |    |    |    |      |

| Bit    | 23       | 22 | 21       | 20   | 19 | 18 | 17 | 16   |

|        | UDPPUDIS |    |          |      |    |    |    |      |

| Access |          |    |          |      |    |    |    |      |

| Reset  | 0        |    |          |      |    |    |    |      |

|        |          |    |          |      |    |    |    |      |

| Bit    | 15       | 14 | 13       | 12   | 11 | 10 | 9  | 8    |

|        |          |    |          |      |    |    |    |      |

| Access |          |    |          |      |    |    |    |      |

| Reset  |          |    |          |      |    |    |    |      |

|        |          |    |          |      |    |    |    |      |

| Bit    | 7        | 6  | 5        | 4    | 3  | 2  | 1  | 0    |

|        |          |    | APPSTART | ARIE |    |    |    | RESx |

| Access |          |    |          |      |    |    |    |      |

| Reset  |          |    | 0        | 0    |    |    |    | 0    |

# Bit 23 - UDPPUDIS USB Device Pull-up Disable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | USB device pull-up connection is enabled.  |

| 1     | USB device pull-up connection is disabled. |

#### Bit 5 - APPSTART Reserved

| Value | Description   |

|-------|---------------|

| 0     | Must write 0. |

## Bit 4 - ARIE OHCI Asynchronous Resume Interrupt Enable

| Value | Description         |

|-------|---------------------|

| 0     | Interrupt disabled. |

| 1     | Interrupt enabled.  |

## Bit 0 - RESx USB PORTx Reset

| Value | Description      |

|-------|------------------|

| 0     | Resets USB port. |

| 1     | Usable USB port. |

# 29. General Purpose Backup Registers (GPBR)

# 29.1 Description

The System Controller embeds 128 bits of General Purpose Backup registers organized as 8 32-bit registers.

It is possible to generate an immediate clear of the content of General Purpose Backup registers 0 to 3 (first half) if a Low-power Debounce event is detected on one of the wakeup pins, WKUP0 or WKUP1. The content of the other General Purpose Backup registers (second half) remains unchanged.

The Supply Controller module must be programmed accordingly. In the register SUPC\_WUMR in the Supply Controller module, LPDBCCLR, LPDBCEN0 and/or LPDBCEN1 bit must be configured to 1 and LPDBC must be other than 0.

If a Tamper event has been detected, it is not possible to write to the General Purpose Backup registers while the LPDBCS0 or LPDBCS1 flags are not cleared in the Supply Controller Status Register (SUPC\_SR).

## 29.2 Embedded Characteristics

- 128 bits of General Purpose Backup Registers

- Immediate Clear on Tamper Event

# Parallel Input/Output Controller (PIO)

0

## 32.6.1.47 PIO Write Protection Status Register

Name:

PIO\_WPSR

Offset:

0x00E8

Reset:

0x00000000

Property:

Read-only

Reset

| Bit    | 31 | 30 | 29 | 28    | 27       | 26 | 25 | 24   |

|--------|----|----|----|-------|----------|----|----|------|

|        |    |    |    |       |          |    |    |      |

| Access |    |    |    |       |          |    |    |      |

| Reset  |    |    |    |       |          |    |    |      |

|        |    |    |    |       |          |    |    |      |

| Bit    | 23 | 22 | 21 | 20    | 19       | 18 | 17 | 16   |

|        |    |    |    | WPVSF | RC[15:8] |    |    |      |

| Access |    |    |    |       |          |    |    |      |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0    |

|        |    |    |    |       |          |    |    |      |

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9  | 8    |

|        |    |    |    | WPVSI | RC[7:0]  |    |    |      |

| Access |    |    |    |       |          |    |    |      |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0    |

|        |    |    |    |       |          |    |    |      |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0    |

|        |    |    |    |       |          |    |    | WPVS |

| Access |    |    |    |       |          |    |    |      |

# Bits 23:8 - WPVSRC[15:0] Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

Bit 0 - WPVS Write Protection Violation Status

| Value | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 0     | No write protection violation has occurred since the last read of the PIO_WPSR.                 |

| 1     | A write protection violation has occurred since the last read of the PIO_WPSR. If this          |

|       | violation is an unauthorized attempt to write a protected register, the associated violation is |

|       | reported into field WPVSRC.                                                                     |

# 36.9.9 XDMAC Global Channel Disable Register

Name: XDMAC\_GD

Offset: 0x20 Reset: -

Property: Write-only

| Bit    | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   |

|--------|------|------|------|------|------|------|------|------|

|        |      |      |      |      |      |      |      |      |

| Access |      |      |      |      |      |      |      |      |

| Reset  |      |      |      |      |      |      |      |      |

|        |      |      |      |      |      |      |      |      |

| Bit    | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|        | DI23 | DI22 | DI21 | DI20 | DI19 | DI18 | DI17 | DI16 |

| Access | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset  | _    | _    | _    | _    | _    | _    | _    | _    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|        | DI15 | DI14 | DI13 | DI12 | DI11 | DI10 | DI9  | DI8  |

| Access | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset  | _    | _    | _    | _    | _    | _    | _    | _    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | DI7  | DI6  | DI5  | DI4  | DI3  | DI2  | DI1  | DI0  |

| Access | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset  | _    | _    | _    | _    | _    | _    | _    | _    |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23 - DI XDMAC Channel x Disable

| Value | Description             |

|-------|-------------------------|

| 0     | This bit has no effect. |

| 1     | Disables channel x.     |

| Bit   | Function                                                                                                                                                                                                                                                                                                            |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22:20 | Transmit IP/TCP/UDP checksum generation offload errors: 000: No Error.                                                                                                                                                                                                                                              |

|       | 001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                                        |

|       | 010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                                        |

|       | 011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.                                                                                                                                                                                                   |

|       | 100: The Packet was not identified as VLAN, SNAP or IP.                                                                                                                                                                                                                                                             |

|       | 101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                                                                     |

|       | 110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                           |

|       | 111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.                                                                                                                                                                                                                        |

| 19:17 | Reserved                                                                                                                                                                                                                                                                                                            |

| 16    | No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.  This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. |

|       | Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.                                                                                                                                                     |

| 15    | Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.                                                                                                                                                                                                                 |

| 14    | Reserved                                                                                                                                                                                                                                                                                                            |

| 13:0  | Length of buffer                                                                                                                                                                                                                                                                                                    |

To transmit frames, the buffer descriptors must be initialized by writing an appropriate Byte address to bits [31:0] of the first word of each descriptor list entry.

The second word of the transmit buffer descriptor is initialized with control information that indicates the length of the frame, whether or not the MAC is to append CRC and whether the buffer is the last buffer in the frame.

After transmission the status bits are written back to the second word of the first buffer along with the used bit. Bit 31 is the used bit which must be zero when the control word is read if transmission is to take place. It is written to '1' once the frame has been transmitted. Bits[29:20] indicate various transmit error conditions. Bit 30 is the wrap bit which can be set for any buffer within a frame. If no wrap bit is encountered the gueue pointer continues to increment.

The Transmit Buffer Queue Base Address register can only be updated while transmission is disabled or halted; otherwise any attempted write will be ignored. When transmission is halted the transmit buffer queue pointer will maintain its value. Therefore when transmission is restarted the next descriptor read

**USB High-Speed Interface (USBHS)**

| Offset                                                 | Name                     | Bit Pos. |                  |                 |            |           |            |           |           |           |  |

|--------------------------------------------------------|--------------------------|----------|------------------|-----------------|------------|-----------|------------|-----------|-----------|-----------|--|

|                                                        |                          | 23:16    |                  |                 |            | BUFF_A    | DD[23:16]  |           | ļ         |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_A    | DD[31:24]  |           |           |           |  |

|                                                        |                          | 7:0      | BURST_LCK        | DESC_LD_IT      | END_BUFFIT | END_TR_IT | END_B_EN   | END_TR_EN | LDNXT_DSC | CHANN_ENB |  |

|                                                        | USBHS_DEVDMAC            | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x0338  0x033C  0x0340  0x0344  0x0344  0x0346  0x0350 | ONTROL4                  | 23:16    |                  |                 |            | BUFF_LE   | NGTH[7:0]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_LEN  | NGTH[15:8] |           |           |           |  |

|                                                        |                          | 7:0      |                  | DESC_LDST       | END_BF_ST  | END_TR_ST |            |           | CHANN_ACT | CHANN_ENB |  |

|                                                        | USBHS_DEVDMAS            | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x033C                                                 | TATUS4                   | 23:16    |                  | BUFF_COUNT[7:0] |            |           |            |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_CO   | UNT[15:8]  |           |           |           |  |

|                                                        |                          | 7:0      |                  |                 |            | NXT_DSC   | _ADD[7:0]  |           |           |           |  |

|                                                        | USBHS_DEVDMAN            | 15:8     |                  |                 |            | NXT_DSC_  | _ADD[15:8] |           |           |           |  |

| 0x0340                                                 | XTDSC5                   | 23:16    |                  |                 |            | NXT_DSC_  | ADD[23:16] |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | NXT_DSC_  | ADD[31:24] |           |           |           |  |

|                                                        |                          | 7:0      |                  |                 |            | BUFF_A    | ADD[7:0]   |           |           |           |  |

|                                                        | USBHS_DEVDMAA            | 15:8     |                  |                 |            | BUFF_A    | DD[15:8]   |           |           |           |  |

| 0x0344                                                 | DDRESS5                  | 23:16    |                  |                 |            | BUFF_A    | DD[23:16]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_A    | DD[31:24]  |           |           |           |  |

|                                                        |                          | 7:0      | BURST_LCK        | DESC_LD_IT      | END_BUFFIT | END_TR_IT | END_B_EN   | END_TR_EN | LDNXT_DSC | CHANN_ENB |  |

|                                                        | USBHS_DEVDMAC<br>ONTROL5 | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x0348                                                 |                          | 23:16    | BUFF_LENGTH[7:0] |                 |            |           |            |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_LEN  | NGTH[15:8] |           |           |           |  |

|                                                        |                          | 7:0      |                  | DESC_LDST       | END_BF_ST  | END_TR_ST |            |           | CHANN_ACT | CHANN_ENB |  |

| 0 0040                                                 | USBHS_DEVDMAS            | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x034C                                                 | TATUS5                   | 23:16    |                  |                 |            | BUFF_CC   | DUNT[7:0]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_CO   | UNT[15:8]  |           |           |           |  |

|                                                        |                          | 7:0      |                  |                 |            | NXT_DSC   | _ADD[7:0]  |           |           |           |  |

|                                                        | USBHS_DEVDMAN            | 15:8     |                  |                 |            | NXT_DSC   | _ADD[15:8] |           |           |           |  |

| 0x0350                                                 | XTDSC6                   | 23:16    |                  |                 |            | NXT_DSC_  | ADD[23:16] |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | NXT_DSC_  | ADD[31:24] |           |           |           |  |

|                                                        |                          | 7:0      |                  |                 |            | BUFF_A    | ADD[7:0]   |           |           |           |  |

| 0 0054                                                 | USBHS_DEVDMAA            | 15:8     |                  |                 |            | BUFF_A    | .DD[15:8]  |           |           |           |  |

| 0x0354                                                 | DDRESS6                  | 23:16    |                  |                 |            | BUFF_A    | DD[23:16]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_A    | DD[31:24]  |           |           |           |  |

|                                                        |                          | 7:0      | BURST_LCK        | DESC_LD_IT      | END_BUFFIT | END_TR_IT | END_B_EN   | END_TR_EN | LDNXT_DSC | CHANN_ENB |  |

|                                                        | USBHS_DEVDMAC            | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x0358                                                 | ONTROL6                  | 23:16    |                  |                 |            | BUFF_LE   | NGTH[7:0]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_LEN  | NGTH[15:8] |           |           |           |  |

|                                                        |                          | 7:0      |                  | DESC_LDST       | END_BF_ST  | END_TR_ST |            |           | CHANN_ACT | CHANN_ENB |  |

| 00050                                                  | USBHS_DEVDMAS            | 15:8     |                  |                 |            |           |            |           |           |           |  |

| 0x035C                                                 | TATUS6                   | 23:16    |                  |                 |            | BUFF_CC   | DUNT[7:0]  |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | BUFF_CO   |            |           |           |           |  |

|                                                        |                          | 7:0      |                  |                 |            | NXT_DSC   | _ADD[7:0]  |           |           |           |  |

| 0.0000                                                 | USBHS_DEVDMAN            | 15:8     |                  |                 |            | NXT_DSC   | _ADD[15:8] |           |           |           |  |

| 0x0360                                                 | XTDSC7                   | 23:16    |                  |                 |            | NXT_DSC_  | ADD[23:16] |           |           |           |  |

|                                                        |                          | 31:24    |                  |                 |            | NXT_DSC   | ADD[31:24] |           |           |           |  |

**USB High-Speed Interface (USBHS)**

| Offset | Name                            | Bit Pos. |                   |           |         |          |       |          |         |          |

|--------|---------------------------------|----------|-------------------|-----------|---------|----------|-------|----------|---------|----------|

|        |                                 | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05D4 | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R5 (INTPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        |                                 | 7:0      | SHORTPACK<br>ETIE | CRCERRE   | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05D4 | USBHS_HSTPIPIM<br>R5 (ISOPIPES) | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R3 (ISOPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        | LICOUC LICTDIDIM                | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | TXSTPE   | TXOUTE  | RXINE    |

| 0x05D8 | USBHS_HSTPIPIM<br>R6            | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | IXO                             | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        | LIODUO LIOTDIDIA                | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05D8 | USBHS_HSTPIPIM<br>R6 (INTPIPES) | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R6 (INTPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        |                                 | 7:0      | SHORTPACK<br>ETIE | CRCERRE   | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05D8 | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R6 (ISOPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        | LICOUR LICTORIM                 | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | TXSTPE   | TXOUTE  | RXINE    |

| 0x05DC | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R7                              | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        |                                 | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05DC | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R7 (INTPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        |                                 | 7:0      | SHORTPACK<br>ETIE | CRCERRE   | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

| 0x05DC | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R7 (ISOPIPES)                   | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

|        | LIOPUS LISTERS                  | 7:0      | SHORTPACK<br>ETIE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | TXSTPE   | TXOUTE  | RXINE    |

| 0x05E0 | USBHS_HSTPIPIM                  | 15:8     |                   | FIFOCON   |         | NBUSYBKE |       |          |         |          |

|        | R8                              | 23:16    |                   |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

|        |                                 | 31:24    |                   |           |         |          |       |          |         |          |

**USB High-Speed Interface (USBHS)**

## 39.6.18 Device Endpoint Interrupt Clear Register (Isochronous Endpoints)

Name: USBHS DEVEPTICRx (ISOENPT)

**Offset:** 0x0160 + x\*0x04 [x=0..9]

Reset: 0

Property: Read/Write

This register view is relevant only if EPTYPE = 0x1 in "Device Endpoint x Configuration Register".

For additional information, see "Device Endpoint x Status Register (Isochronous Endpoints)".

This register always reads as zero.

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Clears the corresponding bit in USBHS\_DEVEPTISRx.

| Bit    | 31         | 30       | 29      | 28          | 27           | 26       | 25      | 24     |

|--------|------------|----------|---------|-------------|--------------|----------|---------|--------|

|        |            |          |         |             |              |          |         |        |

| Access |            |          |         |             |              |          |         |        |

| Reset  |            |          |         |             |              |          |         |        |

|        |            |          |         |             |              |          |         |        |

| Bit    | 23         | 22       | 21      | 20          | 19           | 18       | 17      | 16     |

|        |            |          |         |             |              |          |         |        |

| Access |            |          |         |             |              |          |         |        |

| Reset  |            |          |         |             |              |          |         |        |

|        |            |          |         |             |              |          |         |        |

| Bit    | 15         | 14       | 13      | 12          | 11           | 10       | 9       | 8      |

|        |            |          |         |             |              |          |         |        |

| Access |            |          |         |             |              |          |         |        |

| Reset  |            |          |         |             |              |          |         |        |

|        |            |          |         |             |              |          |         |        |

| Bit    | 7          | 6        | 5       | 4           | 3            | 2        | 1       | 0      |

|        | SHORTPACKE | CRCERRIC | OVERFIC | HBISOFLUSHI | HBISOINERRIC | UNDERFIC | RXOUTIC | TXINIC |

|        | TC         |          |         | С           |              |          |         |        |

| Access |            |          |         |             |              |          |         |        |

| Reset  | 0          | 0        | 0       | 0           | 0            | 0        | 0       | 0      |

Bit 7 - SHORTPACKETC Short Packet Interrupt Clear

Bit 6 – CRCERRIC CRC Error Interrupt Clear

Bit 5 - OVERFIC Overflow Interrupt Clear

Bit 4 – HBISOFLUSHIC High Bandwidth Isochronous IN Flush Interrupt Clear

Bit 3 – HBISOINERRIC High Bandwidth Isochronous IN Underflow Error Interrupt Clear

Bit 2 - UNDERFIC Underflow Interrupt Clear

# **High-Speed Multimedia Card Interface (HSMCI)**

## 40.14.6 HSMCI Command Register

Name: HSMCI\_CMDR

Offset: 0x14

Property: Write-only

This register is write-protected while CMDRDY is 0 in HSMCI\_SR. If an Interrupt command is sent, this register is only writable by an interrupt response (field SPCMD). This means that the current command execution cannot be interrupted or modified.

| Bit    | 31   | 30      | 29 | 28         | 27       | 26     | 25         | 24      |

|--------|------|---------|----|------------|----------|--------|------------|---------|

|        |      |         |    |            | BOOT_ACK | ATACS  | IOSPC      | MD[1:0] |

| Access |      |         |    |            |          |        |            |         |

| Reset  |      |         |    |            |          |        |            |         |

|        |      |         |    |            |          |        |            |         |

| Bit    | 23   | 22      | 21 | 20         | 19       | 18     | 17         | 16      |

|        |      |         |    | TRTYP[2:0] |          | TRDIR  | TRCM       | D[1:0]  |

| Access |      |         |    |            |          |        |            |         |

| Reset  |      |         |    |            |          |        |            |         |

|        |      |         |    |            |          |        |            |         |

| Bit    | 15   | 14      | 13 | 12         | 11       | 10     | 9          | 8       |

|        |      |         |    | MAXLAT     | OPDCMD   |        | SPCMD[2:0] |         |

| Access |      |         |    |            |          |        |            |         |

| Reset  |      |         |    |            |          |        |            |         |

|        |      |         |    |            |          |        |            |         |

| Bit    | 7    | 6       | 5  | 4          | 3        | 2      | 1          | 0       |

|        | RSPT | YP[1:0] |    |            | CMDN     | B[5:0] |            |         |

|        |      |         |    |            |          |        |            |         |

Access

Reset

#### Bit 27 - BOOT ACK Boot Operation Acknowledge

The master can choose to receive the boot acknowledge from the slave when a Boot Request command is issued. When set to one this field indicates that a Boot acknowledge is expected within a programmable amount of time defined with DTOMUL and DTOCYC fields located in the HSMCI\_DTOR. If the acknowledge pattern is not received then an acknowledge timeout error is raised. If the acknowledge pattern is corrupted then an acknowledge pattern error is set.

# Bit 26 – ATACS ATA with Command Completion Signal

0 (NORMAL): Normal operation mode.

1 (COMPLETION): This bit indicates that a completion signal is expected within a programmed amount of time (HSMCI\_CSTOR).

Bits 25:24 - IOSPCMD[1:0] SDIO Special Command

| Value | Name    | Description                 |

|-------|---------|-----------------------------|

| 0     | STD     | Not an SDIO Special Command |

| 1     | SUSPEND | SDIO Suspend Command        |

| 2     | RESUME  | SDIO Resume Command         |

# **High-Speed Multimedia Card Interface (HSMCI)**

## Bits 21:19 - TRTYP[2:0] Transfer Type

| Value | Name     | Description                |

|-------|----------|----------------------------|

| 0     | SINGLE   | MMC/SD Card Single Block   |

| 1     | MULTIPLE | MMC/SD Card Multiple Block |

| 2     | STREAM   | MMC Stream                 |

| 4     | BYTE     | SDIO Byte                  |

| 5     | BLOCK    | SDIO Block                 |

## Bit 18 - TRDIR Transfer Direction

0 (WRITE): Write. 1 (READ): Read.

## Bits 17:16 - TRCMD[1:0] Transfer Command

| Value | Name       | Description         |

|-------|------------|---------------------|

| 0     | NO_DATA    | No data transfer    |

| 1     | START_DATA | Start data transfer |

| 2     | STOP_DATA  | Stop data transfer  |

| 3     | Reserved   | Reserved            |

# Bit 12 - MAXLAT Max Latency for Command to Response

0 (5): 5-cycle max latency.

1 (64): 64-cycle max latency.

## Bit 11 - OPDCMD Open Drain Command

0 (PUSHPULL): Push pull command.

1 (OPENDRAIN): Open drain command.

Bits 10:8 - SPCMD[2:0] Special Command

| Value | Name    | Description                                                                             |

|-------|---------|-----------------------------------------------------------------------------------------|

| 0     | STD     | Not a special CMD.                                                                      |

| 1     | INIT    | Initialization CMD:                                                                     |

|       |         | 74 clock cycles for initialization sequence.                                            |

| 2     | SYNC    | Synchronized CMD:                                                                       |

|       |         | Wait for the end of the current data block transfer before sending the pending command. |

| 3     | CE_ATA  | CE-ATA Completion Signal disable Command.                                               |

|       |         | The host cancels the ability for the device to return a command completion signal       |

|       |         | on the command line.                                                                    |

| 4     | IT_CMD  | Interrupt command:                                                                      |

|       |         | Corresponds to the Interrupt Mode (CMD40).                                              |

| 5     | IT_RESP | Interrupt response:                                                                     |

|       |         | Corresponds to the Interrupt Mode (CMD40).                                              |

# **High-Speed Multimedia Card Interface (HSMCI)**

- Bit 21 DCRCE Data CRC Error Interrupt Mask

- Bit 20 RTOE Response Time-out Error Interrupt Mask

- Bit 19 RENDE Response End Bit Error Interrupt Mask

- Bit 18 RCRCE Response CRC Error Interrupt Mask

- Bit 17 RDIRE Response Direction Error Interrupt Mask

- Bit 16 RINDE Response Index Error Interrupt Mask

- Bit 13 CSRCV Completion Signal Received Interrupt Mask

- Bit 12 SDIOWAIT SDIO Read Wait Operation Status Interrupt Mask

- Bit 8 SDIOIRQA SDIO Interrupt for Slot A Interrupt Mask

- Bit 5 NOTBUSY Data Not Busy Interrupt Mask

- Bit 4 DTIP Data Transfer in Progress Interrupt Mask

- Bit 3 BLKE Data Block Ended Interrupt Mask

- Bit 2 TXRDY Transmit Ready Interrupt Mask

- Bit 1 RXRDY Receiver Ready Interrupt Mask

- Bit 0 CMDRDY Command Ready Interrupt Mask

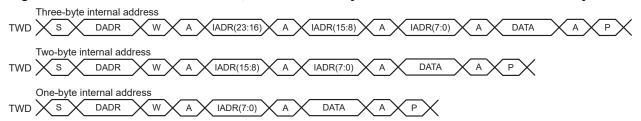

See Master Write with One-, Two- or Three-Byte Internal Address and One Data Byte and Internal Address Usage for the master write operation with internal address.

The three internal address bytes are configurable through TWIHS MMR.

If the slave device supports only a 7-bit address, i.e., no internal address, IADRSZ must be set to 0.

The table below shows the abbreviations used in the figures below.

Table 43-4. Abbreviations

| Abbreviation | Definition       |

|--------------|------------------|

| S            | Start            |

| Sr           | Repeated Start   |

| P            | Stop             |

| W            | Write            |

| R            | Read             |

| A            | Acknowledge      |

| NA           | Not Acknowledge  |

| DADR         | Device Address   |

| IADR         | Internal Address |

Figure 43-10. Master Write with One-, Two- or Three-Byte Internal Address and One Data Byte

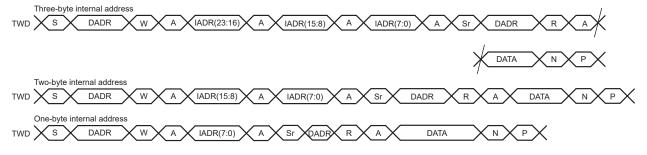

Figure 43-11. Master Read with One-, Two- or Three-Byte Internal Address and One Data Byte

## 43.6.3.5.2 10-bit Slave Addressing

For a slave address higher than seven bits, configure the address size (IADRSZ) and set the other slave address bits in the Internal Address register (TWIHS IADR). The two remaining internal address bytes, IADR[15:8] and IADR[23:16], can be used the same way as in 7-bit slave addressing.

Example: Address a 10-bit device (10-bit device address is b1 b2 b3 b4 b5 b6 b7 b8 b9 b10)

- Program IADRSZ = 1,

- Program DADR with 1 1 1 1 0 b1 b2 (b1 is the MSB of the 10-bit address, b2, etc.)

DS60001527B-page 1181 **Datasheet** © 2018 Microchip Technology Inc.

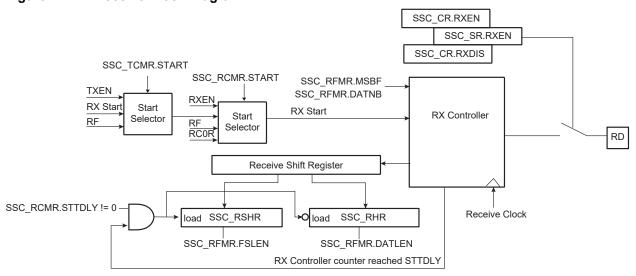

#### 44.8.3 Receive Operations

A receive frame is triggered by a start event and can be followed by synchronization data before data transmission.

The start event is configured setting the Receive Clock Mode Register (SSC\_RCMR). See Start.

The frame synchronization is configured by setting the Receive Frame Mode Register (SSC\_RFMR). See Frame Synchronization.

The receiver uses a shift register clocked by the receive clock signal and the start mode selected in the SSC RCMR. The data is transferred from the shift register depending on the data format selected.

When the receiver shift register is full, the SSC transfers this data in the holding register, the status flag RXRDY is set in the SSC\_SR and the data can be read in the receiver holding register. If another transfer occurs before read of the Receive Holding Register (SSC\_RHR), the status flag OVERUN is set in the SSC\_SR and the receiver shift register is transferred in the SSC\_RHR.

Figure 44-12. Receive Block Diagram

#### 44.8.4 Start

The transmitter and receiver can both be programmed to start their operations when an event occurs, respectively in the Transmit Start Selection (START) field of SSC\_TCMR and in the Receive Start Selection (START) field of SSC\_RCMR.

Under the following conditions the start event is independently programmable:

- Continuous. In this case, the transmission starts as soon as a word is written in SSC\_THR and the

reception starts as soon as the receiver is enabled.

- · Synchronously with the transmitter/receiver

- On detection of a falling/rising edge on TF/RF

- On detection of a low level/high level on TF/RF

- On detection of a level change or an edge on TF/RF

A start can be programmed in the same manner on either side of the Transmit/Receive Clock Register (SSC\_RCMR/SSC\_TCMR). Thus, the start could be on TF (Transmit) or RF (Receive).

Moreover, the receiver can start when data is detected in the bit stream with the Compare Functions.

# Universal Synchronous Asynchronous Receiver Transc...

| Name | Description                                              | Туре   | Active Level |

|------|----------------------------------------------------------|--------|--------------|

|      | or Slave Select (NSS) in SPI Slave mode                  |        |              |

| RTS  | Request to Send or Slave Select (NSS) in SPI Master mode | Output | Low          |

#### 46.5 **Product Dependencies**

#### 46.5.1 I/O Lines

The pins used for interfacing the USART may be multiplexed with the PIO lines. The programmer must first program the PIO controller to assign the desired USART pins to their peripheral function. If I/O lines of the USART are not used by the application, they can be used for other purposes by the PIO Controller.

All the pins of the modems may or may not be implemented on the USART. On USARTs not equipped with the corresponding pin, the associated control bits and statuses have no effect on the behavior of the USART.

#### 46.5.2 **Power Management**

The USART is not continuously clocked. The programmer must first enable the USART clock in the Power Management Controller (PMC) before using the USART. However, if the application does not require USART operations, the USART clock can be stopped when not needed and be restarted later. In this case, the USART will resume its operations where it left off.

#### 46.5.3 **Interrupt Sources**

The USART interrupt line is connected on one of the internal sources of the Interrupt Controller. Using the USART interrupt requires the Interrupt Controller to be programmed first.

#### 46.6 **Functional Description**

#### 46.6.1 **Baud Rate Generator**

The baud rate generator provides the bit period clock, also named the baud rate clock, to both the receiver and the transmitter.

The baud rate generator clock source is selected by configuring the USCLKS field in the USART Mode register (US\_MR) to one of the following:

- The peripheral clock

- A division of the peripheral clock, where the divider is product-dependent, but generally set to 8

- A processor/peripheral independent clock source fully programmable provided by PMC (PCK)

- The external clock, available on the SCK pin

The baud rate generator is based upon a 16-bit divider, which is configured using the CD field of the Baud Rate Generator register (US BRGR). If CD is configured to '0', the baud rate generator does not generate any clocks. If CD is configured to '1', the divider is bypassed and becomes inactive.

If the external SCK clock is selected, the duration of the low and high levels of the signal provided on the SCK pin must be longer than a peripheral clock period. The frequency of the signal provided on SCK must be at least 3 times lower than the frequency provided on the peripheral clock in USART mode (field

DS60001527B-page 1319 **Datasheet** © 2018 Microchip Technology Inc.

**Controller Area Network (MCAN)**

| Offset | Name            | Bit Pos. |       |       |           |        |           |            |           |       |

|--------|-----------------|----------|-------|-------|-----------|--------|-----------|------------|-----------|-------|

|        |                 | 31:24    | F1OM  |       |           |        | F1WM[6:0] |            |           |       |

|        |                 | 7:0      |       |       |           |        | F1FL[6:0] |            |           |       |

|        |                 | 15:8     |       |       |           |        | F1G       | I[5:0]     |           |       |

| 0xB4   | MCAN_RXF1S      | 23:16    |       |       |           |        | F1P       | I[5:0]     |           |       |

|        |                 | 31:24    | DMS   | [1:0] |           |        |           |            | RF1L      | F1F   |

|        |                 | 7:0      |       |       |           |        | F1A       | l[5:0]     |           |       |

| 000    | MOAN DYEAR      | 15:8     |       |       |           |        |           |            |           |       |

| 0xB8   | MCAN_RXF1A      | 23:16    |       |       |           |        |           |            |           |       |

|        |                 | 31:24    |       |       |           |        |           |            |           |       |

|        |                 | 7:0      |       |       | F1DS[2:0] |        |           |            | F0DS[2:0] |       |

| 0vBC   | 0xBC MCAN RXESC | 15:8     |       |       |           |        |           |            | RBDS[2:0] |       |

| UXBC   | MCAN_RXESC      | 23:16    |       |       |           |        |           |            |           |       |

|        |                 | 31:24    |       |       |           |        |           |            |           |       |

|        |                 | 7:0      |       |       | TBS       | A[5:0] |           |            |           |       |

| 0xC0   | MCAN TYPE       | 15:8     |       |       |           | TBSA   | [13:6]    |            |           |       |

| UXCU   | MCAN_TXBC       | 23:16    |       |       |           |        | NDT       | B[5:0]     |           |       |

|        |                 | 31:24    |       | TFQM  |           |        | TFQ       | S[5:0]     |           |       |

|        |                 | 7:0      |       |       |           |        | TFFI      | L[5:0]     |           |       |

| 0xC4   | MCAN TXFQS      | 15:8     |       |       |           |        |           | TFGI[4:0]  |           |       |

| 0.04   | MCAN_TXTQ3      | 23:16    |       |       | TFQF      |        |           | TFQPI[4:0] |           |       |

|        |                 | 31:24    |       |       |           |        |           |            |           |       |

|        | MCAN_TXESC      | 7:0      |       |       |           |        |           |            | TBDS[2:0] |       |

| 0xC8   |                 | 15:8     |       |       |           |        |           |            |           |       |

| UXCO   |                 | 23:16    |       |       |           |        |           |            |           |       |

|        |                 | 31:24    |       |       |           |        |           |            |           |       |

|        |                 | 7:0      | TRP7  | TRP6  | TRP5      | TRP4   | TRP3      | TRP2       | TRP1      | TRP0  |

| 0xCC   | MCAN_TXBRP      | 15:8     | TRP15 | TRP14 | TRP13     | TRP12  | TRP11     | TRP10      | TRP9      | TRP8  |

| 0,00   | WOAN_IXBRI      | 23:16    | TRP23 | TRP22 | TRP21     | TRP20  | TRP19     | TRP18      | TRP17     | TRP16 |

|        |                 | 31:24    | TRP31 | TRP30 | TRP29     | TRP28  | TRP27     | TRP26      | TRP25     | TRP24 |

|        |                 | 7:0      | AR7   | AR6   | AR5       | AR4    | AR3       | AR2        | AR1       | AR0   |

| 0xD0   | MCAN_TXBAR      | 15:8     | AR15  | AR14  | AR13      | AR12   | AR11      | AR10       | AR9       | AR8   |

| OXDO   | WO/W_IXB/W      | 23:16    | AR23  | AR22  | AR21      | AR20   | AR19      | AR18       | AR17      | AR16  |

|        |                 | 31:24    | AR31  | AR30  | AR29      | AR28   | AR27      | AR26       | AR25      | AR24  |

|        |                 | 7:0      | CR7   | CR6   | CR5       | CR4    | CR3       | CR2        | CR1       | CR0   |

| 0xD4   | MCAN_TXBCR      | 15:8     | CR15  | CR14  | CR13      | CR12   | CR11      | CR10       | CR9       | CR8   |

| OAD I  | Mora Line       | 23:16    | CR23  | CR22  | CR21      | CR20   | CR19      | CR18       | CR17      | CR16  |

|        |                 | 31:24    | CR31  | CR30  | CR29      | CR28   | CR27      | CR26       | CR25      | CR24  |

|        |                 | 7:0      | TO7   | TO6   | TO5       | TO4    | ТО3       | TO2        | TO1       | TO0   |

| 0xD8   | MCAN_TXBTO      | 15:8     | TO15  | TO14  | TO13      | TO12   | TO11      | TO10       | TO9       | TO8   |

| 0      |                 | 23:16    | TO23  | TO22  | TO21      | TO20   | TO19      | TO18       | TO17      | TO16  |

|        |                 | 31:24    | TO31  | TO30  | TO29      | TO28   | TO27      | TO26       | TO25      | TO24  |

|        |                 | 7:0      | CF7   | CF6   | CF5       | CF4    | CF3       | CF2        | CF1       | CF0   |

| 0xDC   | MCAN_TXBCF      | 15:8     | CF15  | CF14  | CF13      | CF12   | CF11      | CF10       | CF9       | CF8   |

|        |                 | 23:16    | CF23  | CF22  | CF21      | CF20   | CF19      | CF18       | CF17      | CF16  |

|        |                 | 31:24    | CF31  | CF30  | CF29      | CF28   | CF27      | CF26       | CF25      | CF24  |

| 0xE0   | MCAN_TXBTIE     | 7:0      | TIE7  | TIE6  | TIE5      | TIE4   | TIE3      | TIE2       | TIE1      | TIE0  |

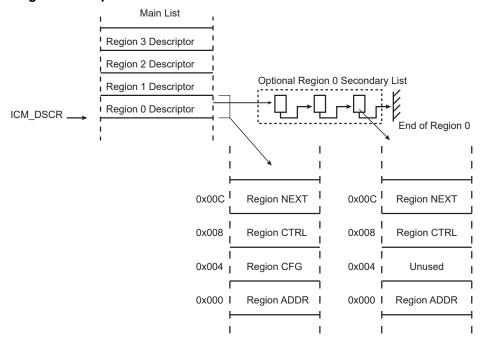

Figure 55-4. Region Descriptor

The figure below shows an example of the mandatory ICM settings required to monitor three memory data blocks of the system memory (defined as two regions) with one region being not contiguous (two separate areas) and one contiguous memory area. For each region, the SHA algorithm may be independently selected (different for each region). The wrap allows continuous monitoring.

## 59.4 Oscillator Characteristics

#### 59.4.1 32 kHz RC Oscillator Characteristics

## Table 59-18. 32 kHz RC Oscillator Characteristics

| Symbol             | Parameter           | Conditions         | Min | Тур | Max | Unit |

|--------------------|---------------------|--------------------|-----|-----|-----|------|

| f <sub>OSC</sub>   | Operating Frequency | _                  | 20  | 32  | 57  | kHz  |

| t <sub>START</sub> | Startup Time        | -                  | _   | _   | 120 | μs   |

| I <sub>DDON</sub>  | Current Consumption | After startup time | _   | 540 | _   | nA   |

#### 59.4.2 4/8/12 MHz RC Oscillator

The 4/8/12 MHz RC oscillator is calibrated in production. This calibration can be read through the Get CALIB Bit command (refer to 22. Enhanced Embedded Flash Controller (EEFC)) and the frequency can be trimmed by software through the PMC.

Table 59-19. 4/8/12 RC Oscillator Characteristics

| Symbol             | Parameter               | Conditions                                             | Min  | Тур  | Max  | Unit |

|--------------------|-------------------------|--------------------------------------------------------|------|------|------|------|

| ACC <sub>4</sub>   | 4 MHz Total Accuracy(2) | 4 MHz output selected (see <b>Note 1</b> )             | -35  | _    | 46   | %    |

|                    |                         | 4 MHz output selected at 25°C (see <b>Notes</b> 1, 3)  | -1.2 | _    | 0.8  | %    |

| ACC <sub>8</sub>   | 8 MHz Total Accuracy    | 8 MHz output selected at 25°C (see <b>Notes</b> 1, 3)  | -1.2 | _    | 0.8  | %    |

| ACC <sub>12</sub>  | 12 MHz Total Accuracy   | 12 MHz output selected at 25°C (see <b>Notes</b> 1, 3) | -1.6 | _    | 0.8  | %    |

|                    | Temp dependency         | (see Note 3)                                           | _    | 0.07 | 0.12 | %/°C |

| t <sub>START</sub> | Startup Time            | <del>-</del>                                           | _    | _    | 20   | μs   |

## Note:

- 1. Frequency range can be configured in the Supply Controller registers.

- 2. Not trimmed from factory.

- 3. After trimming at 25°C and VDDCORE = 1.2V.

## 59.4.3 32.768 kHz Crystal Oscillator Characteristics

## Table 59-20. 32.768 kHz Crystal Oscillator Characteristics

| Symbol                  | Parameter                        | Conditions         | Min | Тур | Max | Unit |

|-------------------------|----------------------------------|--------------------|-----|-----|-----|------|

| 1/(t <sub>CPXIN</sub> ) | XIN32 Clock Frequency            | (see Note)         | _   | _   | 32  | kHz  |

| t <sub>CHXIN</sub>      | XIN32 Clock High Half-<br>period | (see Note)         | 15  | _   | _   | ns   |

| t <sub>CLXIN</sub>      | XIN32 Clock Low Half-<br>period  | (see <b>Note</b> ) | 15  | _   | _   | ns   |

Table 59-55. QSPI Timings

| Symbol            | Parameter                                            | Conditions  | Min  | Max | Unit |

|-------------------|------------------------------------------------------|-------------|------|-----|------|

| QSPI <sub>0</sub> | QIOx data in to QSCK rising edge (input setup time)  | 3.3V domain | 2.5  | _   | ns   |

|                   |                                                      | 1.8V domain | 2.9  | _   | ns   |

| QSPI <sub>1</sub> | QIOx data in to QSCK rising edge (input hold time)   | 3.3V domain | 0    | _   | ns   |

|                   |                                                      | 1.8V domain | 0    | _   | ns   |

| QSPI <sub>2</sub> | QSCK rising edge to QIOx data out valid              | 3.3V domain | -1.3 | 1.9 | ns   |

|                   |                                                      | 1.8V domain | -2.5 | 3.0 | ns   |

| QSPI <sub>3</sub> | QIOx data in to QSCK falling edge (input setup time) | 3.3V domain | 2.9  | _   | ns   |

|                   |                                                      | 1.8V domain | 3.2  | _   | ns   |

| QSPI <sub>4</sub> | QIOx data in to QSCK falling edge(input hold time)   | 3.3V domain | 0    | _   | ns   |

|                   |                                                      | 1.8V domain | 0    | _   | ns   |

| QSPI <sub>5</sub> | QSCK falling edge to QIOx data out valid             | 3.3V domain | -1.6 | 1.8 | ns   |

|                   |                                                      | 1.8V domain | -2.7 | 3.1 | ns   |

Timings are given for the 3.3V domain, with VDDIO from 2.85V to 3.6V, maximum external capacitor = 40 pF.

## 59.13.1.6 SPI Characteristics

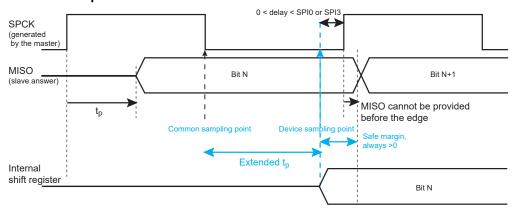

In the figures below, the MOSI line shifting edge is represented with a hold time equal to 0. However, it is important to note that for this device, the MISO line is sampled prior to the MOSI line shifting edge. As shown further below, the device sampling point extends the propagation delay  $(t_p)$  for slave and routing delays to more than half the SPI clock period, whereas the common sampling point allows only less than half the SPI clock period.

As an example, an SPI Slave working in Mode 0 can be safely driven if the SPI Master is configured in Mode 0.

Figure 59-19. MISO Capture in Master Mode

| Date | Changes                                                                             |

|------|-------------------------------------------------------------------------------------|

|      | - Section 63.1.1 "AFE Controller (AFEC)": "AFE max sampling frequency is 1.74 Msps" |

|      | - Section 63.2.1 "AFE Controller (AFEC)": "AFE max sampling frequency is 1.74 Msps" |

| End  |                                                                                     |

Table 62-3. SAM E70/S70/V70/V71 Datasheet Rev. 44003D - Revision History

| Date       | Comments                                                                                                                                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01-June-16 | "Introduction" AFE maximum sampling frequency now 1.7 Msps.                                                                                                                                                              |

|            | "Features" Main RC oscillator default frequency changed to 12 MHz.                                                                                                                                                       |

|            | AFE maximum sampling frequency now 1.7 Msps.                                                                                                                                                                             |

|            | Section 2. "Configuration Summary"  Table 2-1 "Configuration Summary": on QFN64 package, HS USB now supported.                                                                                                           |

|            | Table 4-1 "Signal Description List": updated 'Comments' column for for signals PCK0–PCK2, TRACECLK,, URXDx, Timer Counter - TC and for CANTXx. Added comment on Programmable Clock Output for PCK7 and on I2SC for GCLK. |

|            | Table 6-1 "144-lead Package Pinout": CANRX1 now shown as not available on PD28. Added signal type for I2SC signals. Updated notes (5) and (10).                                                                          |

|            | Table 6-2 "100-lead Package Pinout": Added signal type for I2SC signals. Updated notes (5) and (10).                                                                                                                     |

|            | Table 6-3 "64-lead LQFP Package Pinout": updated notes (4) and (9).                                                                                                                                                      |

|            | Section 7.2.1 "Powerup": updated equation for minimum VDDCORE slope.                                                                                                                                                     |

|            | Table 14-1 "Peripheral Identifiers": Added IDs 71, 72, 73.                                                                                                                                                               |

|            | Section 19. "Bus Matrix (MATRIX)" Section 19.1 "Description", Section 19.2 "Embedded Characteristics": number of masters changed to 13.                                                                                  |

|            | Table 19-1 "Bus Matrix Masters" and Table 19-3 "Master to Slave Access": added Master 12: Cortex-M7.                                                                                                                     |

|            | Table 19-3 "Master to Slave Access": changed access for Master 0/Slave 6.                                                                                                                                                |

|            | Added Section 19.3.6 "Configuration of Automatic Clock-off Mode".                                                                                                                                                        |

|            | Table 19-4 "Register Mapping": added register CCFG_DYNCFG at offset 0x011C and register CCFG_PCCR at offset 0x0118.                                                                                                      |

|            | Added Section 19.4.8 "Peripheral Clock Configuration Register".                                                                                                                                                          |

|            | Added Section 19.4.9 "Dynamic Clock Gating Register".                                                                                                                                                                    |

|            | Section 21. "Chip Identifier (CHIPID)" Updated Table 21-1 "SAM V71 Chip ID Registers". Added notes (1) and (2).                                                                                                          |