#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                                    |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                             |

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                | -                                                                                                  |

| RAM Size                   | 384K x 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-UFBGA                                                                                          |

| Supplier Device Package    | 144-UFBGA (6x6)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q20a-cfnt                        |

|                            |                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 37.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 590                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 3     | 37.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 591                                                                                                                  |

| 3     | 37.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 3     | 37.4.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 3     | 37.5.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| 38. ( | GMA                                                                                                                                                                   | AC - Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 640                                                                                                                  |

| 3     | 38.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 640                                                                                                                  |

| 3     | 38.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 640                                                                                                                  |

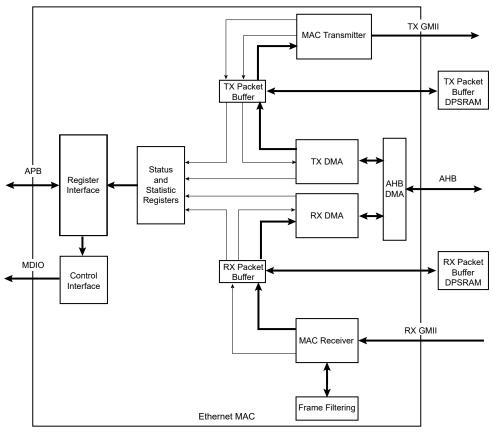

| 3     | 38.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 641                                                                                                                  |

| 3     | 38.4.                                                                                                                                                                 | Signal Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 641                                                                                                                  |

| 3     | 38.5.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 642                                                                                                                  |

| 3     | 38.6.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 642                                                                                                                  |

| 3     | 38.7.                                                                                                                                                                 | Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 673                                                                                                                  |

| 3     | 38.8.                                                                                                                                                                 | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 678                                                                                                                  |

| 30 I  | ISB                                                                                                                                                                   | High-Speed Interface (USBHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 831                                                                                                                  |

|       |                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

|       |                                                                                                                                                                       | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

|       |                                                                                                                                                                       | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

|       |                                                                                                                                                                       | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

|       |                                                                                                                                                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| 40. ł | High                                                                                                                                                                  | -Speed Multimedia Card Interface (HSMCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                                                                                                                 |

| 40. H | <b>-ligh</b><br>10.1.                                                                                                                                                 | n-Speed Multimedia Card Interface (HSMCI)<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                                                                                                                 |

| 40. H | High<br>10.1.<br>10.2.                                                                                                                                                | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>1042<br>1042                                                                                                 |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.                                                                                                                                       | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>1042<br>1042<br>1043                                                                                         |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.                                                                                                                              | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.                                                                                                                     | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.                                                                                                            | Description<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.                                                                                                   | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.<br>10.8.                                                                                          | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.7.<br>40.8.                                                                                          | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation                                                                                                                                                                                                                                                                                                                                                                                                          | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.                                                                        | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.5.<br>40.5.<br>40.7.<br>40.10<br>40.11                                                               | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation<br>HSMCI Boot Operation Mode                                                                                                                                                                                                                                                                                                            | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11.                                                              | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13                                                     | Description<br>Embedded Characteristics.<br>Block Diagram.<br>Application Block Diagram.<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation.<br>O. CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>Register Write Protection.                                                                                                                                                                                                                                                                                                               | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.13                                             | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br>5eria                           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>CE-ATA Operation Mode</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection</li> <li>Register Summary</li> </ul>                                                                                      |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.13<br>40.14<br><b>Seria</b><br>41.1.                    | <ul> <li>Speed Multimedia Card Interface (HSMCI).</li> <li>Description.</li> <li>Embedded Characteristics.</li> <li>Block Diagram.</li> <li>Application Block Diagram.</li> <li>Pin Name List.</li> <li>Product Dependencies.</li> <li>Bus Topology.</li> <li>High-Speed Multimedia Card Operations.</li> <li>SD/SDIO Card Operation.</li> <li>CE-ATA Operation.</li> <li>HSMCI Boot Operation Mode.</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection.</li> <li>Register Summary.</li> <li>al Peripheral Interface (SPI).</li> </ul>                                                               |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> </ul>                                                          | 1042<br>1042<br>1043<br>1043<br>1043<br>1044<br>1044<br>1044<br>1044<br>1055<br>1055<br>1059<br>1095<br>1095<br>1095 |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.<br>41.2.<br>41.3. | A-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics.<br>Block Diagram<br>Application Block Diagram<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation<br>O. CE-ATA Operation.<br>CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>HSMCI Boot Operation Mode<br>Register Write Protection<br>Register Summary.<br>al Peripheral Interface (SPI)<br>Description<br>Embedded Characteristics.                                                                                                                  |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br>41.1.<br>41.2.<br>41.3.<br>41.3.                 | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> </ul> |                                                                                                                      |

## Real-time Clock (RTC)

| Ī | Value | Name        | Description                                                |

|---|-------|-------------|------------------------------------------------------------|

|   | 0     | NO_TIMEVENT | No time event has occurred since the last clear.           |

|   | 1     | TIMEVENT    | At least one time event has occurred since the last clear. |

### Bit 2 – SEC Second Event

| Value | Name        | Description                                                  |

|-------|-------------|--------------------------------------------------------------|

| 0     | NO_SECEVENT | No second event has occurred since the last clear.           |

| 1     | SECEVENT    | At least one second event has occurred since the last clear. |

### Bit 1 – ALARM Alarm Flag

| Value | Name          | Description                               |

|-------|---------------|-------------------------------------------|

| 0     | NO_ALARMEVENT | No alarm matching condition occurred.     |

| 1     | ALARMEVENT    | An alarm matching condition has occurred. |

### Bit 0 – ACKUPD Acknowledge for Update

| Value | Name    | Description                                    |

|-------|---------|------------------------------------------------|

| 0     | FREERUN | Time and calendar registers cannot be updated. |

| 1     | UPDATE  | Time and calendar registers can be updated.    |

## DMA Controller (XDMAC)

| 055        | News          | D'4 D    |        |         |       |        |                  |        |            |        |

|------------|---------------|----------|--------|---------|-------|--------|------------------|--------|------------|--------|

| Offset     | Name          | Bit Pos. |        |         |       |        |                  |        |            |        |

|            |               | 15:8     |        |         |       |        | [13:6]           |        |            |        |

|            |               | 23:16    |        |         |       |        | 21:14]           |        |            |        |

|            |               | 31:24    |        |         |       |        | 29:22]           |        |            |        |

|            |               | 7:0      |        |         |       | NDVIE  | W[1:0]           | NDDUP  | NDSUP      | NDE    |

| 0x02EC     | XDMAC_CNDC10  | 15:8     |        |         |       |        |                  |        |            |        |

|            |               | 23:16    |        |         |       |        |                  |        |            |        |

|            |               | 31:24    |        |         |       |        |                  |        |            |        |

|            |               | 7:0      |        |         |       |        | N[7:0]           |        |            |        |

| 0x02F0     | XDMAC_CUBC10  | 15:8     |        |         |       |        | N[15:8]          |        |            |        |

|            |               | 23:16    |        |         |       | UBLEN  | <b>I</b> [23:16] |        |            |        |

|            |               | 31:24    |        |         |       |        | 177.03           |        |            |        |

|            |               | 7:0      |        |         |       | BLE    | N[7:0]           |        |            |        |

| 0x02F4     | XDMAC_CBC10   | 15:8     |        |         |       |        |                  | BLEI   | N[11:8]    |        |

|            |               | 23:16    |        |         |       |        |                  |        |            |        |

|            |               | 31:24    | MEMOET | 014/050 |       | DOVANO |                  | MDO    | 7514 01    | 7)/05  |

|            |               | 7:0      | MEMSET | SWREQ   | 015   | DSYNC  | TUTA-01          | MBSI   | ZE[1:0]    | TYPE   |

| 0x02F8     | XDMAC_CC10    | 15:8     |        | DIF     | SIF   | DVVID  | TH[1:0]          | 414.03 | CSIZE[2:0] | 14.01  |

|            |               | 23:16    | WRIP   | RDIP    | INITD |        |                  | 1[1:0] | SAN        | I[1:0] |

|            |               | 31:24    |        |         |       | 000 1  | PERID[6:0]       |        |            |        |

|            |               | 7:0      |        |         |       |        | ISP[7:0]         |        |            |        |

| 0x02FC     | XDMAC_CDS_MSP | 15:8     |        |         |       |        | SP[15:8]         |        |            |        |

|            | 10            | 23:16    |        |         |       |        | ISP[7:0]         |        |            |        |

|            |               | 31:24    |        |         |       |        | SP[15:8]         |        |            |        |

|            |               | 7:0      |        |         |       |        | S[7:0]           |        |            |        |

| 0x0300     | XDMAC_CSUS10  | 15:8     |        |         |       |        | S[15:8]          |        |            |        |

|            |               | 23:16    |        |         |       | 2082   | [23:16]          |        |            |        |

|            |               | 31:24    |        |         |       | DUD    | 0[7:0]           |        |            |        |

|            |               | 7:0      |        |         |       |        | S[7:0]           |        |            |        |

| 0x0304     | XDMAC_CDUS10  | 15:8     |        |         |       |        | 6[15:8]          |        |            |        |

|            |               | 23:16    |        |         |       | DOBS   | [23:16]          |        |            |        |

| 0,0200     |               | 31:24    |        |         |       |        |                  |        |            |        |

| 0x0308     | Reserved      |          |        |         |       |        |                  |        |            |        |

| <br>0x030F | Reserved      |          |        |         |       |        |                  |        |            |        |

| 0,0000     |               | 7:0      |        | ROIE    | WBIE  | RBIE   | FIE              | DIE    | LIE        | BIE    |

|            |               | 15:8     |        | ROIL    | WDIE  | INDIE  | 1 12             | DIL    |            | DIL    |

| 0x0310     | XDMAC_CIE11   | 23:16    |        |         |       |        |                  |        |            |        |

|            |               | 31:24    |        |         |       |        |                  |        |            |        |

|            |               | 7:0      |        | ROID    | WBEID | RBEID  | FID              | DID    | LID        | BID    |

|            |               | 15:8     |        | NOID    |       |        |                  |        |            | UIU    |

| 0x0314     | XDMAC_CID11   | 23:16    |        |         |       |        |                  |        |            |        |

|            |               | 31:24    |        |         |       |        |                  |        |            |        |

|            |               | 7:0      |        | ROIM    | WBEIM | RBEIM  | FIM              | DIM    | LIM        | BIM    |

|            |               | 15:8     |        |         |       |        |                  |        |            |        |

| 0x0318     | XDMAC_CIM11   | 23:16    |        |         |       |        |                  |        |            |        |

|            |               | 31:24    |        |         |       |        |                  |        |            |        |

|            |               | 31.24    |        |         |       |        |                  |        |            |        |

## SAM E70/S70/V70/V71 Family DMA Controller (XDMAC)

|        | Name:<br>Offset:<br>Reset:<br>Property: | XDMAC_GRW<br>0x34<br>–<br>Write-only | /R    |       |       |       |       |       |

|--------|-----------------------------------------|--------------------------------------|-------|-------|-------|-------|-------|-------|

| Bit    | 31                                      | 30                                   | 29    | 28    | 27    | 26    | 25    | 24    |

|        |                                         |                                      |       |       |       |       |       |       |

| Access |                                         |                                      |       |       |       |       |       |       |

| Reset  |                                         |                                      |       |       |       |       |       |       |

| Bit    | 23                                      | 22                                   | 21    | 20    | 19    | 18    | 17    | 16    |

|        | RWR23                                   | RWR22                                | RWR21 | RWR20 | RWR19 | RWR18 | RWR17 | RWR16 |

| Access | W                                       | W                                    | W     | W     | W     | W     | W     | W     |

| Reset  | -                                       | -                                    | -     | -     | -     | -     | -     | -     |

| Bit    | 15                                      | 14                                   | 13    | 12    | 11    | 10    | 9     | 8     |

|        | RWR15                                   | RWR14                                | RWR13 | RWR12 | RWR11 | RWR10 | RWR9  | RWR8  |

| Access | W                                       | W                                    | W     | W     | W     | W     | W     | W     |

| Reset  | -                                       | _                                    | _     | _     | -     | _     | -     | _     |

|        |                                         |                                      |       |       |       |       |       |       |

| Bit    | 7                                       | 6                                    | 5     | 4     | 3     | 2     | 1     | 0     |

|        | RWR7                                    | RWR6                                 | RWR5  | RWR4  | RWR3  | RWR2  | RWR1  | RWR0  |

| Access | W                                       | W                                    | W     | W     | W     | W     | W     | W     |

| Reset  | -                                       | -                                    | _     | _     | -     | _     | -     | _     |

### 36.9.14 XDMAC Global Channel Read Write Resume Register

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23 – RWRx XDMAC Channel x Read Write Resume

| Value | Description                           |

|-------|---------------------------------------|

| 0     | No effect.                            |

| 1     | Read and write requests are serviced. |

As described above, the DMA can be programmed into a low latency mode, known as Partial Store and Forward. For further details of this mode, see the related Links.

When the DMA is in full store and forward mode, full packets are buffered which provides the possibility to:

- Discard packets with error on the receive path before they are partially written out of the DMA, thus saving AHB bus bandwidth and driver processing overhead,

- Retry collided transmit frames from the buffer, thus saving AHB bus bandwidth,

- Implement transmit IP/TCP/UDP checksum generation offload.

With the packet buffers included, the structure of the GMAC data paths is shown in this image:

Figure 38-2. Data Paths with Packet Buffers Included

### 38.6.3.7 Transmit Packet Buffer

The transmitter packet buffer will continue attempting to fetch frame data from the AHB system memory until the packet buffer itself is full, at which point it will attempt to maintain its full level.

To accommodate the status and statistics associated with each frame, three words per packet (or two if the GMAC is configured in 64-bit data path mode) are reserved at the end of the packet data. If the packet is bad and requires to be dropped, the status and statistics are the only information held on that packet. Storing the status in the DPRAM is required in order to decouple the DMA interface of the buffer from the MAC interface, to update the MAC status/statistics and to generate interrupts in the order in which the packets that they represent were fetched from the AHB memory.

If any errors occur on the AHB while reading the transmit frame, the fetching of packet data from AHB memory is halted. The MAC transmitter will continue to fetch packet data, thereby emptying the packet

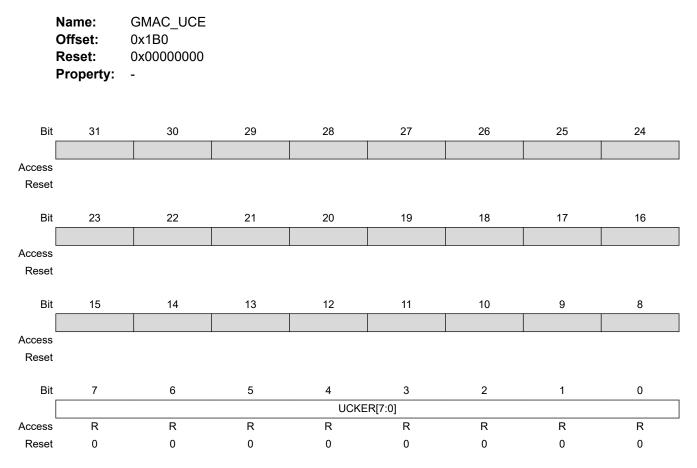

### 38.8.82 GMAC UDP Checksum Errors Register

### Bits 7:0 - UCKER[7:0] UDP Checksum Errors

This register counts the number of frames discarded due to an incorrect UDP checksum, but are between 64 and 1518 Bytes (1536 Bytes if GMAC\_NCFGR.MAXFS=1) and do not have a CRC error, an alignment error, nor a symbol error.

## High-Speed Multimedia Card Interface (HSMCI)

| Value | Description                   |

|-------|-------------------------------|

| 0     | Disables Force Byte Transfer. |

| 1     | Enables Force Byte Transfer.  |

### Bit 12 – WRPROOF Write Proof Enable

Enabling Write Proof allows to stop the HSMCI Clock during write access if the internal FIFO is full. This will guarantee data integrity, not bandwidth.

| Value | Description           |

|-------|-----------------------|

| 0     | Disables Write Proof. |

| 1     | Enables Write Proof.  |

### Bit 11 – RDPROOF Read Proof Enable

Enabling Read Proof allows to stop the HSMCI Clock during read access if the internal FIFO is full. This will guarantee data integrity, not bandwidth.

| Value | Description          |

|-------|----------------------|

| 0     | Disables Read Proof. |

| 1     | Enables Read Proof.  |

### Bits 10:8 – PWSDIV[2:0] Power Saving Divider

High Speed MultiMedia Card Interface clock is divided by 2<sup>(PWSDIV)</sup> + 1 when entering Power Saving Mode.

| A WARNING | This value must be different from 0 before enabling the Power Save Mode in the HSMCI_CR |

|-----------|-----------------------------------------------------------------------------------------|

|           | (PWSEN bit).                                                                            |

### Bits 7:0 - CLKDIV[7:0] Clock Divider

High Speed MultiMedia Card Interface clock (MCCK or HSMCI\_CK) is Master Clock (MCK) divided by 2 × CLKDIV + CLKODD + 2.

### Serial Peripheral Interface (SPI)

| Value | Description                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

| 0     | As soon as data is written in SPI_TDR.                                                                                           |

| 1     | SPI_TDR and internal shift register are empty. If a transfer delay has been defined, TXEMPTY is set after the end of this delay. |

Bit 8 – NSSR NSS Rising (cleared on read)

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | No rising edge detected on NSS pin since the last read of SPI_SR. |

| 1     | A rising edge occurred on NSS pin since the last read of SPI_SR.  |

### Bit 3 – OVRES Overrun Error Status (cleared on read)

An overrun occurs when SPI\_RDR is loaded at least twice from the internal shift register since the last read of SPI\_RDR.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | No overrun has been detected since the last read of SPI_SR. |

| 1     | An overrun has occurred since the last read of SPI_SR.      |

**Bit 2 – MODF** Mode Fault Error (cleared on read)

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | No mode fault has been detected since the last read of SPI_SR. |

| 1     | A mode fault occurred since the last read of SPI_SR.           |

**Bit 1 – TDRE** Transmit Data Register Empty (cleared by writing SPI\_TDR)

0: Data has been written to SPI\_TDR and not yet transferred to the internal shift register.

1: The last data written in SPI\_TDR has been transferred to the internal shift register.

TDRE is cleared when the SPI is disabled or at reset. Enabling the SPI sets the TDRE flag.

**Bit 0 – RDRF** Receive Data Register Full (cleared by reading SPI\_RDR)

0: No data has been received since the last read of SPI\_RDR.

1: Data has been received and the received data has been transferred from the internal shift register to SPI\_RDR since the last read of SPI\_RDR.

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.24 USART Receiver Timeout Register

| Name:     | US_RTOR    |  |  |  |  |

|-----------|------------|--|--|--|--|

| Offset:   | 0x0024     |  |  |  |  |

| Reset:    | 0x0        |  |  |  |  |

| Property: | Read/Write |  |  |  |  |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27    | 26  | 25  | 24        |

|--------|-----|-----|-----|-----|-------|-----|-----|-----------|

|        |     |     |     |     |       |     |     |           |

| Access |     |     |     |     |       |     |     |           |

| Reset  |     |     |     |     |       |     |     |           |

|        |     |     |     |     |       |     |     |           |

| Bit    | 23  | 22  | 21  | 20  | 19    | 18  | 17  | 16        |

|        |     |     |     |     |       |     |     | TO[16:16] |

| Access |     | •   |     |     |       |     |     | R/W       |

| Reset  |     |     |     |     |       |     |     | 0         |

|        |     |     |     |     |       |     |     |           |

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9   | 8         |

|        |     |     |     | TO  | 15:8] |     |     |           |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W       |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0         |

|        |     |     |     |     |       |     |     |           |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0         |

|        |     |     |     | TO  | 7:0]  |     |     |           |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W       |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0         |

### Bits 16:0 - TO[16:0] Timeout Value

| Value   | Description                                                           |

|---------|-----------------------------------------------------------------------|

| 0       | The receiver timeout is disabled.                                     |

| 1-65535 | The receiver timeout is enabled and TO is Timeout Delay / Bit Period. |

| 1-      | The receiver timeout is enabled and TO is Timeout Delay / Bit Period. |

| 131071  |                                                                       |

### **Controller Area Network (MCAN)**

### 49.5.6 FIFO Acknowledge Handling

The Get Indices of Rx FIFO 0, Rx FIFO 1, and the Tx Event FIFO are controlled by writing to the corresponding FIFO Acknowledge Index in the registers MCAN\_RXF0A, MCAN\_RXF1A and MCAN\_TXEFA. Writing to the FIFO Acknowledge Index will set the FIFO Get Index to the FIFO Acknowledge Index plus one and thereby updates the FIFO Fill Level. There are two use cases:

When only a single element has been read from the FIFO (the one being pointed to by the Get Index), this Get Index value is written to the FIFO Acknowledge Index.

When a sequence of elements has been read from the FIFO, it is sufficient to write the FIFO Acknowledge Index only once at the end of that read sequence (value: Index of the last element read), to update the FIFO's Get Index.

Due to the fact that the processor has free access to the MCAN's Message RAM, special care has to be taken when reading FIFO elements in an arbitrary order (Get Index not considered). This might be useful when reading a High Priority Message from one of the two Rx FIFOs. In this case the FIFO's Acknowledge Index should not be written because this would set the Get Index to a wrong position and also alters the FIFO's Fill Level. In this case some of the older FIFO elements would be lost.

**Note:** The application has to ensure that a valid value is written to the FIFO Acknowledge Index. The MCAN does not check for erroneous values.

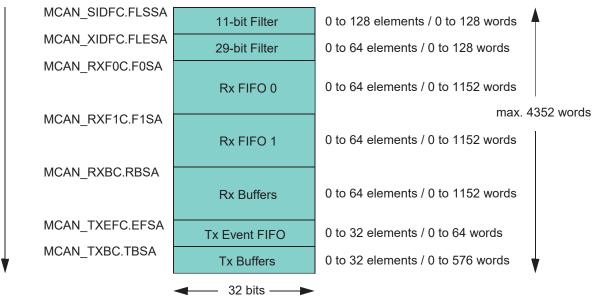

### 49.5.7 Message RAM

### 49.5.7.1 Message RAM Configuration

The Message RAM has a width of 32 bits. The MCAN module can be configured to allocate up to 4352 words in the Message RAM. It is not necessary to configure each of the sections listed in the figure below, nor is there any restriction with respect to the sequence of the sections.

When operated in CAN FD mode, the required Message RAM size depends on the element size configured for Rx FIFO0, Rx FIFO1, Rx Buffers, and Tx Buffers via MCAN\_RXESC.F0DS, MCAN\_RXESC.F1DS, MCAN\_RXESC.RBDS, and MCAN\_TXESC.TBDS.

### Figure 49-12. Message RAM Configuration

Start Address

## **Controller Area Network (MCAN)**

| Value | Name      | Description                        |

|-------|-----------|------------------------------------|

| 2     | DOMINANT  | Dominant ('0') level at pin CANTX. |

| 3     | RECESSIVE | Recessive ('1') at pin CANTX.      |

Bit 4 – LBCK Loop Back Mode (read/write)

0 (DISABLED): Reset value. Loop Back mode is disabled.

1 (ENABLED): Loop Back mode is enabled (see Test Modes).

## Pulse Width Modulation Controller (PWM)

- Independent Clock Selection for Each Channel

- Independent Period, Duty-Cycle and Dead-Time for Each Channel

- Independent Double Buffering of Period, Duty-Cycle and Dead-Times for Each Channel

- Independent Programmable Selection of The Output Waveform Polarity for Each Channel, with Double Buffering

- Independent Programmable Center- or Left-aligned Output Waveform for Each Channel

- Independent Output Override for Each Channel

- Independent Interrupt for Each Channel, at Each Period for Left-Aligned or Center-Aligned Configuration

- Independent Update Time Selection of Double Buffering Registers (Polarity, Duty Cycle) for Each Channel, at Each Period for Left-Aligned or Center-Aligned Configuration

- External Trigger Input Management (e.g., for DC/DC or Lighting Control)

- External PWM Reset Mode

- External PWM Start Mode

- Cycle-By-Cycle Duty Cycle Mode

- Leading-Edge Blanking

- 2 2-bit Gray Up/Down Channels for Stepper Motor Control

- Spread Spectrum Counter to Allow a Constantly Varying Duty Cycle (only for Channel 0)

- Synchronous Channel Mode

- Synchronous Channels Share the Same Counter

- Mode to Update the Synchronous Channels Registers after a Programmable Number of Periods

- Synchronous Channels Supports Connection of one DMA Controller Channel Which Offers Buffer Transfer Without Processor Intervention To Update Duty-Cycle Registers

- 2 Independent Events Lines Intended to Synchronize ADC Conversions

- Programmable delay for Events Lines to delay ADC measurements

- 8 Comparison Units Intended to Generate Interrupts, Pulses on Event LinesDMA Controller Transfer Requests

- 8 Programmable Fault Inputs Providing an Asynchronous Protection of PWM Outputs

- 3 User Driven through PIO Inputs

- PMC Driven when Crystal Oscillator Clock Fails

- ADC Controller Driven through Configurable Comparison Function

- Analog Comparator Controller Driven

- Timer/Counter Driven through Configurable Comparison Function

- Register Write Protection

## Pulse Width Modulation Controller (PWM)

### 51.7.33 PWM Fault Protection Value Register 2

| Name:     | PWM_FPV2   |  |  |  |  |

|-----------|------------|--|--|--|--|

| Offset:   | 0xC0       |  |  |  |  |

| Reset:    | 0x000F000F |  |  |  |  |

| Property: | Read/Write |  |  |  |  |

This register can only be written if bits WPSWS5 and WPHWS5 are cleared in the PWM Write Protection Status Register.

| Bit    | 31 | 30 | 29 | 28 | 27    | 26    | 25    | 24    |

|--------|----|----|----|----|-------|-------|-------|-------|

|        |    |    |    |    |       |       |       |       |

| Access |    |    | •  |    |       |       |       |       |

| Reset  |    |    |    |    |       |       |       |       |

|        |    |    |    |    |       |       |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19    | 18    | 17    | 16    |

|        |    |    |    |    | FPZL3 | FPZL2 | FPZL1 | FPZL0 |

| Access |    |    |    |    | R/W   | R/W   | R/W   | R/W   |

| Reset  |    |    |    |    | 1     | 1     | 1     | 1     |

|        |    |    |    |    |       |       |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11    | 10    | 9     | 8     |

|        |    |    |    |    |       |       |       |       |

| Access |    |    |    |    |       |       |       |       |

| Reset  |    |    |    |    |       |       |       |       |

|        |    |    |    |    |       |       |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3     | 2     | 1     | 0     |

|        |    |    |    |    | FPZH3 | FPZH2 | FPZH1 | FPZH0 |

| Access |    |    |    |    | R/W   | R/W   | R/W   | R/W   |

| Reset  |    |    |    |    | 1     | 1     | 1     | 1     |

### Bits 16, 17, 18, 19 – FPZLx Fault Protection to Hi-Z for PWML output on channel x

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | When fault occurs, PWML output of channel x is forced to value defined by the bit FPVLx in |

|       | PWM Fault Protection Value Register 1.                                                     |

| 1     | When fault occurs, PWML output of channel x is forced to high-impedance state.             |

### Bits 0, 1, 2, 3 – FPZHx Fault Protection to Hi-Z for PWMH output on channel x

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | When fault occurs, PWMH output of channel x is forced to value defined by the bit FPVHx in |

|       | PWM Fault Protection Value Register 1.                                                     |

| 1     | When fault occurs, PWMH output of channel x is forced to high-impedance state.             |

### 51.7.43 PWM Channel Period Register

| Name:     | PWM_CPRDx              |

|-----------|------------------------|

| Offset:   | 0x020C + x*0x20 [x=03] |

| Reset:    | 0x0000000              |

| Property: | Read/Write             |

This register can only be written if bits WPSWS3 and WPHWS3 are cleared in the PWM Write Protection Status Register.

Only the first 16 bits (channel counter size) are significant.

| Bit    | 31        | 30  | 29  | 28   | 27      | 26  | 25  | 24  |

|--------|-----------|-----|-----|------|---------|-----|-----|-----|

|        |           |     |     |      |         |     |     |     |

| Access |           |     |     |      |         |     |     |     |

| Reset  |           |     |     |      |         |     |     |     |

|        |           |     |     |      |         |     |     |     |

| Bit    | 23        | 22  | 21  | 20   | 19      | 18  | 17  | 16  |

|        |           |     |     | CPRD | [23:16] |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |           |     |     |      |         |     |     |     |

| Bit    | 15        | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|        |           |     |     | CPRD | [15:8]  |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |           |     |     |      |         |     |     |     |

| Bit    | 7         | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        | CPRD[7:0] |     |     |      |         |     |     |     |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

| Reset  | 0         | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

### Bits 23:0 - CPRD[23:0] Channel Period

If the waveform is left-aligned, then the output waveform period depends on the channel counter source clock and can be calculated:

- By using the PWM peripheral clock divided by a given prescaler value "X" (where  $X = 2^{PREA}$  is 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, or 1024). The resulting period formula is:

$(X \times CPRD)$

$f_{

m peripheral\, clock}$

– By using the PWM peripheral clock divided by a given prescaler value "X" (see above) and by either the DIVA or the DIVB divider. The formula becomes, respectively:

$$(X \times CPRD \times DIVA)$$

or  $(X \times CPRD \times DIVB)$

$f_{\text{peripheral clock}}$   $f_{\text{peripheral clock}}$

If the waveform is center-aligned, then the output waveform period depends on the channel counter source clock and can be calculated:

## Digital-to-Analog Converter Controller (DACC)

### 53.7.12 DACC Analog Current Register

| Name:     | DACC_ACR   |

|-----------|------------|

| Offset:   | 0x94       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the DACC Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28 | 27     | 26  | 25  | 24       |

|--------|----|----|----|----|--------|-----|-----|----------|

|        |    |    |    |    |        |     |     |          |

| Access |    |    |    |    |        | -   |     |          |

| Reset  |    |    |    |    |        |     |     |          |

|        |    |    |    |    |        |     |     |          |

| Bit    | 23 | 22 | 21 | 20 | 19     | 18  | 17  | 16       |

|        |    |    |    |    |        |     |     |          |

| Access |    |    |    |    |        |     |     |          |

| Reset  |    |    |    |    |        |     |     |          |

|        |    |    |    |    |        |     |     |          |

| Bit    | 15 | 14 | 13 | 12 | 11     | 10  | 9   | 8        |

|        |    |    |    |    |        |     |     |          |

| Access |    |    |    |    |        |     |     |          |

| Reset  |    |    |    |    |        |     |     |          |

|        |    |    |    |    |        |     |     | _        |

| Bit    | 7  | 6  | 5  | 4  | 3      | 2   | 1   | 0        |

|        |    |    |    |    | IBCTLC |     |     | CH0[1:0] |

| Access |    |    |    |    | R/W    | R/W | R/W | R/W      |

| Reset  |    |    |    |    | 0      | 0   | 0   | 0        |

### Bits 0:1, 2:3 – IBCTLCHx Analog Output Current Control

Allows to adapt the slew rate of the analog output. For more details, refer to the DAC Characteristics in the section "Electrical Characteristics" of this datasheet.

### **Related Links**

58. Electrical Characteristics for SAM V70/V71

## True Random Number Generator (TRNG)

|                 | Name:<br>Offset:<br>Reset:<br>Property: | TRNG_IDR<br>0x14<br>–<br>Write-only |    |    |    |    |    |        |

|-----------------|-----------------------------------------|-------------------------------------|----|----|----|----|----|--------|

| Bit             | 31                                      | 30                                  | 29 | 28 | 27 | 26 | 25 | 24     |

| Access<br>Reset |                                         |                                     |    |    |    |    |    |        |

| Bit             | 23                                      | 22                                  | 21 | 20 | 19 | 18 | 17 | 16     |

| Access<br>Reset |                                         |                                     |    |    |    |    |    |        |

| Bit             | 15                                      | 14                                  | 13 | 12 | 11 | 10 | 9  | 8      |

| Access<br>Reset |                                         |                                     |    |    |    |    |    |        |

| Bit             | 7                                       | 6                                   | 5  | 4  | 3  | 2  | 1  | 0      |

|                 |                                         |                                     |    |    |    |    |    | DATRDY |

| Access<br>Reset |                                         |                                     |    |    |    |    |    | W<br>_ |

### 56.6.3 TRNG Interrupt Disable Register

Bit 0 – DATRDY Data Ready Interrupt Disable

| Value | Description                           |

|-------|---------------------------------------|

| 0     | No effect.                            |

| 1     | Disables the corresponding interrupt. |

### 57.5.12 AES Plaintext/Ciphertext Length Register

| Name:     | AES_CLENR  |

|-----------|------------|

| Offset:   | 0x74       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |