Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                | -                                                                                                  |

| RAM Size                   | 384K x 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-LFBGA                                                                                          |

| Supplier Device Package    | 144-LFBGA (10x10)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q20a-cnt                         |

|                            |                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Bit 1 – SMC\_NFCS1 SMC NAND Flash Chip Select 1 Assignment

$\widehat{\mathbf{M}}$  WARNING This bit must not be used if SDRAMEN is set.

| Valu | le Description                                                             |

|------|----------------------------------------------------------------------------|

| 0    | NCS1 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS1). |

| 1    | NCS1 is assigned to a NAND Flash (NANDOE and NANWE used for NCS1).         |

## Bit 0 - SMC\_NFCS0 SMC NAND Flash Chip Select 0 Assignment

| Value | Description                                                                |

|-------|----------------------------------------------------------------------------|

| 0     | NCS0 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS0). |

| 1     | NCS0 is assigned to a NAND Flash (NANDOE and NANWE used for NCS0).         |

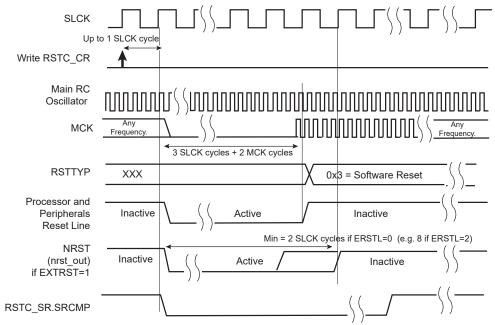

The internal reset signals are asserted as soon as the register write is performed. This is detected on the Master Clock (MCK). They are released when the software reset has ended, i.e., synchronously to SLCK.

If EXTRST is written to '1', the nrst\_out signal is asserted depending on the configuration of RSTC\_MR.ERSTL. However, the resulting falling edge on NRST does not lead to a user reset.

If and only if the RSTC\_CR.PROCRST is written to '1', the RSTC reports the software status in field RSTC\_SR.RSTTYP. Other software resets are not reported in RSTTYP.

As soon as a software operation is detected, RSTC\_SR.SRCMP is written to '1'. SRCMP is cleared at the end of the software reset. No other software reset can be performed while SRCMP is written to '1', and writing any value in the RSTC\_CR has no effect.

### Figure 26-5. Software Reset Timing Diagram

### 26.4.3.5 User Reset

A user reset is generated when a low level is detected on the NRST pin and RSTC\_MR.URSTEN is at '1'. The NRST input signal is resynchronized with SLCK to ensure proper behavior of the system. Thus, the NRST pin must be asserted for at least 1 SLCK clock cycle to ensure execution of a user reset.

The user reset is triggered 2 SLCK cycles after a low level is detected on NRST. The processor reset and the peripheral reset are asserted.

The user reset ends when NRST rises, after a two-cycle resynchronization time and a three-cycle processor startup. The processor clock is reenabled as soon as NRST is confirmed high.

When the processor reset signal is released, RSTC\_SR.RSTTYP is loaded with the value '4', indicating a user reset.

The NRST manager guarantees that the NRST line is asserted for External Reset Length SLCK cycles, as configured in RSTC\_MR.ERSTL. However, if NRST does not rise after External Reset Length because it is driven low externally, the internal reset lines remain asserted until NRST actually rises.

# Parallel Input/Output Controller (PIO)

|        | Name:<br>Offset:<br>Reset:<br>Property: | PIO_SCDR<br>0x008C<br>0x00000000<br>Read/Write |    |    |       |       |                                       |    |

|--------|-----------------------------------------|------------------------------------------------|----|----|-------|-------|---------------------------------------|----|

| Bit    | 31                                      | 30                                             | 29 | 28 | 27    | 26    | 25                                    | 24 |

|        |                                         |                                                |    |    |       |       |                                       |    |

| Access |                                         |                                                |    |    |       |       |                                       |    |

| Reset  |                                         |                                                |    |    |       |       |                                       |    |

|        |                                         |                                                |    |    |       |       |                                       |    |

| Bit    | 23                                      | 22                                             | 21 | 20 | 19    | 18    | 17                                    | 16 |

|        |                                         |                                                |    |    |       |       |                                       |    |

| Access |                                         |                                                |    |    |       |       |                                       |    |

| Reset  |                                         |                                                |    |    |       |       |                                       |    |

| Bit    | 15                                      | 14                                             | 13 | 12 | 11    | 10    | 9                                     | 0  |

| DIL    | 15                                      | 14                                             | 13 | 12 |       | 13:8] | 9                                     | 8  |

| Access |                                         |                                                |    |    | טוען  | 13.0] |                                       |    |

| Reset  |                                         |                                                | 0  | 0  | 0     | 0     | 0                                     | 0  |

| Reset  |                                         |                                                | 0  | 0  | 0     | 0     | 0                                     | 0  |

| Bit    | 7                                       | 6                                              | 5  | 4  | 3     | 2     | 1                                     | 0  |

|        | _                                       |                                                |    |    | [7:0] |       | · · · · · · · · · · · · · · · · · · · | -  |

| Access | <u> </u>                                |                                                |    |    |       |       |                                       |    |

| Reset  |                                         | 0                                              | 0  | 0  | 0     | 0     | 0                                     | 0  |

|        |                                         |                                                |    |    |       |       |                                       |    |

### 32.6.1.29 PIO Slow Clock Divider Debouncing Register

**Bits 13:0 – DIV[13:0]** Slow Clock Divider Selection for Debouncing  $t_{div slck} = ((DIV + 1) \times 2) \times t_{slck}$

## Parallel Input/Output Controller (PIO)

### 32.6.1.40 PIO Level Select Register

|        | Name:<br>Offset:<br>Property: | PIO_LSR<br>0x00C4<br>Write-only |     |     |     |     |     |     |

|--------|-------------------------------|---------------------------------|-----|-----|-----|-----|-----|-----|

|        |                               |                                 |     |     |     |     |     |     |

| Bit    |                               | 30                              | 29  | 28  | 27  | 26  | 25  | 24  |

|        | P31                           | P30                             | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |                               |                                 |     |     |     |     |     |     |

| Reset  |                               |                                 |     |     |     |     |     |     |

| Bit    | 23                            | 22                              | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23                           | P22                             | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |                               |                                 |     |     | •   |     |     |     |

| Reset  |                               |                                 |     |     |     |     |     |     |

|        |                               |                                 |     |     |     |     |     |     |

| Bit    | 15                            | 14                              | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15                           | P14                             | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |                               |                                 |     |     |     |     |     |     |

| Reset  |                               |                                 |     |     |     |     |     |     |

| Bit    | 7                             | 6                               | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7                            | P6                              | P5  | P4  | P3  | P2  | P1  | P0  |

| Access | <u>L</u>                      | 1                               | 1   | 1   | 1   | 1   | 1   | I]  |

| Reset  |                               |                                 |     |     |     |     |     |     |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Level Interrupt Selection

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | No effect.                                       |

| 1     | The interrupt source is a level-detection event. |

### Static Memory Controller (SMC)

#### 35.16.1.2 SMC Pulse Register

Name:

SMC\_PULSE[0..3]

Offset:

0x00

Reset:

0

Property:

R/W

This register can only be written if the WPEN bit is cleared in the "SMC Write Protection Mode Register" .

| Bit    | 31 | 30             | 29                | 28 | 27            | 26   | 25 | 24 |

|--------|----|----------------|-------------------|----|---------------|------|----|----|

|        |    |                |                   | NC | S_RD_PULSE[6  | 5:0] |    |    |

| Access |    |                |                   |    |               |      |    |    |

| Reset  |    | 0              | 0                 | 0  | 0             | 0    | 0  | 0  |

|        |    |                |                   |    |               |      |    |    |

| Bit    | 23 | 22             | 21                | 20 | 19            | 18   | 17 | 16 |

|        |    |                |                   |    | NRD_PULSE[6:0 | ]    |    |    |

| Access |    |                |                   |    |               |      |    |    |

| Reset  |    | 0              | 0                 | 0  | 0             | 0    | 0  | 0  |

|        |    |                |                   |    |               |      |    |    |

| Bit    | 15 | 14             | 13                | 12 | 11            | 10   | 9  | 8  |

|        |    |                | NCS_WR_PULSE[6:0] |    |               |      |    |    |

| Access |    |                |                   |    |               |      |    |    |

| Reset  |    | 0              | 0                 | 0  | 0             | 0    | 0  | 0  |

|        |    |                |                   |    |               |      |    |    |

| Bit    | 7  | 6              | 5                 | 4  | 3             | 2    | 1  | 0  |

|        |    | NWE_PULSE[6:0] |                   |    |               |      |    |    |

| Access |    |                |                   |    |               |      |    |    |

| Reset  |    | 0              | 0                 | 0  | 0             | 0    | 0  | 0  |

# Bits 30:24 – NCS\_RD\_PULSE[6:0] NCS Pulse Length in READ Access

In standard read access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_RD\_PULSE[6] + NCS\_RD\_PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

In Page mode read access, the NCS\_RD\_PULSE parameter defines the duration of the first access to one page.

### Bits 22:16 - NRD\_PULSE[6:0] NRD Pulse Length

In standard read access, the NRD signal pulse length is defined in clock cycles as:

NRD pulse length = (256\* NRD\_PULSE[6] + NRD\_PULSE[5:0]) clock cycles

The NRD pulse length must be at least 1 clock cycle.

In Page mode read access, the NRD\_PULSE parameter defines the duration of the subsequent accesses in the page.

### Bits 14:8 – NCS\_WR\_PULSE[6:0] NCS Pulse Length in WRITE Access

In write access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_WR\_PULSE[6] + NCS\_WR\_PULSE[5:0]) clock cycles

USB High-Speed Interface (USBHS)

Bit 0 - RXINIC Received IN Data Interrupt Clear

## **Two-wire Interface (TWIHS)**

### 43.7.6 TWIHS Status Register

| Name:     | TWIHS_SR   |

|-----------|------------|

| Offset:   | 0x20       |

| Reset:    | 0x03000009 |

| Property: | Read-only  |

| Bit    | 31   | 30   | 29     | 28     | 27     | 26    | 25     | 24     |

|--------|------|------|--------|--------|--------|-------|--------|--------|

|        |      |      |        |        |        |       | SDA    | SCL    |

| Access |      |      |        |        |        |       | R      | R      |

| Reset  |      |      |        |        |        |       | 1      | 1      |

|        |      |      |        |        |        |       |        |        |

| Bit    | 23   | 22   | 21     | 20     | 19     | 18    | 17     | 16     |

|        |      |      | SMBHHM | SMBDAM | PECERR | TOUT  |        | MCACK  |

| Access |      |      | R      | R      | R      | R     |        | R      |

| Reset  |      |      | 0      | 0      | 0      | 0     |        | 0      |

|        |      |      |        |        |        |       |        |        |

| Bit    | 15   | 14   | 13     | 12     | 11     | 10    | 9      | 8      |

|        |      |      |        |        | EOSACC | SCLWS | ARBLST | NACK   |

| Access |      |      |        |        | R      | R     | R      | R      |

| Reset  |      |      |        |        | 0      | 0     | 0      | 0      |

|        |      |      |        |        |        |       |        |        |

| Bit    | 7    | 6    | 5      | 4      | 3      | 2     | 1      | 0      |

|        | UNRE | OVRE | GACC   | SVACC  | SVREAD | TXRDY | RXRDY  | TXCOMP |

| Access | R    | R    | R      | R      | R      | R     | R      | R      |

| Reset  | 0    | 0    | 0      | 0      | 1      | 0     | 0      | 1      |

### Bit 25 – SDA SDA Line Value

| V | alue | Description                    |

|---|------|--------------------------------|

| 0 |      | SDA line sampled value is '0'. |

| 1 |      | SDA line sampled value is '1'. |

### Bit 24 - SCL SCL Line Value

| Value | Description                    |

|-------|--------------------------------|

| 0     | SCL line sampled value is '0'. |

| 1     | SCL line sampled value is '1.' |

### Bit 21 – SMBHHM SMBus Host Header Address Match (cleared on read)

| Value | Description                                                                |

|-------|----------------------------------------------------------------------------|

| 0     | No SMBus Host Header Address received since the last read of TWIHS_SR.     |

| 1     | An SMBus Host Header Address was received since the last read of TWIHS_SR. |

### Bit 20 - SMBDAM SMBus Default Address Match (cleared on read)

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | No SMBus Default Address received since the last read of TWIHS_SR.     |

| 1     | An SMBus Default Address was received since the last read of TWIHS_SR. |

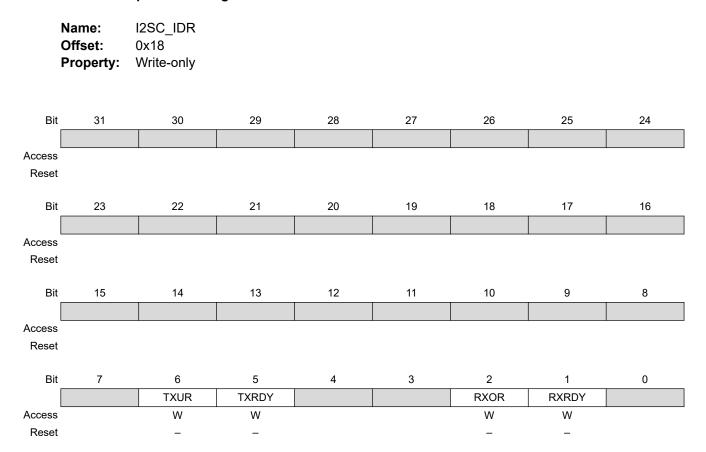

## Inter-IC Sound Controller (I2SC)

### 45.8.7 I2SC Interrupt Disable Register

### Bit 6 – TXUR Transmit Underflow Interrupt Disable

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                            |

| 1     | Writing a '1' to this bit clears the corresponding bit in I2SC_IMR. |

### Bit 5 – TXRDY Transmit Ready Interrupt Disable

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                            |

| 1     | Writing a '1' to this bit clears the corresponding bit in I2SC_IMR. |

### Bit 2 – RXOR Receiver Overrun Interrupt Disable

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                            |

| 1     | Writing a '1' to this bit clears the corresponding bit in I2SC_IMR. |

### Bit 1 – RXRDY Receiver Ready Interrupt Disable

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                            |

| 1     | Writing a '1' to this bit clears the corresponding bit in I2SC_IMR. |

### LIN Mode

- Compliant with LIN 1.3 and LIN 2.0 SPECIFICATIONS

- Master or Slave

- Processing of Frames with Up to 256 Data Bytes

- Response Data Length can be Configurable or Defined Automatically by the Identifier

- Self-synchronization in Slave Node Configuration

- Automatic Processing and Verification of the "Synch Break" and the "Synch Field"

- "Synch Break" Detection Even When Partially Superimposed with a Data Byte

- Automatic Identifier Parity Calculation/Sending and Verification

- Parity Sending and Verification Can be Disabled

- Automatic Checksum Calculation/sending and Verification

- Checksum Sending and Verification Can be Disabled

- Support Both "Classic" and "Enhanced" Checksum Types

- Full LIN Error Checking and Reporting

- Frame Slot Mode: Master Allocates Slots to the Scheduled Frames Automatically

- Generation of the Wakeup Signal

- LON Mode

- Compliant with CEA-709 Specification

- Full-layer 2 Implementation

- Differential Manchester Encoding/Decoding (CDP)

- Preamble Generation Including Bit- and Byte-sync Fields

- LON Timings Handling (beta1, beta2, IDT, etc.)

- CRC Generation and Checking

- Automated Random Number Generation

- Backlog Calculation and Update

- Collision Detection Support

- Supports Both comm\_type=1 and comm\_type=2 Modes

- Clock Drift Tolerance Up to 16%

- Optimal for Node-to-Node Communication (no embedded digital line filter)

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

- Supports Connection of:

- Two DMA Controller Channels (DMAC)

- Offers Buffer Transfer without Processor Intervention

- Register Write Protection

### Universal Synchronous Asynchronous Receiver Transc...

- 3. Write CD and FP in US\_BRGR to configure the baud rate.

- 4. Write COMMT, COLDET, TCOL, CDTAIL, RDMNBM and DMAM in US\_LONMR to configure the LON operating mode.

- 5. Write BETA2, BETA1TX, BETA1RX, PCYCLE, PSNB, NPS, IDTTX and ITDRX respectively in US\_FIDI, US\_LONB1TX, US\_LONB1RX, US\_TTGR, US\_LONPRIO, US\_LONIDTTX and US\_LONIDTRX to set the LON network configuration.

- 6. Write TX\_PL in US\_MAN to select the preamble pattern to use.

- 7. Write LONPL and LONDL in US\_LONPR and US\_LONDL to set the frame transfer.

- 8. Check that TXRDY in US\_CSR is set to 1.

- 9. Write US\_LONL2HDR register to send the header.

- 10. Wait until TXRDY in US\_CSR rises.

- 11. Write TCHR in US\_THR to send a byte.

- 12. If all the data have not been written, redo the two previous steps.

- 13. Wait until LTXD in US\_CSR rises.

- 14. Check the LON errors.

### Figure 46-61. Tx Frame

|                      | -      | Random Delay | Preamble | l2hdr  | Data   | 1 Dat  | a 2    | Data N | -1 Data N | CRC | CRC |   |

|----------------------|--------|--------------|----------|--------|--------|--------|--------|--------|-----------|-----|-----|---|

| TXRDY                | $\neg$ |              |          |        |        |        |        |        |           |     |     | J |

| RXRDY                |        |              |          |        |        |        |        |        |           |     |     |   |

| Write<br>US_LONL2HDR |        |              |          |        |        |        | ·      |        |           |     |     |   |

| Write<br>US THR      |        |              |          | t      | t      | t      | t      |        |           |     |     |   |

| LTXD                 |        |              |          | Data 1 | Data 2 | Data 3 | Data 4 | Data N |           |     |     |   |

### 46.6.10.11.2 Receiving A Frame

- 1. Write TXEN and RXEN in US\_CR to enable both the transmitter and the receiver.

- 2. Write USART\_MODE in US\_MR to select the LON mode configuration.

- 3. Write CD and FP in US\_BRGR to configure the baud rate.

- 4. Write COMMT, COLDET, TCOL, CDTAIL, RDMNBM and DMAM in US\_LONMR to configure the LON operating mode.

- 5. Write BETA2, BETA1TX, BETA1RX, PCYCLE, PSNB, NPS, IDTTX and ITDRX respectively in US\_FIDI, US\_LONB1TX, US\_LONB1RX, US\_TTGR, US\_LONPRIO, US\_LONIDTTX and US\_LONIDTRX to set the LON network configuration.

- 6. Write RXIDLEV and RX\_PL in US\_MAN to indicate the receiver line value and select the preamble pattern to use.

- 7. Wait until RXRDY in US\_CSR rises.

- 8. Read RCHR in US\_RHR.

- 9. If all the data and the two CRC bytes have not been read, redo the two previous steps.

- 10. Wait until LRXD in US\_CSR rises.

- 11. Check the LON errors.

- 12.

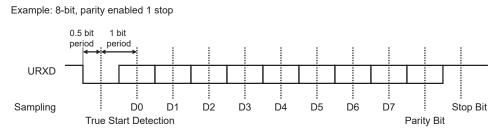

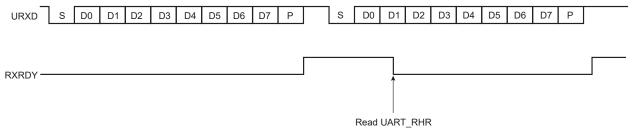

### Figure 47-4. Character Reception

### 47.5.2.3 Receiver Ready

When a complete character is received, it is transferred to the Receive Holding Register (UART\_RHR) and the RXRDY status bit in the Status Register (UART\_SR) is set. The bit RXRDY is automatically cleared when UART\_RHR is read.

### Figure 47-5. Receiver Ready

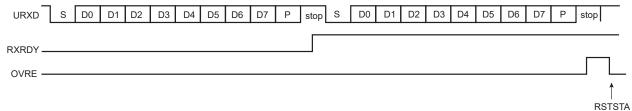

### 47.5.2.4 Receiver Overrun

The OVRE status bit in UART\_SR is set if UART\_RHR has not been read by the software (or the DMA Controller) since the last transfer, the RXRDY bit is still set and a new character is received. OVRE is cleared when the software writes a 1 to the bit RSTSTA (Reset Status) in UART\_CR.

### Figure 47-6. Receiver Overrun

### 47.5.2.5 Parity Error

Each time a character is received, the receiver calculates the parity of the received data bits, in accordance with the field PAR in the Mode Register (UART\_MR). It then compares the result with the received parity bit. If different, the parity error bit PARE in UART\_SR is set at the same time RXRDY is set. The parity bit is cleared when UART\_CR is written with the bit RSTSTA (Reset Status) at 1. If a new character is received before the reset status command is written, the PARE bit remains at 1.

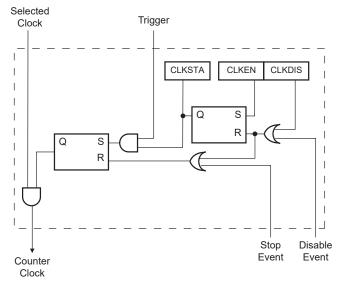

- The clock can be enabled or disabled by the user with the CLKEN and the CLKDIS commands in the Channel Control register (TC\_CCR). In Capture mode it can be disabled by an RB load event if TC\_CMRx.LDBDIS is set to '1'. In Waveform mode, it can be disabled by an RC Compare event if TC\_CMRx.CPCDIS is set to '1'. When disabled, the start or the stop actions have no effect: only a CLKEN command in the TC\_CCR can reenable the clock. When the clock is enabled, TC\_SR.CLKSTA is set.

- The clock can also be started or stopped: a trigger (software, synchro, external or compare) always starts the clock. The clock can be stopped by an RB load event in Capture mode (TC\_CMRx.LDBSTOP = 1) or an RC compare event in Waveform mode (TC\_CMRx.CPCSTOP = 1). The start and the stop commands are effective only if the clock is enabled.

### Figure 50-4. Clock Control

### 50.6.5 Operating Modes

Each channel can operate independently in two different modes:

- Capture mode provides measurement on signals.

- Waveform mode provides wave generation.

The TC operating mode is programmed with TC\_CMRx.WAVE.

In Capture mode, TIOAx and TIOBx are configured as inputs.

In Waveform mode, TIOAx is always configured to be an output and TIOBx is an output if it is not selected to be the external trigger.

### 50.6.6 Trigger

A trigger resets the counter and starts the counter clock. Three types of triggers are common to both modes, and a fourth external trigger is available to each mode.

Regardless of the trigger used, it will be taken into account at the following active edge of the selected clock. This means that the counter value can be read differently from zero just after a trigger, especially when a low frequency signal is selected as the clock.

The following triggers are common to both modes:

• Software Trigger: Each channel has a software trigger, available by setting TC\_CCR.SWTRG.

# Pulse Width Modulation Controller (PWM)

| 055-11 | News        | D' D.          |       |       |         |       |         |         |         |          |

|--------|-------------|----------------|-------|-------|---------|-------|---------|---------|---------|----------|

| Offset | Name        | Bit Pos.       |       |       |         |       |         |         |         |          |

|        |             | 31:24          |       |       |         |       |         |         | 10.01   |          |

|        |             | 7:0            |       | UPRC  | NT[3:0] |       |         | UPR     | [3:0]   |          |

| 0x2C   | PWM_SCUP    | 15:8           |       |       |         |       |         |         |         |          |

|        |             | 23:16<br>31:24 |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       |         | UPRU    |         |          |

|        |             | 15:8           |       |       |         |       |         |         | D[3.0]  |          |

| 0x30   | PWM_SCUPUPD | 23:16          |       |       |         |       |         |         |         |          |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | UNRE    |         |         | WRDY     |

|        |             | 15:8           | CMPM7 | CMPM6 | CMPM5   | CMPM4 | CMPM3   | CMPM2   | CMPM1   | CMPM0    |

| 0x34   | PWM_IER2    | 23:16          | CMPU7 | CMPU6 | CMPU5   | CMPU4 | CMPU3   | CMPU2   | CMPU1   | CMPU0    |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | UNRE    |         |         | WRDY     |

|        |             | 15:8           | CMPM7 | CMPM6 | CMPM5   | CMPM4 | CMPM3   | CMPM2   | CMPM1   | CMPM0    |

| 0x38   | PWM_IDR2    | 23:16          | CMPU7 | CMPU6 | CMPU5   | CMPU4 | CMPU3   | CMPU2   | CMPU1   | CMPU0    |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | UNRE    |         |         | WRDY     |

|        |             | 15:8           | CMPM7 | CMPM6 | CMPM5   | CMPM4 | CMPM3   | CMPM2   | CMPM1   | CMPM0    |

| 0x3C   | PWM_IMR2    | 23:16          | CMPU7 | CMPU6 | CMPU5   | CMPU4 | CMPU3   | CMPU2   | CMPU1   | CMPU0    |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | UNRE    |         |         | WRDY     |

| 0x40   | PWM_ISR2    | 15:8           | CMPM7 | CMPM6 | CMPM5   | CMPM4 | CMPM3   | CMPM2   | CMPM1   | CMPM0    |

| 0x40   |             | 23:16          | CMPU7 | CMPU6 | CMPU5   | CMPU4 | CMPU3   | CMPU2   | CMPU1   | CMPU0    |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | OOVH3   | OOVH2   | OOVH1   | OOVH0    |

| 0x44   | PWM_OOV     | 15:8           |       |       |         |       |         |         |         |          |

| 0, TT  |             | 23:16          |       |       |         |       | OOVL3   | OOVL2   | OOVL1   | OOVL0    |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | OSH3    | OSH2    | OSH1    | OSH0     |

| 0x48   | PWM_OS      | 15:8           |       |       |         |       |         |         |         |          |

|        | _           | 23:16          |       |       |         |       | OSL3    | OSL2    | OSL1    | OSL0     |

|        |             | 31:24          |       |       |         |       |         |         |         |          |

|        |             | 7:0            |       |       |         |       | OSSH3   | OSSH2   | OSSH1   | OSSH0    |

| 0x4C   | PWM_OSS     | 15:8           |       |       |         |       | 00010   | 00010   | 00014   |          |

|        |             | 23:16          |       |       |         |       | OSSL3   | OSSL2   | OSSL1   | OSSL0    |

|        |             | 31:24          |       |       |         |       | 000110  | 000110  | 000114  | 000110   |

|        |             | 7:0<br>15:8    |       |       |         |       | OSCH3   | OSCH2   | OSCH1   | OSCH0    |

| 0x50   | PWM_OSC     | 23:16          |       |       |         |       | OSCL3   | OSCL2   | OSCL1   | OSCL0    |

|        |             | 31:24          |       |       |         |       | USULS   | UGGLZ   | USCLI   | USULU    |

|        |             | 7:0            |       |       |         |       | OSSUPH3 | OSSUPH2 | OSSUPH1 | OSSUPH0  |

|        |             | 15:8           |       |       |         |       | 0000000 |         |         | 00001110 |

| 0x54   | PWM_OSSUPD  | 23:16          |       |       |         |       | OSSUPL3 | OSSUPL2 | OSSUPL1 | OSSUPL0  |

|        |             | 31:24          |       |       |         |       |         |         | SECOLET | 0000120  |

| 0x58   | PWM_OSCUPD  | 7:0            |       |       |         |       | OSCUPH3 | OSCUPH2 | OSCUPH1 | OSCUPH0  |

| 5.00   |             |                |       |       |         |       |         |         |         |          |

## Pulse Width Modulation Controller (PWM)

|        | Name:<br>Offset:<br>Reset:<br>Property: | PWM_SMMR<br>0xB0<br>0x00000000<br>Read/Write |    |    |    |    |       |       |

|--------|-----------------------------------------|----------------------------------------------|----|----|----|----|-------|-------|

| Bit    | 31                                      | 30                                           | 29 | 28 | 27 | 26 | 25    | 24    |

|        |                                         |                                              |    |    |    |    |       |       |

| Access |                                         |                                              |    |    |    |    |       |       |

| Reset  |                                         |                                              |    |    |    |    |       |       |

| Bit    | 23                                      | 22                                           | 21 | 20 | 19 | 18 | 17    | 16    |

|        |                                         |                                              |    |    |    |    | DOWN1 | DOWN0 |

| Access |                                         |                                              |    |    |    |    |       |       |

| Reset  |                                         |                                              |    |    |    |    | 0     | 0     |

| Bit    | 15                                      | 14                                           | 13 | 12 | 11 | 10 | 9     | 8     |

| Access |                                         |                                              |    |    |    |    |       |       |

| Reset  |                                         |                                              |    |    |    |    |       |       |

| Bit    | 7                                       | 6                                            | 5  | 4  | 3  | 2  | 1     | 0     |

|        |                                         |                                              |    |    |    |    | GCEN1 | GCEN0 |

| Access |                                         |                                              |    |    |    |    | R/W   | R/W   |

| Reset  |                                         |                                              |    |    |    |    | 0     | 0     |

### 51.7.32 PWM Stepper Motor Mode Register

## Bits 16, 17 – DOWNx Down Count

| Value | Description   |

|-------|---------------|

| 0     | Up counter.   |

| 1     | Down counter. |

### Bits 0, 1 – GCENx Gray Count Enable

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | Disable gray count generation on PWML[2*x], PWMH[2*x], PWML[2*x +1], PWMH[2*x +1] |

| 1     | Enable gray count generation on PWML[2*x], PWMH[2*x], PWML[2*x +1], PWMH[2*x +1]. |

## Integrity Check Monitor (ICM)

### 55.6.2 ICM Control Register

|        | Name:<br>Offset:<br>Reset:<br>Property: | ICM_CTRL<br>0x04<br>–<br>Write-only |         |    |    |       |         |        |

|--------|-----------------------------------------|-------------------------------------|---------|----|----|-------|---------|--------|

| Bit    | 31                                      | 30                                  | 29      | 28 | 27 | 26    | 25      | 24     |

|        |                                         |                                     |         |    |    |       |         |        |

| Access |                                         |                                     |         |    |    |       |         |        |

| Reset  |                                         |                                     |         |    |    |       |         |        |

|        |                                         |                                     |         |    |    |       |         |        |

| Bit    | 23                                      | 22                                  | 21      | 20 | 19 | 18    | 17      | 16     |

|        |                                         |                                     |         |    |    |       |         |        |

| Access |                                         |                                     |         |    |    |       |         |        |

| Reset  |                                         |                                     |         |    |    |       |         |        |

| Bit    | 15                                      | 14                                  | 13      | 12 | 11 | 10    | 9       | 8      |

| Dit    | 15                                      |                                     | N[3:0]  | 12 |    |       | S[3:0]  |        |

| A      | W                                       |                                     |         | W  | W  |       |         | W      |

| Access |                                         | W                                   | W       |    |    | W     | W       | vv     |

| Reset  | 0                                       | 0                                   | 0       | _  | 0  | 0     | 0       | -      |

| Bit    | 7                                       | 6                                   | 5       | 4  | 3  | 2     | 1       | 0      |

|        |                                         |                                     | SH[3:0] |    | -  | SWRST | DISABLE | ENABLE |

| Access | W                                       | W                                   | W       | W  |    | W     | W       | W      |

| Reset  |                                         | 0                                   | 0       | _  |    | _     | _       | _      |

# **Bits 15:12 – RMEN[3:0]** Region Monitoring Enable Monitoring is activated by default.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | No effect                                                                                |

| 1     | When bit RMEN[i] is set to one, the monitoring of region with identifier i is activated. |

### Bits 11:8 – RMDIS[3:0] Region Monitoring Disable

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | No effect                                                                                |

| 1     | When bit RMDIS[i] is set to one, the monitoring of region with identifier i is disabled. |

### Bits 7:4 - REHASH[3:0] Recompute Internal Hash

| Value | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0     | No effect                                                                                                                    |

| 1     | When REHASH[i] is set to one, Region i digest is re-computed. This bit is only available when region monitoring is disabled. |

### Bit 2 - SWRST Software Reset

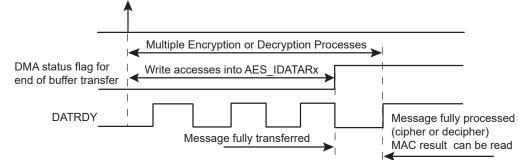

### 57.4.3.2.2 If AES\_MR.LOD = 1

This mode is optimized to process AES CBC-MAC operating mode.

The user must first wait for the DMA buffer transfer complete flag, then for the flag DATRDY to rise to ensure that the encryption/decryption is completed (see the figure below).

In this case, no receive buffers are required.

The output data are only available on AES\_ODATARx.

### Figure 57-4. DMA Transfer with AES\_MR.LOD = 1

Enable DMA Channels associated with AES\_IDATARx and AES\_ODATARx registers

The table below summarizes the different cases.

### Table 57-1. Last Output Data Mode Behavior versus Start Modes

| Sequence                                            | Manual and Auto M                          | odes                                          | DMA Transfer                                                                |                                                               |  |

|-----------------------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------|--|

|                                                     | AES_MR.LOD = 0                             | AES_MR.LOD = 1                                | AES_MR.LOD = 0                                                              | AES_MR.LOD = 1                                                |  |

| DATRDY Flag<br>Clearing<br>Condition <sup>(1)</sup> | At least one<br>AES_ODATAR<br>must be read | At least one<br>AES_IDATAR must<br>be written | Not used                                                                    | Managed by the<br>DMA                                         |  |

| End of<br>Encryption/<br>Decryption<br>Notification | DATRDY                                     | DATRDY                                        | 2 DMA Buffer<br>transfer complete<br>flags (channel m and<br>channel n)     | DMA buffer transfer<br>complete flag, then<br>AES DATRDY flag |  |

| Encrypted/<br>Decrypted<br>Data Result<br>Location  | In AES_ODATARx                             | In AES_ODATARx                                | At the address<br>specified in the<br>Channel Buffer<br>Transfer Descriptor | In AES_ODATARx                                                |  |

### Note:

1. Depending on the mode, there are other ways of clearing the DATRDY flag. See AES Interrupt Status Register.

**AWARNING** In DMA mode, reading AES\_ODATARx before the last data transfer may lead to unpredictable results.

### 57.5.13 AES GCM Intermediate Hash Word Register x

AES\_GHASHRx

0x78 + x\*0x04 [x=0..3]

Name:

Offset:

|        | Reset:<br>Property: | 0x00000000<br>R/W |     |       |          |     |     |     |

|--------|---------------------|-------------------|-----|-------|----------|-----|-----|-----|

| Bit    | 31                  | 30                | 29  | 28    | 27       | 26  | 25  | 24  |

|        |                     |                   |     | GHASH | I[31:24] |     |     |     |

| Access | R/W                 | R/W               | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0                   | 0                 | 0   | 0     | 0        | 0   | 0   | 0   |

|        |                     |                   |     |       |          |     |     |     |

| Bit    | 23                  | 22                | 21  | 20    | 19       | 18  | 17  | 16  |

|        |                     |                   |     | GHASH | H[23:16] |     |     |     |

| Access | R/W                 | R/W               | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0                   | 0                 | 0   | 0     | 0        | 0   | 0   | 0   |

|        |                     |                   |     |       |          |     |     |     |

| Bit    | 15                  | 14                | 13  | 12    | 11       | 10  | 9   | 8   |

|        |                     |                   |     | GHAS  | H[15:8]  |     |     |     |

| Access | R/W                 | R/W               | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0                   | 0                 | 0   | 0     | 0        | 0   | 0   | 0   |

|        |                     |                   |     |       |          |     |     |     |

| Bit    | 7                   | 6                 | 5   | 4     | 3        | 2   | 1   | 0   |

|        | GHASH[7:0]          |                   |     |       |          |     |     |     |

| Access | R/W                 | R/W               | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0                   | 0                 | 0   | 0     | 0        | 0   | 0   | 0   |

|        |                     |                   |     |       |          |     |     |     |

### Bits 31:0 - GHASH[31:0] Intermediate GCM Hash Word x

The four 32-bit Intermediate Hash Word registers expose the intermediate GHASH value. May be read to save the current GHASH value so processing can later be resumed, presumably on a later message fragment. Whenever a new key is written to the AES Key Register two automatic actions are processed:

- GCM hash subkey generation

- AES\_GHASHRx Clear

See Key Writing and Automatic Hash Subkey Calculation for details.

If an application software-specific hash initial value is needed for the GHASH, it must be written to AES\_GHASHRx:

- after a write to the AES Key Register, if any,

- before starting the input data feed.

### Electrical Characteristics for SAM ...

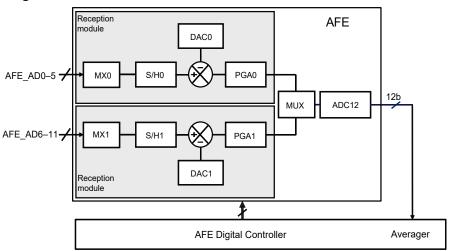

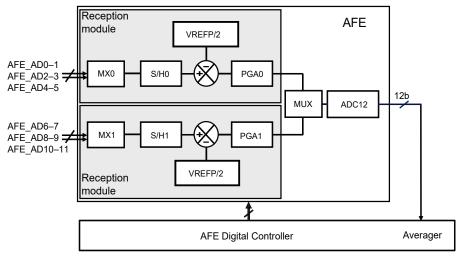

### Figure 58-11. Single-ended Mode AFE

### Figure 58-12. Differential Mode AFE

### 58.8.1 AFE Power Supply

### 58.8.1.1 Power Supply Characteristics Table 58-29. Power Supply Characteristics

| Symbol             | Parameter                   | Conditions                     |   | Тур | Мах | Unit |

|--------------------|-----------------------------|--------------------------------|---|-----|-----|------|

| I <sub>VDDIN</sub> | Analog Current Consumption  | Sleep mode (see Note 2)        |   | 2   |     | μA   |

|                    |                             | Fast wake-up mode (see Note 3) |   | 0.4 |     | mA   |

|                    |                             | Normal mode, single sampling   | _ | 3.4 | -   | mA   |

|                    |                             | Normal mode, dual sampling     |   | 4.2 |     | mA   |

|                    | Digital Current Consumption | Sleep mode (see Note 2)        |   | 1   |     |      |

| IVDDCORE           | Digital Current Consumption | Normal mode                    | - | 80  | -   | μA   |

### Note:

1. Current consumption is measured with AFEC\_ACR.IBCTL=10.

### Electrical Characteristics for SAM ...

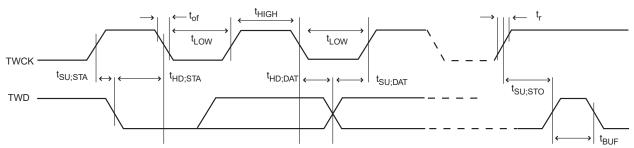

| Symbol                        | Parameter                                  | Condition                   | Min                                                         | Мах                                  | Unit |

|-------------------------------|--------------------------------------------|-----------------------------|-------------------------------------------------------------|--------------------------------------|------|

| C <sub>i</sub> <sup>(1)</sup> | Capacitance for each I/O Pin               | -                           | -                                                           | 10                                   | pF   |

| f <sub>TWCK</sub>             | TWCK Clock Frequency                       | -                           | 0                                                           | 400                                  | kHz  |

| R <sub>P</sub>                | Value of Pull-up resistor                  | f <sub>TWCK</sub> ≤ 100 kHz | (V <sub>DDIO</sub> - 0.4V) ÷                                | 1000ns ÷ C <sub>b</sub>              | Ω    |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | 3mA                                                         | 300ns ÷ C <sub>b</sub>               |      |

| t <sub>LOW</sub>              | Low Period of the TWCK clock               | f <sub>TWCK</sub> ≤ 100 kHz | (3)                                                         | -                                    | μs   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | (3)                                                         | -                                    | μs   |

| t <sub>HIGH</sub>             | High period of the TWCK clock              | f <sub>TWCK</sub> ≤ 100 kHz | (4)                                                         | -                                    | μs   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | (4)                                                         | _<br>_                               | μs   |

| t <sub>HD;STA</sub>           | Hold Time (repeated) START                 | f <sub>TWCK</sub> ≤ 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

|                               | Condition                                  | f <sub>TWCK</sub> > 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

| t <sub>SU;STA</sub>           | Set-up time for a repeated START condition | f <sub>TWCK</sub> ≤ 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

| t <sub>HD;DAT</sub>           | Data hold time                             |                             |                                                             | $3 \times t_{CPMCK}^{(5)}$           | μs   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | 0                                                           | 3 ×t <sub>CPMCK</sub> <sup>(5)</sup> | μs   |

| t <sub>SU;DAT</sub>           | Data setup time                            | f <sub>TWCK</sub> ≤ 100 kHz | t <sub>LOW -</sub> 3 ×<br>t <sub>CPMCK</sub> <sup>(5)</sup> | -                                    | ns   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | t <sub>LOW -</sub> 3 ×<br>t <sub>CPMCK</sub> <sup>(5)</sup> | -                                    | ns   |

| t <sub>SU;STO</sub>           | Setup time for STOP condition              | f <sub>TWCK</sub> ≤ 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

|                               |                                            | f <sub>TWCK</sub> > 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

| t <sub>HD;STA</sub>           | Hold Time (repeated) START                 | f <sub>TWCK</sub> ≤ 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

|                               | Condition                                  | f <sub>TWCK</sub> > 100 kHz | t <sub>HIGH</sub>                                           | -                                    | μs   |

### Note:

- 1. Required only for  $f_{TWCK} > 100 \text{ kHz}$ .

- 2.  $C_b$  = capacitance of one bus line in pF. Per I<sup>2</sup>C standard,  $C_b$  max = 400pF.

- 3. The TWCK low period is defined as follows:  $t_{LOW} = ((CLDIV \times 2^{CKDIV}) + 4) \times t_{MCK}$ .

- 4. The TWCK high period is defined as follows:  $t_{HIGH} = ((CHDIV \times 2^{CKDIV}) + 4) \times t_{MCK}$ .

- 5.  $t_{CPMCK}$  = MCK bus period

## Electrical Characteristics for SAM ...

### Figure 58-29. Two-wire Serial Bus Timing

### 58.13.1.13 GMAC Characteristics

### 58.13.1.13.1 Timing Conditions

### Table 58-69. Load Capacitance on Data, Clock Pads

| Supply | CL    |      |  |

|--------|-------|------|--|

|        | Max   | Min  |  |

| 3.3V   | 20 pF | 0 pF |  |

### 58.13.1.13.2 Timing Constraints

The GMAC must be constrained so as to satisfy the timings of standards shown below and in 58.13.1.13.3 MII Mode, in MAX corner.

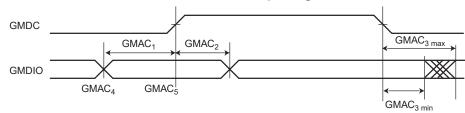

### Table 58-70. GMAC Signals Relative to GMDC

| Symbol            | Parameter                        | Min  | Max               | Unit |

|-------------------|----------------------------------|------|-------------------|------|

| GMAC <sub>1</sub> | Setup for GMDIO from GMDC rising | 10   | -                 | ns   |

| GMAC <sub>2</sub> | Hold for GMDIO from GMDC rising  |      | -                 |      |

| GMAC <sub>3</sub> | GMDIO toggling from GMDC falling | 0(1) | 10 <sup>(1)</sup> |      |

Note: 1. For GMAC output signals, min and max access time are defined. The min access time is the time between the GMDC falling edge and the signal change. The max access timing is the time between the GMDC falling edge and the signal stabilizes. The figure below illustrates min and max accesses for GMAC<sub>3</sub>.

#### Figure 58-30. Min and Max Access Time of GMAC Output Signals