#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                    |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                             |

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                | -                                                                                                  |

| RAM Size                   | 384K x 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-UFBGA                                                                                          |

| Supplier Device Package    | 144-UFBGA (6x6)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q21a-cfnt                        |

|                            |                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Peripherals

| Instance ID | Instance Name | NVIC Interrupt | PMC<br>Clock<br>Control | Description                                                                                                                     |

|-------------|---------------|----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 67          | GMAC          | Q2             | -                       | GMAC Queue 2 Interrupt signal<br>toggled on a DMA write to the first<br>word of each DMA data buffer<br>associated with queue 2 |

| 66          | -             | -              | -                       | Reserved                                                                                                                        |

| 67          | -             | -              | -                       | Reserved                                                                                                                        |

| 68          | ARM           | IXC            | _                       | Floating Point Unit Interrupt IXC associated with FPU cumulative exception bit                                                  |

| 69          | I2SC0         | Х              | Х                       | Inter-IC Sound Controller                                                                                                       |

| 70          | I2SC1         | Х              | Х                       | Inter-IC Sound Controller                                                                                                       |

| 71          | GMAC          | Q3             | _                       | GMAC Queue 3 Interrupt signal<br>toggled on a DMA write to the first<br>word of each DMA data buffer<br>associated with queue 3 |

| 72          | GMAC          | Q4             | _                       | GMAC Queue 4 Interrupt signal<br>toggled on a DMA write to the first<br>word of each DMA data buffer<br>associated with queue 4 |

| 73          | GMAC          | Q5             | -                       | GMAC Queue 5 Interrupt signal<br>toggled on a DMA write to the first<br>word of each DMA data buffer<br>associated with queue 5 |

### 14.2 Peripheral Signal Multiplexing on I/O Lines

The SAM E70/S70/V70/V71 features

- Two PIO controllers on 64-pin versions (PIOA and PIOB)

- Three PIO controllers on the 100-pin version (PIOA, PIOB and PIOD)

- Five PIO controllers on the 144-pin version (PIOA, PIOB, PIOC, PIOD and PIOE), that multiplex the I/O lines of the peripheral set.

The SAM E70/S70/V70/V71 PIO Controllers control up to 32 lines and each line can be assigned to one of four peripheral functions: A, B, C or D.

For more information on multiplexed signals, refer to the "Package and Pinout" chapter.

## Enhanced Embedded Flash Controller (EEFC)

## 22.5.2 EEFC Flash Command Register

| Name:     | EEFC_FCR   |

|-----------|------------|

| Offset:   | 0x04       |

| Property: | Write-only |

| GETD, GLB,<br>GGPB, STUI,<br>SPUI, GCALB,<br>WUS, EUS,<br>STUS, SPUS,<br>EA | Commands requiring<br>no argument,<br>including Erase all<br>command | FARG is meaningless, must be written with 0                                                         |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| ES                                                                          | Erase sector command                                                 | FARG must be written with any page number within the sector to be erased                            |

| EPA                                                                         | Erase pages<br>command                                               | FARG[1:0] defines the number of pages to be erased<br>The start page must be written in FARG[15:2]. |

|                                                                             |                                                                      | FARG[1:0] = 0: Four pages to be erased. FARG[15:2] =<br>Page_Number / 4                             |

|                                                                             |                                                                      | FARG[1:0] = 1: Eight pages to be erased. FARG[15:3] =<br>Page_Number / 8, FARG[2]=0                 |

|                                                                             |                                                                      | FARG[1:0] = 2: Sixteen pages to be erased. FARG[15:4] =<br>Page_Number / 16, FARG[3:2]=0            |

|                                                                             |                                                                      | FARG[1:0] = 3: Thirty-two pages to be erased. FARG[15:5] =<br>Page_Number / 32, FARG[4:2]=0         |

|                                                                             |                                                                      | Refer to "EEFC_FCR.FARG Field for EPA Command".                                                     |

| WP, WPL,<br>EWP, EWPL                                                       | Programming commands                                                 | FARG must be written with the page number to be programmed                                          |

| SLB, CLB                                                                    | Lock bit commands                                                    | FARG defines the page number to be locked or unlocked                                               |

| SGPB, CGPB                                                                  | GPNVM commands                                                       | FARG defines the GPNVM number to be programmed                                                      |

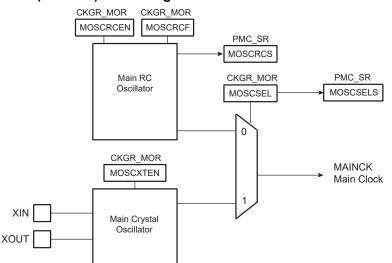

### Figure 30-2. Main Clock (MAINCK) Block Diagram

#### 30.5.1 Main RC Oscillator

After reset, the Main RC oscillator is enabled with the 12 MHz frequency selected. This oscillator is selected as the source of MAINCK. MAINCK is the default clock selected to start the system.

Only the 8/12 MHz RC oscillator frequencies are calibrated in production. Refer to the section "Electrical Characteristics".

The software can disable or enable the Main RC oscillator with the MOSCRCEN bit in the Clock Generator Main Oscillator Register (CKGR\_MOR).

The output frequency of the Main RC oscillator can be selected among 4, 8 or 12 MHz. Selection is done by configuring the field MOSCRCF in CKGR\_MOR. When changing the frequency selection, the MOSCRCS bit in the Power Management Controller Status Register (PMC\_SR) is automatically cleared and MAINCK is stopped until the oscillator is stabilized. Once the oscillator is stabilized, MAINCK restarts and PMC\_SR.MOSCRCS is set. Note that enabling the Main RC oscillator (MOSCRCEN = 1) and changing its frequency (MOSCRCF) at the same time is not allowed.

This oscillator must be enabled first and its frequency changed in a second step.

When disabling the Main RC oscillator by clearing the CKGR\_MOR.MOSCRCEN bit, the PMC\_SR.MOSCRCS bit is automatically cleared, indicating that the oscillator is OFF.

Setting the MOSCRCS bit in the Power Management Controller Interrupt Enable Register (PMC\_IER) triggers an interrupt to the processor.

### **Related Links**

58. Electrical Characteristics for SAM V70/V71

59. Electrical Characteristics for SAM E70/S70

#### 30.5.2 Main RC Oscillator Frequency Adjustment

The 8 MHz and 12 MHz frequencies are factory-centered to the typical values by using Flash calibration bits (refer to the "Electrical Characteristics" chapter).

The Flash calibration bits setting the Main RC oscillator frequency to 8 MHz and 12 MHz vary from device to device. To get a starting point when changing the CAL8 or CAL12 fields, it is recommended to first read their corresponding Flash calibration bits in the Flash Controller.

© 2018 Microchip Technology Inc.

Specific Address 1 Bottom register (GMAC\_SAB1) (Address 0x088) 0x87654321

Specific Address 1 Top register (GMAC\_SAT1) (Address 0x08C) 0x0000CBA9

For a successful match to the type ID, the following Type ID Match 1 register must be set up:

Type ID Match 1 register (GMAC\_TIDM1) (Address 0x0A8) 0x80004321

#### 38.6.8 Broadcast Address

#### 38.6.9 Hash Addressing

The hash address register is 64 bits long and takes up two locations in the memory map. The least significant bits are stored in Hash Register Bottom and the most significant bits in Hash Register Top.

The unicast hash enable and the multicast hash enable bits in the Network Configuration register enable the reception of hash matched frames. The destination address is reduced to a 6-bit index into the 64-bit Hash register using the following hash function: The hash function is an XOR of every sixth bit of the destination address.

$hash\_index[05] = da[05] ^ da[11] ^ da[17] ^ da[23] ^ da[29] ^ da[35] ^ da[41] ^ da[47]$

$hash\_index[04] = da[04] ^ da[10] ^ da[16] ^ da[22] ^ da[28] ^ da[34] ^ da[40] ^ da[46]$

hash\_index[03] = da[03] ^ da[09] ^ da[15] ^ da[21] ^ da[27] ^ da[33] ^ da[39] ^ da[45]

hash\_index[02] = da[02] ^ da[08] ^ da[14] ^ da[20] ^ da[26] ^ da[32] ^ da[38] ^ da[44]

$hash\_index[01] = da[01] ^ da[07] ^ da[13] ^ da[19] ^ da[25] ^ da[31] ^ da[37] ^ da[43]$

hash\_index[00] = da[00] ^ da[06] ^ da[12] ^ da[18] ^ da[24] ^ da[30] ^ da[36] ^ da[42]

da[0] represents the least significant bit of the first byte received, that is, the multicast/unicast indicator, and da[47] represents the most significant bit of the last byte received.

If the hash index points to a bit that is set in the Hash register then the frame will be matched according to whether the frame is multicast or unicast.

A multicast match will be signaled if the multicast hash enable bit is set, da[0] is logic 1 and the hash index points to a bit set in the Hash register.

A unicast match will be signaled if the unicast hash enable bit is set, da[0] is logic 0 and the hash index points to a bit set in the Hash register.

To receive all multicast frames, the Hash register should be set with all ones and the multicast hash enable bit should be set in the Network Configuration register.

#### 38.6.10 Copy all Frames (Promiscuous Mode)

If the Copy All Frames bit is set in the Network Configuration register then all frames (except those that are too long, too short, have FCS errors or have GRXER asserted during reception) will be copied to memory. Frames with FCS errors will be copied if bit 26 is set in the Network Configuration register.

#### 38.6.11 Disable Copy of Pause Frames

Pause frames can be prevented from being written to memory by setting the disable copying of pause frames control bit 23 in the Network Configuration register. When set, pause frames are not copied to memory regardless of the Copy All Frames bit, whether a hash match is found, a type ID match is identified or if a destination address match is found.

# SAM E70/S70/V70/V71 Family GMAC - Ethernet MAC

#### 38.8.48 GMAC 512 to 1023 Byte Frames Transmitted Register

| Name:     | GMAC_TBFT1023 |

|-----------|---------------|

| Offset:   | 0x128         |

| Reset:    | 0x0000000     |

| Property: | -             |

| Bit             | 31          | 30     | 29     | 28                 | 27                     | 26     | 25     | 24     |

|-----------------|-------------|--------|--------|--------------------|------------------------|--------|--------|--------|

|                 | NFTX[31:24] |        |        |                    |                        |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Reset           | 0           | 0      | 0      | 0                  | 0                      | 0      | 0      | 0      |

|                 |             |        |        |                    |                        |        |        |        |

| Bit             | 23          | 22     | 21     | 20                 | 19                     | 18     | 17     | 16     |

|                 |             |        |        | NFTX               | [23:16]                |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Reset           | 0           | 0      | 0      | 0                  | 0                      | 0      | 0      | 0      |

|                 |             |        |        |                    |                        |        |        |        |

| Bit             | 15          | 14     | 13     | 12                 | 11                     | 10     | 9      | 8      |

|                 | NFTX[15:8]  |        |        |                    |                        |        |        |        |

|                 |             |        |        |                    | [15.6]                 |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Access<br>Reset |             | R<br>0 | R<br>0 |                    |                        | R<br>0 | R<br>0 | R<br>0 |

|                 |             |        |        | R                  | R                      |        |        |        |

|                 | 0           |        |        | R                  | R                      |        |        |        |

| Reset           | 0           | 0      | 0      | R<br>0<br>4        | R<br>0                 | 0      |        | 0      |

| Reset           | 0<br>7      | 0      | 0      | R<br>0<br>4        | R<br>0<br>3            | 0      |        | 0      |

| Reset<br>Bit    | 0<br>7<br>R | 0<br>6 | 0<br>5 | R<br>0<br>4<br>NFT | R<br>0<br>3<br><([7:0] | 0<br>2 | 0      | 0      |

Bits 31:0 – NFTX[31:0] 512 to 1023 Byte Frames Transmitted without Error

This register counts the number of 512 to 1023 byte frames successfully transmitted without error, i.e., no underrun and not too many retries.

## USB High-Speed Interface (USBHS)

- Bit 6 STALLEDEC STALLed Interrupt Clear

- Bit 5 OVERFEC Overflow Interrupt Clear

- Bit 4 NAKINEC NAKed IN Interrupt Clear

- Bit 3 NAKOUTEC NAKed OUT Interrupt Clear

- Bit 2 RXSTPEC Received SETUP Interrupt Clear

- Bit 1 RXOUTEC Received OUT Data Interrupt Clear

- Bit 0 TXINEC Transmitted IN Interrupt Clear

## **USB High-Speed Interface (USBHS)**

#### 39.6.24 Device Endpoint Interrupt Disable Register (Isochronous Endpoints)

Name:

USBHS\_DEVEPTIDRx (ISOENPT)

Offset:

0x0220 + x\*0x04 [x=0..9]

Reset:

0

Property:

Read/Write

This register view is relevant only if EPTYPE = 0x1 in "Device Endpoint x Configuration Register".

For additional information, see "Device Endpoint x Mask Register (Isochronous Endpoints)".

This register always reads as zero.

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Clears the corresponding bit in USBHS\_DEVEPTIMRx.

| Bit    | 31         | 30       | 29      | 28          | 27          | 26         | 25      | 24         |

|--------|------------|----------|---------|-------------|-------------|------------|---------|------------|

|        |            |          |         |             |             |            |         |            |

| Access |            |          |         |             |             |            |         |            |

| Reset  |            |          |         |             |             |            |         |            |

|        |            |          |         |             |             |            |         |            |

| Bit    | 23         | 22       | 21      | 20          | 19          | 18         | 17      | 16         |

|        |            |          |         |             |             |            |         | EPDISHDMAC |

| Access |            |          |         |             |             |            |         |            |

| Reset  |            |          |         |             |             |            |         | 0          |

|        |            |          |         |             |             |            |         |            |

| Bit    | 15         | 14       | 13      | 12          | 11          | 10         | 9       | 8          |

|        |            | FIFOCONC |         | NBUSYBKEC   |             | ERRORTRANS | DATAXEC | MDATEC     |

|        |            |          |         |             |             | EC         |         |            |

| Access |            |          |         | •           |             |            |         |            |

| Reset  |            | 0        |         | 0           |             | 0          | 0       | 0          |

|        |            |          |         |             |             |            |         |            |

| Bit    | 7          | 6        | 5       | 4           | 3           | 2          | 1       | 0          |

|        | SHORTPACKE | CRCERREC | OVERFEC | HBISOFLUSHE | HBISOINERRE | UNDERFEC   | RXOUTEC | TXINEC     |

|        | TEC        |          |         | С           | С           |            |         |            |

| Access |            |          |         |             |             | - I        |         |            |

| Reset  | 0          | 0        | 0       | 0           | 0           | 0          | 0       | 0          |

Bit 16 - EPDISHDMAC Endpoint Interrupts Disable HDMA Request Clear

- Bit 14 FIFOCONC FIFO Control Clear

- Bit 12 NBUSYBKEC Number of Busy Banks Interrupt Clear

- Bit 10 ERRORTRANSEC Transaction Error Interrupt Clear

- Bit 9 DATAXEC DataX Interrupt Clear

- Bit 8 MDATEC MData Interrupt Clear

## **USB High-Speed Interface (USBHS)**

#### 39.6.64 Host Pipe x Error Register

| Name:     | USBHS_HSTPIPERRx       |

|-----------|------------------------|

| Offset:   | 0x0680 + x*0x04 [x=09] |

| Reset:    | 0                      |

| Property: | Read/Write             |

Writing a zero in a bit/field in this register clears the bit/field. Writing a one has no effect.

| Bit    | 31 | 30    | 29      | 28    | 27      | 26  | 25      | 24      |

|--------|----|-------|---------|-------|---------|-----|---------|---------|

|        |    |       |         |       |         |     |         |         |

| Access |    | •     | •       | •     | •       | •   | •       |         |

| Reset  |    |       |         |       |         |     |         |         |

|        |    |       |         |       |         |     |         |         |

| Bit    | 23 | 22    | 21      | 20    | 19      | 18  | 17      | 16      |

|        |    |       |         |       |         |     |         |         |

| Access |    |       |         |       |         |     |         |         |

| Reset  |    |       |         |       |         |     |         |         |

|        |    |       |         |       |         |     |         |         |

| Bit    | 15 | 14    | 13      | 12    | 11      | 10  | 9       | 8       |

|        |    |       |         |       |         |     |         |         |

| Access |    |       |         |       |         |     |         |         |

| Reset  |    |       |         |       |         |     |         |         |

|        |    |       |         |       |         |     |         |         |

| Bit    | 7  | 6     | 5       | 4     | 3       | 2   | 1       | 0       |

|        |    | COUNT | ER[1:0] | CRC16 | TIMEOUT | PID | DATAPID | DATATGL |

| Access |    |       |         | •     |         |     |         |         |

| Reset  |    | 0     | 0       | 0     | 0       | 0   | 0       | 0       |

#### Bits 6:5 - COUNTER[1:0] Error Counter

This field is incremented each time an error occurs (CRC16, TIMEOUT, PID, DATAPID or DATATGL).

This field is cleared when receiving a USB packet free of error.

When this field reaches 3 (i.e., 3 consecutive errors), this pipe is automatically frozen (USBHS\_HSTPIPIMRx.PFREEZE is set).

#### Bit 4 – CRC16 CRC16 Error

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | No CRC16 error occurred since last clear of this bit.               |

| 1     | This bit is automatically set when a CRC16 error has been detected. |

#### Bit 3 - TIMEOUT Time-Out Error

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | No Time-Out error occurred since last clear of this bit.               |

| 1     | This bit is automatically set when a Time-Out error has been detected. |

### Bit 2 - PID PID Error

## SAM E70/S70/V70/V71 Family Universal Synchronous Asynchronous Receiver Transc...

#### Figure 46-25. Break Transmission ...... Baud Rate Clock TXD Star ParitySto Bit B D0 D2 D3 D4 D5 D6 D7 Break Transmission End of Break D1 STTBRK = 1 STPBRK = 1 Write US\_CR TXRDY TXEMPTY

#### 46.6.3.14 Receive Break

The receiver detects a break condition when all data, parity and stop bits are low. This corresponds to detecting a framing error with data to 0x00, but FRAME remains low.

When the low stop bit is detected, the receiver asserts US\_CSR.RXBRK. This bit may be cleared by writing a '1' to US\_CR.RSTSTA.

An end of receive break is detected by a high level for at least 2/16 of a bit period in Asynchronous operating mode or one sample at high level in Synchronous operating mode. The end of break detection also asserts US\_CSR.RXBRK bit.

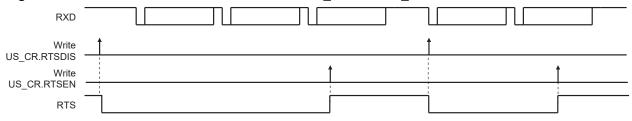

#### 46.6.3.15 Hardware Handshaking

The USART features a hardware handshaking out-of-band flow control. The RTS and CTS pins are used to connect with the remote device, as shown in the following figure.

#### Figure 46-26. Connection with a Remote Device for Hardware Handshaking

| USART |   | Remote<br>Device |

|-------|---|------------------|

| TXD   |   | RXD              |

| RXD   | 4 | TXD              |

| CTS   | • | RTS              |

| RTS   |   | CTS              |

|       |   |                  |

Setting the USART to operate with hardware handshaking is performed by writing the value 0x2 to US\_MR.USART\_MODE.

When hardware handshaking is enabled, the USART displays similar behavior as in standard Synchronous or Asynchronous modes, with the difference that the receiver drives the RTS pin and the level on the CTS pin modifies the behavior of the transmitter, as shown in the following figures. The transmitter can handle hardware handshaking in any case.

#### Figure 46-27. RTS Line Software Control when US\_MR.USART\_MODE = 2

Universal Synchronous Asynchronous Receiver Transc...

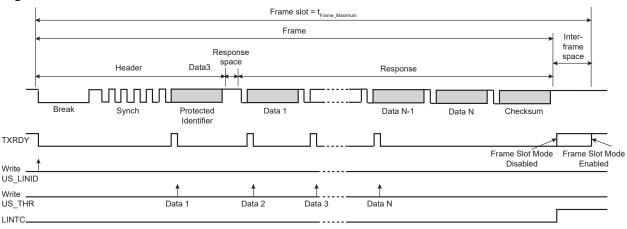

#### Figure 46-44. Frame Slot Mode

#### 46.6.9.14 LIN Errors

#### 46.6.9.14.1 Bit Error

This error is generated in master of slave node configuration, when the USART is transmitting and if the transmitted value on the Tx line is different from the value sampled on the Rx line. If a bit error is detected, the transmission is aborted at the next byte border.

This error is reported by flag US\_CSR.LINBE.

#### 46.6.9.14.2 Inconsistent Synch Field Error

This error is generated in slave node configuration, if the Synch Field character received is other than 0x55.

This error is reported by flag US\_CSR.LINISFE.

#### 46.6.9.14.3 Identifier Parity Error

This error is generated in slave node configuration, if the parity of the identifier is wrong. This error can be generated only if the parity feature is enabled (PARDIS = 0).

This error is reported by flag US\_CSR.LINIPE.

#### 46.6.9.14.4 Checksum Error

This error is generated in master of slave node configuration, if the received checksum is wrong. This flag can be set to 1 only if the checksum feature is enabled (CHKDIS = 0).

This error is reported by flag US\_CSR.LINCE.

#### 46.6.9.14.5 Slave Not Responding Error

This error is generated in master of slave node configuration, when the USART expects a response from another node (NACT = SUBSCRIBE) but no valid message appears on the bus within the time given by the maximum length of the message frame,  $t_{Frame\_Maximum}$  (see Frame Slot Mode). This error is disabled if the USART does not expect any message (NACT = PUBLISH or NACT = IGNORE).

This error is reported by flag US\_CSR.LINSNRE.

#### 46.6.9.14.6 Synch Tolerance Error

This error is generated in slave node configuration if, after the clock synchronization procedure, it appears that the computed baudrate deviation compared to the initial baudrate is superior to the maximum tolerance FTol\_Unsynch (±15%).

This error is reported by flag US\_CSR.LINSTE.

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.6 USART Interrupt Enable Register (SPI\_MODE)

Name:US\_IER (SPI\_MODE)Offset:0x0008Property:Write-only

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

The following configuration values are valid for all listed bit names of this register:

0: No effect

1: Enables the corresponding interrupt.

| Bit    | 31 | 30 | 29   | 28 | 27   | 26   | 25      | 24    |

|--------|----|----|------|----|------|------|---------|-------|

|        |    |    |      |    |      |      |         |       |

| Access |    |    |      |    |      |      |         |       |

| Reset  |    |    |      |    |      |      |         |       |

|        |    |    |      |    |      |      |         |       |

| Bit    | 23 | 22 | 21   | 20 | 19   | 18   | 17      | 16    |

|        |    |    |      |    | NSSE |      |         |       |

| Access |    | •  | •    | •  |      |      | •       |       |

| Reset  |    |    |      |    |      |      |         |       |

|        |    |    |      |    |      |      |         |       |

| Bit    | 15 | 14 | 13   | 12 | 11   | 10   | 9       | 8     |

|        |    |    |      |    |      | UNRE | TXEMPTY |       |

| Access |    |    |      |    |      |      |         |       |

| Reset  |    |    |      |    |      |      |         |       |

|        |    |    |      |    |      |      |         |       |

| Bit    | 7  | 6  | 5    | 4  | 3    | 2    | 1       | 0     |

|        |    |    | OVRE |    |      |      | TXRDY   | RXRDY |

| Access |    |    |      |    |      |      |         |       |

Reset

Bit 19 – NSSE NSS Line (Driving CTS Pin) Rising or Falling Edge Event Interrupt Enable

Bit 10 – UNRE SPI Underrun Error Interrupt Enable

Bit 9 – TXEMPTY TXEMPTY Interrupt Enable

Bit 5 – OVRE Overrun Error Interrupt Enable

Bit 1 – TXRDY TXRDY Interrupt Enable

Bit 0 – RXRDY RXRDY Interrupt Enable

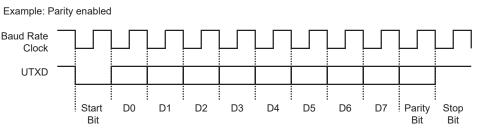

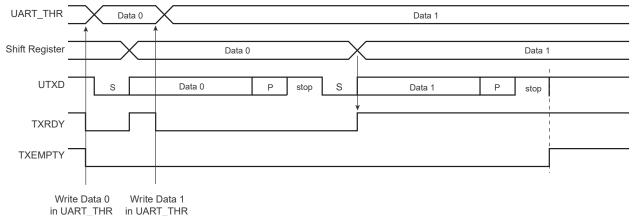

#### Figure 47-9. Character Transmission

#### 47.5.3.3 Transmitter Control

When the transmitter is enabled, the bit TXRDY (Transmitter Ready) is set in UART\_SR. The transmission starts when the programmer writes in the UART\_THR, and after the written character is transferred from UART\_THR to the internal shift register. The TXRDY bit remains high until a second character is written in UART\_THR. As soon as the first character is completed, the last character written in UART\_THR is transferred into the internal shift register and TXRDY rises again, showing that the holding register is empty.

When both the internal shift register and UART\_THR are empty, i.e., all the characters written in UART\_THR have been processed, the TXEMPTY bit rises after the last stop bit has been completed.

#### 47.5.4 DMA Support

Both the receiver and the transmitter of the UART are connected to a DMA Controller (DMAC) channel.

The DMA Controller channels are programmed via registers that are mapped within the DMAC user interface.

#### 47.5.5 Comparison Function on Received Character

When a comparison is performed on a received character, the result of the comparison is reported on the CMP flag in UART\_SR when UART\_RHR is loaded with the new received character. The CMP flag is cleared by writing a one to the RSTSTA bit in UART\_CR.

UART\_CMPR (see UART Comparison Register) can be programmed to provide different comparison methods. These are listed below:

- If VAL1 equals VAL2, then the comparison is performed on a single value and the flag is set to 1 if the received character equals VAL1.

- If VAL1 is strictly lower than VAL2, then any value between VAL1 and VAL2 sets the CMP flag.

### Media Local Bus (MLB)

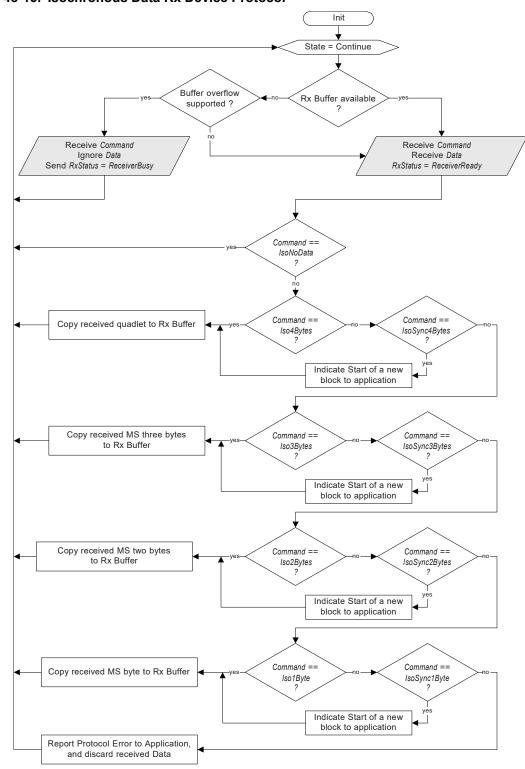

#### Figure 48-15. Isochronous Data Rx Device Protocol

### 48.6.2 Compliance

The MediaLB specification is targeted towards many levels of chip complexity and native intelligence. Therefore, different levels of implementation are allowed to support MediaLB and still remain compliant to this specification. The Physical Layer portion of this specification must be met by all Devices for

## Media Local Bus (MLB)

| Bit Offset | 15       | 14      | 13       | 12 | 11       | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----------|---------|----------|----|----------|----|---|---|---|---|---|---|---|---|---|---|

| 96         | RSTS[4]  | WSTS[4] | rsvd     |    | BD[11:0] |    |   |   |   |   |   |   |   |   |   |   |

| 112        | Reserved |         | BA[13:0] |    |          |    |   |   |   |   |   |   |   |   |   |   |

### Table 48-19. Asynchronous/Control CDT Entry Field Definitions

| Field | Description            | Details                                                                                                                                                                                                                                                                        | Accessibility        |

|-------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| BA    | Buffer Base<br>Address | - BA can start at any byte in the 16k DBR                                                                                                                                                                                                                                      | r,w                  |

| BD    | Buffer Depth           | <ul> <li>BD = size of buffer in bytes - 1</li> <li>Buffer end address = BA + BD</li> <li>BD ≥ max packet length - 1</li> </ul>                                                                                                                                                 | r,w                  |

| RPC   | Read Packet<br>Count   | <ul> <li>Software initializes to zero, hardware updates</li> <li>Used in conjunction with WPC, RPTR and WPTR to<br/>determine if the buffer is empty or full</li> </ul>                                                                                                        | r,w,u <sup>(1)</sup> |

| WPC   | Write Packet<br>Count  | <ul> <li>Software initializes to zero, hardware updates</li> <li>Used in conjunction with RPC, RPTR and WPTR to<br/>determine if the buffer is empty or full</li> </ul>                                                                                                        | r,w,u <sup>(1)</sup> |

| RPTR  | Read Pointer           | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the read address offset within a buffer</li> <li>DMA read address = BA + RPTR</li> </ul>                                                                                                               | r,w,u <sup>(1)</sup> |

| WPTR  | Write Pointer          | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the write address offset within a buffer</li> <li>DMA read address = BA + WPTR</li> </ul>                                                                                                              | r,w,u <sup>(1)</sup> |

| RSTS  | Read Status            | <ul> <li>Software initializes to zero, hardware updates</li> <li>Status states:<sup>(2)</sup></li> <li>x0x00 = idle</li> <li>xx1xx = ReceiverProtocolError response received from</li> <li>Rx Device</li> <li>1xxxx = ReceiverBreak command received from Rx Device</li> </ul> | r,w,u <sup>(1)</sup> |

| WSTS  | Write Status           | <ul> <li>Software initializes to zero, hardware updates</li> <li>Status states:<sup>(2)</sup></li> <li>x0x00 = idle</li> <li>xx1xx = command protocol error detected</li> </ul>                                                                                                | r,w,u <sup>(1)</sup> |

## Digital-to-Analog Converter Controller (DACC)

|        |               |          | <br> |      |      |          |          |        |          |

|--------|---------------|----------|------|------|------|----------|----------|--------|----------|

| Offset | Name          | Bit Pos. |      |      |      |          |          |        |          |

|        |               | 7:0      |      | EOC1 | EOC0 |          |          | TXRDY1 | TXRDY0   |

| 0x2C   |               | 15:8     |      |      |      |          |          |        |          |

| UX2C   | DACC_IMR      | 23:16    |      |      |      |          |          |        |          |

|        |               | 31:24    |      |      |      |          |          |        |          |

|        |               | 7:0      |      | EOC1 | EOC0 |          |          | TXRDY1 | TXRDY0   |

| 0x30   | DACC_ISR      | 15:8     |      |      |      |          |          |        |          |

| 0x30   | DACC_ISK      | 23:16    |      |      |      |          |          |        |          |

|        |               | 31:24    |      |      |      |          |          |        |          |

| 0x34   |               |          |      |      |      |          |          |        |          |

|        | Reserved      |          |      |      |      |          |          |        |          |

| 0x93   |               |          |      |      |      |          |          |        |          |

|        | DACC_ACR      | 7:0      |      |      |      | IBCTLO   | CH1[1:0] | IBCTLC | CH0[1:0] |

| 0x94   |               | 15:8     |      |      |      |          |          |        |          |

| 0,01   |               | 23:16    |      |      |      |          |          |        |          |

|        |               | 31:24    |      |      |      |          |          |        |          |

| 0x98   |               |          |      |      |      |          |          |        |          |

|        | Reserved      |          |      |      |      |          |          |        |          |

| 0xE3   |               |          |      |      |      |          |          |        |          |

|        |               | 7:0      |      |      |      |          |          |        | WPEN     |

| 0xE4   | DACC_WPMR     | 15:8     | <br> |      | WPKE | EY[7:0]  |          |        |          |

| 0/12 1 |               | 23:16    |      |      | WPKE | Y[15:8]  |          |        |          |

|        |               | 31:24    |      |      | WPKE | Y[23:16] | 1        |        |          |

|        |               | 7:0      |      |      |      |          |          |        | WPVS     |

| 0xE8   | DACC_WPSR     | 15:8     |      |      | WPVS | RC[7:0]  |          |        |          |

| 0/20   | 2,100_111 011 | 23:16    |      |      |      |          |          |        |          |

|        |               | 31:24    |      |      |      |          |          |        |          |

### Electrical Characteristics for SAM ...

For the other resolution defined by RES, the code C<sub>i</sub> is extended to the corresponding resolution.

The table below is a computation example for the above formula, where  $V_{VREFP}$  = 3V:

### Table 58-33. Input Voltage Values in Single-ended Mode

| Ci     | Gain      |     |      |       |  |  |

|--------|-----------|-----|------|-------|--|--|

| Signed | Nonsigned | 1   | 2    | 4     |  |  |

| -2048  | 0         | 0   | 0.75 | 1.125 |  |  |

| 0      | 2047      | 1.5 | 1.5  | 1.5   |  |  |

| 2047   | 4095      | 3   | 2.25 | 1.875 |  |  |

### 58.8.4.3 Example of LSB Computation

The LSB is relative to the analog scale  $V_{VREFP}$ .

The term LSB expresses the quantization step in volts, also used for one AFE code variation.

- Single-ended (SE) (ex: V<sub>VREFP</sub> = 3.0V)

- Gain = 1, LSB =  $(3.0V / 4096) = 732 \mu V$

- Gain = 2, LSB = (1.5V / 4096) = 366 μV

- Gain = 4, LSB = (750 mV / 4096) = 183 μV

- Differential (DIFF) (ex: V<sub>VREFP</sub> = 3.0V)

- Gain = 0.5, LSB = (6.0V / 4096) = 1465 μV

- Gain = 1, LSB =  $(3.0V / 4096) = 732 \mu V$

- Gain = 2, LSB = (1.5V / 4096) = 366 μV

The data include the AFE performances, as the PGA and AFE core cannot be separated. The temperature and voltage dependency are given as separate parameters.

#### 58.8.4.4 Gain and Offset Errors

For:

- a given gain error:  $E_G$  (%)

- a given ideal code (C<sub>i</sub>)

- a given offset error: E<sub>O</sub> (LSB of 12 bits)

in 12-bit mode, the actual code (C<sub>A</sub>) is calculated using the following formula

$$C_A = \left(1 + \frac{E_G}{100}\right) \times (C_i - 2047) + 2047 + E_0$$

For higher resolutions, the code can be extended to the corresponding resolution defined by RES.

#### 58.8.4.4.1 Differential Mode

In Differential mode, the offset is defined when the differential input voltage is zero.

## Electrical Characteristics for SAM ...

| Symbol            | VDDIO Supply                                                                              | 1.8V Domain                                                                | 1.8V<br>Domain                                                             | 3.3V<br>Domain | Unit |    |

|-------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------|------|----|

|                   | Parameter                                                                                 | Min                                                                        |                                                                            | Max            |      | -  |

| SMC <sub>18</sub> | NCS low before<br>NWE high                                                                | (NWE_SETUP -<br>NCS_RD_SETUP +<br>NWE_PULSE) ×<br>t <sub>CPMCK</sub> - 3.2 | (NWE_SETUP -<br>NCS_RD_SETUP +<br>NWE_PULSE) ×<br>t <sub>CPMCK</sub> - 2.2 |                | _    | ns |

| HOLD S            | ettings (NWE_HO                                                                           | LD ≠ 0)                                                                    |                                                                            |                |      |    |

| SMC <sub>19</sub> | NWE High to<br>Data OUT,<br>NBS0/A0<br>NBS1, A1, A2–<br>A25 change                        | NWE_HOLD × t <sub>CPMCK</sub><br>- 4.6                                     | NWE_HOLD × t <sub>CPMCK</sub><br>- 3.9                                     | _              | _    | ns |

| SMC <sub>20</sub> | NWE High to<br>NCS Inactive <sup>(1)</sup>                                                | (NWE_HOLD -<br>NCS_WR_HOLD) ×<br>t <sub>CPMCK</sub> - 3.9                  | (NWE_HOLD -<br>NCS_WR_HOLD) ×<br>t <sub>CPMCK</sub> - 3.6                  | -              | -    | ns |

| NO HOL            | D Settings (NWE_                                                                          | _HOLD = 0)                                                                 |                                                                            |                |      |    |

| SMC <sub>21</sub> | NWE High to<br>Data OUT,<br>NBS0/A0<br>NBS1, A1, A2–<br>A25, NCS<br>change <sup>(1)</sup> | 2.1                                                                        | 1.5                                                                        | -              | -    | ns |

#### Note:

Hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "NCS\_WR\_HOLD length" or "NWE\_HOLD length"

### Table 58-63. SMC Write NCS Controlled (WRITE\_MODE = 0)

| Symbol VDDIO Supply |                                      | 1.8V Domain                                                             | 3.3V Domain                                                             | 1.8V<br>Domain | 3.3V<br>Domain | Unit |

|---------------------|--------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|----------------|------|

|                     | Parameter                            | Min                                                                     |                                                                         | Max            |                |      |

| SMC <sub>22</sub>   | Data Out Valid<br>before NCS<br>High | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 2.8                              | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 3.9                              |                |                | ns   |

| SMC <sub>23</sub>   | NCS Pulse<br>Width                   | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 0.9                              | NCS_WR_PULSE ×<br>t <sub>CPMCK</sub> - 0.2                              |                |                | ns   |

| SMC <sub>24</sub>   | A0–A22 valid<br>before NCS<br>low    | NCS_WR_SETUP ×<br>t <sub>CPMCK</sub> - 4.0                              | NCS_WR_SETUP ×<br>t <sub>CPMCK</sub> - 4.6                              |                |                | ns   |

| SMC <sub>25</sub>   | NWE low<br>before NCS<br>high        | (NCS_WR_SETUP -<br>NWE_SETUP + NCS<br>pulse) × t <sub>CPMCK</sub> - 4.6 | (NCS_WR_SETUP -<br>NWE_SETUP + NCS<br>pulse) × t <sub>CPMCK</sub> - 4.6 |                |                | ns   |

## **Electrical Characteristics for SAM E70/S70**

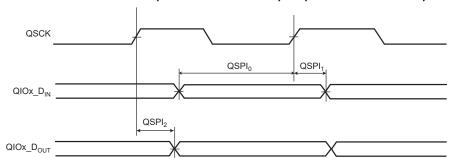

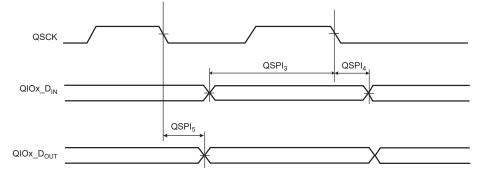

#### 59.13.1.5 QSPI Characteristics

Figure 59-17. QSPI Master Mode with (CPOL= NCPHA = 0) or (CPOL= NCPHA= 1)

Figure 59-18. QSPI Master Mode with (CPOL = 0 and NCPHA=1) or (CPOL=1 and NCPHA= 0)

#### 59.13.1.5.1 Maximum QSPI Frequency

The following formulas give maximum QSPI frequency in Master read and write modes.

$$f_{\text{QSCK}} \text{max} = \frac{1}{QSPI_0(\text{or } QSPI_3) + t_{\text{VALID}}}$$

t<sub>valid</sub> is the slave time response to output data after detecting a QSCK edge.

For a QSPI slave device with  $t_{VALID}$  (or  $t_V$ ) = 12 ns,  $f_{QSCK}$ max = 66 MHz at VDDIO = 3.3V.

For a QSPI Flash memory device with  $t_{VALID}$  (or  $t_V$ ) = 6 ns, the formula returns a value of 112 MHz. In worst case conditions, this exceeds 66 MHz, which is the maximum allowed frequency of the QSPI master. In this case, the limitation is due to the controller and not the slave.

#### Master Write Mode

The QSPI sends data to a slave device only, e.g. an LCD. The limit is given by QSPI<sub>2</sub> (or QSPI<sub>5</sub>) timing. Since it gives a maximum frequency above the maximum pad speed (see I/O Characteristics), the max QSPI frequency is the one from the pad.

#### Master Read Mode

#### 59.13.1.5.2 QSPI Timings

Timings are given in the following domains:

- 1.8V domain: VDDIO from 1.7V to 1.95V, maximum external capacitor = 20 pF

- 3.3V domain: VDDIO from 2.85V to 3.6V, maximum external capacitor = 40 pF.

## **Electrical Characteristics for SAM E70/S70**

## **Electrical Characteristics for SAM E70/S70**

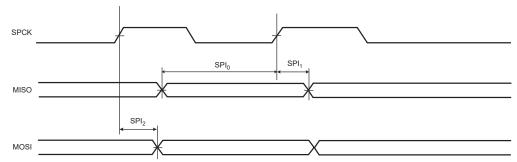

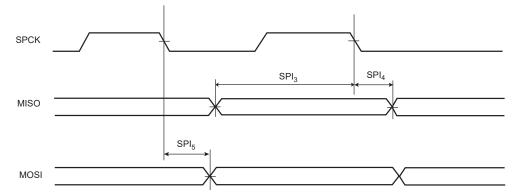

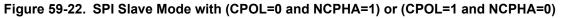

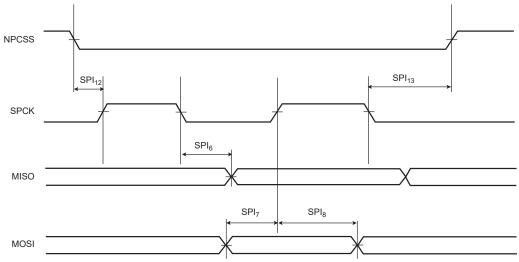

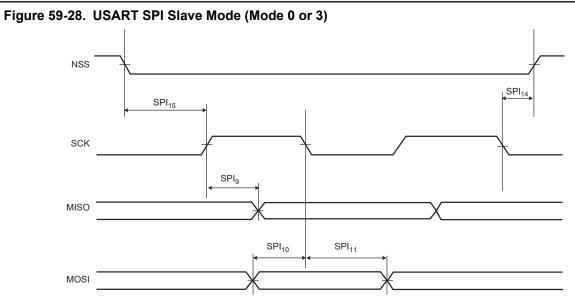

### 59.13.1.11.1 USART SPI Timings

Timings are given in the following domains:

- 1.8V domain: VDDIO from 1.7V to 1.95V, maximum external capacitor = 20 pF

- 3.3V domain: VDDIO from 2.85V to 3.6V, maximum external capacitor = 40 pF

### Table 59-66. USART SPI Timings

| Symbol           | Parameter                            | Conditions                 | Min          | Max          | Unit |  |  |  |  |

|------------------|--------------------------------------|----------------------------|--------------|--------------|------|--|--|--|--|

| Master Mo        |                                      |                            |              |              |      |  |  |  |  |

| SPI0             | SCK Period                           | 1.8V domain<br>3.3V domain | MCK/6        | -            | ns   |  |  |  |  |

| SPI <sub>1</sub> | Input Data Setup Time                | 1.8V domain<br>3.3V domain | 2.8<br>2.5   | -            | ns   |  |  |  |  |

| SPI <sub>2</sub> | Input Data Hold Time                 | 1.8V domain<br>3.3V domain | 0.5<br>0.2   | -            | ns   |  |  |  |  |

| SPI3             | Chip Select Active to Serial Clock   | 1.8V domain<br>3.3V domain | -1.1<br>-0.9 | -            | ns   |  |  |  |  |

| SPI4             | Output Data Setup Time               | 1.8V domain<br>3.3V domain | -1.9<br>-1.9 | 10.9<br>10.4 | ns   |  |  |  |  |

| SPI <sub>5</sub> | Serial Clock to Chip Select Inactive | 1.8V domain<br>3.3V domain | -2.4<br>-2.4 | -1.9<br>-1.9 | ns   |  |  |  |  |

| Slave Mode       | 9                                    |                            |              |              |      |  |  |  |  |

| SPI <sub>6</sub> | SCK falling to MISO                  | 1.8V domain<br>3.3V domain | 3.6<br>2.9   | 16.8<br>13.9 | ns   |  |  |  |  |

| SPI7             | MOSI Setup time before SCK rises     | 1.8V domain                | 2.4          | -            | ns   |  |  |  |  |