Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                |                                                                                                    |

| RAM Size                   | 384К х 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-LQFP                                                                                           |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q21b-ant                         |

|                            |                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Debug and Test Features**

For more information, refer to BDSL files available on www.microchip.com.

### 16.7.9 ID Code Register

Access: Read-only

| 04 00 00 07 00 05 |                                       |    |    |          |            |              |    |  |

|-------------------|---------------------------------------|----|----|----------|------------|--------------|----|--|

| 31                | 30                                    | 29 | 28 | 27       | 26         | 25           | 24 |  |

| VERSION           |                                       |    |    | PART N   | UMBER      |              |    |  |

| 23                | 22                                    | 21 | 20 | 19       | 18         | 17           | 16 |  |

|                   |                                       |    |    | PART NUM | IBER       |              |    |  |

| 15                | 14                                    | 13 | 12 | 11       | 10         | 9            | 8  |  |

| PART NUMBER       |                                       |    |    |          | MANUFACTUF | RER IDENTITY |    |  |

| 7                 | 7     6     5     4     3     2     1 |    |    |          |            |              |    |  |

|                   | MANUFACTURER IDENTITY                 |    |    |          |            |              |    |  |

- VERSION[31:28]: Product Version Number Set to 0x0.

- **PART NUMBER[27:12]: Product Part Number** Set to 0x0.

| PART NUMBER |

|-------------|

| 0x5B3D      |

|             |

- MANUFACTURER IDENTITY[11:1]: Manufacturer ID Set to 0x01F.

- Bit[0]: Required by IEEE Std. 1149.1 Set to 0x1.

| JTAG ID Code |

|--------------|

| 0x5B3D_D03F  |

### Fast Flash Programming Interface (FFPI)

### Table 18-12. Get GP NVM Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]                                                                   |

|------|--------------------|-----------|------------------------------------------------------------------------------|

| 1    | Write handshaking  | CMDE GGPB |                                                                              |

| 2    | Read handshaking   | DATA      | GP NVM Bit Mask Status<br>0 = GP NVM bit is cleared<br>1 = GP NVM bit is set |

### 18.3.5.6 Flash Security Bit Command

A security bit can be set using the Set Security Bit command (SSE). Once the security bit is active, the Fast Flash programming is disabled. No other command can be run. An event on the Erase signal can erase the security bit once the contents of the Flash have been erased.

### Table 18-13. Set Security Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |  |

|------|--------------------|-----------|------------|--|

| 1    | Write handshaking  | CMDE      | SSE        |  |

| 2    | Write handshaking  | DATA      | 0          |  |

Once the security bit is set, it is not possible to access FFPI. The only way to erase the security bit is to erase the Flash.

To erase the Flash, perform the following steps:

- 1. Power off the chip.

- 2. Power on the chip with TST = 0.

- 3. Assert the ERASE signal for at least the ERASE pin assertion time as defined in the section "Electrical Characteristics".

- 4. Power off the chip.

Return to FFPI mode to check that the Flash is erased.

#### 18.3.5.7 Memory Write Command

This command is used to perform a write access to any memory location.

The Memory Write command (WRAM) is optimized for consecutive writes. Write handshaking can be chained; an internal address buffer is automatically increased.

#### Table 18-14. Write Command

| Step | Handshake Sequence | MODE[3:0]            | DATA[15:0]        |  |

|------|--------------------|----------------------|-------------------|--|

| 1    | Write handshaking  | CMDE                 | WRAM              |  |

| 2    | Write handshaking  | ADDR0 Memory Address |                   |  |

| 3    | Write handshaking  | ADDR1                | Memory Address    |  |

| 4    | Write handshaking  | DATA                 | *Memory Address++ |  |

| 5    | Write handshaking  | DATA                 | *Memory Address++ |  |

|      |                    |                      |                   |  |

### 19.4.11 Write Protection Mode Register

| Name:     | MATRIX_WPMR |

|-----------|-------------|

| Offset:   | 0x01E4      |

| Reset:    | 0x0000000   |

| Property: | Read/Write  |

| Bit    | 31           | 30 | 29 | 28   | 27      | 26 | 25 | 24   |  |  |  |

|--------|--------------|----|----|------|---------|----|----|------|--|--|--|

|        | WPKEY[23:16] |    |    |      |         |    |    |      |  |  |  |

| Access | iss          |    |    |      |         |    |    |      |  |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |  |  |

|        |              |    |    |      |         |    |    |      |  |  |  |

| Bit    | 23           | 22 | 21 | 20   | 19      | 18 | 17 | 16   |  |  |  |

|        |              |    |    | WPKE | Y[15:8] |    |    |      |  |  |  |

| Access |              |    |    |      |         |    |    |      |  |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |  |  |

|        |              |    |    |      |         |    |    |      |  |  |  |

| Bit    | 15           | 14 | 13 | 12   | 11      | 10 | 9  | 8    |  |  |  |

|        |              |    |    | WPK  | EY[7:0] |    |    |      |  |  |  |

| Access |              |    |    |      |         |    |    |      |  |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |  |  |

|        |              |    |    |      |         |    |    |      |  |  |  |

| Bit    | 7            | 6  | 5  | 4    | 3       | 2  | 1  | 0    |  |  |  |

|        |              |    |    |      |         |    |    | WPEN |  |  |  |

| Access |              |    |    |      |         |    |    |      |  |  |  |

| Reset  |              |    |    |      |         |    |    | 0    |  |  |  |

### Bits 31:8 - WPKEY[23:0] Write Protection Key

| Value   | Name   | Description                                                                       |

|---------|--------|-----------------------------------------------------------------------------------|

| 0x4D415 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

| 4       |        | Always reads as 0.                                                                |

### Bit 0 – WPEN Write Protection Enable

Refer to the "Register Write Protection" section for the list of registers that can be write-protected.

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Disables the write protection if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII). |

| 1     | Enables the write protection if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII).  |

## 29.3 Register Summary

| Offset | Name      | Bit Pos. |  |         |            |  |  |

|--------|-----------|----------|--|---------|------------|--|--|

|        | SYS_GPBRx | 7:0      |  | GPBR_V  | ALUE[7:0]  |  |  |

| 0×00   |           | 15:8     |  | GPBR_VA | LUE[15:8]  |  |  |

| 0x00   |           | 23:16    |  | GPBR_VA | LUE[23:16] |  |  |

|        |           | 31:24    |  | GPBR_VA | LUE[31:24] |  |  |

## Parallel Input/Output Controller (PIO)

### 32.6.1.6 PIO Output Status Register

| Name:     | PIO_OSR    |

|-----------|------------|

| Offset:   | 0x0018     |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |     |     |     |     |     |     |     |     |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |     |     |     |     |     |     |     |     |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |     |     | •   |     |     |     |     |     |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Access |     |     |     |     |     |     |     |     |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Output Status

| Value | Description                        |

|-------|------------------------------------|

| 0     | The I/O line is a pure input.      |

| 1     | The I/O line is enabled in output. |

## DMA Controller (XDMAC)

| Offset   | Name          | Bit Pos. |                |              |       |             |            |                |                 |       |  |  |

|----------|---------------|----------|----------------|--------------|-------|-------------|------------|----------------|-----------------|-------|--|--|

|          |               | 15:8     |                |              |       |             |            |                |                 |       |  |  |

|          |               | 23:16    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      |                | ROIM         | WBEIM | RBEIM       | FIM        | DIM            | LIM             | BIM   |  |  |

|          |               | 15:8     |                |              |       |             |            |                |                 |       |  |  |

| 0x0418   | XDMAC_CIM15   | 23:16    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      |                | ROIS         | WBEIS | RBEIS       | FIS        | DIS            | LIS             | BIS   |  |  |

|          |               | 15:8     |                |              |       |             |            |                |                 |       |  |  |

| 0x041C   | XDMAC_CIS15   | 23:16    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      |                |              |       | SAI         | 7:0]       |                |                 |       |  |  |

|          |               | 15:8     |                |              |       | SA[         |            |                |                 |       |  |  |

| 0x0420   | XDMAC_CSA15   | 23:16    |                |              |       | SA[2        |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       | SA[3        |            |                |                 |       |  |  |

|          |               | 7:0      |                |              |       | DA          |            |                |                 |       |  |  |

|          |               | 15:8     |                |              |       | DA[         |            |                |                 |       |  |  |

| 0x0424   | XDMAC_CDA15   | 23:16    |                |              |       | DA[<br>DA[2 |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               |          |                |              |       | DA[3        | 1.24]      |                |                 |       |  |  |

|          | XDMAC_CNDA15  | 7:0      | NDA[5:0] NDAIF |              |       |             |            |                |                 |       |  |  |

| 0x0428   |               | 15:8     | NDA[13:6]      |              |       |             |            |                |                 |       |  |  |

|          |               | 23:16    | NDA[21:14]     |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             | 29:22]     |                | 1               |       |  |  |

|          |               | 7:0      |                |              |       | NDVIE       | W[1:0]     | NDDUP          | NDSUP           | NDE   |  |  |

| 0x042C   | XDMAC_CNDC15  | 15:8     |                |              |       |             |            |                |                 |       |  |  |

|          | _             | 23:16    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      |                |              |       | UBLE        | N[7:0]     |                |                 |       |  |  |

| 0x0430   | XDMAC_CUBC15  | 15:8     |                |              |       | UBLE        |            |                |                 |       |  |  |

| 0,0100   |               | 23:16    |                | UBLEN[23:16] |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      |                |              |       | BLEN        | N[7:0]     |                |                 |       |  |  |

| 0x0434   | XDMAC_CBC15   | 15:8     |                |              |       |             |            | BLEN           | <b>I</b> [11:8] |       |  |  |

| 0X0434   | ADIVIAC_CBC15 | 23:16    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             |            |                |                 |       |  |  |

|          |               | 7:0      | MEMSET         | SWREQ        |       | DSYNC       |            | MBSI           | ZE[1:0]         | TYPE  |  |  |

| 0.0400   |               | 15:8     |                | DIF          | SIF   | DWID        | FH[1:0]    |                | CSIZE[2:0]      |       |  |  |

| 0x0438   | XDMAC_CC15    | 23:16    | WRIP           | RDIP         | INITD |             | DAN        | <b>/</b> [1:0] | SAM             | [1:0] |  |  |

|          |               | 31:24    |                |              |       |             | PERID[6:0] |                |                 |       |  |  |

|          |               | 7:0      |                | 1            |       | SDS_M       | ISP[7:0]   |                |                 |       |  |  |

|          | XDMAC_CDS_MSP |          |                |              |       |             | SP[15:8]   |                |                 |       |  |  |

| 0x043C   | 15            | 23:16    |                |              |       |             | ISP[7:0]   |                |                 |       |  |  |

|          |               | 31:24    |                |              |       |             | SP[15:8]   |                |                 |       |  |  |

|          |               | 7:0      |                |              |       |             | S[7:0]     |                |                 |       |  |  |

| 0x0440   | XDMAC_CSUS15  | 15:8     |                |              |       |             | 5[15:8]    |                |                 |       |  |  |

| 5/10 110 |               | 23:16    |                |              |       |             | [23:16]    |                |                 |       |  |  |

|          |               | 20.10    |                |              |       | 0000        | [=0.10]    |                |                 |       |  |  |

### Serial Peripheral Interface (SPI)

last character transfer. Then, another DMA transfer can be started if SPI\_CR.SPIEN has previously been written.

### 41.7.3.6 SPI Direct Access Memory Controller (DMAC)

In both Fixed and Variable modes, the Direct Memory Access Controller (DMAC) can be used to reduce processor overhead.

The fixed peripheral selection allows buffer transfers with a single peripheral. Using the DMAC is an optimal means, as the size of the data transfer between the memory and the SPI is either 8 bits or 16 bits. However, if the peripheral selection is modified, SPI\_MR must be reprogrammed.

The variable peripheral selection allows buffer transfers with multiple peripherals without reprogramming SPI\_MR. Data written in SPI\_TDR is 32 bits wide and defines the real data to be transmitted and the destination peripheral. Using the DMAC in this mode requires 32-bit wide buffers, with the data in the LSBs and the PCS and LASTXFER fields in the MSBs. However, the SPI still controls the number of bits (8 to 16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in terms of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

#### 41.7.3.7 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 slave peripherals by decoding the four chip select lines, NPCS0 to NPCS3 with an external decoder/demultiplexer (see figure below). This can be enabled by setting SPI\_MR.PCSDEC.

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e., one NPCS line driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field on the NPCS lines of either SPI\_MR or SPI\_TDR (depending on PS).

As the SPI sets a default value of 0xF on the chip select lines (i.e., all chip select lines at 1) when not processing any transfer, only 15 peripherals can be decoded.

The SPI has four chip select registers (SPI\_CSR0...SPI\_CSR3). As a result, when external decoding is activated, each NPCS chip select defines the characteristics of up to four peripherals. As an example, SPI\_CRS0 defines the characteristics of the externally decoded peripherals 0 to 3, corresponding to the PCS values 0x0 to 0x3. Consequently, the user has to make sure to connect compatible peripherals on the decoded chip select lines 0 to 3, 4 to 7, 8 to 11 and 12 to 14. The following figure shows this type of implementation.

If SPI\_CSRx.CSAAT bit is used, with or without the DMAC, the Mode Fault detection for NPCS0 line must be disabled. This is not needed for all other chip select lines since Mode Fault detection is only on NPCS0.

### Serial Peripheral Interface (SPI)

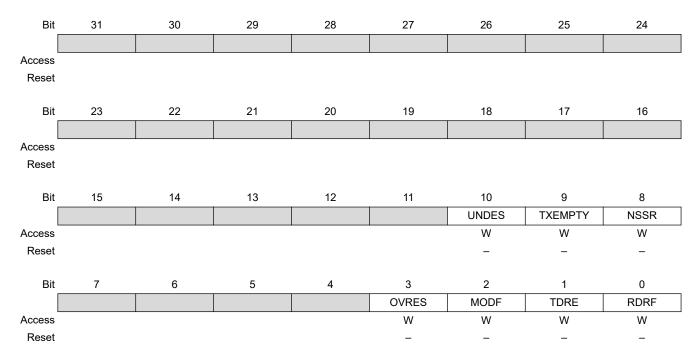

### 41.8.7 SPI Interrupt Disable Register

Name:SPI\_IDROffset:0x18Reset:-Property:Write-only

This register can only be written if the WPITEN bit is cleared in the SPI Write Protection Mode Register. The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Disables the corresponding interrupt.

Bit 10 – UNDES Underrun Error Interrupt Disable

Bit 9 – TXEMPTY Transmission Registers Empty Disable

Bit 8 – NSSR NSS Rising Interrupt Disable

Bit 3 – OVRES Overrun Error Interrupt Disable

Bit 2 – MODF Mode Fault Error Interrupt Disable

Bit 1 – TDRE SPI Transmit Data Register Empty Interrupt Disable

Bit 0 – RDRF Receive Data Register Full Interrupt Disable

## Universal Synchronous Asynchronous Receiver Transc...

| 0             | Baud Rate Clock Disabled                     |                                             |                                    |                                                       |  |  |  |  |

|---------------|----------------------------------------------|---------------------------------------------|------------------------------------|-------------------------------------------------------|--|--|--|--|

| 1 to<br>65535 | CD = Selected<br>Clock /<br>(16 × Baud Rate) | CD = Selected<br>Clock /<br>(8 × Baud Rate) | CD = Selected Clock /<br>Baud Rate | CD = Selected Clock /<br>(FI_DI_RATIO × Baud<br>Rate) |  |  |  |  |

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.43 USART LON IDT Tx Register

| Name:     | US_IDTTX   |

|-----------|------------|

| Offset:   | 0x0080     |

| Reset:    | 0x0        |

| Property: | Read/Write |

This register is relevant only if USART\_MODE = 0x9 in the USART Mode Register.

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28    | 27      | 26 | 25 | 24 |

|--------|----|----|----|-------|---------|----|----|----|

|        |    |    |    |       |         |    |    |    |

| Access |    |    |    |       |         |    |    |    |

| Reset  |    |    |    |       |         |    |    |    |

|        |    |    |    |       |         |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19      | 18 | 17 | 16 |

|        |    |    |    | IDTTX | [23:16] |    |    |    |

| Access |    |    |    |       |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |    |    |    |       |         |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11      | 10 | 9  | 8  |

|        |    |    |    | IDTTX | [15:8]  |    |    |    |

| Access |    |    |    |       |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |    |    |    |       |         |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3       | 2  | 1  | 0  |

|        |    |    |    | IDTTX | X[7:0]  |    |    |    |

| Access |    |    |    |       |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |    |    |    |       |         |    |    |    |

Bits 23:0 – IDTTX[23:0] LON Indeterminate Time after Transmission (comm\_type = 1 mode only)

| Value   | Description                                                     |

|---------|-----------------------------------------------------------------|

| 0-      | LON indeterminate time after transmission in t <sub>bit</sub> . |

| 1677721 |                                                                 |

| 5       |                                                                 |

## SAM E70/S70/V70/V71 Family Universal Asynchronous Receiver Transmitter (UART)

## 47.6 Register Summary

| Offset   | Name      | Bit Pos. |       |         |       |                  |                    |          |         |        |

|----------|-----------|----------|-------|---------|-------|------------------|--------------------|----------|---------|--------|

|          |           | 7:0      | TXDIS | TXEN    | RXDIS | RXEN             | RSTTX              | RSTRX    |         |        |

| 000      |           | 15:8     |       |         |       | REQCLR           |                    |          |         | RSTSTA |

| 0x00     | UART_CR   | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      |       |         |       | FILTER           |                    |          |         |        |

|          |           | 15:8     | CHMC  | DE[1:0] |       | BRSRCCK          |                    | PAR[2:0] |         |        |

| 0x04     | UART_MR   | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      | PARE  | FRAME   | OVRE  |                  |                    |          | TXRDY   | RXRDY  |

|          |           | 15:8     | CMP   |         |       |                  |                    |          | TXEMPTY |        |

| 0x08     | UART_IER  | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      | PARE  | FRAME   | OVRE  |                  |                    |          | TXRDY   | RXRDY  |

|          |           | 15:8     | CMP   |         |       |                  |                    |          | TXEMPTY |        |

| 0x0C     | UART_IDR  | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      | PARE  | FRAME   | OVRE  |                  |                    |          | TXRDY   | RXRDY  |

|          | UART_IMR  | 15:8     | CMP   |         | -     |                  |                    |          | TXEMPTY |        |

| 0x10     |           | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      | PARE  | FRAME   | OVRE  |                  |                    |          | TXRDY   | RXRDY  |

|          | UART_SR   | 15:8     | CMP   |         | 01112 |                  |                    |          | TXEMPTY | TOULDT |

| 0x14     |           | 23:16    | 0     |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      |       |         |       | RXCH             | R[7·0]             |          |         |        |

|          |           | 15:8     |       |         |       |                  | ii ([ <i>1</i> .0] |          |         |        |

| 0x18     | UART_RHR  | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           |          |       |         |       | TYCU             | D[7:0]             |          |         |        |

|          |           | 7:0      |       |         |       | TXCH             | rt[7:0]            |          |         |        |

| 0x1C     | UART_THR  | 15:8     |       |         |       |                  |                    |          |         |        |

|          |           | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      |       |         |       | CD[              |                    |          |         |        |

| 0x20     | UART_BRGR | 15:8     |       |         |       | CD[ <sup>2</sup> | 15:8]              |          |         |        |

|          |           | 23:16    |       |         |       |                  |                    |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

|          |           | 7:0      |       |         |       | VAL1             | [7:0]              |          |         |        |

| 0x24     | UART_CMPR | 15:8     |       | CMPPAR  |       | CMPMODE          |                    |          |         |        |

|          | -         | 23:16    |       |         |       | VAL2             | 2[7:0]             |          |         |        |

|          |           | 31:24    |       |         |       |                  |                    |          |         |        |

| 0x28     |           |          |       |         |       |                  |                    |          |         |        |

| <br>0xE3 | Reserved  |          |       |         |       |                  |                    |          |         |        |

### **Controller Area Network (MCAN)**

### Table 49-9. Tx Event FIFO Element

|    | 31     |     |     | 24       | 23          |     |     |       | 16  | 15 8      | 7 0 |

|----|--------|-----|-----|----------|-------------|-----|-----|-------|-----|-----------|-----|

| E0 | ESI    | XTD | RTR | ID[28:   | 0]          |     |     |       |     |           |     |

| E1 | MM[7:0 | )]  | 1   | <u> </u> | ET<br>[1:0] | FDF | BRS | DLC[3 | :0] | TXTS[15:0 | D]  |

• E0 Bit 31 ESI: Error State Indicator

- 0: Transmitting node is error active.

- 1: Transmitting node is error passive.

- E0 Bit 30 XTD: Extended Identifier

- 0: 11-bit standard identifier.

- 1: 29-bit extended identifier.

- E0 Bit 29 RTR: Remote Transmission Request

- 0: Data frame transmitted.

- 1: Remote frame transmitted.

- E0 Bits 28:0 ID[28:0]: Identifier

Standard or extended identifier depending on bit XTD. A standard identifier is stored into ID[28:18].

• E1 Bits 31:24 MM[7:0]: Message Marker

Copied from Tx Buffer into Tx Event FIFO element for identification of Tx message status.

- E1 Bit 23:22 ET[1:0]: Event Type

- 0: Reserved

- 1: Tx event

- 2: Transmission in spite of cancellation (always set for transmissions in DAR mode)

- 3: Reserved

- E1 Bit 21 FDF: FD Format

- 0: Standard frame format.

- 1: CAN FD frame format (new DLC-coding and CRC).

- E1 Bit 20 BRS: Bit Rate Switch

- 0: Frame transmitted without bit rate switching.

- 1: Frame transmitted with bit rate switching.

- E1 Bits 19:16 DLC[3:0]: Data Length Code

- 0-8: CAN + CAN FD: frame with 0-8 data bytes transmitted.

- 9-15: CAN: frame with 8 data bytes transmitted.

- 9-15: CAN FD: frame with 12/16/20/24/32/48/64 data bytes transmitted

- E1 Bits 15:0 TXTS[15:0]: Tx Timestamp

### Controller Area Network (MCAN)

### 49.6.17 MCAN Interrupt Enable Register

| Name:     | MCAN_IE    |

|-----------|------------|

| Offset:   | 0x54       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

The following configuration values are valid for all listed bit names of this register:

- 0: Disables the corresponding interrupt.

- 1: Enables the corresponding interrupt.

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | ARAE  | PEDE  | PEAE  | WDIE  | BOE   | EWE   |

| Access |       |       | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset  |       |       | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|        | EPE   | ELOE  |       |       | DRXE  | TOOE  | MRAFE | TSWE  |

| Access | R/W   | R/W   |       |       | R/W   | R/W   | R/W   | R/W   |

| Reset  | 0     | 0     |       |       | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

|        | TEFLE | TEFFE | TEFWE | TEFNE | TFEE  | TCFE  | TCE   | HPME  |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        | RF1LE | RF1FE | RF1WE | RF1NE | RF0LE | RF0FE | RF0WE | RF0NE |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Bit 29 – ARAE Access to Reserved Address Enable

- Bit 28 PEDE Protocol Error in Data Phase Enable

- **Bit 27 PEAE** Protocol Error in Arbitration Phase Enable

- Bit 26 WDIE Watchdog Interrupt Enable

- Bit 25 BOE Bus\_Off Status Interrupt Enable

- Bit 24 EWE Warning Status Interrupt Enable

- Bit 23 EPE Error Passive Interrupt Enable

- Bit 22 ELOE Error Logging Overflow Interrupt Enable

- Bit 19 DRXE Message stored to Dedicated Receive Buffer Interrupt Enable

### 51.7.1 PWM Clock Register

| Name:     | PWM_CLK    |

|-----------|------------|

| Offset:   | 0x00       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if bits WPSWS0 and WPHWS0 are cleared in the PWM Write Protection Status Register.

| Bit    | 31  | 30  | 29  | 28   | 27     | 26  | 25     | 24  |

|--------|-----|-----|-----|------|--------|-----|--------|-----|

|        |     |     |     |      |        | PRE | B[3:0] |     |

| Access |     |     |     |      | R/W    | R/W | R/W    | R/W |

| Reset  |     |     |     |      | 0      | 0   | 0      | 0   |

|        |     |     |     |      |        |     |        |     |

| Bit    | 23  | 22  | 21  | 20   | 19     | 18  | 17     | 16  |

|        |     |     |     | DIVE | 8[7:0] |     |        |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W    | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0      | 0   |

|        |     |     |     |      |        |     |        |     |

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9      | 8   |

|        |     |     |     |      |        | PRE | A[3:0] |     |

| Access |     |     |     |      | R/W    | R/W | R/W    | R/W |

| Reset  |     |     |     |      | 0      | 0   | 0      | 0   |

|        |     |     |     |      |        |     |        |     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1      | 0   |

|        |     |     |     | DIVA | [7:0]  |     |        |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W    | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0      | 0   |

Bits 27:24 – PREB[3:0] CLKB Source Clock Selection

| Value | Name        | Description           |

|-------|-------------|-----------------------|

| 0     | CLK         | Peripheral clock      |

| 1     | CLK_DIV2    | Peripheral clock/2    |

| 2     | CLK_DIV4    | Peripheral clock/4    |

| 3     | CLK_DIV8    | Peripheral clock/8    |

| 4     | CLK_DIV16   | Peripheral clock/16   |

| 5     | CLK_DIV32   | Peripheral clock/32   |

| 6     | CLK_DIV64   | Peripheral clock/64   |

| 7     | CLK_DIV128  | Peripheral clock/128  |

| 8     | CLK_DIV256  | Peripheral clock/256  |

| 9     | CLK_DIV512  | Peripheral clock/512  |

| 10    | CLK_DIV1024 | Peripheral clock/1024 |

| Other | -           | Reserved              |

Bits 23:16 - DIVB[7:0] CLKB Divide Factor

## 52. Analog Front-End Controller (AFEC)

### 52.1 Description

The Analog Front-End Controller (AFEC) is based on an Analog Front-End (AFE) cell integrating a 12-bit Analog-to-Digital Converter (ADC), a Programmable Gain Amplifier (PGA), a Digital-to-Analog Converter (DAC) and two 6-to-1 analog multiplexers, making possible the analog-to-digital conversions of 12 analog lines (in single Sample-and-Hold mode) or two simultaneous conversions of 6 analog lines (in dual Sample-and-Hold mode). The conversions extend from 0V to VREFP. The AFEC supports a 12-bit resolution mode which can be extended up to a 16-bit resolution by digital averaging.

Conversion results are reported in a common register for all channels, as well as in a channel-dedicated register.

Software trigger, external trigger on rising edge of the AFE\_ADTRG pin or internal triggers from Timer Counter output(s) are configurable.

The comparison circuitry allows automatic detection of values below a threshold, higher than a threshold, in a given range or outside the range. Thresholds and ranges are fully configurable.

The AFEC internal fault output is directly connected to PWM Fault input. This input can be asserted by means of comparison circuitry in order to immediately put the PWM outputs in a safe state (pure combinational path).

The AFEC also integrates a Sleep mode and a conversion sequencer and connects with a DMA channel. These features reduce both power consumption and processor intervention.

The AFEC has a selectable single-ended or fully differential input and benefits from a 2-bit programmable gain. A set of reference voltages is generated internally from a single external reference voltage node that may be equal to the analog supply voltage. An external decoupling capacitance is required for noise filtering.

A digital error correction circuit based on the multi-bit redundant signed digit (RSD) algorithm is employed in order to reduce INL and DNL errors.

Finally, the user can configure AFE timings, such as startup time and tracking time.

### 52.2 Embedded Characteristics

- 12-bit Resolution up to 16-bit Resolution by Digital Averaging

- Wide Range of Power Supply Operation

- Selectable Single-ended or Differential Input Voltage

- Selectable Single or Dual Sample-and-Hold Mode

- Programmable Gain for Maximum Full-Scale Input Range 0–V<sub>DD</sub>

- Programmable Offset Per Channel

- Automatic Correction of Offset and Gain Errors

- Integrated Multiplexers Offering Up to 12 Independent Analog Inputs

- Individual Enable and Disable of Each Channel

- Hardware or Software Trigger

- External trigger pin

## Analog Front-End Controller (AFEC)

### 52.7.16 AFEC Channel Gain Register

| Name:     | AFEC_CGR   |

|-----------|------------|

| Offset:   | 0x54       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the AFEC Write Protection Mode Register.

| Bit    | 31   | 30      | 29   | 28      | 27   | 26     | 25   | 24     |

|--------|------|---------|------|---------|------|--------|------|--------|

|        |      |         |      |         |      |        |      |        |

| Access |      | •       | •    | •       |      |        | •    |        |

| Reset  |      |         |      |         |      |        |      |        |

|        |      |         |      |         |      |        |      |        |

| Bit    | 23   | 22      | 21   | 20      | 19   | 18     | 17   | 16     |

|        | GAIN | 11[1:0] | GAIN | 10[1:0] | GAIN | 9[1:0] | GAIN | 8[1:0] |

| Access | R/W  | R/W     | R/W  | R/W     | R/W  | R/W    | R/W  | R/W    |

| Reset  | 0    | 0       | 0    | 0       | 0    | 0      | 0    | 0      |

|        |      |         |      |         |      |        |      |        |

| Bit    | 15   | 14      | 13   | 12      | 11   | 10     | 9    | 8      |

|        | GAIN | 7[1:0]  | GAIN | 6[1:0]  | GAIN | 5[1:0] | GAIN | 4[1:0] |

| Access | R/W  | R/W     | R/W  | R/W     | R/W  | R/W    | R/W  | R/W    |

| Reset  | 0    | 0       | 0    | 0       | 0    | 0      | 0    | 0      |

|        |      |         |      |         |      |        |      |        |

| Bit    | 7    | 6       | 5    | 4       | 3    | 2      | 1    | 0      |

|        | GAIN | 3[1:0]  | GAIN | 2[1:0]  | GAIN | 1[1:0] | GAIN | 0[1:0] |

| Access | R/W  | R/W     | R/W  | R/W     | R/W  | R/W    | R/W  | R/W    |

| Reset  | 0    | 0       | 0    | 0       | 0    | 0      | 0    | 0      |

**Bits 0:1, 2:3, 4:5, 6:7, 8:9, 10:11, 12:13, 14:15, 16:17, 18:19, 20:21, 22:23 – GAINx** Gain for Channel x Gain applied on input of Analog Front-End.

See section AFEC Channel Differential Register for a description of DIFFx.

| GAINx | Gain Applied |           |  |  |  |

|-------|--------------|-----------|--|--|--|

|       | DIFFx = 0    | DIFFx = 1 |  |  |  |

| 0     | 1            | 1         |  |  |  |

| 1     | 2            | 2         |  |  |  |

| 2     | 4            | 4         |  |  |  |

| 3     | 4            | 4         |  |  |  |

## **Advanced Encryption Standard (AES)**

#### Bit 15 – LOD Last Output Data Mode

Awarning In DMA mode, reading to the Output Data registers before the last data encryption/decryption process may lead to unpredictable results.

| Value | Description                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No effect.                                                                                                                                                                                                             |

|       | After each end of encryption/decryption, the output data are available either on the output data registers (Manual and Auto modes) or at the address specified in the Channel Buffer Transfer Descriptor for DMA mode. |

|       | In Manual and Auto modes, the DATRDY flag is cleared when at least one of the Output Data registers is read.                                                                                                           |

| 1     | The DATRDY flag is cleared when at least one of the Input Data Registers is written.<br>No more Output Data Register reads are necessary between consecutive encryptions/<br>decryptions (see Last Output Data Mode).  |

### Bits 14:12 – OPMOD[2:0] Operating Mode

For CBC-MAC operating mode, set OPMOD to CBC and LOD to 1.

| Value | Name | Description                                 |

|-------|------|---------------------------------------------|

| 0     | ECB  | ECB: Electronic Codebook mode               |

| 1     | CBC  | CBC: Cipher Block Chaining mode             |

| 2     | OFB  | OFB: Output Feedback mode                   |

| 3     | CFB  | CFB: Cipher Feedback mode                   |

| 4     | CTR  | CTR: Counter mode (16-bit internal counter) |

| 5     | GCM  | GCM: Galois/Counter mode                    |

### Bits 11:10 - KEYSIZE[1:0] Key Size

| Value | Name   | Description              |

|-------|--------|--------------------------|

| 0     | AES128 | AES Key Size is 128 bits |

| 1     | AES192 | AES Key Size is 192 bits |

| 2     | AES256 | AES Key Size is 256 bits |

### Bits 9:8 - SMOD[1:0] Start Mode

If a DMA transfer is used, configure SMOD to 2. See DMA Mode for more details.

| Value | Name          | Description                             |

|-------|---------------|-----------------------------------------|

| 0     | MANUAL_START  | Manual Mode                             |

| 1     | AUTO_START    | Auto Mode                               |

| 2     | IDATAR0_START | AES_IDATAR0 access only Auto Mode (DMA) |

## Bits 7:4 – PROCDLY[3:0] Processing Delay

Processing Time =  $N \times (PROCDLY + 1)$

### where

• N = 10 when KEYSIZE = 0

## Advanced Encryption Standard (AES)

### 57.5.3 AES Interrupt Enable Register

Name:AES\_IEROffset:0x10Reset:-Property:Write-only

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24     |

|--------|----|----|----|----|----|----|----|--------|

|        |    |    |    |    |    |    |    |        |

| Access |    |    |    |    |    |    |    |        |

| Reset  |    |    |    |    |    |    |    |        |

|        |    |    |    |    |    |    |    |        |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     |

|        |    |    |    |    |    |    |    | TAGRDY |

| Access |    |    |    |    |    |    |    | W      |

| Reset  |    |    |    |    |    |    |    | _      |

|        |    |    |    |    |    |    |    |        |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      |

|        |    |    |    |    |    |    |    | URAD   |

| Access |    |    |    |    |    |    |    | W      |

| Reset  |    |    |    |    |    |    |    | _      |

|        |    |    |    |    |    |    |    |        |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0      |

|        |    |    |    |    |    |    |    | DATRDY |

| Access |    |    |    |    |    |    | •  | W      |

| Reset  |    |    |    |    |    |    |    | _      |

|        |    |    |    |    |    |    |    |        |

Bit 16 – TAGRDY GCM Tag Ready Interrupt Enable

Bit 8 – URAD Unspecified Register Access Detection Interrupt Enable

Bit 0 – DATRDY Data Ready Interrupt Enable

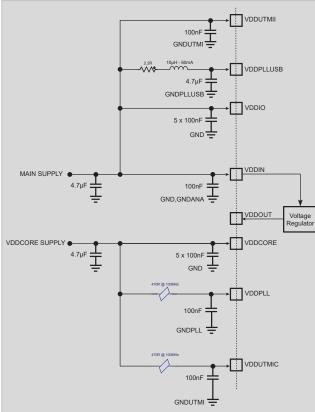

### **Schematic Checklist**

Power Supplies Schematic Example With Separate Power Supplies 60.3 Boot Program Hardware Constraints

Component values are given only as a typical example.

Note:

Note: Restrictions

With main supply < 3.0 V, USB is not usable.

With main supply < 2.0 V, AFE, DAC and Analog comparator are not usable.

With main supply and VDDIN > 3.0 V, all peripherals are usable.

| Signal Name | Recommended Pin<br>Connection                                                             | Description                                                                                                                                            |

|-------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDIN       | Decoupling/filtering<br>capacitors<br>(100 nF and 4.7 µF) <sup>(1,</sup><br><sub>2)</sub> | Powers the voltage regulator, AFE, DAC, and Analog<br>comparator power supply<br>Supply ripple must not exceed 20 mVrms for 10 kHz to<br>20 MHz range. |

|             |                                                                                           | <b>WARNING</b> VDDIN and VDDIO must have the same level and must always be higher than VDDCORE.                                                        |

## **Revision History**

| Date      | Changes                                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Section 25.5.2 "Reinforced Safety Watchdog Timer Mode Register": bit 14 now reserved.                                                                                                                                      |

|           | Section 26. "Reset Controller (RSTC)"<br>Section 26.4.3.1 "General Reset": removed reference to NRSTB.                                                                                                                     |

|           | Table 26.5 "Reset Controller (RSTC) User Interface": updated reset value for RSTC_MR.                                                                                                                                      |

|           | Section 27. "Real-time Clock (RTC)"<br>Updated Section 27.5.7 "RTC Accurate Clock Calibration".                                                                                                                            |

|           | Figure 27-4, "Calibration Circuitry Waveforms": corrected two instances of "3,906 ms" to "3.906 ms".                                                                                                                       |

|           | Table 27-2 "Register Mapping": corrected reset for RTC_CALR. Added offset 0xCC as reserved. Added RTC_WPMR at offset 0xE4                                                                                                  |

|           | Section 27.6.1 "RTC Control Register": updated descriptions of value '0' for bits UPDTIM and UPDCAL.                                                                                                                       |

|           | Added Section 27.6.13 "RTC Write Protection Mode Register".                                                                                                                                                                |

|           | Added write protection for Section 27.6.1 "RTC Control Register", Section 27.6.2 "RTC<br>Mode Register", Section 27.6.5 "RTC Time Alarm Register" and Section 27.6.6 "RTC<br>Calendar Alarm Register".                     |

|           | Section 30. "General Purpose Backup Registers (GPBR)"<br>Corrected total size of backup registers.                                                                                                                         |

| 08-Feb-16 | Section 31. "Clock Generator"<br>Section 31.2 "Embedded Characteristics": updated bullet on embedded RC oscillator.                                                                                                        |

|           | Figure 31-3, "Main Clock Block Diagram": renamed "3-20 MHz Crystal or Ceramic Resonator Oscillator" to "Main Crystal or Ceramic Resonator Oscillator". Renamed "3-20 MHz Oscillator Counter" to "Main Oscillator Counter". |

|           | Section 31.5.1 "Embedded 4/8/12 MHz RC Oscillator": changed last paragraph beginning<br>"The user can adjust the value".                                                                                                   |

|           | Section 31.5.4 "Main Clock Source Selection": added that the RC oscillator must be selected for Wait mode.                                                                                                                 |

|           | Updated Section 31.5.6 "Main Clock Frequency Counter".                                                                                                                                                                     |

|           | Updated Section 31.5.7 "Switching Main Clock between the RC Oscillator and Crystal Oscillator".                                                                                                                            |

|           | Updated Section 31.6.1 "Divider and Phase Lock Loop Programming" with paragraph on correct programming of the multiplication factor of the PLL.                                                                            |

|           | Section 31.7 "UTMI Phase Lock Loop Programming": deleted sentence on crystal requirements for USB.                                                                                                                         |

|           | Section 32. "Power Management Controller (PMC)"<br>Section 32.1 "Description": corrected list of oscillators that can be trimmed by software.                                                                              |