Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                                 |

| Speed                      | 300MHz                                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |

| Number of I/O              | 114                                                                                                |

| Program Memory Size        | 2MB (2M × 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                              |

| EEPROM Size                | -                                                                                                  |

| RAM Size                   | 384K x 8                                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                              |

| Oscillator Type            | Internal                                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                 |

| Mounting Type              | Surface Mount                                                                                      |

| Package / Case             | 144-LFBGA                                                                                          |

| Supplier Device Package    | 144-LFBGA (10x10)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame70q21b-cn                          |

|                            |                                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 32.6. Register Summary                                       | 362 |

|--------------------------------------------------------------|-----|

| 33. External Bus Interface (EBI)                             |     |

| 33.1. Description                                            |     |

| 33.2. Embedded Characteristics                               |     |

| 33.3. EBI Block Diagram                                      |     |

| 33.4. I/O Lines Description                                  |     |

| 33.5. Application Example                                    | 427 |

| 34. SDRAM Controller (SDRAMC)                                | 431 |

| 34.1. Description                                            | 431 |

| 34.2. Embedded Characteristics                               |     |

| 34.3. Signal Description                                     |     |

| 34.4. Software Interface/SDRAM Organization, Address Mapping | 432 |

| 34.5. Product Dependencies                                   |     |

| 34.6. Functional Description                                 | 435 |

| 34.7. Register Summary                                       | 442 |

| 35. Static Memory Controller (SMC)                           | 461 |

| 35.1. Description                                            |     |

| 35.2. Embedded Characteristics                               |     |

| 35.3. I/O Lines Description                                  | 461 |

| 35.4. Multiplexed Signals                                    |     |

| 35.5. Product Dependencies                                   |     |

| 35.6. External Memory Mapping                                |     |

| 35.7. Connection to External Devices                         |     |

| 35.8. Application Example                                    | 467 |

| 35.9. Standard Read and Write Protocols                      | 469 |

| 35.10. Scrambling/Unscrambling Function                      |     |

| 35.11. Automatic Wait States                                 |     |

| 35.12. Data Float Wait States                                |     |

| 35.13. External Wait                                         | 485 |

| 35.14. Slow Clock Mode                                       |     |

| 35.15. Asynchronous Page Mode                                | 491 |

| 35.16. Register Summary                                      |     |

| 36. DMA Controller (XDMAC)                                   |     |

| 36.1. Description                                            | 508 |

| 36.2. Embedded Characteristics                               |     |

| 36.3. Block Diagram                                          |     |

| 36.4. DMA Controller Peripheral Connections                  | 509 |

| 36.5. Functional Description                                 | 511 |

| 36.6. Linked List Descriptor Operation                       | 515 |

| 36.7. XDMAC Maintenance Software Operations                  | 517 |

| 36.8. XDMAC Software Requirements                            | 518 |

| 36.9. Register Summary                                       | 519 |

| 37. Image Sensor Interface (ISI)                             | 590 |

All lock regions must be unlocked before the Full Erase command by using the CLB command. Otherwise, the erase command is aborted and no page is erased.

#### Table 18-8. Full Erase Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |  |

|------|--------------------|-----------|------------|--|

| 1    | Write handshaking  | CMDE      | EA         |  |

| 2    | Write handshaking  | DATA      | 0          |  |

#### 18.3.5.4 Flash Lock Commands

Lock bits can be set using WPL or EWPL commands. They can also be set by using the Set Lock command (SLB). With this command, several lock bits can be activated. A Bit Mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first lock bit is activated.

In the same way, the Clear Lock command (CLB) is used to clear lock bits.

Table 18-9. Set and Clear Lock Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |  |

|------|--------------------|-----------|------------|--|

| 1    | Write handshaking  | CMDE      | SLB or CLB |  |

| 2    | Write handshaking  | DATA      | Bit Mask   |  |

Lock bits can be read using Get Lock Bit command (GLB). The n<sup>th</sup> lock bit is active when the bit n of the bit mask is set.

#### Table 18-10. Get Lock Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]                                                             |

|------|--------------------|-----------|------------------------------------------------------------------------|

| 1    | Write handshaking  | CMDE      | GLB                                                                    |

| 2    | Read handshaking   | DATA      | Lock Bit Mask Status<br>0 = Lock bit is cleared<br>1 = Lock bit is set |

#### 18.3.5.5 Flash General-purpose NVM Commands

General-purpose NVM bits (GP NVM bits) can be set using the Set GPNVM command (SGPB). This command also activates GP NVM bits. A bit mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first GP NVM bit is activated.

In the same way, the Clear GPNVM command (CGPB) is used to clear general-purpose NVM bits. The general-purpose NVM bit is deactivated when the corresponding bit in the pattern value is set to 1.

#### Table 18-11. Set/Clear GP NVM Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]               |

|------|--------------------|-----------|--------------------------|

| 1    | Write handshaking  | CMDE      | SGPB or CGPB             |

| 2    | Write handshaking  | DATA      | GP NVM bit pattern value |

General-purpose NVM bits can be read using the Get GPNVM Bit command (GGPB). The n<sup>th</sup> GP NVM bit is active when bit n of the bit mask is set.

#### 19.4.11 Write Protection Mode Register

| Name:     | MATRIX_WPMR |

|-----------|-------------|

| Offset:   | 0x01E4      |

| Reset:    | 0x0000000   |

| Property: | Read/Write  |

| Bit    | 31           | 30 | 29 | 28   | 27      | 26 | 25 | 24   |  |

|--------|--------------|----|----|------|---------|----|----|------|--|

|        | WPKEY[23:16] |    |    |      |         |    |    |      |  |

| Access | SS           |    |    |      |         |    |    |      |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |

|        |              |    |    |      |         |    |    |      |  |

| Bit    | 23           | 22 | 21 | 20   | 19      | 18 | 17 | 16   |  |

|        |              |    |    | WPKE | Y[15:8] |    |    |      |  |

| Access |              |    |    |      |         |    |    |      |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |

|        |              |    |    |      |         |    |    |      |  |

| Bit    | 15           | 14 | 13 | 12   | 11      | 10 | 9  | 8    |  |

|        |              |    |    | WPK  | EY[7:0] |    |    |      |  |

| Access |              |    |    |      |         |    |    |      |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0    |  |

|        |              |    |    |      |         |    |    |      |  |

| Bit    | 7            | 6  | 5  | 4    | 3       | 2  | 1  | 0    |  |

|        |              |    |    |      |         |    |    | WPEN |  |

| Access |              |    |    |      |         |    |    |      |  |

| Reset  |              |    |    |      |         |    |    | 0    |  |

#### Bits 31:8 - WPKEY[23:0] Write Protection Key

| Value   | Name   | Description                                                                       |

|---------|--------|-----------------------------------------------------------------------------------|

| 0x4D415 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

| 4       |        | Always reads as 0.                                                                |

#### Bit 0 – WPEN Write Protection Enable

Refer to the "Register Write Protection" section for the list of registers that can be write-protected.

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Disables the write protection if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII). |

| 1     | Enables the write protection if WPKEY corresponds to 0x4D4154 ("MAT" in ASCII).  |

3. When programming is completed, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the corresponding interrupt line of the interrupt controller is activated.

Two errors can be detected in EEFC\_FSR after this sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Flash Error: At the end of the programming, the WriteVerify test of the Flash memory has failed.

The sequence to erase the user signature area is the following:

- 1. Execute the 'Erase User Signature' command by writing EEFC\_FCR.FCMD with the EUS command. Field EEFC\_FCR.FARG is meaningless.

- 2. When programming is completed, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the corresponding interrupt line of the interrupt controller is activated.

Two errors can be detected in EEFC\_FSR after this sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Flash Error: At the end of the programming, the EraseVerify test of the Flash memory has failed.

#### 22.4.3.10 ECC Errors and Corrections

The Flash embeds an ECC module able to correct one unique error and able to detect two errors. The errors are detected while a read access is performed into memory array and stored in EEFC\_FSR (see "EEFC Flash Status Register"). The error report is kept until EEFC\_FSR is read.

There is one flag for a unique error on lower half part of the Flash word (64 LSB) and one flag for the upper half part (MSB). The multiple errors are reported in the same way.

Due to the anticipation technique to improve bandwidth throughput on instruction fetch, a reported error can be located in the next sequential Flash word compared to the location of the instruction being executed, which is located in the previously fetched Flash word.

If a software routine processes the error detection independently from the main software routine, the entire Flash located software must be rewritten because there is no storage of the error location.

If only a software routine is running to program and check pages by reading EEFC\_FSR, the situation differs from the previous case. Performing a check for ECC unique errors just after page programming completion involves a read of the newly programmed page. This read sequence is viewed as data accesses and is not optimized by the Flash controller. Thus, in case of unique error, only the current page must be reprogrammed.

#### 22.4.4 Register Write Protection

To prevent any single software error from corrupting EEFC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the "EEFC Write Protection Mode Register" (EEFC\_WPMR).

The following register can be write-protected:

"EEFC Flash Mode Register"

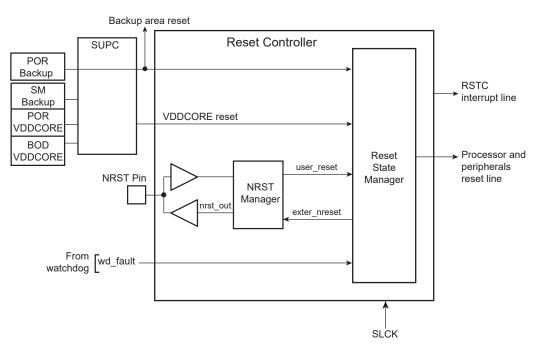

# 26. Reset Controller (RSTC)

### 26.1 Description

The Reset Controller (RSTC), driven by Power-On Reset (POR) cells, software, external reset pin and peripheral events, handles all the resets of the system without any external components. It reports which reset occurred last.

The RSTC also drives simultaneously the external reset and the peripheral and processor resets.

## 26.2 Embedded Characteristics

- Driven by embedded POR, software, external reset pin and peripheral events

- Management of all system resets, including:

- External devices through the NRST pin

- Processor

- Peripheral set

- Reset source status:

- Status of the last reset

- Either VDDCORE and VDDIO POR, Software Reset, User Reset, Watchdog Reset

- External reset signal control and shaping

### 26.3 Block Diagram

#### Figure 26-1. Reset Controller Block Diagram

### Real-time Clock (RTC)

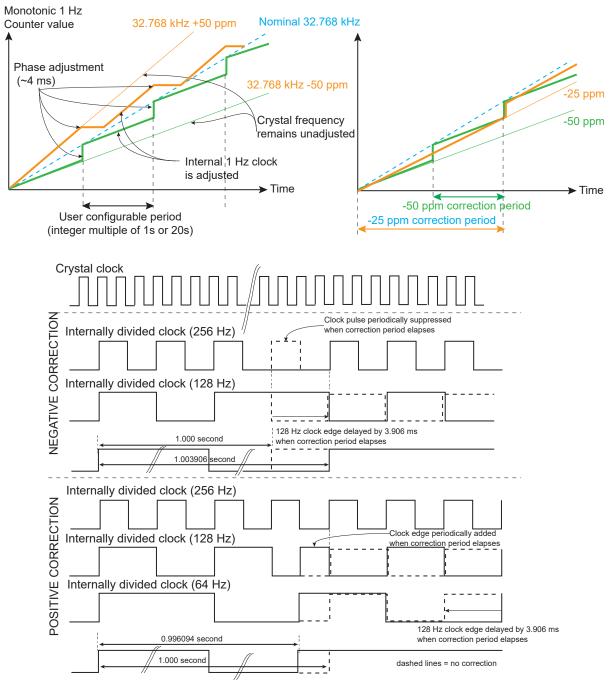

#### Figure 27-5. Calibration Circuitry Waveforms

The inaccuracy of a crystal oscillator at typical room temperature (±20 ppm at 20–25 °C) can be compensated if a reference clock/signal is used to measure such inaccuracy. This kind of calibration operation can be set up during the final product manufacturing by means of measurement equipment embedding such a reference clock. The correction of value must be programmed into the (RTC\_MR), and this value is kept as long as the circuitry is powered (backup area). Removing the backup power supply cancels this calibration. This room temperature calibration can be further processed by means of the networking capability of the target application.

To ease the comparison of the inherent crystal accuracy with the reference clock/signal during manufacturing, an internal prescaled 32.768 kHz clock derivative signal can be assigned to drive RTC

© 2018 Microchip Technology Inc.

## **Power Management Controller (PMC)**

#### 31.20.27 PMC Oscillator Calibration Register

| Name:     | PMC_OCR    |  |  |  |

|-----------|------------|--|--|--|

| Offset:   | 0x0110     |  |  |  |

| Reset:    | 0x00404040 |  |  |  |

| Property: | Read/Write |  |  |  |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31    | 30 | 29 | 28 | 27         | 26 | 25 | 24 |

|--------|-------|----|----|----|------------|----|----|----|

|        |       |    |    |    |            |    |    |    |

| Access |       |    |    |    | -          |    |    |    |

| Reset  |       |    |    |    |            |    |    |    |

|        |       |    |    |    |            |    |    |    |

| Bit    | 23    | 22 | 21 | 20 | 19         | 18 | 17 | 16 |

|        | SEL12 |    |    |    | CAL12[6:0] |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

|        |       |    |    |    |            |    |    |    |

| Bit    | 15    | 14 | 13 | 12 | 11         | 10 | 9  | 8  |

|        | SEL8  |    |    |    | CAL8[6:0]  |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

|        |       |    |    |    |            |    |    |    |

| Bit    | 7     | 6  | 5  | 4  | 3          | 2  | 1  | 0  |

|        | SEL4  |    |    |    | CAL4[6:0]  |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

Bit 23 – SEL12 Selection of Main RC Oscillator Calibration Bits for 12 MHz

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Factory-determined value stored in Flash memory.       |

| 1     | Value written by user in CAL12 field of this register. |

**Bits 22:16 – CAL12[6:0]** Main RC Oscillator Calibration Bits for 12 MHz Calibration bits applied to the RC Oscillator when SEL12 is set.

Bit 15 – SEL8 Selection of Main RC Oscillator Calibration Bits for 8 MHz

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Factory-determined value stored in Flash memory.      |

| 1     | Value written by user in CAL8 field of this register. |

**Bits 14:8 – CAL8[6:0]** Main RC Oscillator Calibration Bits for 8 MHz Calibration bits applied to the RC Oscillator when SEL8 is set.

Bit 7 – SEL4 Selection of Main RC Oscillator Calibration Bits for 4 MHz

## **Power Management Controller (PMC)**

#### 31.20.28 PMC SleepWalking Enable Register 0

Name:PMC\_SLPWK\_ER0Offset:0x0114Property:Write-only

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | PID31 | PID30 | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| Access |       |       | ·     |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

|        |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|        | PID23 | PID22 | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| Access |       |       | •     |       |       |       |       | •     |

| Reset  |       |       |       |       |       |       |       |       |

|        |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

|        | PID15 | PID14 | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

|        |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        | PID7  |       |       |       |       |       |       |       |

| Access |       |       |       |       |       |       |       |       |

Reset

Bits 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – PIDx Peripheral x SleepWalking Enable

Not all PIDs can be configured with asynchronous partial wake-up.

Only the following PID can be configured with asynchronous partial wake-up: UARTx and TWIHSx.

The clock of the peripheral must be enabled before using its asynchronous partial wake-up (SleepWalking) function (its associated PIDx field in PMC Peripheral Clock Status Register 0 or PMC Peripheral Clock Status Register 1 is set to '1').

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | No effect.                                                                                          |

| 1     | The asynchronous partial wakeup (SleepWalking) function of the corresponding peripheral is enabled. |

|       | Note: "PIDx" refers to identifiers as defined in the section "Peripheral Identifiers"               |

# **GMAC** - Ethernet MAC

| Offset | Name            | Bit Pos. |       |             |      |         |          |       |       |  |  |  |

|--------|-----------------|----------|-------|-------------|------|---------|----------|-------|-------|--|--|--|

|        |                 | 7:0      | TCOMP | TFC         | RLEX |         |          | RXUBR | RCOMP |  |  |  |

| 0x0400 | GMAC_ISRPQ1     | 15:8     |       |             |      |         | HRESP    | ROVR  |       |  |  |  |

|        |                 | 23:16    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 7:0      | TCOMP | TFC         | RLEX |         |          | RXUBR | RCOMP |  |  |  |

| 0x0404 | GMAC_ISRPQ2     | 15:8     |       |             |      |         | HRESP    | ROVR  |       |  |  |  |

|        |                 | 23:16    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 7:0      | TCOMP | TFC         | RLEX |         |          | RXUBR | RCOMP |  |  |  |

| 0x0408 | GMAC_ISRPQ3     | 15:8     |       |             |      |         | HRESP    | ROVR  |       |  |  |  |

| 070400 |                 | 23:16    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 7:0      | TCOMP | TFC         | RLEX |         |          | RXUBR | RCOMP |  |  |  |

| 0x040C | GMAC ISPRO4     | 15:8     |       |             |      |         | HRESP    | ROVR  |       |  |  |  |

| 070400 | GMAC_ISRPQ4     | 23:16    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 7:0      | TCOMP | TFC         | RLEX |         |          | RXUBR | RCOMP |  |  |  |

| 0.0440 |                 | 15:8     |       |             |      |         | HRESP    | ROVR  |       |  |  |  |

| 0x0410 | GMAC_ISRPQ5     | 23:16    |       |             |      |         |          |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         |          |       |       |  |  |  |

| 0x0414 |                 |          |       |             |      |         |          |       |       |  |  |  |

|        | Reserved        |          |       |             |      |         |          |       |       |  |  |  |

| 0x043F |                 |          |       |             |      |         |          |       |       |  |  |  |

|        |                 | 7:0      |       | TXBQBA[5:0] |      |         |          |       |       |  |  |  |

| 0x0440 | GMAC_TBQBAPQ1   | 15:8     |       |             |      | TXBQE   | BA[13:6] |       |       |  |  |  |

| 0x0440 | GINAC_I DQDAFQI | 23:16    |       |             |      | TXBQB   | A[21:14] |       |       |  |  |  |

|        |                 | 31:24    |       |             |      | TXBQB   | A[29:22] |       |       |  |  |  |

|        |                 | 7:0      |       |             | TXBQ | BA[5:0] |          |       |       |  |  |  |

| 0x0444 |                 | 15:8     |       |             |      | TXBQE   | BA[13:6] |       |       |  |  |  |

| 0x0444 | GMAC_TBQBAPQ2   | 23:16    |       |             |      | TXBQB   | A[21:14] |       |       |  |  |  |

|        |                 | 31:24    |       |             |      | TXBQB   | A[29:22] |       |       |  |  |  |

|        |                 | 7:0      |       |             | TXBQ | BA[5:0] |          |       |       |  |  |  |

| 0.0440 |                 | 15:8     |       |             |      | TXBQE   | 3A[13:6] |       |       |  |  |  |

| 0x0448 | GMAC_TBQBAPQ3   | 23:16    |       |             |      | TXBQB   | A[21:14] |       |       |  |  |  |

|        |                 | 31:24    |       |             |      | TXBQB   | A[29:22] |       |       |  |  |  |

|        |                 | 7:0      |       |             | TXBQ | BA[5:0] |          |       |       |  |  |  |

| 0.0440 |                 | 15:8     |       |             |      | TXBQE   | BA[13:6] |       |       |  |  |  |

| 0x044C | GMAC_TBQBAPQ4   | 23:16    |       |             |      |         | A[21:14] |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         | A[29:22] |       |       |  |  |  |

|        |                 | 7:0      |       |             | TXBQ | BA[5:0] |          |       |       |  |  |  |

|        |                 | 15:8     |       |             |      |         | 3A[13:6] |       |       |  |  |  |

| 0x0450 | GMAC_TBQBAPQ5   | 23:16    |       |             |      |         | A[21:14] |       |       |  |  |  |

|        |                 | 31:24    |       |             |      |         | A[29:22] |       |       |  |  |  |

| 0x0454 |                 |          |       |             |      |         |          |       |       |  |  |  |

|        | Reserved        |          |       |             |      |         |          |       |       |  |  |  |

| 0x047F |                 |          |       |             |      |         |          |       |       |  |  |  |

|        |                 |          |       |             |      |         |          |       |       |  |  |  |

#### Bit 24 - RXCOEN Receive Checksum Offload Enable

Writing a '1' to this bit enables the receive checksum engine, and frames with bad IP, TCP or UDP checksums are discarded.

#### Bit 23 – DCPF Disable Copy of Pause Frames

Writing a '1' to this bit prevents valid pause frames from being copied to memory. Pause frames are not copied regardless of the state of the Copy All Frames (CAF) bit, whether a hash match is found or whether a type ID match is identified.

If a destination address match is found, the pause frame will be copied to memory. Note that valid pause frames received will still increment pause statistics and pause the transmission of frames, as required.

#### Bits 22:21 – DBW[1:0] Data Bus Width

Should always be written to '0'.

| Value | Name  | Description           |

|-------|-------|-----------------------|

| 0     | DBW32 | 32-bit data bus width |

| 1     | DBW64 | 64-bit data bus width |

#### Bits 20:18 - CLK[2:0] MDC Clock Division

These bits must be set according to MCK speed, and determine the number MCK will be divided by to generate Management Data Clock (MDC). For conformance with the 802.3 specification, MDC must not exceed 2.5MHz.

**Note:** MDC is only active during MDIO read and write operations.

| Value | Name   | Description                          |

|-------|--------|--------------------------------------|

| 0     | MCK_8  | MCK divided by 8 (MCK up to 20MHz)   |

| 1     | MCK_16 | MCK divided by 16 (MCK up to 40MHz)  |

| 2     | MCK_32 | MCK divided by 32 (MCK up to 80MHz)  |

| 3     | MCK_48 | MCK divided by 48 (MCK up to 120MHz) |

| 4     | MCK_64 | MCK divided by 64 (MCK up to 160MHz) |

| 5     | MCK_96 | MCK divided by 96 (MCK up to 240MHz) |

#### Bit 17 – RFCS Remove FCS

Writing this bit to '1' will cause received frames to be written to memory without their frame check sequence (last 4 bytes). The indicated frame length will be reduced by four bytes in this mode.

#### Bit 16 – LFERD Length Field Error Frame Discard

Writing a '1' to this bit discards frames with a measured length shorter than the extracted length field (as indicated by bytes 13 and 14 in a non-VLAN tagged frame). This only applies to frames with a length field less than 0x0600.

#### Bits 15:14 – RXBUFO[1:0] Receive Buffer Offset

These bits determine the number of bytes by which the received data is offset from the start of the receive buffer.

#### Bit 13 – PEN Pause Enable

When written to '1', transmission will pause if a non-zero 802.3 classic pause frame is received and PFC has not been negotiated.

# USB High-Speed Interface (USBHS)

| Offset | Name                           | Bit Pos. |                  |           |         |                  |                  |          |         |        |

|--------|--------------------------------|----------|------------------|-----------|---------|------------------|------------------|----------|---------|--------|

|        |                                |          | SHORTPACK        |           |         | HBISOFLUSH       | HBISOINERRI      |          |         |        |

|        |                                | 7:0      | ETC              | CRCERRIC  | OVERFIC | IC               | С                | UNDERFIC | RXOUTIC | TXINIC |

| 0x016C | USBHS_DEVEPTIC                 | 15:8     |                  |           |         |                  |                  |          |         |        |

|        | R3 (ISOENPT)                   | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 01.24    | SHORTPACK        |           |         |                  |                  |          |         |        |

|        | USBHS_DEVEPTIC                 | 7:0      | ETC              | STALLEDIC | OVERFIC | NAKINIC          | NAKOUTIC         | RXSTPIC  | RXOUTIC | TXINIC |

| 0x0170 | R4                             | 15:8     |                  |           |         |                  |                  |          |         |        |

|        | 114                            | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 7:0      | SHORTPACK<br>ETC | CRCERRIC  | OVERFIC | HBISOFLUSH<br>IC | HBISOINERRI<br>C | UNDERFIC | RXOUTIC | TXINIC |

| 0x0170 | USBHS_DEVEPTIC                 | 15:8     |                  |           |         |                  |                  |          |         |        |

|        | R4 (ISOENPT)                   | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 51.24    | SHODEDAOK        |           |         |                  |                  |          |         |        |

|        |                                | 7:0      | SHORTPACK<br>ETC | STALLEDIC | OVERFIC | NAKINIC          | NAKOUTIC         | RXSTPIC  | RXOUTIC | TXINIC |

| 0x0174 | USBHS_DEVEPTIC<br>R5           | 15:8     |                  |           |         |                  |                  |          |         |        |

|        |                                | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        | USBHS_DEVEPTIC<br>R5 (ISOENPT) | 7:0      | SHORTPACK<br>ETC | CRCERRIC  | OVERFIC | HBISOFLUSH<br>IC | HBISOINERRI<br>C | UNDERFIC | RXOUTIC | TXINIC |

| 0x0174 |                                | 15:8     | -                |           |         |                  |                  |          |         |        |

| 0,0171 |                                | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 51.24    | SUODTRACK        |           |         |                  |                  |          |         |        |

|        | USBHS_DEVEPTIC                 | 7:0      | SHORTPACK<br>ETC | STALLEDIC | OVERFIC | NAKINIC          | NAKOUTIC         | RXSTPIC  | RXOUTIC | TXINIC |

| 0x0178 | R6                             | 15:8     |                  |           |         |                  |                  |          |         |        |

|        |                                | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 7:0      | SHORTPACK<br>ETC | CRCERRIC  | OVERFIC | HBISOFLUSH<br>IC | HBISOINERRI<br>C | UNDERFIC | RXOUTIC | TXINIC |

| 0x0178 | USBHS_DEVEPTIC                 | 15:8     | 210              |           |         |                  | <b>v</b>         |          |         |        |

| 010170 | R6 (ISOENPT)                   |          |                  |           |         |                  |                  |          |         |        |

|        |                                | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    | 0110000000       |           |         |                  |                  |          |         |        |

|        |                                | 7:0      | SHORTPACK<br>ETC | STALLEDIC | OVERFIC | NAKINIC          | NAKOUTIC         | RXSTPIC  | RXOUTIC | TXINIC |

| 0x017C | USBHS_DEVEPTIC                 | 15:8     |                  |           |         |                  |                  |          |         |        |

|        | R7                             | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

|        |                                | 7:0      | SHORTPACK<br>ETC | CRCERRIC  | OVERFIC | HBISOFLUSH       | HBISOINERRI<br>C | UNDERFIC | RXOUTIC | TXINIC |

| 0x017C | USBHS_DEVEPTIC                 | 15:8     | 210              |           |         |                  | <b>J</b>         |          |         |        |

| UXU17C | R7 (ISOENPT)                   |          |                  |           |         |                  |                  |          |         |        |

|        |                                | 23:16    |                  |           |         |                  |                  |          |         |        |

|        |                                | 31:24    |                  |           |         |                  |                  |          |         |        |

# USB High-Speed Interface (USBHS)

| Offset | Name          | Bit Pos. |           |                  |            |           |            |           |           |           |  |  |

|--------|---------------|----------|-----------|------------------|------------|-----------|------------|-----------|-----------|-----------|--|--|

|        |               | 7:0      |           |                  |            | BUFF A    | ADD[7:0]   |           |           |           |  |  |

|        | USBHS_DEVDMAA | 15:8     |           |                  |            | BUFF_A    |            |           |           |           |  |  |

| 0x0364 | DDRESS7       | 23:16    |           |                  |            |           | DD[23:16]  |           |           |           |  |  |

|        |               | 31:24    |           |                  |            |           | DD[31:24]  |           |           |           |  |  |

|        |               | 7:0      | BURST LCK | DESC LD IT       | END_BUFFIT | _         |            | END TR EN | LDNXT DSC | CHANN ENB |  |  |

|        | USBHS_DEVDMAC | 15:8     | _         |                  | _          |           |            |           | _         | _         |  |  |

| 0x0368 | ONTROL7       | 23:16    |           | BUFF LENGTH[7:0] |            |           |            |           |           |           |  |  |

|        |               | 31:24    |           |                  |            | BUFF_LEN  | IGTH[15:8] |           |           |           |  |  |

|        |               | 7:0      |           | DESC_LDST        | END_BF_ST  | END_TR_ST |            |           | CHANN_ACT | CHANN_ENB |  |  |

|        | USBHS_DEVDMAS | 15:8     |           |                  |            |           |            |           |           |           |  |  |

| 0x036C | TATUS7        | 23:16    |           |                  |            | BUFF_CC   | DUNT[7:0]  |           |           |           |  |  |

|        |               | 31:24    |           |                  |            | BUFF_CO   | UNT[15:8]  |           |           |           |  |  |

| 0x0370 |               |          |           |                  |            |           |            |           |           |           |  |  |

|        | Reserved      |          |           |                  |            |           |            |           |           |           |  |  |

| 0x03FF |               |          |           |                  |            |           |            |           |           |           |  |  |

|        |               | 7:0      |           |                  |            |           |            |           |           |           |  |  |

| 0x0400 | USBHS_HSTCTRL | 15:8     |           |                  | SPDCC      | NF[1:0]   |            | RESUME    | RESET     | SOFE      |  |  |

| 070400 |               | 23:16    |           |                  |            |           |            |           |           |           |  |  |

|        |               | 31:24    |           |                  |            |           |            |           |           |           |  |  |

|        |               | 7:0      |           | HWUPI            | HSOFI      | RXRSMI    | RSMEDI     | RSTI      | DDISCI    | DCONNI    |  |  |

| 0x0404 | USBHS_HSTISR  | 15:8     | PEP_7     | PEP_6            | PEP_5      | PEP_4     | PEP_3      | PEP_2     | PEP_1     | PEP_0     |  |  |

|        |               | 23:16    |           |                  |            |           |            |           | PEP_9     | PEP_8     |  |  |

|        |               | 31:24    | DMA_6     | DMA_5            | DMA_4      | DMA_3     | DMA_2      | DMA_1     | DMA_0     |           |  |  |

|        | USBHS_HSTICR  | 7:0      |           | HWUPIC           | HSOFIC     | RXRSMIC   | RSMEDIC    | RSTIC     | DDISCIC   | DCONNIC   |  |  |

| 0x0408 |               | 15:8     |           |                  |            |           |            |           |           |           |  |  |

|        |               | 23:16    |           |                  |            |           |            |           |           |           |  |  |

|        |               | 31:24    |           |                  |            |           |            |           |           |           |  |  |

|        |               | 7:0      |           | HWUPIS           | HSOFIS     | RXRSMIS   | RSMEDIS    | RSTIS     | DDISCIS   | DCONNIS   |  |  |

| 0x040C | USBHS_HSTIFR  | 15:8     |           |                  |            |           |            |           |           |           |  |  |

|        | _             | 23:16    |           |                  |            |           |            |           |           |           |  |  |

|        |               | 31:24    | DMA_6     | DMA_5            | DMA_4      | DMA_3     | DMA_2      | DMA_1     | DMA_0     |           |  |  |

|        |               | 7:0      |           | HWUPIE           | HSOFIE     | RXRSMIE   | RSMEDIE    | RSTIE     | DDISCIE   | DCONNIE   |  |  |

| 0x0410 | USBHS_HSTIMR  | 15:8     | PEP_7     | PEP_6            | PEP_5      | PEP_4     | PEP_3      | PEP_2     | PEP_1     | PEP_0     |  |  |

|        |               | 23:16    |           |                  |            |           |            |           | PEP_9     | PEP_8     |  |  |

|        |               | 31:24    | DMA_6     | DMA_5            | DMA_4      | DMA_3     | DMA_2      | DMA_1     | DMA_0     |           |  |  |

|        |               | 7:0      |           | HWUPIEC          | HSOFIEC    | RXRSMIEC  | RSMEDIEC   | RSTIEC    | DDISCIEC  | DCONNIEC  |  |  |

| 0x0414 | USBHS_HSTIDR  | 15:8     | PEP_7     | PEP_6            | PEP_5      | PEP_4     | PEP_3      | PEP_2     | PEP_1     | PEP_0     |  |  |

|        |               | 23:16    |           |                  |            |           |            |           | PEP_9     | PEP_8     |  |  |

|        |               | 31:24    | DMA_6     | DMA_5            | DMA_4      | DMA_3     | DMA_2      | DMA_1     | DMA_0     | DOONINUES |  |  |

|        |               | 7:0      |           | HWUPIES          | HSOFIES    | RXRSMIES  | RSMEDIES   | RSTIES    | DDISCIES  | DCONNIES  |  |  |

| 0x0418 | USBHS_HSTIER  | 15:8     | PEP_7     | PEP_6            | PEP_5      | PEP_4     | PEP_3      | PEP_2     | PEP_1     | PEP_0     |  |  |

|        | _ ``          | 23:16    |           |                  |            |           |            |           | PEP_9     | PEP_8     |  |  |

|        |               | 31:24    | DMA_6     | DMA_5            | DMA_4      | DMA_3     | DMA_2      | DMA_1     | DMA_0     | DENO      |  |  |

| 0x0440 |               | 7:0      | PEN7      | PEN6             | PEN5       | PEN4      | PEN3       | PEN2      | PEN1      | PEN0      |  |  |

| 0x041C | USBHS_HSTPIP  | 15:8     | DDOT7     | DDOTO            | DDOTE      | DDOTA     | DDOTO      | DDETO     | DDOT4     | PEN8      |  |  |

|        |               | 23:16    | PRST7     | PRST6            | PRST5      | PRST4     | PRST3      | PRST2     | PRST1     | PRST0     |  |  |

# 40.14 Register Summary

| Offset | Name        | Bit Pos. |           |             |             |             |          |        |             |          |  |  |

|--------|-------------|----------|-----------|-------------|-------------|-------------|----------|--------|-------------|----------|--|--|

|        |             | 7:0      | SWRST     |             |             |             | PWSDIS   | PWSEN  | MCIDIS      | MCIEN    |  |  |

| 000    |             | 15:8     |           |             |             |             |          |        |             |          |  |  |

| 0x00   | HSMCI_CR    | 23:16    |           |             |             |             |          |        |             |          |  |  |

|        |             | 31:24    |           |             |             |             |          |        |             |          |  |  |

|        |             | 7:0      |           |             |             | DATA        | 4[7:0]   |        |             |          |  |  |

|        | HSMCI_FIFOx | 15:8     |           |             |             | DATA        | [15:8]   |        |             |          |  |  |

| 0x00   | [x=0255]    | 23:16    |           |             |             | DATA        | [23:16]  |        |             |          |  |  |

|        |             | 31:24    |           |             |             | DATA        | [31:24]  |        |             |          |  |  |

|        |             | 7:0      |           | CLKDIV[7:0] |             |             |          |        |             |          |  |  |

|        |             | 15:8     |           | PADV        | FBYTE       | WRPROOF     | RDPROOF  |        | PWSDIV[2:0] |          |  |  |

| 0x04   | HSMCI_MR    | 23:16    |           |             |             |             |          |        |             | CLKODE   |  |  |

|        |             | 31:24    |           |             |             |             |          |        |             |          |  |  |

|        |             | 7:0      |           |             | DTOMUL[2:0  | 1           |          | DTOC   | YC[3:0]     |          |  |  |

|        |             | 15:8     |           |             |             |             |          |        |             |          |  |  |

| 0x08   | HSMCI_DTOR  | 23:16    |           |             |             |             |          |        |             |          |  |  |

|        |             | 31:24    |           |             |             |             |          |        |             |          |  |  |

|        |             | 7:0      | SDCBL     | JS[1:0]     |             |             |          |        | SDCS        | EL[1:0]  |  |  |

|        |             | 15:8     |           | []          |             |             |          |        |             | []       |  |  |

| 0x0C   | HSMCI_SDCR  | 23:16    |           |             |             |             |          |        |             |          |  |  |

|        |             | 31:24    |           |             |             |             |          |        |             |          |  |  |

|        |             | 7:0      | ARG[7:0]  |             |             |             |          |        |             |          |  |  |

|        |             | 15:8     | ARG[15:8] |             |             |             |          |        |             |          |  |  |

| 0x10   | HSMCI_ARGR  | 23:16    |           |             |             |             | 23:16]   |        |             |          |  |  |

|        |             | 31:24    |           |             |             |             | 31:24]   |        |             |          |  |  |

|        |             | 7:0      | RSPT      | /P[1·0]     |             | 7.1.0[      | CMDN     | B[5:0] |             |          |  |  |

|        |             | 15:8     |           | 11 [1.0]    |             | MAXLAT      | OPDCMD   | D[0.0] | SPCMD[2:0]  |          |  |  |

| 0x14   | HSMCI_CMDR  | 23:16    |           |             |             | TRTYP[2:0]  |          | TRDIR  | 1           | /ID[1:0] |  |  |

|        |             | 31:24    |           |             |             | II(IIF[2.0] | BOOT_ACK | ATACS  |             | MD[1:0]  |  |  |

|        |             | 7:0      |           |             |             | BCN         |          | AIACO  | 103FC       | ויזטואה, |  |  |

|        |             |          |           |             |             |             |          |        |             |          |  |  |

| 0x18   | HSMCI_BLKR  | 15:8     |           |             |             |             | [15:8]   |        |             |          |  |  |

|        |             | 23:16    |           |             |             |             | EN[7:0]  |        |             |          |  |  |

|        |             | 31:24    |           |             | 007010000   |             | N[15:8]  | 0.070  |             |          |  |  |

|        |             | 7:0      |           |             | CSTOMUL[2:0 | וי          |          | CSTO   | CYC[3:0]    |          |  |  |

| 0x1C   | HSMCI_CSTOR | 15:8     |           |             |             |             |          |        |             |          |  |  |

|        |             | 23:16    |           |             |             |             |          |        |             |          |  |  |

|        |             | 31:24    |           |             |             |             |          |        |             |          |  |  |

|        |             | 7:0      |           |             |             |             | [7:0]    |        |             |          |  |  |

| 0x20   | HSMCI_RSPR  | 15:8     |           |             |             |             | [15:8]   |        |             |          |  |  |

|        | _           | 23:16    |           |             |             |             | 23:16]   |        |             |          |  |  |

|        |             | 31:24    |           |             |             | RSP[;       | 31:24]   |        |             |          |  |  |

| 0x24   |             |          |           |             |             |             |          |        |             |          |  |  |

|        | Reserved    |          |           |             |             |             |          |        |             |          |  |  |

| 0x2F   |             |          |           |             |             |             |          |        |             |          |  |  |

# **Quad Serial Peripheral Interface (QSPI)**

#### 42.7.6 QSPI Interrupt Enable Register

Name:QSPI\_IEROffset:0x14Reset:-Property:Write-only

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

| Bit    | 31 | 30 | 29 | 28 | 27    | 26      | 25   | 24   |

|--------|----|----|----|----|-------|---------|------|------|

|        |    |    |    |    |       |         |      |      |

| Access |    |    |    |    |       |         |      |      |

| Reset  |    |    |    |    |       |         |      |      |

|        |    |    |    |    |       |         |      |      |

| Bit    | 23 | 22 | 21 | 20 | 19    | 18      | 17   | 16   |

|        |    |    |    |    |       |         |      |      |

| Access |    |    |    |    |       |         |      |      |

| Reset  |    |    |    |    |       |         |      |      |

|        |    |    | 10 | 10 |       |         |      |      |

| Bit    | 15 | 14 | 13 | 12 | 11    | 10      | 9    | 8    |

|        |    |    |    |    |       | INSTRE  | CSS  | CSR  |

| Access |    |    |    |    |       | W       | W    | W    |

| Reset  |    |    |    |    |       | -       | -    | _    |

|        |    |    |    |    |       |         |      |      |

| Bit    | 7  | 6  | 5  | 4  | 3     | 2       | 1    | 0    |

|        |    |    |    |    | OVRES | TXEMPTY | TDRE | RDRF |

| Access |    |    |    |    | W     | W       | W    | W    |

| Reset  |    |    |    |    | _     | -       | -    | -    |

Bit 10 – INSTRE Instruction End Interrupt Enable

**Bit 9 – CSS** Chip Select Status Interrupt Enable

**Bit 8 – CSR** Chip Select Rise Interrupt Enable

**Bit 3 – OVRES** Overrun Error Interrupt Enable

Bit 2 – TXEMPTY Transmission Registers Empty Enable

**Bit 1 – TDRE** Transmit Data Register Empty Interrupt Enable

Bit 0 - RDRF Receive Data Register Full Interrupt Enable

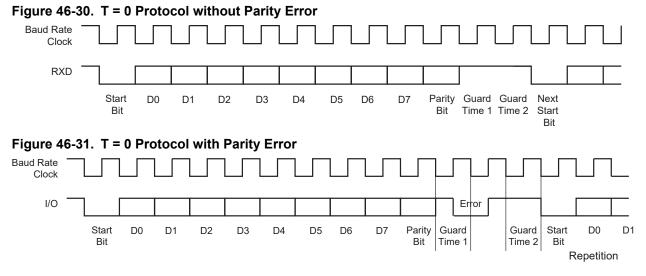

If no parity error is detected, the I/O line remains at 1 during the guard time and the transmitter can continue with the transmission of the next character, as shown in Figure 46-30.

If a parity error is detected by the receiver, it drives the I/O line to 0 during the guard time, as shown in Figure 46-31. This error bit, NACK, for Non Acknowledge. In this case, the character lasts one additional bit time, as the guard time does not change and is added to the error bit time, which lasts one bit time.

When the USART is the receiver and it detects an error, it does not load the erroneous character in US\_RHR. It sets US\_SR.PARE so that the software can handle the error.

#### 46.6.4.2.1 Receive Error Counter

The USART receiver also records the total number of errors. This can be read in the Number of Errors (US\_NER) register. The NB\_ERRORS field can record up to 255 errors. Reading US\_NER automatically clears the NB\_ERRORS field.

#### 46.6.4.2.2 Receive NACK Inhibit

The USART can be configured to inhibit an error. This is done by writing a '1' to US\_MR.INACK. In this case, no error signal is driven on the I/O line even if a parity bit is detected.

Moreover, if INACK = 1, the erroneous received character is stored in the Receive Holding register as if no error occurred, and the RXRDY bit rises.

#### 46.6.4.2.3 Transmit Character Repetition

When the USART is transmitting a character and gets a NACK, it can automatically repeat the character before moving on to the next one. Repetition is enabled by writing US\_MR.MAX\_ITERATION to a value greater than 0. Each character can be transmitted up to eight times; the first transmission plus seven repetitions.

If MAX\_ITERATION does not equal zero, the USART repeats the character as many times as the value loaded in MAX\_ITERATION.

When the USART repetition number reaches MAX\_ITERATION and the last repeated character is not acknowledged, the US\_CSR.ITER is set. If the repetition of the character is acknowledged by the receiver, the repetitions are stopped and the iteration counter is cleared.

US\_CSR.ITER can be cleared by writing a '1' to US\_CR.RSTIT.

#### 46.6.4.2.4 Disable Successive Receive NACK

The receiver can limit the number of successive NACKs sent back to the remote transmitter. This is programmed by setting US\_MR.DSNACK. The maximum number of NACKs transmitted is configured in

## Media Local Bus (MLB)

| Field | Description                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| FCE   | Flow Control Enable <sup>(2)</sup> :<br>1 = Enabled<br>0 = Disabled                                                                        |

| MFE   | Multi-Frame per Sub-buffer Enable $^{(3)}$ : 1 = Enabled 0 = Disabled                                                                      |

| rsvd  | Reserved. Software writes a zero to all reserved bits when the entry is initialized. The reserved bits are Read-only after initialization. |

Notes: 1. When set for synchronous channels, the MT bit forces Rx channels to write zeros into the channel data buffer, and Tx channels to output zeros on the physical interface. When set for asynchronous and control channels, the MT bit causes DMA to halt at a packet boundary. Not valid for isochronous channels.

- 2. The FCE bit is used by MediaLB isochronous Rx channels only.

- 3. The MFE bit is used by MediaLB synchronous channels only.

#### Channel Setup

Data direction in the MLB is in reference to the DBR. Therefore, the data direction of CAT entries corresponding to the same channel is reversed for the HBI CAT and the MediaLB CAT.

For a Tx channel (from the HC to the MediaLB interface):

- HBI CAT entry: RNW = 0 (write)

- MediaLB CAT entry: RNW = 1 (read)

Conversely, for a Rx channel (data from MediaLB to HC):

- HBI CAT entry: RNW = 1 (read)

- MediaLB CAT entry: RNW = 0 (write)

The figure below illustrates the directional relationship in the MLB.

### Figure 48-16. MLB DBR Directional Relationship

**Channel Descriptor Table**

The Channel Descriptor Table (CDT) is comprised of 64 CTR entries (addresses 0x00–0x3F), as shown in Table 48-10.

Each 128-bit CDT entry (also referred to as a Channel Descriptor) is referenced by a Connection Label and contains information about a data buffer in the DBR (e.g., buffer size, address pointers).

The format of each CDT entry (also referred to as a Channel Descriptor) depends on the channel type (e.g. synchronous, isochronous, asynchronous, or control).

### 48.7.15 MIF Data 0 Register

| Name:     | MLB_MDAT0  |

|-----------|------------|

| Offset:   | 0x0C0      |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

| Bit    | 31 | 30 | 29 | 28   | 27      | 26 | 25 | 24 |

|--------|----|----|----|------|---------|----|----|----|

|        |    |    |    | DATA | [31:24] |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19      | 18 | 17 | 16 |

|        |    |    |    | DATA | [23:16] |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|        |    |    |    | DATA | [15:8]  |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        |    |    |    | DAT  | 4[7:0]  |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

Bits 31:0 – DATA[31:0] CRT or DBR Data CTR data - bits[31:0] of 128-bit entry or

DBR data - bits[7:0] of 8-bit entry

## 48.7.23 MIF Control Register

| Bit       31       30       29       28       27       26       25       24         Access       Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Name:<br>Offset:<br>Reset:<br>Property: | MLB_MCTL<br>0x0E0<br>0x00000000<br>Read/Write |    |    |    |    |    |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|-----------------------------------------------|----|----|----|----|----|------|

| Reset       Bit       23       22       21       20       19       18       17       16         Access<br>Reset       Image: Constraint of the set of the                                                                                                | Bit    | 31                                      | 30                                            | 29 | 28 | 27 | 26 | 25 | 24   |

| Reset       Bit       23       22       21       20       19       18       17       16         Access<br>Reset       Image: Constraint of the set of the                                                                                                |        |                                         |                                               |    |    |    |    |    |      |

| Bit     23     22     21     20     19     18     17     16       Access<br>Reset     Image: Constraint of the sector of th                                                                     |        |                                         |                                               |    |    |    |    |    |      |

| Access       Reset       Image: state in the st | Reset  |                                         |                                               |    |    |    |    |    |      |

| Access       Reset       Image: state in the st |        |                                         |                                               |    |    |    |    |    |      |

| Reset       Bit       15       14       13       12       11       10       9       8         Access<br>Reset       Image: Constraint of the second seco                                                                                                | Bit    | 23                                      | 22                                            | 21 | 20 | 19 | 18 | 17 | 16   |

| Reset       Bit       15       14       13       12       11       10       9       8         Access<br>Reset       Image: Constraint of the second seco                                                                                                |        |                                         |                                               |    |    |    |    |    |      |

| Bit       15       14       13       12       11       10       9       8         Access<br>Reset       Image: Constraint of the second seco                                                                                       |        |                                         |                                               |    |    |    |    |    |      |

| Access<br>Reset<br>Bit 7 6 5 4 3 2 1 0<br>Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset  |                                         |                                               |    |    |    |    |    |      |

| Access<br>Reset<br>Bit 7 6 5 4 3 2 1 0<br>Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit    | 15                                      | 14                                            | 13 | 12 | 11 | 10 | 9  | 8    |

| Bit         7         6         5         4         3         2         1         0           Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BR     |                                         |                                               | 10 | 12 |    | 10 |    |      |

| Bit         7         6         5         4         3         2         1         0           Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Access |                                         |                                               |    |    |    |    |    |      |

| Bit       7       6       5       4       3       2       1       0         Image: Constraint of the second sec                                                                                 |        |                                         |                                               |    |    |    |    |    |      |