Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M7                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 300MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, SSC, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 44                                                                        |

| Program Memory Size        | 2MB (2M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 384K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                              |

| Data Converters            | A/D 5x12b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-LQFP                                                                   |

| Supplier Device Package    | 64-LQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70j21b-an |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

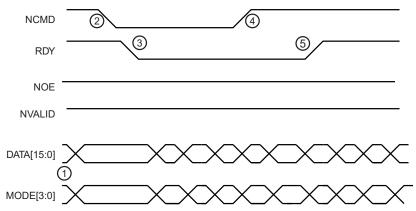

#### 18.3.4.1 Write Handshaking

For details on the write handshaking sequence, refer to the following figure and table.

### Figure 18-2. Parallel Programming Timing, Write Sequence

#### Table 18-4. Write Handshake

| Step | Programmer Action              | Device Action                        | Data I/O |

|------|--------------------------------|--------------------------------------|----------|

| 1    | Sets MODE and DATA signals     | Waits for NCMD low                   | Input    |

| 2    | Clears NCMD signal             | Latches MODE and DATA                | Input    |

| 3    | Waits for RDY low              | Clears RDY signal                    | Input    |

| 4    | Releases MODE and DATA signals | Executes command and polls NCMD high | Input    |

| 5    | Sets NCMD signal               | Executes command and polls NCMD high | Input    |

| 6    | Waits for RDY high             | Sets RDY                             | Input    |

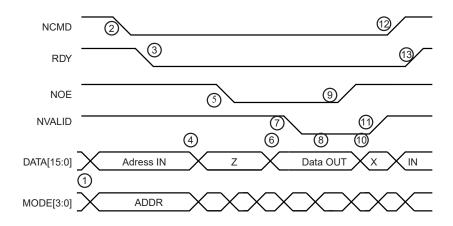

#### 18.3.4.2 Read Handshaking

For details on the read handshaking sequence, refer to the following figure and table.

#### Figure 18-3. Parallel Programming Timing, Read Sequence

## Parallel Input/Output Controller (PIO)

#### 32.6.1.4 PIO Output Enable Register

| Name:     | PIO_OER    |

|-----------|------------|

| Offset:   | 0x0010     |

| Property: | Write-only |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Output Enable

| Value | Description                         |

|-------|-------------------------------------|

| 0     | No effect.                          |

| 1     | Enables the output on the I/O line. |

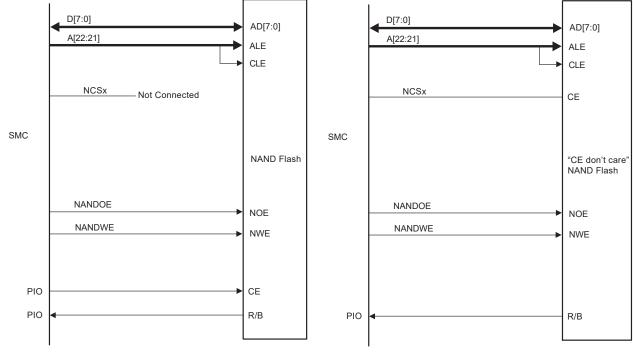

## Static Memory Controller (SMC)

#### Figure 35-6. Standard and "CE don't care" NAND Flash Application Examples

19. Bus Matrix (MATRIX)

### 35.8 Application Example

#### 35.8.1 Implementation Examples

Hardware configurations are given for illustration only. The user should refer to the manufacturer web site to check for memory device availability.

For hardware implementation examples, refer to the evaluation kit schematics for this microcontroller, which show examples of a connection to an LCD module and NAND Flash.

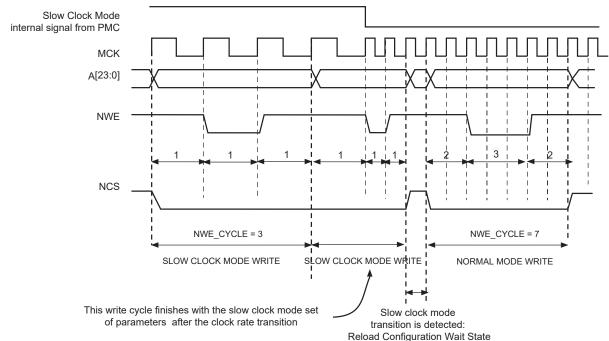

### Static Memory Controller (SMC)

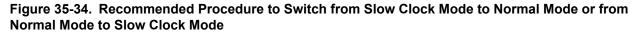

#### Figure 35-33. Clock Rate Transition Occurs while the SMC is Performing a Write Operation

### 35.15 Asynchronous Page Mode

The SMC supports asynchronous burst reads in Page mode, provided that the Page mode is enabled (SMC\_MODE.PMEN =1). The page size must be configured in the SMC\_MODE register (PS field) to 4, 8, 16 or 32 bytes.

The page defines a set of consecutive bytes into memory. A 4-byte page (resp. 8-, 16-, 32-byte page) is always aligned to 4-byte boundaries (resp. 8-, 16-, 32-byte boundaries) of memory. The MSB of data address defines the address of the page in memory, the LSB of address define the address of the data in the page as detailed in the following table.

## SAM E70/S70/V70/V71 Family GMAC - Ethernet MAC

#### 38.8.45 GMAC 65 to 127 Byte Frames Transmitted Register

| Name:<br>Offset:<br>Reset:<br>Property: |    | GMAC_TBFT127<br>0x11C<br>0x00000000<br>- |    |       |        |    |    |    |

|-----------------------------------------|----|------------------------------------------|----|-------|--------|----|----|----|

| Bit                                     | 31 | 30                                       | 29 | 28    | 27     | 26 | 25 | 24 |

|                                         |    |                                          |    | NFTX[ | 31:24] |    |    |    |

| Access                                  | R  | R                                        | R  | R     | R      | R  | R  | R  |

| Reset                                   | 0  | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

|                                         |    |                                          |    |       |        |    |    |    |

| Bit                                     | 23 | 22                                       | 21 | 20    | 19     | 18 | 17 | 16 |

|                                         |    |                                          |    | NFTX[ | 23:16] |    |    |    |

| Access                                  | R  | R                                        | R  | R     | R      | R  | R  | R  |

| Reset                                   | 0  | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

|                                         |    |                                          |    |       |        |    |    |    |

| Bit                                     | 15 | 14                                       | 13 | 12    | 11     | 10 | 9  | 8  |

|                                         |    |                                          |    |       | [15:8] |    |    |    |

| Access                                  | R  | R                                        | R  | R     | R      | R  | R  | R  |

| Reset                                   | 0  | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

|                                         |    |                                          |    |       |        |    |    |    |

| Bit                                     | 7  | 6                                        | 5  | 4     | 3      | 2  | 1  | 0  |

|                                         |    |                                          |    | NFT>  |        |    |    |    |

| Access                                  | R  | R                                        | R  | R     | R      | R  | R  | R  |

| Reset                                   | 0  | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

Bits 31:0 – NFTX[31:0] 65 to 127 Byte Frames Transmitted without Error

This register counts the number of 65 to 127 byte frames successfully transmitted without error, i.e., no underrun and not too many retries. Excludes pause frames.

## **USB High-Speed Interface (USBHS)**

- Endpoint Direction (USBHS\_DEVEPTCFGx.EPDIR)

- Endpoint Type (USBHS\_DEVEPTCFGx.EPTYPE)

To free endpoint memory, the user must write a zero to the USBHS\_DEVEPTCFGx.ALLOC bit. The x+1 pipe/endpoint memory window then slides down and its data is lost. Note that the following pipe/endpoint memory windows (from x + 2) do not slide.

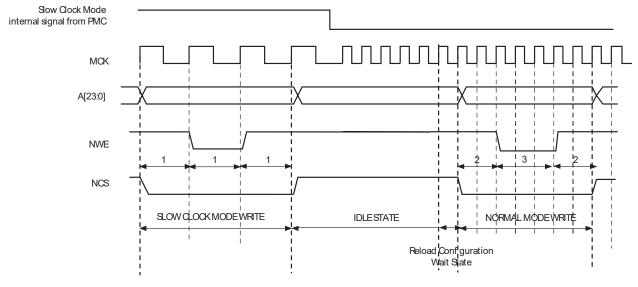

The following figure illustrates the allocation and reorganization of the DPRAM in a typical example.

Figure 39-4. Allocation and Reorganization of the DPRAM

- 1. Pipes/endpoints 0 to 5 are enabled, configured and allocated in ascending order. Each pipe/ endpoint then owns a memory area in the DPRAM.

- 2. Pipe/endpoint 3 is disabled, but its memory is kept allocated by the controller.

- 3. In order to free its memory, its USBHS\_DEVEPTCFGx.ALLOC bit is written to zero. The pipe/ endpoint 4 memory window slides down, but pipe/endpoint 5 does not move.

- 4. If the user chooses to reconfigure pipe/endpoint 3 with a larger size, the controller allocates a memory area after the pipe/endpoint 2 memory area and automatically slides up the pipe/endpoint 4 memory window. Pipe/endpoint 5 does not move and a memory conflict appears as the memory windows of pipes/endpoints 4 and 5 overlap. The data of these pipes/endpoints is potentially lost. Note: 1. The data of pipe/endpoint 0 cannot be lost (except if it is de-allocated) as the memory allocation and de-allocation may affect only higher pipes/endpoints.

2. Deactivating then reactivating the same pipe/endpoint with the same configuration only modifies temporarily the controller DPRAM pointer and size for this pipe/endpoint. Nothing changes in the DPRAM. Higher endpoints seem not to have been moved and their data is preserved as long as nothing has been written or received into them while changing the allocation state of the first pipe/ endpoint.

3. When the user writes a one to the USBHS\_DEVEPTCFGx.ALLOC bit, the Configuration OK Status bit (USBHS\_DEVEPTISRx.CFGOK) is set only if the configured size and number of banks are correct as compared to the endpoint maximum allowed values and to the maximum FIFO size (i.e., the DPRAM size). The USBHS\_DEVEPTISRx.CFGOK value does not consider memory allocation conflicts.

## USB High-Speed Interface (USBHS)

| Offset | Name                           | Bit Pos. |                  |          |        |                 |                 |                 |         |          |

|--------|--------------------------------|----------|------------------|----------|--------|-----------------|-----------------|-----------------|---------|----------|

|        |                                | 7:0      | SHORTPACK<br>ETE | CRCERRE  | OVERFE | HBISOFLUSH<br>E | HBISOINERR<br>E | UNDERFE         | RXOUTE  | TXINE    |

| 0x01D4 | USBHS_DEVEPTIM<br>R5 (ISOENPT) | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 | ERRORTRAN<br>SE | DATAXE  | MDATAE   |

|        |                                | 23:16    |                  |          |        |                 |                 | RSTDT           |         | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        | USBHS_DEVEPTIM                 | 7:0      | SHORTPACK<br>ETE | STALLEDE | OVERFE | NAKINE          | NAKOUTE         | RXSTPE          | RXOUTE  | TXINE    |

| 0x01D8 | R6                             | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 |                 |         |          |

|        | 110                            | 23:16    |                  |          |        |                 | STALLRQ         | RSTDT           | NYETDIS | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        |                                | 7:0      | SHORTPACK<br>ETE | CRCERRE  | OVERFE | HBISOFLUSH<br>E | HBISOINERR<br>E | UNDERFE         | RXOUTE  | TXINE    |

| 0x01D8 | USBHS_DEVEPTIM<br>R6 (ISOENPT) | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 | ERRORTRAN<br>SE | DATAXE  | MDATAE   |

|        |                                | 23:16    |                  |          |        |                 |                 | RSTDT           |         | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        |                                | 7:0      | SHORTPACK<br>ETE | STALLEDE | OVERFE | NAKINE          | NAKOUTE         | RXSTPE          | RXOUTE  | TXINE    |

| 0x01DC | USBHS_DEVEPTIM<br>R7           | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 |                 |         |          |

|        |                                | 23:16    |                  |          |        |                 | STALLRQ         | RSTDT           | NYETDIS | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        | USBHS_DEVEPTIM<br>R7 (ISOENPT) | 7:0      | SHORTPACK<br>ETE | CRCERRE  | OVERFE | HBISOFLUSH<br>E | HBISOINERR<br>E | UNDERFE         | RXOUTE  | TXINE    |

| 0x01DC |                                | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 | ERRORTRAN<br>SE | DATAXE  | MDATAE   |

|        |                                | 23:16    |                  |          |        |                 |                 | RSTDT           |         | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        | USBHS_DEVEPTIM                 | 7:0      | SHORTPACK<br>ETE | STALLEDE | OVERFE | NAKINE          | NAKOUTE         | RXSTPE          | RXOUTE  | TXINE    |

| 0x01E0 | R8                             | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 |                 |         |          |

|        |                                | 23:16    |                  |          |        |                 | STALLRQ         | RSTDT           | NYETDIS | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        |                                | 7:0      | SHORTPACK<br>ETE | CRCERRE  | OVERFE | HBISOFLUSH<br>E | HBISOINERR<br>E | UNDERFE         | RXOUTE  | TXINE    |

| 0x01E0 | USBHS_DEVEPTIM<br>R8 (ISOENPT) | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 | ERRORTRAN<br>SE | DATAXE  | MDATAE   |

|        |                                | 23:16    |                  |          |        |                 |                 | RSTDT           |         | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

|        |                                | 7:0      | SHORTPACK<br>ETE | STALLEDE | OVERFE | NAKINE          | NAKOUTE         | RXSTPE          | RXOUTE  | TXINE    |

| 0x01E4 | USBHS_DEVEPTIM<br>R9           | 15:8     |                  | FIFOCON  | KILLBK | NBUSYBKE        |                 |                 |         |          |

|        |                                | 23:16    |                  |          |        |                 | STALLRQ         | RSTDT           | NYETDIS | EPDISHDM |

|        |                                | 31:24    |                  |          |        |                 |                 |                 |         |          |

| 0x01E4 | USBHS_DEVEPTIM<br>R9 (ISOENPT) | 7:0      | SHORTPACK<br>ETE | CRCERRE  | OVERFE | HBISOFLUSH<br>E | HBISOINERR<br>E | UNDERFE         | RXOUTE  | TXINE    |

## USB High-Speed Interface (USBHS)

| Offset | Name                  | Bit Pos. |           |            |          |           |               |           |          |           |

|--------|-----------------------|----------|-----------|------------|----------|-----------|---------------|-----------|----------|-----------|

|        |                       |          | SHORTPACK |            |          |           |               |           |          |           |

|        |                       | 7:0      | ETIEC     | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC        | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0644 | USBHS_HSTPIPID        | 15:8     |           | FIFOCONC   |          | NBUSYBKEC |               |           |          |           |

|        | R9 (INTPIPES)         | 23:16    |           |            |          |           |               |           | PFREEZEC | PDISHDMAC |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       |          | SHORTPACK |            |          |           |               |           |          |           |

|        |                       | 7:0      | ETIEC     | CRCERREC   | OVERFIEC | NAKEDEC   | PERREC        | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0644 | USBHS_HSTPIPID        | 15:8     | 2.1.20    | FIFOCONC   |          | NBUSYBKEC |               |           |          |           |

| 0,0044 | R9 (ISOPIPES)         | 23:16    |           |            |          | NBOOTBREO |               |           | PFREEZEC | PDISHDMAC |

|        |                       | 31:24    |           |            |          |           |               |           | FINELZEC | PDISHDMA  |

| 00040  |                       | 31.24    |           |            |          |           |               |           |          |           |

| 0x0648 | December              |          |           |            |          |           |               |           |          |           |

|        | Reserved              |          |           |            |          |           |               |           |          |           |

| 0x064F |                       |          |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0x0650 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ0                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0,0654 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x0654 | RQ1                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN<br>RQ2 | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x0658 |                       | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | 0[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN        | 15:8     |           |            |          |           | -[]           |           |          | INMODE    |

| 0x065C | RQ3                   | 23:16    |           |            |          |           |               |           |          |           |

|        | T CQ O                | 31:24    |           |            |          |           |               |           |          |           |

|        |                       |          |           |            |          | INDC      | 17.01         |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | <b>λ[1:0]</b> |           |          | INNODE    |

| 0x0660 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ4                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0x0664 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ5                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0x0668 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 000000 | RQ6                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | Q[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x066C | RQ7                   | 23:16    |           |            |          |           |               |           |          |           |

|        | 11527                 | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | • ···E 1 |           |            |          |           |               |           |          |           |

## **USB High-Speed Interface (USBHS)**

### Bit 1 – RXOUTIC Received OUT Data Interrupt Clear

Bit 0 – TXINIC Transmitted IN Data Interrupt Clear

## USB High-Speed Interface (USBHS)

#### 39.6.38 Host Frame Number Register

|        | Name:<br>Offset:<br>Reset:<br>Property: | USBHS_HSTFNUM<br>0x0420<br>0x00000000<br>y: Read/Write |           |        |         |         |            |    |

|--------|-----------------------------------------|--------------------------------------------------------|-----------|--------|---------|---------|------------|----|

| Bit    | 31                                      | 30                                                     | 29        | 28     | 27      | 26      | 25         | 24 |

|        |                                         |                                                        |           |        |         |         |            |    |

| Access |                                         |                                                        |           |        |         |         |            |    |

| Reset  |                                         |                                                        |           |        |         |         |            |    |

|        |                                         |                                                        |           |        |         |         |            |    |

| Bit    | 23                                      | 22                                                     | 21        | 20     | 19      | 18      | 17         | 16 |

|        |                                         |                                                        |           | FLENHI | GH[7:0] |         |            |    |

| Access |                                         |                                                        |           |        |         |         |            |    |

| Reset  | 0                                       | 0                                                      | 0         | 0      | 0       | 0       | 0          | 0  |

|        |                                         |                                                        |           |        |         |         |            |    |

| Bit    | 15                                      | 14                                                     | 13        | 12     | 11      | 10      | 9          | 8  |

|        |                                         |                                                        |           |        | FNUM    | I[10:5] |            |    |

| Access |                                         | -                                                      |           |        |         |         |            |    |

| Reset  |                                         |                                                        | 0         | 0      | 0       | 0       | 0          | 0  |

|        |                                         |                                                        |           |        |         |         |            |    |

| Bit    | 7                                       | 6                                                      | 5         | 4      | 3       | 2       | 1          | 0  |

|        |                                         |                                                        | FNUM[4:0] | -      |         |         | MFNUM[2:0] |    |

| Access |                                         |                                                        |           |        |         |         |            |    |

| Reset  | 0                                       | 0                                                      | 0         | 0      | 0       | 0       | 0          | 0  |

#### Bits 23:16 - FLENHIGH[7:0] Frame Length

In High-speed mode, this field contains the 8 high-order bits of the 16-bit internal frame counter (at 30 MHz, the counter length is 3750 to ensure a SOF generation every  $125 \ \mu$ s).

#### Bits 13:3 - FNUM[10:0] Frame Number

This field contains the current SOF number.

This field can be written. In this case, the MFNUM field is reset to zero.

#### Bits 2:0 – MFNUM[2:0] Micro Frame Number

This field contains the current microframe number (can vary from 0 to 7), updated every 125 µs.

When operating in Full-speed mode, this field is tied to zero.

## **USB High-Speed Interface (USBHS)**

#### 39.6.51 Host Pipe x Set Register (Control, Bulk Pipes)

Name:USBHS\_HSTPIPIFRxOffset:0x0590Reset:0Property:Read/Write

This register view is relevant only if PTYPE = 0x0 or 0x2 in "Host Pipe x Configuration Register".

For additional information, see "Host Pipe x Status Register (Control, Bulk Pipes)".

This register always reads as zero.

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Sets the corresponding bit in USBHS\_HSTPIPISRx, which may be useful for test or debug purposes.

| Bit    | 31         | 30         | 29      | 28       | 27     | 26      | 25      | 24     |

|--------|------------|------------|---------|----------|--------|---------|---------|--------|

|        |            |            |         |          |        |         |         |        |

| Access |            |            |         |          |        |         |         |        |

| Reset  |            |            |         |          |        |         |         |        |

|        |            |            |         |          |        |         |         |        |

| Bit    | 23         | 22         | 21      | 20       | 19     | 18      | 17      | 16     |

|        |            |            |         |          |        |         |         |        |

| Access |            |            |         |          |        |         |         |        |

| Reset  |            |            |         |          |        |         |         |        |

|        |            |            |         |          |        |         |         |        |

| Bit    | 15         | 14         | 13      | 12       | 11     | 10      | 9       | 8      |

|        |            |            |         | NBUSYBKS |        |         |         |        |

| Access |            |            |         |          |        |         |         |        |

| Reset  |            |            |         | 0        |        |         |         |        |

|        |            |            |         |          |        |         |         |        |

| Bit    |            | 6          | 5       | 4        | 3      | 2       | 1       | 0      |

|        | SHORTPACKE | RXSTALLDIS | OVERFIS | NAKEDIS  | PERRIS | TXSTPIS | TXOUTIS | RXINIS |

|        | TIS        |            |         |          |        |         |         |        |

| Access |            |            |         |          |        |         |         |        |

| Reset  | 0          | 0          | 0       | 0        | 0      | 0       | 0       | 0      |

|        |            |            |         |          |        |         |         |        |

Bit 12 – NBUSYBKS Number of Busy Banks Set

Bit 7 – SHORTPACKETIS Short Packet Interrupt Set

Bit 6 – RXSTALLDIS Received STALLed Interrupt Set

Bit 5 - OVERFIS Overflow Interrupt Set

Bit 4 - NAKEDIS NAKed Interrupt Set

Bit 3 – PERRIS Pipe Error Interrupt Set

## USB High-Speed Interface (USBHS)

#### 39.6.63 Host Pipe x IN Request Register

| Name:     | USBHS_HSTPIPINRQx      |

|-----------|------------------------|

| Offset:   | 0x0650 + x*0x04 [x=09] |

| Reset:    | 0                      |

| Property: | Read/Write             |

| Bit    | 31 | 30  | 29 | 28   | 27     | 26 | 25 | 24     |

|--------|----|-----|----|------|--------|----|----|--------|

|        |    |     |    |      |        |    |    |        |

| Access |    |     |    |      |        |    |    |        |

| Reset  |    |     |    |      |        |    |    |        |

|        |    |     |    |      |        |    |    |        |

| Bit    | 23 | 22  | 21 | 20   | 19     | 18 | 17 | 16     |

|        |    |     |    |      |        |    |    |        |

| Access |    |     |    |      |        |    |    |        |

| Reset  |    |     |    |      |        |    |    |        |

| 10000  |    |     |    |      |        |    |    |        |

| Bit    | 15 | 14  | 13 | 12   | 11     | 10 | 9  | 8      |

|        |    | 1-7 |    | 12   |        |    | 5  | INMODE |

| , I    |    |     |    |      |        |    |    | INMODE |

| Access |    |     |    |      |        |    |    |        |

| Reset  |    |     |    |      |        |    |    | 0      |

|        |    |     |    |      |        |    |    |        |

| Bit    | 7  | 6   | 5  | 4    | 3      | 2  | 1  | 0      |

|        |    |     |    | INRO | Q[7:0] |    |    |        |

| Access |    |     |    |      |        |    |    |        |

| Reset  | 0  | 0   | 0  | 0    | 0      | 0  | 0  | 0      |

#### Bit 8 - INMODE IN Request Mode

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | Performs a pre-defined number of IN requests. This number is the INRQ field.   |

| 1     | Enables the USBHS to perform infinite IN requests when the pipe is not frozen. |

#### Bits 7:0 - INRQ[7:0] IN Request Number before Freeze

This field contains the number of IN transactions before the USBHS freezes the pipe. The USBHS performs (INRQ+1) IN requests before freezing the pipe. This counter is automatically decreased by 1 each time an IN request has been successfully performed.

This register has no effect when INMODE = 1.

## SAM E70/S70/V70/V71 Family Universal Synchronous Asynchronous Receiver Transc...

- Bit 9 TXEMPTY TXEMPTY Interrupt Mask

- Bit 8 TIMEOUT Timeout Interrupt Mask

- Bit 7 PARE Parity Error Interrupt Mask

- **Bit 6 FRAME** Framing Error Interrupt Mask

- Bit 5 OVRE Overrun Error Interrupt Mask

- Bit 2 RXBRK Receiver Break Interrupt Mask

- Bit 1 TXRDY TXRDY Interrupt Mask

- Bit 0 RXRDY RXRDY Interrupt Mask

## Media Local Bus (MLB)

| Field           | Description                 | Details                                                                                                                                  | Accessibility        |

|-----------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| BA              | Buffer Base<br>Address      | - BA can start at any byte in the 16k DBR                                                                                                | r,w                  |

| BD Buffer Depth |                             | - BD = size of buffer in bytes - 1<br>- Buffer end address = BA + BD                                                                     | r,w                  |

|                 |                             | - BD = 4 x m x bpf $-$ 1, where:                                                                                                         |                      |

|                 |                             | m = frames per sub-buffer (for MFE = 0, m = 1) bpf = bytes per frame.                                                                    |                      |

| RPTR            | Read Pointer                | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the read address offset within a buffer</li> </ul>               | r,w,u <sup>(1)</sup> |

|                 |                             | - DMA read address = BA + RPTR                                                                                                           |                      |

| WPTR            | Write Pointer               | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the write address offset within a buffer</li> </ul>              | r,w,u <sup>(1)</sup> |

|                 |                             | - DMA write address = BA + WPTR                                                                                                          |                      |

| RSBC            | Read Sub-buffer<br>Counter  | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the read sub-buffer offset</li> </ul>                            | r,w,u <sup>(1)</sup> |

|                 |                             | - DMA uses for pointer management                                                                                                        |                      |

| WSBC            | Write Sub-buffer<br>Counter | <ul> <li>Software initializes to zero, hardware updates</li> <li>Counts the write sub-buffer offset</li> </ul>                           | r,w,u <sup>(1)</sup> |

|                 |                             | - DMA uses for pointer management                                                                                                        |                      |

| RSTS            | Read Status                 | - Software initializes to zero, hardware updates<br>- RSTS states: <sup>(2)</sup>                                                        | r,w,u <sup>(1)</sup> |

|                 |                             | xxx0 = normal operation (no mute)                                                                                                        |                      |

|                 |                             | xxx1 = normal operation (mute)                                                                                                           |                      |

|                 |                             | xx0x = idle                                                                                                                              |                      |

| WSTS            | Write Status                | - Software initializes to zero, hardware updates<br>- WSTS states: <sup>(2)</sup>                                                        | r,w,u <sup>(1)</sup> |

|                 |                             | xxx0 = normal operation (no mute)                                                                                                        |                      |

|                 |                             | xxx1 = normal operation (mute)                                                                                                           |                      |

|                 |                             | xx0x = idle                                                                                                                              |                      |

|                 |                             | 1xxx = command protocol error                                                                                                            |                      |

| Reserved        | Reserved                    | - Software writes a zero to all reserved bits when the entry<br>is initialized. The reserved bits are Read-only after<br>initialization. | r,w,u <sup>(1)</sup> |

| Table 48-15. | Synchronous | <b>CDT Entr</b> | ry Field Definitions |

|--------------|-------------|-----------------|----------------------|

|--------------|-------------|-----------------|----------------------|

Notes: 1. "u" means "Updated periodically by hardware".

### Controller Area Network (MCAN)

#### 49.6.40 MCAN Transmit Buffer Cancellation Request

|        | Name:<br>Offset:<br>Reset:<br>Property: | MCAN_TXBCF<br>0xD4<br>0x00000000<br>Read/Write | 3    |      |      |      |      |      |

|--------|-----------------------------------------|------------------------------------------------|------|------|------|------|------|------|

| Bit    | 31                                      | 30                                             | 29   | 28   | 27   | 26   | 25   | 24   |

|        | CR31                                    | CR30                                           | CR29 | CR28 | CR27 | CR26 | CR25 | CR24 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 23                                      | 22                                             | 21   | 20   | 19   | 18   | 17   | 16   |

|        | CR23                                    | CR22                                           | CR21 | CR20 | CR19 | CR18 | CR17 | CR16 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 15                                      | 14                                             | 13   | 12   | 11   | 10   | 9    | 8    |

|        | CR15                                    | CR14                                           | CR13 | CR12 | CR11 | CR10 | CR9  | CR8  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 7                                       | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |

|        | CR7                                     | CR6                                            | CR5  | CR4  | CR3  | CR2  | CR1  | CR0  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – CRx Cancellation Request for Transmit Buffer x

Each Transmit Buffer has its own Cancellation Request bit. Writing a '1' will set the corresponding Cancellation Request bit; writing a '0' has no impact. This enables the processor to set cancellation requests for multiple Transmit Buffers with one write to MCAN\_TXBCR. MCAN\_TXBCR bits are set only for those Transmit Buffers configured via TXBC. The bits remain set until the corresponding bit of MCAN\_TXBRP is reset.

| Valu | e Description            |  |

|------|--------------------------|--|

| 0    | No cancellation pending. |  |

| 1    | Cancellation pending.    |  |

## Pulse Width Modulation Controller (PWM)

#### 51.7.47 PWM Channel Dead Time Update Register

| Name:     | PWM_DTUPDx             |

|-----------|------------------------|

| Offset:   | 0x021C + x*0x20 [x=03] |

| Reset:    | 0x0000000              |

| Property: | Write-only             |

This register can only be written if bits WPSWS4 and WPHWS4 are cleared in the PWM Write Protection Status Register.

This register acts as a double buffer for the DTH and DTL values. This prevents an unexpected waveform when modifying the dead-time values.

| Bit    | 31          | 30 | 29 | 28    | 27       | 26 | 25 | 24 |

|--------|-------------|----|----|-------|----------|----|----|----|

|        |             |    |    | DTLUF | PD[15:8] |    |    |    |

| Access | W           | W  | W  | W     | W        | W  | W  | W  |

| Reset  | 0           | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |             |    |    |       |          |    |    |    |

| Bit    | 23          | 22 | 21 | 20    | 19       | 18 | 17 | 16 |

|        |             |    |    | DTLU  | PD[7:0]  |    |    |    |

| Access | W           | W  | W  | W     | W        | W  | W  | W  |

| Reset  | 0           | 0  | 0  | 0     | 0        | 0  | 0  | -  |

|        |             |    |    |       |          |    |    |    |

| Bit    | 15          | 14 | 13 | 12    | 11       | 10 | 9  | 8  |

|        |             |    |    | DTHUF | PD[15:8] |    |    |    |

| Access | W           | W  | W  | W     | W        | W  | W  | W  |

| Reset  | 0           | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |             |    |    |       |          |    |    |    |

| Bit    | 7           | 6  | 5  | 4     | 3        | 2  | 1  | 0  |

|        | DTHUPD[7:0] |    |    |       |          |    |    |    |

| Access | W           | W  | W  | W     | W        | W  | W  | W  |

| Reset  | 0           | 0  | 0  | 0     | 0        | 0  | 0  | -  |

Only the first 12 bits (dead-time counter size) of fields DTHUPD and DTLUPD are significant.

#### Bits 31:16 – DTLUPD[15:0] Dead-Time Value Update for PWMLx Output

Defines the dead-time value for PWMLx output. This value must be defined between 0 and CDTY (PWM\_CDTYx). This value is applied only at the beginning of the next channel x PWM period.

#### Bits 15:0 – DTHUPD[15:0] Dead-Time Value Update for PWMHx Output

Defines the dead-time value for PWMHx output. This value must be defined between 0 and the value (CPRD – CDTY) (PWM\_CPRDx and PWM\_CDTYx). This value is applied only at the beginning of the next channel x PWM period.

### Electrical Characteristics for SAM ...

| Symbol         | Parameter                              | Conditions | Min  | Typ(1) | Max | Unit |

|----------------|----------------------------------------|------------|------|--------|-----|------|

|                |                                        | Gain=2     | -0.3 | 0.3    | 1.4 |      |

|                |                                        | Gain=4     | -0.3 | 0.7    | 3.3 |      |

|                | Single-Ended Mode                      |            |      |        |     |      |

| Eo             | Single-ended Offset Error (see Note 1) | Gain=1     | -20  | -      | 35  | LSB  |

|                |                                        | Gain=1     | 0.3  | 0.7    | 1.8 |      |

| E <sub>G</sub> | Single-ended Gain Error                | Gain=2     | 0.3  | 1.3    | 3.6 | %    |

|                |                                        |            | 0.3  | 1.7    | 4.7 |      |

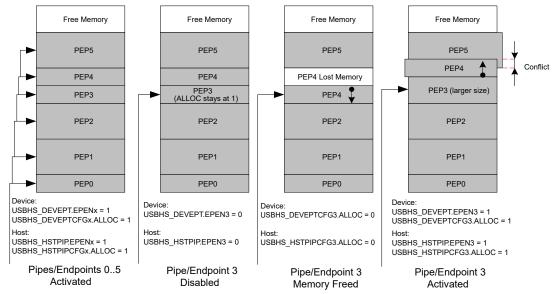

### 58.8.6 AFE Channel Input Impedance Figure 58-15. Input Channel Model

where:

- Z<sub>IN</sub> is input impedance in Single-ended or Differential mode

- C<sub>IN</sub> = 2 to 8 pF ±20% depending on the gain value and mode (SE or DIFF); temperature dependency is negligible

- $R_{ON}$  is typical 2 k $\Omega$  and 8 k $\Omega$  max (worst case process and high temperature)

The following formula is used to calculate input impedance:

$$Z_{\rm IN} = \frac{1}{f_S \times C_{\rm IN}}$$

where:

- $f_S$  is the sampling frequency of the AFE channel

- Typ values are used to compute AFE input impedance Z<sub>IN</sub>

### Table 58-37. Input Capacitance (CIN) Values

| Gain Selection | Single-ended | Differential | Unit |

|----------------|--------------|--------------|------|

| 1              | 2            | 2            | pF   |

| 2              | 4            | 4            |      |

| 4              | 8            | 8            |      |

### **Electrical Characteristics for SAM E70/S70**

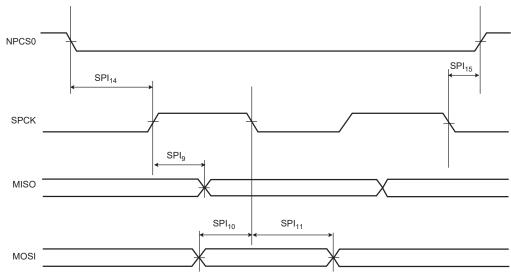

#### 59.13.1.6.1 Maximum SPI Frequency

The following formulas give maximum SPI frequency in Master read and write modes and in Slave read and write modes.

$f_{\text{SPCK}}$ max =  $\frac{1}{\text{SPI}_0(\text{or SPI}_3) + t_{\text{valid}}}$

t<sub>valid</sub> is the slave time response to output data after detecting an SPCK edge.

For a nonvolatile memory with  $t_{valid}$  (or  $t_v$ ) = 5 ns,  $f_{SPCK}max$  = 57 MHz at  $V_{DDIO}$  = 3.3V.

$$f_{\text{SPCK}} \text{max} = \frac{1}{2x(SPI_{6max}(\text{or SPI}_{9max}) + t_{\text{setup}})}$$

t<sub>setup</sub> is the setup time from the master before sampling data.

#### Master Write Mode

The SPI sends data to a slave device only, e.g. an LCD. The limit is given by  $SPI_2$  (or  $SPI_5$ ) timing. Since it gives a maximum frequency above the maximum pad speed (see I/O Characteristics), the max SPI frequency is the one from the pad.

#### Master Read Mode

#### Slave Read Mode

In slave mode, SPCK is the input clock for the SPI. The max SPCK frequency is given by setup and hold timings  $SPI_7/SPI_8$  (or  $SPI_{10}/SPI_{11}$ ). Since this gives a frequency well above the pad limit, the limit in slave read mode is given by SPCK pad.

#### Slave Write Mode

#### 59.13.1.6.2 SPI Timings

Timings are given in the following domains:

- 1.8V domain: V<sub>DDIO</sub> from 1.7V to 1.95V, maximum external capacitor = 20 pF

- 3.3V domain: V<sub>DDIO</sub> from 2.85V to 3.6V, maximum external capacitor = 40 pF

## **Electrical Characteristics for SAM E70/S70**

| Symbol            | Parameter                                  | Conditions  | Min   | Max  | Unit |

|-------------------|--------------------------------------------|-------------|-------|------|------|

| SPI0              | MISO Setup time before SPCK rises (master) | 3.3V domain | 12.4  | -    | ns   |

|                   |                                            | 1.8V domain | 14.6  | -    | ns   |

| SPI1              | MISO Hold time after SPCK rises (master)   | 3.3V domain | 0     | -    | ns   |

|                   |                                            | 1.8V domain | 0     | -    | ns   |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)         | 3.3V domain | -3.7  | 2.2  | ns   |

|                   |                                            | 1.8V domain | -3.8  | 2.7  | ns   |

| SPI <sub>3</sub>  | MISO Setup time before SPCK falls (master) | 3.3V domain | 12.6  | -    | ns   |

|                   |                                            | 1.8V domain | 15.13 | -    | ns   |

| SPI4              | MISO Hold time after SPCK falls (master)   | 3.3V domain | 0     | -    | ns   |

|                   |                                            | 1.8V domain | 0     | -    | ns   |

| SPI5              | SPCK falling to MOSI Delay (master)        | 3.3V domain | -3.6  | 2.0  | ns   |

|                   |                                            | 1.8V domain | -3.3  | 2.8  | ns   |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)         | 3.3V domain | 3.0   | 11.9 | ns   |

|                   |                                            | 1.8V domain | 3.5   | 13.9 | ns   |

| SPI7              | MOSI Setup time before SPCK rises (slave)  | 3.3V domain | 1.2   | -    | ns   |

|                   |                                            | 1.8V domain | 1.5   | -    | ns   |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)    | 3.3V domain | 0.6   | -    | ns   |

|                   |                                            | 1.8V domain | 0.8   | -    | ns   |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)          | 3.3V domain | 3.0   | 12.0 | ns   |

|                   |                                            | 1.8V domain | 3.4   | 13.7 | ns   |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)  | 3.3V domain | 1.2   | -    | ns   |

|                   |                                            | 1.8V domain | 1.5   | -    | ns   |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)    | 3.3V domain | 0.6   | -    | ns   |

|                   |                                            | 1.8V domain | 0.8   | -    | ns   |

| SPI <sub>12</sub> | NPCS setup to SPCK rising (slave)          | 3.3V domain | 3.9   | -    | ns   |

|                   |                                            | 1.8V domain | 4.4   | -    | ns   |

| SPI <sub>13</sub> | NPCS hold after SPCK falling (slave)       | 3.3V domain | 0     | -    | ns   |

|                   |                                            | 1.8V domain | 0     | -    | ns   |

| SPI <sub>14</sub> | NPCS setup to SPCK falling (slave)         | 3.3V domain | 4.0   | -    | ns   |

|                   |                                            | 1.8V domain | 4.1   | -    | ns   |

#### Table 59-56. SPI Timings

## Schematic Checklist

| Signal Name | Recommended Pin<br>Connection                                                                            | Description                                                                                                                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                                                          | Decoupling/filtering capacitors must be added to improve startup stability and reduce source voltage drop.                                                                                                                    |

|             |                                                                                                          | Supply ripple must not exceed 20 mVrms for 10 kHz to 20 MHz range.                                                                                                                                                            |

|             |                                                                                                          | Awarning Powerup and powerdown sequences given in the<br>"Power Considerations" chapter must be respected.                                                                                                                    |

| VDDPLL      | Decoupling/filtering<br>capacitors ferrite beads<br>(100 nF and 470 Ohm<br>@ 100 MHz) <sup>(1) (2)</sup> | Powers the PLLA and the fast RC oscillator.<br>The VDDPLL power supply pin draws small current, but it is<br>noise sensitive. Care must be taken in VDDPLL power supply<br>routing, decoupling and also on bypass capacitors. |

|             |                                                                                                          | Supply ripple must not exceed 20 mVrms for 10 kHz to 10 MHz range and 10 mVrms for higher frequencies.                                                                                                                        |

| VDDUTMIC    | Decoupling/filtering<br>capacitors ferrite beads<br>(100 nF and 470 Ohm<br>@ 100 MHz) <sup>(1) (2)</sup> | Powers the USB transceiver core.<br>Must always be connected even if the USB is not used.                                                                                                                                     |

|             |                                                                                                          | Decoupling/filtering capacitors/ferrite beads must be added to improve startup stability and reduce source voltage drop.                                                                                                      |

|             |                                                                                                          | Supply ripple must not exceed 10 mVrms for 10 kHz to 10 MHz range.                                                                                                                                                            |

| GND         | Voltage Regulator, Core<br>Chip and Peripheral I/O<br>lines ground                                       | GND pins are common to VDDIN, VDDCORE and VDDIO<br>pins.<br>GND pins should be connected as shortly as possible to the                                                                                                        |

|             |                                                                                                          | system ground plane.                                                                                                                                                                                                          |

| GNDUTMI     | UDPHS and UHPHS<br>UTMI+ Core and<br>interface ground                                                    | GNDUTMI pins are common to VDDUTMII and VDDUTMIC<br>pins.<br>GNDUTMI pins should be connected as shortly as possible to<br>the system ground plane.                                                                           |

| GNDPLL      | PLLA cell and Main<br>Oscillator ground                                                                  | GNDPLL pin is provided for VDDPLL pin. GNDPLL pin should<br>be connected as shortly as possible to the system ground<br>plane.                                                                                                |

| GNDANA      | Analog ground                                                                                            | GNDANA pins are common to AFE, DAC and ACC supplied by VDDIN pin.<br>GNDANA pins should be connected as shortly as possible to the system ground plane.                                                                       |

| GNDPLLUSB   | USB PLL ground                                                                                           | GNDPLLUSB pin is provided for VDDPLLUSB pin.<br>GNDPLLUSB pin should be connected as shortly as possible<br>to the system ground plane.                                                                                       |