Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M7                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 300MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, SSC, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 44                                                                         |

| Program Memory Size        | 2MB (2M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 384К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                               |

| Data Converters            | A/D 5x12b; D/A 1x12b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70j21b-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Signal Description

| Signal Name                                 | Function                                         | Туре   | Active<br>Level | Voltage<br>Reference | Comments                                                                           |

|---------------------------------------------|--------------------------------------------------|--------|-----------------|----------------------|------------------------------------------------------------------------------------|

| PWMCx_PWMH0<br>-<br>PWMCx_PWMH3             | Waveform Output High<br>for Channel 0–3          | Output | -               | -                    | -                                                                                  |

| PWMCx_PWML0-<br>PWMCx_PWML3                 | Waveform Output Low<br>for Channel 0–3           | Output | _               | _                    | Only output in<br>complementary<br>mode when dead<br>time insertion is<br>enabled. |

| PWMCx_PWMFI0<br>-<br>PWMCx_PWMFI2           | Fault Input                                      | Input  | -               | -                    | -                                                                                  |

| PWMCx_PWMEX<br>TRG0-<br>PWMCx_PWMEX<br>TRG1 |                                                  |        | _               | _                    | _                                                                                  |

| Serial Peripheral In                        | terface - SPI(x=[01])                            |        |                 |                      |                                                                                    |

| SPIx_MISO                                   | Master In Slave Out                              | I/O    | _               | -                    | _                                                                                  |

| SPIx_MOSI                                   | Master Out Slave In                              | I/O    | _               | -                    | _                                                                                  |

| SPIx_SPCK                                   | SPI Serial Clock                                 | I/O    | _               | _                    | _                                                                                  |

| SPIx_NPCS0                                  | SPI Peripheral Chip<br>Select 0                  | I/O    | Low             | -                    | -                                                                                  |

| SPIx_NPCS1-<br>SPIx_NPCS3                   | SPI Peripheral Chip<br>Select                    | Output | Low             | -                    | _                                                                                  |

| Quad IO SPI - QSP                           | 1                                                |        |                 |                      |                                                                                    |

| QSCK                                        | QSPI Serial Clock                                | Output | _               | _                    | _                                                                                  |

| QCS                                         | QSPI Chip Select                                 | Output | _               | -                    | -                                                                                  |

| QIO0–QIO3                                   | QSPI I/O<br>QIO0 is QMOSI<br>Master Out Slave In | I/O    | -               | -                    | -                                                                                  |

|                                             | QIO1 is QMISO<br>Master In Slave Out             |        |                 |                      |                                                                                    |

| Two-Wire Interface                          | - TWIHS(x=02)                                    |        |                 |                      |                                                                                    |

| TWDx                                        | TWIx Two-wire Serial<br>Data                     | I/O    | _               | -                    | -                                                                                  |

| TWCKx                                       | TWIx Two-wire Serial<br>Clock                    | I/O    | -               | -                    | -                                                                                  |

| Analog                                      |                                                  |        |                 |                      |                                                                                    |

## 21.3.2 Chip ID Extension Register

| Name:     | CHIPID_EXID |

|-----------|-------------|

| Offset:   | 0x4         |

| Reset:    | -           |

| Property: | Read-only   |

| Bit    | 31 | 30 | 29 | 28   | 27     | 26 | 25 | 24 |

|--------|----|----|----|------|--------|----|----|----|

|        |    |    |    | EXID | 31:24] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  |    |    |    |      |        |    |    |    |

|        |    |    |    |      |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19     | 18 | 17 | 16 |

|        |    |    |    | EXID | 23:16] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  |    |    |    |      |        |    |    |    |

|        |    |    |    |      |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11     | 10 | 9  | 8  |

|        |    |    |    | EXID | [15:8] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  |    |    |    |      |        |    |    |    |

|        |    |    |    |      |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3      | 2  | 1  | 0  |

|        |    |    |    | EXI  | D[7:0] |    |    |    |

| Access | R  | R  | R  | R    | R      | R  | R  | R  |

| Reset  |    |    |    |      |        |    |    |    |

**Bits 31:0 – EXID[31:0]** Chip ID Extension This field is cleared if CHIPID\_CIDR.EXT = 0.

| Value | Name     | Description |

|-------|----------|-------------|

| 0xX   | Reserved | Reserved    |

#### 22.4.2.3 Data Read Optimization

The organization of the Flash in 128 bits is associated with two 128-bit prefetch buffers and one 128-bit data read buffer, thus providing maximum system performance. This buffer is added in order to store the requested data plus all the data contained in the 128-bit aligned data. This speeds up sequential data reads if, for example, FWS is equal to 1 (see Figure 22-6). The data read optimization is enabled by default. If the bit EEFC\_FMR.SCOD is set, this buffer is disabled and the data read is no longer optimized.

Note: No consecutive data read accesses are mandatory to benefit from this optimization.

| Figure 22-6             | 6. Data | a Read ( | Optimiz   | zation | for FWS | 5 = 1     |          |       |       |       |             |             |

|-------------------------|---------|----------|-----------|--------|---------|-----------|----------|-------|-------|-------|-------------|-------------|

| Master Clock            |         |          |           |        |         |           |          |       |       |       |             |             |

| ARM Request<br>(32-bit) |         |          | 1         | 1      | 1       | 1         |          | 1     | 1     | 1     | 1           | 1           |

|                         | @Byte 0 |          | @4        | @ 8    | @ 12    | @ 16      |          | @ 20  | @ 24  | @ 28  | @ 32        | @ 36        |

| Flash Access            | xxx     | X Bytes  | 0–15      |        |         | X         | Bytes 16 | 6–31  |       |       | X_          | Bytes 32–47 |

| Buffer (128 bits)       | X       | XXX      |           | (      | By      | ytes 0–15 |          | X     |       | E     | Bytes 16–31 |             |

| Data to ARM             | χ_,     | XX       | Bytes 0-3 | 4-7    | X 8–11  | (12–15)   |          | 16–19 | 20–23 | 24–27 | 28–31       | 32–35       |

#### 22.4.3 Flash Commands

The EEFC offers a set of commands to manage programming the Flash memory, locking and unlocking lock regions, consecutive programming, locking and full Flash erasing, etc.

The commands are listed in the following table.

#### Table 22-1. Set of Commands

| Command                                 | Value | Mnemonic |

|-----------------------------------------|-------|----------|

| Get Flash Descriptor                    | 0x00  | GETD     |

| Write Page                              | 0x01  | WP       |

| Write Page and Lock                     | 0x02  | WPL      |

| Erase Page and Write Page               | 0x03  | EWP      |

| Erase Page and Write Page and then Lock | 0x04  | EWPL     |

| Erase All                               | 0x05  | EA       |

| Erase Pages                             | 0x07  | EPA      |

| Set Lock Bit                            | 0x08  | SLB      |

| Clear Lock Bit                          | 0x09  | CLB      |

| Get Lock Bit                            | 0x0A  | GLB      |

| Set GPNVM Bit                           | 0x0B  | SGPB     |

| Clear GPNVM Bit                         | 0x0C  | CGPB     |

## **Power Management Controller (PMC)**

#### 31.20.27 PMC Oscillator Calibration Register

| Name:     | PMC_OCR    |

|-----------|------------|

| Offset:   | 0x0110     |

| Reset:    | 0x00404040 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31    | 30 | 29 | 28 | 27         | 26 | 25 | 24 |

|--------|-------|----|----|----|------------|----|----|----|

|        |       |    |    |    |            |    |    |    |

| Access |       |    |    |    | -          |    |    |    |

| Reset  |       |    |    |    |            |    |    |    |

|        |       |    |    |    |            |    |    |    |

| Bit    | 23    | 22 | 21 | 20 | 19         | 18 | 17 | 16 |

|        | SEL12 |    |    |    | CAL12[6:0] |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

|        |       |    |    |    |            |    |    |    |

| Bit    | 15    | 14 | 13 | 12 | 11         | 10 | 9  | 8  |

|        | SEL8  |    |    |    | CAL8[6:0]  |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

|        |       |    |    |    |            |    |    |    |

| Bit    | 7     | 6  | 5  | 4  | 3          | 2  | 1  | 0  |

|        | SEL4  |    |    |    | CAL4[6:0]  |    |    |    |

| Access |       |    |    |    |            |    |    |    |

| Reset  | 0     | 1  | 0  | 0  | 0          | 0  | 0  | 0  |

Bit 23 – SEL12 Selection of Main RC Oscillator Calibration Bits for 12 MHz

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Factory-determined value stored in Flash memory.       |

| 1     | Value written by user in CAL12 field of this register. |

**Bits 22:16 – CAL12[6:0]** Main RC Oscillator Calibration Bits for 12 MHz Calibration bits applied to the RC Oscillator when SEL12 is set.

Bit 15 – SEL8 Selection of Main RC Oscillator Calibration Bits for 8 MHz

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Factory-determined value stored in Flash memory.      |

| 1     | Value written by user in CAL8 field of this register. |

**Bits 14:8 – CAL8[6:0]** Main RC Oscillator Calibration Bits for 8 MHz Calibration bits applied to the RC Oscillator when SEL8 is set.

Bit 7 – SEL4 Selection of Main RC Oscillator Calibration Bits for 4 MHz

## Parallel Input/Output Controller (PIO)

#### 32.6.1.21 PIO Pull-Up Disable Register

| Name:     | PIO_PUDR   |

|-----------|------------|

| Offset:   | 0x0060     |

| Property: | Write-only |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Pull-Up Disable

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | No effect.                                    |

| 1     | Disables the pullup resistor on the I/O line. |

## Static Memory Controller (SMC)

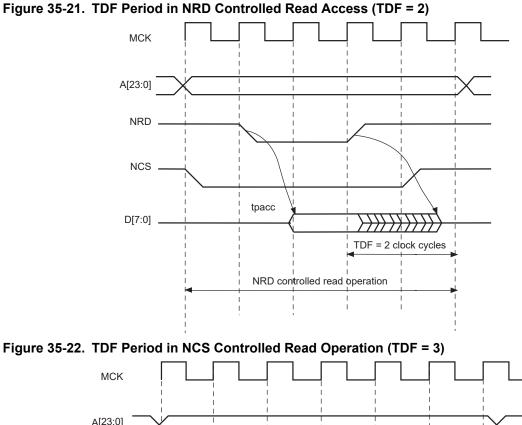

### 35.12.2 TDF Optimization Enabled (SMC\_MODE.TDF\_MODE = 1)

When SMC\_MODE.TDF\_MODE is set to 1 (TDF optimization is enabled), the SMC takes advantage of the setup period of the next access to optimize the number of wait states cycle to insert.

The following figure shows a read access controlled by NRD, followed by a write access controlled by NWE, on Chip Select 0. Chip Select 0 has been programmed with:

nrd\_hold = 4; SMC\_MODE.read\_mode = 1 (NRD controlled)

nwe\_setup = 3; SMC\_MODE.write\_mode = 1 (NWE controlled)

SMC\_MODE.TDF\_CYCLES = 6; SMC\_MODE.TDF\_MODE = 1 (optimization enabled).

|                 | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_LC<br>0x144<br>0x00000000<br>- |    |    |        |    |    |        |

|-----------------|-----------------------------------------|-------------------------------------|----|----|--------|----|----|--------|

| Bit             | 31                                      | 30                                  | 29 | 28 | 27     | 26 | 25 | 24     |

| •               |                                         |                                     |    |    |        |    |    |        |

| Access<br>Reset |                                         |                                     |    |    |        |    |    |        |

| Resei           |                                         |                                     |    |    |        |    |    |        |

| Bit             | 23                                      | 22                                  | 21 | 20 | 19     | 18 | 17 | 16     |

|                 |                                         |                                     |    |    |        |    |    |        |

| Access          |                                         |                                     |    |    |        |    |    |        |

| Reset           |                                         |                                     |    |    |        |    |    |        |

|                 |                                         |                                     |    |    |        |    |    |        |

| Bit             | 15                                      | 14                                  | 13 | 12 | 11     | 10 | 9  | 8      |

|                 |                                         |                                     |    |    |        |    |    | L[9:8] |

| Access          |                                         |                                     |    |    |        |    | R  | R      |

| Reset           |                                         |                                     |    |    |        |    | 0  | 0      |

| Dit             | 7                                       | c                                   | F  | 4  | 3      | 2  | 4  | 0      |

| Bit             | 7                                       | 6                                   | 5  | 4  | _[7:0] | 2  | 1  | 0      |

| A               |                                         |                                     |    |    |        |    |    |        |

| Access          | R                                       | R                                   | R  | R  | R      | R  | R  | R      |

| Reset           | 0                                       | 0                                   | 0  | 0  | 0      | 0  | 0  | 0      |

### 38.8.55 GMAC Late Collisions Register

### Bits 9:0 - LCOL[9:0] Late Collisions

This register counts the number of late collisions occurring after the slot time (512 bits) has expired. In 10/100 mode, late collisions are counted twice i.e., both as a collision and a late collision.

### 38.8.67 GMAC 256 to 511 Byte Frames Received Register

| Bit       31       30       29       28       27       26       25       24         NFRX[31:24]         Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R<                                                                                                                                                                                                                                                                                                                       |        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TBFR511<br>0x174<br>0x00000000<br>- |    |       |        |    |    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|------------------------------------------|----|-------|--------|----|----|----|

| Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R <td>Bit</td> <td>31</td> <td>30</td> <td>29</td> <td>28</td> <td>27</td> <td>26</td> <td>25</td> <td>24</td>                                                                                                                                                                                                   | Bit    | 31                                      | 30                                       | 29 | 28    | 27     | 26 | 25 | 24 |

| Reset       0       0       0       0       0       0       0       0         Bit       23       22       21       20       19       18       17       16         Access       R       R       R       R       R       R       R       R       R       R         Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R                                                                                                                                                                                                                                                                                                                               |        |                                         |                                          |    | NFRX[ | 31:24] |    |    |    |

| Bit     23     22     21     20     19     18     17     16       Access     R     R     R     R     R     R     R     R       Access     R     R     R     R     R     R     R     R       Bit     15     14     13     12     11     10     9     8       Access     R     R     R     R     R     R     R       Bit     7     6     5     4     3     2     1     0       Bit     7     6     5     4     3     2     1     0       Access     R     R     R     R     R     R     R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Access | R                                       | R                                        | R  | R     | R      | R  | R  | R  |

| Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R <td>Reset</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td>                                                                                                                                                                                                         | Reset  | 0                                       | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

| Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                      |        |                                         |                                          |    |       |        |    |    |    |

| Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R <td>Bit</td> <td>23</td> <td>22</td> <td>21</td> <td>20</td> <td>19</td> <td>18</td> <td>17</td> <td>16</td>                                                                                                                                                                                                   | Bit    | 23                                      | 22                                       | 21 | 20    | 19     | 18 | 17 | 16 |

| Reset       0       0       0       0       0       0       0       0       0         Bit       15       14       13       12       11       10       9       8         Access       R       R       R       R       R       R       R       R         Access       R       10       0       0       0       0       0       0         Bit       7       6       5       4       3       2       1       0         Bit       7       6       7       8       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7       7                                                                                                                                                                                                                                                                                                                                        |        |                                         |                                          |    | NFRX[ | 23:16] |    |    |    |

| Bit       15       14       13       12       11       10       9       8         Model       NFRX[15:8]       NFRX[15:8]       NFRX[15:8]       NFRX[15:8]       NFRX[15:8]       NFRX[15:8]         Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R<                                                                                                                                                                                                                                                                                         | Access | R                                       | R                                        | R  | R     | R      | R  | R  | R  |

| NFRX[15:8]         Access       R       R       R       R       R       R       R         Reset       0       0       0       0       0       0       0       0         Bit       7       6       5       4       3       2       1       0         Access       R       R       R       R       R       R       R       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reset  | 0                                       | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

| NFRX[15:8]         Access       R       R       R       R       R       R       R         Reset       0       0       0       0       0       0       0       0         Bit       7       6       5       4       3       2       1       0         Access       R       R       R       R       R       R       R       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                         |                                          |    |       |        |    |    |    |

| Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R <td>Bit</td> <td>15</td> <td>14</td> <td>13</td> <td>12</td> <td>11</td> <td>10</td> <td>9</td> <td>8</td>                                                                                 | Bit    | 15                                      | 14                                       | 13 | 12    | 11     | 10 | 9  | 8  |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td></td> <td></td> <td></td> <td></td> <td>NFRX</td> <td>[15:8]</td> <td></td> <td></td> <td></td>                                                                                         |        |                                         |                                          |    | NFRX  | [15:8] |    |    |    |

| Bit       7       6       5       4       3       2       1       0         NFRX[7:0]       NFRX[7:0] | Access | R                                       | R                                        | R  | R     | R      | R  | R  | R  |

| NFRX[7:0]           Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                      | Reset  | 0                                       | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

| NFRX[7:0]           Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                      |        |                                         |                                          |    |       |        |    |    |    |

| Access R R R R R R R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit    | 7                                       | 6                                        | 5  | 4     | 3      | 2  | 1  | 0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                                         |                                          |    | NFRX  | ([7:0] |    |    |    |

| Reset 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Access | R                                       | R                                        | R  | R     | R      | R  | R  | R  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reset  | 0                                       | 0                                        | 0  | 0     | 0      | 0  | 0  | 0  |

Bits 31:0 - NFRX[31:0] 256 to 511 Byte Frames Received without Error

This bit fields counts the number of 256 to 511 byte frames successfully received without error. Excludes pause frames, and is only incremented if the frame is successfully filtered and copied to memory.

## USB High-Speed Interface (USBHS)

| Offset | Name                  | Bit Pos. |           |            |          |           |               |           |          |           |

|--------|-----------------------|----------|-----------|------------|----------|-----------|---------------|-----------|----------|-----------|

|        |                       |          | SHORTPACK |            |          |           |               |           |          |           |

|        |                       | 7:0      | ETIEC     | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC        | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0644 | USBHS_HSTPIPID        | 15:8     |           | FIFOCONC   |          | NBUSYBKEC |               |           |          |           |

|        | R9 (INTPIPES)         | 23:16    |           |            |          |           |               |           | PFREEZEC | PDISHDMAC |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       |          | SHORTPACK |            |          |           |               |           |          |           |

|        |                       | 7:0      | ETIEC     | CRCERREC   | OVERFIEC | NAKEDEC   | PERREC        | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0644 | USBHS_HSTPIPID        | 15:8     | 2.1.20    | FIFOCONC   |          | NBUSYBKEC |               |           |          |           |

| 0,0044 | R9 (ISOPIPES)         | 23:16    |           |            |          | NBOOTBREO |               |           | PFREEZEC | PDISHDMAC |

|        |                       | 31:24    |           |            |          |           |               |           | FINELZEC | PDISHDMA  |

| 00040  |                       | 31.24    |           |            |          |           |               |           |          |           |

| 0x0648 | December              |          |           |            |          |           |               |           |          |           |

|        | Reserved              |          |           |            |          |           |               |           |          |           |

| 0x064F |                       |          |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0x0650 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ0                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0,0654 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x0654 | RQ1                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN<br>RQ2 | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x0658 |                       | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | 0[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN        | 15:8     |           |            |          |           | -[]           |           |          | INMODE    |

| 0x065C | RQ3                   | 23:16    |           |            |          |           |               |           |          |           |

|        | T CQ O                | 31:24    |           |            |          |           |               |           |          |           |

|        |                       |          |           |            |          | INDC      | 17.01         |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | <b>λ[1:0]</b> |           |          | INNODE    |

| 0x0660 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ4                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

| 0x0664 | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ5                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

| 0x0668 |                       | 7:0      |           |            |          | INRC      | Q[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

|        | RQ6                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | 7:0      |           |            |          | INRG      | Q[7:0]        |           |          |           |

|        | USBHS_HSTPIPIN        | 15:8     |           |            |          |           |               |           |          | INMODE    |

| 0x066C | RQ7                   | 23:16    |           |            |          |           |               |           |          |           |

|        |                       | 31:24    |           |            |          |           |               |           |          |           |

|        |                       | • ···E 1 |           |            |          |           |               |           |          |           |

## High-Speed Multimedia Card Interface (HSMCI)

| Value | Name    | Description       |

|-------|---------|-------------------|

| 6     | 65536   | CSTOCYC x 65536   |

| 7     | 1048576 | CSTOCYC x 1048576 |

Bits 3:0 – CSTOCYC[3:0] Completion Signal Timeout Cycle Number

This field determines the maximum number of Master Clock cycles that the HSMCI waits between two data block transfers. Its value is calculated by (CSTOCYC x Multiplier).

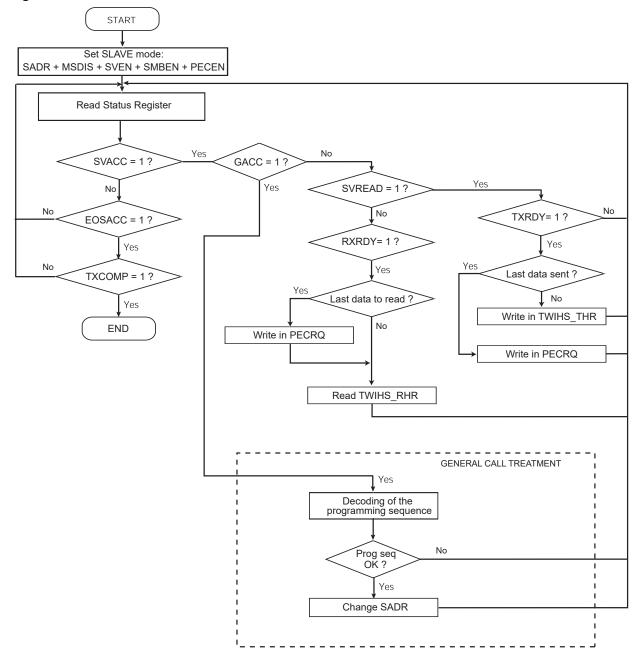

## **Two-wire Interface (TWIHS)**

- Bit 7 UNRE Underrun Error Interrupt Enable

- Bit 6 OVRE Overrun Error Interrupt Enable

- Bit 5 GACC General Call Access Interrupt Enable

- Bit 4 SVACC Slave Access Interrupt Enable

- Bit 2 TXRDY Transmit Holding Register Ready Interrupt Enable

- Bit 1 RXRDY Receive Holding Register Ready Interrupt Enable

- Bit 0 TXCOMP Transmission Completed Interrupt Enable

## Universal Synchronous Asynchronous Receiver Transc...

- Bit 14 LINID LIN Identifier Sent or LIN Identifier Received Interrupt Mask

- Bit 13 LINBK LIN Break Sent or LIN Break Received

- Bit 9 TXEMPTY TXEMPTY Interrupt Mask

- Bit 8 TIMEOUT Timeout Interrupt Mask

- Bit 7 PARE Parity Error Interrupt Mask

- **Bit 6 FRAME** Framing Error Interrupt Mask

- Bit 5 OVRE Overrun Error Interrupt Mask

- Bit 1 TXRDY TXRDY Interrupt Mask

- Bit 0 RXRDY RXRDY Interrupt Mask

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.23 USART Baud Rate Generator Register

| Name:     | US_BRGR    |

|-----------|------------|

| Offset:   | 0x0020     |

| Reset:    | 0x0        |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28               | 27    | 26 | 25      | 24 |

|--------|----|----|----|------------------|-------|----|---------|----|

|        |    |    |    |                  |       |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  |    |    |    |                  |       |    |         |    |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 23 | 22 | 21 | 20               | 19    | 18 | 17      | 16 |

|        |    |    |    |                  |       |    | FP[2:0] |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  |    |    |    |                  |       | 0  | 0       | 0  |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 15 | 14 | 13 | 12               | 11    | 10 | 9       | 8  |

|        |    |    |    | CD[ <sup>*</sup> | 15:8] |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0  | 0       | 0  |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 7  | 6  | 5  | 4                | 3     | 2  | 1       | 0  |

|        |    |    |    | CD               | 7:0]  |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0  | 0       | 0  |

#### Bits 18:16 - FP[2:0] Fractional Part

▲ WARNING When the value of field FP is greater than 0, the SCK (oversampling clock) generates nonconstant duty cycles. The SCK high duration is increased by "selected clock" period from time to time. The duty cycle depends on the value of the CD field.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Fractional divider is disabled.            |

| 1-7   | Baud rate resolution, defined by FP × 1/8. |

#### Bits 15:0 – CD[15:0] Clock Divider

| CD | USART_MODE ≠ IS | USART_MODE = |                   |         |  |

|----|-----------------|--------------|-------------------|---------|--|

|    | SYNC = 0        |              | SYNC = 1          | ISO7816 |  |

|    | OVER = 0        | OVER = 1     | or                |         |  |

|    |                 |              | USART_MODE = SPI  |         |  |

|    |                 |              | (Master or Slave) |         |  |

(e.g. MediaLB or HBI channel). All entries are indexed according to a fixed physical address assigned to every Rx/Tx channel (as shown in the following table). The value stored in a CAT entry includes a 6-bit Connection Label, which provides a pointer to the CDT. To complete a logical channel and form a routing connection, system software must assign the same Connection Label to both the Rx and Tx channels.

| Peripheral | Tx Channels | Rx Channels      | CAT Start Index | CAT End Index | Entries |

|------------|-------------|------------------|-----------------|---------------|---------|

| MediaLB    | 0 to 64     | 64 - Tx Channels | 0               | 63            | 64      |

| HBI        | 0 to 64     | 64 - Tx Channels | 64              | 127           | 64      |

### Table 48-11. CAT Entry Map

The format of a full CAT entry is shown in Table 48-12, with field descriptions described in Table 48-13. All reserved bits of a CAT entry field should be written as zero.

|  | Table 48-12. | CAT Entry | Formats |

|--|--------------|-----------|---------|

|--|--------------|-----------|---------|

| Channel Type | 15   | 14  | 13   | 12  | 11 | 10          | 9      | 8 | 7   | 6          | 5  | 4    | 3  | 2 | 1 | 0 |

|--------------|------|-----|------|-----|----|-------------|--------|---|-----|------------|----|------|----|---|---|---|

| Isochronous  | rsvd | FCE | rsvd | RNW | CE | CT[2:       | 0] = 3 | 3 | rsv | d          | CL | [5:0 | )] |   |   |   |

| Asynchronous | rsvd |     | MT   | RNW | CE | CT[2:0] = 2 |        |   | rsv | vd CL[5:0] |    |      |    |   |   |   |

| Control      | rsvd |     | MT   | RNW | CE | CT[2:       | 0] = 1 | 1 | rsv | d          | CL | [5:0 | )] |   |   |   |

| Synchronous  | rsvd | MFE | MT   | RNW | CE | CT[2:       | 0] = ( | ) | rsv | d          | CL | [5:0 | )] |   |   |   |

### Table 48-13. CAT Field Definitions

| Field   | Description                                                                                                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL[5:0] | Connection Label (offset into CDT)                                                                                                                                              |

| CT[2:0] | Channel Type (Others):<br>111 = Reserved<br>110 = Reserved<br>101 = Reserved<br>100 = Reserved<br>011 = Isochronous<br>010 = Asynchronous<br>001 = Control<br>000 = Synchronous |

| CE      | Channel Enable:<br>1 = Enabled<br>0 = Disabled                                                                                                                                  |

| RNW     | Read Not Write:<br>1 = Read<br>0 = Write                                                                                                                                        |

| MT      | Mute Enable <sup>(1)</sup> :<br>1 = Enabled<br>0 = Disabled                                                                                                                     |

## **Controller Area Network (MCAN)**

| Offset | Name        | Bit Pos. |            |          |        |           |        |           |        |        |  |

|--------|-------------|----------|------------|----------|--------|-----------|--------|-----------|--------|--------|--|

|        |             | 15:8     | TIE15      | TIE14    | TIE13  | TIE12     | TIE11  | TIE10     | TIE9   | TIE8   |  |

|        |             | 23:16    | TIE23      | TIE22    | TIE21  | TIE20     | TIE19  | TIE18     | TIE17  | TIE16  |  |

|        |             | 31:24    | TIE31      | TIE30    | TIE29  | TIE28     | TIE27  | TIE26     | TIE25  | TIE24  |  |

|        |             | 7:0      | CFIE7      | CFIE6    | CFIE5  | CFIE4     | CFIE3  | CFIE2     | CFIE1  | CFIE0  |  |

| 0xE4   | MCAN TXBCIE | 15:8     | CFIE15     | CFIE14   | CFIE13 | CFIE12    | CFIE11 | CFIE10    | CFIE9  | CFIE8  |  |

| 0,2,4  | WOAN_TABOL  | 23:16    | CFIE23     | CFIE22   | CFIE21 | CFIE20    | CFIE19 | CFIE18    | CFIE17 | CFIE16 |  |

|        |             | 31:24    | CFIE31     | CFIE30   | CFIE29 | CFIE28    | CFIE27 | CFIE26    | CFIE25 | CFIE24 |  |

| 0xE8   |             |          |            |          |        |           |        |           |        |        |  |

|        | Reserved    |          |            |          |        |           |        |           |        |        |  |

| 0xEF   |             |          |            |          |        |           |        |           |        |        |  |

|        | MCAN TXEFC  | 7:0      | EFSA[5:0]  |          |        |           |        |           |        |        |  |

| 0xF0   |             | 15:8     | EFSA[13:6] |          |        |           |        |           |        |        |  |

| 0,10   |             | 23:16    |            | EFS[5:0] |        |           |        |           |        |        |  |

|        |             | 31:24    |            |          |        | EFWM[5:0] |        |           |        |        |  |

|        |             | 7:0      |            |          |        |           |        |           |        |        |  |

| 0xF4   | MCAN TXEFS  | 15:8     |            |          |        | EFGI[4:0] |        |           |        |        |  |

|        |             | 23:16    |            |          |        |           |        | EFPI[4:0] |        |        |  |

|        |             | 31:24    |            |          |        |           |        |           | TEFL   | EFF    |  |

|        |             | 7:0      |            |          |        |           |        | EFAI[4:0] |        |        |  |

| 0xF8   | MCAN TXEFA  | 15:8     |            |          |        |           |        |           |        |        |  |

|        |             | 23:16    |            |          |        |           |        |           |        |        |  |

|        |             | 31:24    |            |          |        |           |        |           |        |        |  |

## **Controller Area Network (MCAN)**

#### 49.6.14 MCAN Protocol Status Register

|        | Name:<br>Offset:<br>Reset:<br>Property: | MCAN_PSR<br>0x44<br>0x00000707<br>Read-only |      |      |           |    |           |    |

|--------|-----------------------------------------|---------------------------------------------|------|------|-----------|----|-----------|----|

| Bit    | 31                                      | 30                                          | 29   | 28   | 27        | 26 | 25        | 24 |

|        |                                         |                                             |      |      |           |    |           |    |

| Access |                                         |                                             |      |      |           |    |           |    |

| Reset  |                                         |                                             |      |      |           |    |           |    |

| Bit    | 23                                      | 22                                          | 21   | 20   | 19        | 18 | 17        | 16 |

|        |                                         |                                             |      |      | TDCV[6:0] |    |           |    |

| Access |                                         | R                                           | R    | R    | R         | R  | R         | R  |

| Reset  |                                         | 0                                           | 0    | 0    | 0         | 0  | 0         | 0  |

|        |                                         |                                             |      |      |           |    |           |    |

| Bit    | 15                                      | 14                                          | 13   | 12   | 11        | 10 | 9         | 8  |

|        |                                         | PXE                                         | RFDF | RBRS | RESI      |    | DLEC[2:0] |    |

| Access |                                         |                                             |      |      |           |    |           |    |

| Reset  |                                         | 0                                           | 0    | 0    | 0         | 1  | 1         | 1  |

|        |                                         |                                             |      |      |           |    |           |    |

| Bit    |                                         | 6                                           | 5    | 4    | 3         | 2  | 1         | 0  |

|        | BO                                      | EW                                          | EP   |      | [1:0]     |    | LEC[2:0]  |    |

| Access | R                                       | R                                           | R    | R    | R         |    |           |    |

| Reset  | 0                                       | 0                                           | 0    | 0    | 0         | 1  | 1         | 1  |

**Bits 22:16 – TDCV[6:0]** Transmitter Delay Compensation Value 0 to 127: Position of the secondary sample point, in CAN core clock periods, defined by the sum of the measured delay from CANTX to CANRX and MCAN\_TDCR.TDCO.

Bit 14 – PXE Protocol Exception Event (cleared on read)

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | No protocol exception event occurred since last read access |

| 1     | Protocol exception event occurred                           |

Bit 13 – RFDF Received a CAN FD Message (cleared on read)

This bit is set independently from acceptance filtering.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | Since this bit was reset by the CPU, no CAN FD message has been received |

| 1     | Message in CAN FD format with FDF flag set has been received             |

**Bit 12 – RBRS** BRS Flag of Last Received CAN FD Message (cleared on read) This bit is set together with RFDF, independently from acceptance filtering.

## **Controller Area Network (MCAN)**

### 49.6.25 MCAN New Data 1

|        | Name:<br>Offset:<br>Reset:<br>Property: | MCAN_NDAT1<br>0x98<br>0x00000000<br>Read/Write | I    |      |      |      |      |      |

|--------|-----------------------------------------|------------------------------------------------|------|------|------|------|------|------|

| Bit    | 31                                      | 30                                             | 29   | 28   | 27   | 26   | 25   | 24   |

|        | ND31                                    | ND30                                           | ND29 | ND28 | ND27 | ND26 | ND25 | ND24 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 23                                      | 22                                             | 21   | 20   | 19   | 18   | 17   | 16   |

|        | ND23                                    | ND22                                           | ND21 | ND20 | ND19 | ND18 | ND17 | ND16 |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 15                                      | 14                                             | 13   | 12   | 11   | 10   | 9    | 8    |

|        | ND15                                    | ND14                                           | ND13 | ND12 | ND11 | ND10 | ND9  | ND8  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

|        |                                         |                                                |      |      |      |      |      |      |

| Bit    | 7                                       | 6                                              | 5    | 4    | 3    | 2    | 1    | 0    |

|        | ND7                                     | ND6                                            | ND5  | ND4  | ND3  | ND2  | ND1  | ND0  |

| Access | R/W                                     | R/W                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset  | 0                                       | 0                                              | 0    | 0    | 0    | 0    | 0    | 0    |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 - NDx New Data

The register holds the New Data flags of Receive Buffers 0 to 31. The flags are set when the respective Receive Buffer has been updated from a received frame. The flags remain set until the processor clears them. A flag is cleared by writing a '1' to the corresponding bit position. Writing a '0' has no effect. A hard reset will clear the register.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Buffer not updated              |

| 1     | Receive Buffer updated from new message |

## Analog Comparator Controller (ACC)

| Value | Description                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------|

| 0     | No edge occurred (defined by EDGETYP) on analog comparator output since the last read of ACC_ISR.         |

| 1     | A selected edge (defined by EDGETYP) on analog comparator output occurred since the last read of ACC_ISR. |

## 57.5.15 AES GCM Encryption Counter Value Register

| Name:     | AES_CTRR   |

|-----------|------------|

| Offset:   | 0x98       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

| Bit    | 31         | 30 | 29 | 28   | 27     | 26 | 25 | 24 |  |  |  |

|--------|------------|----|----|------|--------|----|----|----|--|--|--|

|        | CTR[31:24] |    |    |      |        |    |    |    |  |  |  |

| Access | R          | R  | R  | R    | R      | R  | R  | R  |  |  |  |

| Reset  | 0          | 0  | 0  | 0    | 0      | 0  | 0  | 0  |  |  |  |

|        |            |    |    |      |        |    |    |    |  |  |  |

| Bit    | 23         | 22 | 21 | 20   | 19     | 18 | 17 | 16 |  |  |  |

|        |            |    |    | CTR[ | 23:16] |    |    |    |  |  |  |

| Access | R          | R  | R  | R    | R      | R  | R  | R  |  |  |  |

| Reset  | 0          | 0  | 0  | 0    | 0      | 0  | 0  | 0  |  |  |  |

|        |            |    |    |      |        |    |    |    |  |  |  |

| Bit    | 15         | 14 | 13 | 12   | 11     | 10 | 9  | 8  |  |  |  |

|        |            |    |    | CTR  | [15:8] |    |    |    |  |  |  |

| Access | R          | R  | R  | R    | R      | R  | R  | R  |  |  |  |

| Reset  | 0          | 0  | 0  | 0    | 0      | 0  | 0  | 0  |  |  |  |

|        |            |    |    |      |        |    |    |    |  |  |  |

| Bit    | 7          | 6  | 5  | 4    | 3      | 2  | 1  | 0  |  |  |  |

|        | CTR[7:0]   |    |    |      |        |    |    |    |  |  |  |

| Access | R          | R  | R  | R    | R      | R  | R  | R  |  |  |  |

| Reset  | 0          | 0  | 0  | 0    | 0      | 0  | 0  | 0  |  |  |  |

**Bits 31:0 – CTR[31:0]** GCM Encryption Counter Reports the current value of the 32-bit GCM counter.