Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 300MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 75                                                                          |

| Program Memory Size        | 1MB (1M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 384K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-VFBGA                                                                   |

| Supplier Device Package    | 100-VFBGA (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70n20a-cfnt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Signal Description

| Signal Name Function                   |                                                                                 | Туре        | Active<br>Level | Voltage<br>Reference | Comments                |

|----------------------------------------|---------------------------------------------------------------------------------|-------------|-----------------|----------------------|-------------------------|

| PCK0–PCK2 Programmable Clock<br>Output |                                                                                 | Output      | _               |                      | _                       |

| Real Time Clock                        |                                                                                 |             |                 |                      |                         |

| RTCOUT0                                | Programmable RTC<br>Waveform Output                                             | Output      | -               | VDDIO                | -                       |

| RTCOUT1                                | Programmable RTC<br>Waveform Output                                             | Output      | -               | -                    | -                       |

| Serial Wire Debug/                     | JTAG Boundary Scan                                                              | I           |                 |                      |                         |

| SWCLK/TCK                              | Serial Wire Clock /<br>Test Clock (Boundary<br>scan mode only)                  | Input       | -               | VDDIO                | -                       |

| TDI                                    | Test Data In (Boundary scan mode only)                                          | Input       | -               | -                    | _                       |

| TDO/TRACESWO                           | Test Data Out<br>(Boundary scan mode<br>only)                                   | Output      | -               |                      | -                       |

| SWDIO/TMS                              | Serial Wire Input/<br>Output / Test Mode<br>Select (Boundary scan<br>mode only) | I/O / Input | -               | -                    | -                       |

| JTAGSEL                                | JTAG Selection                                                                  | Input       | High            |                      | _                       |

| Trace Debug Port                       | ·                                                                               | 1           |                 | 1                    | ·                       |

| TRACECLK                               | Trace Clock                                                                     | Output      | -               | VDDIO                | PCK3 is used for<br>ETM |

| TRACED0–<br>TRACED3                    | Trace Data                                                                      | Output      | -               |                      | -                       |

| Flash Memory                           |                                                                                 |             |                 |                      |                         |

| ERASE                                  | Flash and NVM<br>Configuration Bits<br>Erase Command                            | Input       | High            | VDDIO                | _                       |

| Reset/Test                             |                                                                                 |             |                 |                      |                         |

| NRST                                   | Synchronous<br>Microcontroller Reset                                            | I/O         | Low             | VDDIO                | _                       |

| TST                                    | Test Select                                                                     | Input       | -               |                      | -                       |

| Universal Asynchro                     | nous Receiver Transceiv                                                         | er - UART(> | (=[0:4])        |                      |                         |

## Reset Controller (RSTC)

| Value | Name     | Description                              |

|-------|----------|------------------------------------------|

| 3     | SOFT_RST | Processor reset required by the software |

| 4     | USER_RST | NRST pin detected low                    |

| 5     | -        | Reserved                                 |

| 6     | -        | Reserved                                 |

| 7     | -        | Reserved                                 |

### Bit 0 – URSTS User Reset Status

A high-to-low transition of the NRST pin sets the URSTS. This transition is also detected on the MCK rising edge. If the user reset is disabled (URSTEN = 0 in RSTC\_MR) and if the interrupt is enabled by RSTC\_MR.URSTIEN, URSTS triggers an interrupt. Reading the RSTC\_SR resets URSTS and clears the interrupt.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | No high-to-low edge on NRST happened since the last read of RSTC_SR.                          |

| 1     | At least one high-to-low transition of NRST has been detected since the last read of RSTC_SR. |

## Reset Controller (RSTC)

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | The detection of a low level on the NRST pin does not generate a user reset. |

| 1     | The detection of a low level on the NRST pin triggers a user reset.          |

### Parallel Input/Output Controller (PIO)

| Offset           | Name      | Bit Pos. |     |     |     |     |     |     |     |     |

|------------------|-----------|----------|-----|-----|-----|-----|-----|-----|-----|-----|

|                  |           | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0x94             | PIO_PPDER | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 0,101            |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0x98             | PIO_PPDSR | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 0x9C<br><br>0x9F | Reserved  |          |     |     |     |     |     |     |     |     |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0.40             |           | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 0xA0             | PIO_OWER  | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xA4 PI          | PIO_OWDR  | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  | PIO_OWDR  | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xA8             | PIO_OWSR  | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 0740             |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| OxAC             |           |          |     |     |     |     |     |     |     |     |

| <br>0xAF         | Reserved  |          |     |     |     |     |     |     |     |     |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xB0             | PIO_AIMER | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xB4             | PIO_AIMDR | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

|                  |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xB8             | PIO_AIMMR | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|                  |           | 23:16    | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

|                  |           | 31:24    | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 0xBC<br><br>0xBF | Reserved  |          |     |     |     |     |     |     |     |     |

| 0                |           | 7:0      | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 0xC0             | PIO_ESR   | 15:8     | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

## DMA Controller (XDMAC)

| Offset   | Name                | Bit Pos. |               |           |       |        |            |        |            |        |  |  |

|----------|---------------------|----------|---------------|-----------|-------|--------|------------|--------|------------|--------|--|--|

|          |                     | 15:8     |               |           |       | NDA[   | 13:6]      |        |            |        |  |  |

|          |                     | 23:16    |               |           |       | NDA[2  | 1:14]      |        |            |        |  |  |

|          |                     | 31:24    |               |           |       | NDA[2  | 9:22]      |        |            |        |  |  |

|          |                     | 7:0      |               |           |       | NDVIE  | W[1:0]     | NDDUP  | NDSUP      | NDE    |  |  |

| 0x04AC   | XDMAC_CNDC17        | 15:8     |               |           |       |        |            |        |            |        |  |  |

|          |                     | 23:16    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               |           |       | UBLEN  | N[7:0]     |        |            |        |  |  |

| 0x04B0   | XDMAC_CUBC17        | 15:8     |               |           |       | UBLEN  | [15:8]     |        |            |        |  |  |

|          |                     | 23:16    |               |           |       | UBLEN  | [23:16]    |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               |           |       | BLEN   | [7:0]      |        |            |        |  |  |

| 0x04B4   | XDMAC_CBC17         | 15:8     |               |           |       |        |            | BLEN   | N[11:8]    |        |  |  |

| 0.00121  |                     | 23:16    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      | MEMSET        | SWREQ     |       | DSYNC  |            | MBSI   | ZE[1:0]    | TYPE   |  |  |

| 0x04B8   | XDMAC_CC17          | 15:8     |               | DIF       | SIF   | DWIDT  | H[1:0]     |        | CSIZE[2:0] |        |  |  |

| 0.00 120 |                     | 23:16    | WRIP          | RDIP      | INITD |        | DAM        | 1[1:0] | SAM        | I[1:0] |  |  |

|          |                     | 31:24    |               |           |       |        | PERID[6:0] |        |            |        |  |  |

|          |                     | 7:0      | SDS_MSP[7:0]  |           |       |        |            |        |            |        |  |  |

| 0x04BC   | XDMAC_CDS_MSP<br>17 | 15:8     | SDS_MSP[15:8] |           |       |        |            |        |            |        |  |  |

| 0,0400   |                     | 23:16    | DDS_MSP[7:0]  |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    | DDS_MSP[15:8] |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               | SUBS[7:0] |       |        |            |        |            |        |  |  |

| 0x04C0   | XDMAC_CSUS17        | 15:8     |               |           |       | SUBS   | [15:8]     |        |            |        |  |  |

|          |                     | 23:16    |               |           |       | SUBS[2 | 23:16]     |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               |           |       | DUBS   |            |        |            |        |  |  |

| 0x04C4   | XDMAC_CDUS17        | 15:8     |               |           |       | DUBS   |            |        |            |        |  |  |

|          |                     | 23:16    |               |           |       | DUBS[2 | 23:16]     |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

| 0x04C8   |                     |          |               |           |       |        |            |        |            |        |  |  |

|          | Reserved            |          |               |           |       |        |            |        |            |        |  |  |

| 0x04CF   |                     |          |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               | ROIE      | WBIE  | RBIE   | FIE        | DIE    | LIE        | BIE    |  |  |

| 0x04D0   | XDMAC_CIE18         | 15:8     |               |           |       |        |            |        |            |        |  |  |

|          |                     | 23:16    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               | ROID      | WBEID | RBEID  | FID        | DID    | LID        | BID    |  |  |

| 0x04D4   | XDMAC_CID18         | 15:8     |               |           |       |        |            |        |            |        |  |  |

|          |                     | 23:16    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 7:0      |               | ROIM      | WBEIM | RBEIM  | FIM        | DIM    | LIM        | BIM    |  |  |

| 0x04D8   | XDMAC_CIM18         | 15:8     |               |           |       |        |            |        |            |        |  |  |

| -        |                     | 23:16    |               |           |       |        |            |        |            |        |  |  |

|          |                     | 31:24    |               |           |       |        |            |        |            |        |  |  |

### Image Sensor Interface (ISI)

### 37.6.3 ISI Preview Size Register

| Name:     | ISI_PSIZE  |

|-----------|------------|

| Offset:   | 0x08       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

| Bit                                     | 31          | 30             | 29             | 28                       | 27                          | 26             | 25                                  | 24                                     |

|-----------------------------------------|-------------|----------------|----------------|--------------------------|-----------------------------|----------------|-------------------------------------|----------------------------------------|

|                                         |             |                |                |                          |                             |                | PREV_H                              | SIZE[9:8]                              |

| Access                                  |             | ·              |                |                          |                             |                | R/W                                 | R/W                                    |

| Reset                                   |             |                |                |                          |                             |                | 0                                   | 0                                      |

|                                         |             |                |                |                          |                             |                |                                     |                                        |

| Bit                                     | 23          | 22             | 21             | 20                       | 19                          | 18             | 17                                  | 16                                     |

|                                         |             |                |                | PREV_H                   | SIZE[7:0]                   |                |                                     |                                        |

| Access                                  | R/W         | R/W            | R/W            | R/W                      | R/W                         | R/W            | R/W                                 | R/W                                    |

| Reset                                   | 0           | 0              | 0              | 0                        | 0                           | 0              | 0                                   | 0                                      |

|                                         |             |                |                |                          |                             |                |                                     |                                        |

| Bit                                     | 15          | 14             | 13             | 12                       | 11                          | 10             | 9                                   | 8                                      |

|                                         |             |                |                |                          |                             |                | PREV_V                              | SIZE[9:8]                              |

| Access                                  |             |                |                |                          |                             |                | R/W                                 | R/W                                    |

| Reset                                   |             |                |                |                          |                             |                | 0                                   | 0                                      |

|                                         |             |                |                |                          |                             |                |                                     |                                        |

| Bit                                     | 7           | 6              | 5              | 4                        | 3                           | 2              | 1                                   | 0                                      |

|                                         |             |                |                | PREV_V                   | SIZE[7:0]                   |                |                                     |                                        |

| Access                                  | R/W         | R/W            | R/W            | R/W                      | R/W                         | R/W            | R/W                                 | R/W                                    |

| Reset                                   | 0           | 0              | 0              | 0                        | 0                           | 0              | 0                                   | 0                                      |

| Bit<br>Access<br>Reset<br>Bit<br>Access | 15<br>7<br> | 14<br>6<br>R/W | 13<br>5<br>R/W | 12<br>4<br>PREV_V<br>R/W | 11<br>3<br>SIZE[7:0]<br>R/W | 10<br>2<br>R/W | 9<br>PREV_V<br>R/W<br>0<br>1<br>R/W | 8<br>SIZE[9:8]<br>R/W<br>0<br>0<br>R/W |

**Bits 25:16 – PREV\_HSIZE[9:0]** Horizontal Size for the Preview Path PREV\_HSIZE = Horizontal Preview size - 1 (640 max only in RGB mode).

**Bits 9:0 – PREV\_VSIZE[9:0]** Vertical Size for the Preview Path PREV\_VSIZE = Vertical Preview size - 1 (480 max only in RGB mode).

## SAM E70/S70/V70/V71 Family GMAC - Ethernet MAC

### 38.8.32 GMAC 1588 Timer Second Comparison Low Register

GMAC\_SCL

0x0E0

Name: Offset:

| Reset:<br>Property: |     | 0x00000000<br>- |     |       |        |     |     |     |

|---------------------|-----|-----------------|-----|-------|--------|-----|-----|-----|

| Bit                 | 31  | 30              | 29  | 28    | 27     | 26  | 25  | 24  |

|                     |     |                 |     | SEC[  | 31:24] |     |     |     |

| Access              | R/W | R/W             | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset               | 0   | 0               | 0   | 0     | 0      | 0   | 0   | 0   |

|                     |     |                 |     |       |        |     |     |     |

| Bit                 | 23  | 22              | 21  | 20    | 19     | 18  | 17  | 16  |

|                     |     |                 |     | SEC[2 | 23:16] |     |     |     |

| Access              | R/W | R/W             | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset               | 0   | 0               | 0   | 0     | 0      | 0   | 0   | 0   |

|                     |     |                 |     |       |        |     |     |     |

| Bit                 | 15  | 14              | 13  | 12    | 11     | 10  | 9   | 8   |

|                     |     |                 |     | SEC   | [15:8] |     |     |     |

| Access              | R/W | R/W             | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset               | 0   | 0               | 0   | 0     | 0      | 0   | 0   | 0   |

|                     |     |                 |     |       |        |     |     |     |

| Bit                 | 7   | 6               | 5   | 4     | 3      | 2   | 1   | 0   |

|                     |     |                 |     | SEC   | [7:0]  |     |     |     |

| Access              | R/W | R/W             | R/W | R/W   | R/W    | R/W | R/W | R/W |

| Reset               | 0   | 0               | 0   | 0     | 0      | 0   | 0   | 0   |

|                     |     |                 |     |       |        |     |     |     |

**Bits 31:0 – SEC[31:0]** 1588 Timer Second Comparison Value Value is compared to seconds value bits [31:0] of the TSU timer count value.

### 38.8.42 GMAC Multicast Frames Transmitted Register

GMAC\_MFT

0x110

Name:

Offset:

|        | Reset:<br>Property: | 0x00000000<br>- |    |      |         |    |    |    |

|--------|---------------------|-----------------|----|------|---------|----|----|----|

| Bit    | 31                  | 30              | 29 | 28   | 27      | 26 | 25 | 24 |

|        |                     |                 |    | MFTX | [31:24] |    |    |    |

| Access | R                   | R               | R  | R    | R       | R  | R  | R  |

| Reset  | 0                   | 0               | 0  | 0    | 0       | 0  | 0  | 0  |

| Bit    | 23                  | 22              | 21 | 20   | 19      | 18 | 17 | 16 |

|        |                     |                 |    | MFTX | [23:16] |    |    |    |

| Access | R                   | R               | R  | R    | R       | R  | R  | R  |

| Reset  | 0                   | 0               | 0  | 0    | 0       | 0  | 0  | 0  |

| Bit    | 15                  | 14              | 13 | 12   | 11      | 10 | 9  | 8  |

|        |                     |                 |    | MFTX | [15:8]  |    |    |    |

| Access | R                   | R               | R  | R    | R       | R  | R  | R  |

| Reset  | 0                   | 0               | 0  | 0    | 0       | 0  | 0  | 0  |

| Bit    | 7                   | 6               | 5  | 4    | 3       | 2  | 1  | 0  |

|        |                     |                 |    | MFT  | X[7:0]  |    |    |    |

| Access | R                   | R               | R  | R    | R       | R  | R  | R  |

| Reset  | 0                   | 0               | 0  | 0    | 0       | 0  | 0  | 0  |

Bits 31:0 – MFTX[31:0] Multicast Frames Transmitted without Error

This register counts the number of multicast frames successfully transmitted without error, i.e., no underrun and not too many retries. Excludes pause frames.

### USB High-Speed Interface (USBHS)

| Value | Description                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Frees the endpoint memory.                                                                                                                      |

| 1     | Allocates the endpoint memory. The user should check the USBHS_DEVEPTISRx.CFGOK bit to know whether the allocation of this endpoint is correct. |

### USB High-Speed Interface (USBHS)

### Bit 16 - RWALL Read/Write Allowed

This bit is set for IN endpoints when the current bank is not full, i.e., the user can write further data into the FIFO.

This bit is set for OUT endpoints when the current bank is not empty, i.e., the user can read further data from the FIFO.

This bit is never set in case of error.

This bit is cleared otherwise.

### Bits 15:14 - CURRBK[1:0] Current Bank

This field is used to indicate the current bank. It may be updated one clock cycle after the RWALL bit changes, so the user should not poll this field as an interrupt bit.

| Value | Name     | Description           |

|-------|----------|-----------------------|

| 0     | BANK0    | Current bank is bank0 |

| 1     | BANK1    | Current bank is bank1 |

| 2     | BANK2    | Current bank is bank2 |

| 3     | Reserved |                       |

### Bits 13:12 – NBUSYBK[1:0] Number of Busy Banks

This field is set to indicate the number of busy banks:

For IN endpoints, it indicates the number of banks filled by the user and ready for IN transfer. When all banks are free, this triggers a PEP\_x interrupt if NBUSYBKE = 1.

For OUT endpoints, it indicates the number of banks filled by OUT transactions from the host. When all banks are busy, this triggers a PEP\_x interrupt if NBUSYBKE = 1.

When the USBHS\_DEVEPTIMRx.FIFOCON bit is cleared (by writing a one to the USBHS\_DEVEPTIMRx.FIFOCONC bit) to validate a new bank, this field is updated two or three clock cycles later to calculate the address of the next bank.

A PEP\_x interrupt is triggered if:

| Value | Name   | Description                                                                                                                                                                         |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0_BUSY | 0 busy bank (all banks free)                                                                                                                                                        |

| 1     | 1_BUSY | 1 busy bank                                                                                                                                                                         |

| 2     | 2_BUSY | 2 busy banks                                                                                                                                                                        |

| 3     | 3_BUSY | 3 busy banks<br>• For IN endpoint, USBHS_DEVEPTIMRx.NBUSYBKE = 1 and all the banks are<br>free.<br>• For OUT endpoint, USBHS_DEVEPTIMRx.NBUSYBKE = 1 and all the banks are<br>busy. |

**Bit 10 – ERRORTRANS** High-bandwidth Isochronous OUT Endpoint Transaction Error Interrupt This bit is set when a transaction error occurs during the current microframe (the data toggle sequencing is not compliant with the USB 2.0 standard). This triggers a PEP\_x interrupt if USBHS\_DEVEPTIMRx.ERRORTRANSE = 1.

This bit is set as long as the current bank (CURRBK) belongs to the bad n-transactions (n = 1, 2 or 3) transferred during the microframe. It is cleared by software by clearing (at least once) the

© 2018 Microchip Technology Inc.

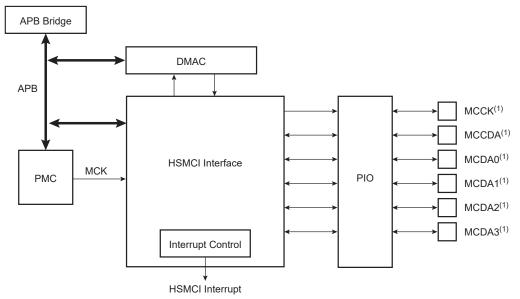

### 40.3 Block Diagram

Figure 40-1. Block Diagram (4-bit configuration)

### Note:

1. When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA, MCDAy to HSMCIx\_DAy.

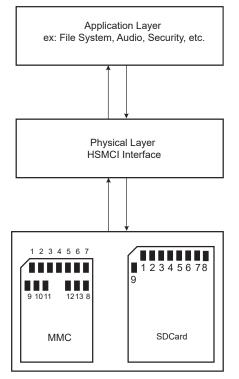

### 40.4 Application Block Diagram

Figure 40-2. Application Block Diagram

Universal Synchronous Asynchronous Receiver Transc...

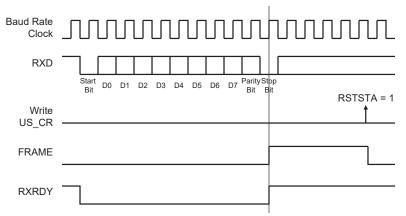

### Figure 46-24. Framing Error Status

#### 46.6.3.13 Transmit Break

The user can request the transmitter to generate a break condition on the TXD line. A break condition drives the TXD line low during at least one complete character. It appears the same as a 0x00 character sent with the parity and the stop bits at 0. However, the transmitter holds the TXD line at least during one character until the user requests the break condition to be removed.

A break is transmitted by writing a '1' to US\_CR.STTBRK. This can be performed at any time, either while the transmitter is empty (no character in either the Shift register or in US\_THR) or when a character is being transmitted. If a break is requested while a character is being shifted out, the character is first completed before the TXD line is held low.

Once STTBRK command is requested, further STTBRK commands are ignored until the end of the break is completed.

The break condition is removed by writing a '1' to US\_CR.STPBRK. If the STPBRK is requested before the end of the minimum break duration (one character, including start, data, parity and stop bits), the transmitter ensures that the break condition completes.

The transmitter considers the break as though it is a character, i.e., the STTBRK and STPBRK commands are processed only if US\_CSR. TXRDY = 1 and the start of the break condition clears the TXRDY and TXEMPTY bits as if a character is processed.

Writing US\_CR with both STTBRK and STPBRK bits to '1' can lead to an unpredictable result. All STPBRK commands requested without a previous STTBRK command are ignored. A byte written into US\_THR while a break is pending, but not started, is ignored.

After the break condition, the transmitter returns the TXD line to 1 for a minimum of 12 bit times. Thus, the transmitter ensures that the remote receiver detects correctly the end of break and the start of the next character. If the timeguard is programmed with a value higher than 12, the TXD line is held high for the timeguard period.

After holding the TXD line for this period, the transmitter resumes normal operations.

The following figure illustrates the effect of both the Start Break (STTBRK) and Stop Break (STPBRK) commands on the TXD line.

### NACT(slave1)=PUBLISH

NACT(slave2)=SUBSCRIBE

• Data transfer from the slave2 to the master and to the slave1:

NACT(master)=SUBSCRIBE

NACT(slave1)=SUBSCRIBE

NACT(slave2)=PUBLISH

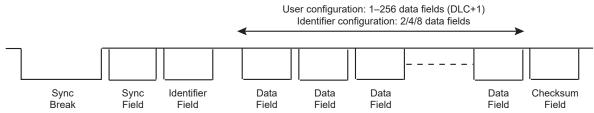

### 46.6.9.11 Response Data Length

The LIN response data length is the number of data fields (bytes) of the response excluding the checksum.

The response data length can either be configured by the user or be defined automatically by bits 4 and 5 of the Identifier (compatibility to LIN Specification 1.1). The user can choose between these two modes using the US\_LINMR.DLM:

- DLM = 0: The response data length is configured by the user via US\_LINMR.DLC. The response data length is equal to (DLC + 1) bytes. DLC can be programmed from 0 to 255, so the response can contain from 1 data byte up to 256 data bytes.

- DLM = 1: The response data length is defined by the Identifier (US\_LINIR.IDCHR) according to the table below. The US\_LINMR.DLC is discarded. The response can contain 2 or 4 or 8 data bytes.

| Table 46-13. | Response | Data I | Length | if DLM = 1 |

|--------------|----------|--------|--------|------------|

|--------------|----------|--------|--------|------------|

| IDCHR[5] | IDCHR[4] | Response Data Length [Bytes] |

|----------|----------|------------------------------|

| 0        | 0        | 2                            |

| 0        | 1        | 2                            |

| 1        | 0        | 4                            |

| 1        | 1        | 8                            |

### 46.6.9.12 Checksum

The last field of a frame is the checksum. The checksum contains the inverted 8-bit sum with carry, over all data bytes or all data bytes and the protected identifier. Checksum calculation over the data bytes only is called classic checksum and it is used for communication with LIN 1.3 slaves. Checksum calculation over the data bytes and the protected identifier byte is called enhanced checksum and it is used for communication with LIN 2.0 slaves.

The USART can be configured to:

- Send/Check an Enhanced checksum automatically (CHKDIS = 0 & CHKTYP = 0)

- Send/Check a Classic checksum automatically (CHKDIS = 0 & CHKTYP = 1)

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.37 USART LON Data Length Register

| Name:     | US_LONDL   |

|-----------|------------|

| Offset:   | 0x0068     |

| Reset:    | 0x0        |

| Property: | Read/Write |

This register is relevant only if USART\_MODE = 0x9 in the USART Mode Register.

| Bit    | 31       | 30 | 29 | 28   | 27      | 26 | 25 | 24 |

|--------|----------|----|----|------|---------|----|----|----|

|        |          |    |    |      |         |    |    |    |

| Access | <b>L</b> | •  | •  |      |         | •  | •  |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 23       | 22 | 21 | 20   | 19      | 18 | 17 | 16 |

|        |          |    |    |      |         |    |    |    |

| Access |          | 1  |    |      |         |    |    |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 15       | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|        |          |    |    |      |         |    |    |    |

| Access |          |    |    |      |         |    |    |    |

| Reset  |          |    |    |      |         |    |    |    |

|        |          |    |    |      |         |    |    |    |

| Bit    | 7        | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        |          |    |    | LOND | DL[7:0] |    |    |    |

| Access |          |    |    |      |         |    |    |    |

| Reset  | 0        | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |          |    |    |      |         |    |    |    |

### Bits 7:0 - LONDL[7:0] LON Data Length

| Value | Description                       |

|-------|-----------------------------------|

| 0-255 | LON data length is LONDL+1 bytes. |

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.38 USART LON L2HDR Register

| Name:     | US_LONL2HDR |

|-----------|-------------|

| Offset:   | 0x006C      |

| Reset:    | 0x0         |

| Property: | Read/Write  |

This register is relevant only if USART\_MODE = 0x9 in the USART Mode Register.

| Bit    | 31 | 30   | 29 | 28 | 27  | 26    | 25 | 24 |

|--------|----|------|----|----|-----|-------|----|----|

|        |    |      |    |    |     |       |    |    |

| Access |    |      |    |    |     |       |    |    |

| Reset  |    |      |    |    |     |       |    |    |

|        |    |      |    |    |     |       |    |    |

| Bit    | 23 | 22   | 21 | 20 | 19  | 18    | 17 | 16 |

|        |    |      |    |    |     |       |    |    |

| Access |    |      |    |    |     |       |    |    |

| Reset  |    |      |    |    |     |       |    |    |

|        |    |      |    |    |     |       |    |    |

| Bit    | 15 | 14   | 13 | 12 | 11  | 10    | 9  | 8  |

|        |    |      |    |    |     |       |    |    |

| Access |    |      |    |    |     |       |    |    |

| Reset  |    |      |    |    |     |       |    |    |

|        |    |      |    |    |     |       |    |    |

| Bit    |    | 6    | 5  | 4  | 3   | 2     | 1  | 0  |

|        | PB | ALTP |    |    | BLI | [5:0] |    |    |

| Access |    |      |    |    |     |       |    |    |

| Reset  | 0  | 0    | 0  | 0  | 0   | 0     | 0  | 0  |

Bit 7 – PB LON Priority Bit

| Value | Description             |

|-------|-------------------------|

| 0     | LON priority bit reset. |

| 1     | LON priority bit set.   |

### Bit 6 – ALTP LON Alternate Path Bit

| Value | Description                   |

|-------|-------------------------------|

| 0     | LON alternate path bit reset. |

| 1     | LON alternate path bit set.   |

### Bits 5:0 - BLI[5:0] LON Backlog Increment

|   | Value | Description                                                                    |

|---|-------|--------------------------------------------------------------------------------|

| ( | 0-63  | LON backlog increment to be generated as a result of delivering the LON frame. |

### Controller Area Network (MCAN)

### 49.6.17 MCAN Interrupt Enable Register

| Name:     | MCAN_IE    |

|-----------|------------|

| Offset:   | 0x54       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

The following configuration values are valid for all listed bit names of this register:

- 0: Disables the corresponding interrupt.

- 1: Enables the corresponding interrupt.

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | ARAE  | PEDE  | PEAE  | WDIE  | BOE   | EWE   |

| Access |       |       | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset  |       |       | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|        | EPE   | ELOE  |       |       | DRXE  | TOOE  | MRAFE | TSWE  |

| Access | R/W   | R/W   |       |       | R/W   | R/W   | R/W   | R/W   |

| Reset  | 0     | 0     |       |       | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

|        | TEFLE | TEFFE | TEFWE | TEFNE | TFEE  | TCFE  | TCE   | HPME  |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        | RF1LE | RF1FE | RF1WE | RF1NE | RF0LE | RF0FE | RF0WE | RF0NE |

| Access | R/W   |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Bit 29 – ARAE Access to Reserved Address Enable

- Bit 28 PEDE Protocol Error in Data Phase Enable

- **Bit 27 PEAE** Protocol Error in Arbitration Phase Enable

- Bit 26 WDIE Watchdog Interrupt Enable

- Bit 25 BOE Bus\_Off Status Interrupt Enable

- Bit 24 EWE Warning Status Interrupt Enable

- Bit 23 EPE Error Passive Interrupt Enable

- Bit 22 ELOE Error Logging Overflow Interrupt Enable

- Bit 19 DRXE Message stored to Dedicated Receive Buffer Interrupt Enable

### Integrity Check Monitor (ICM)

| Value | Name | Description                                                                   |

|-------|------|-------------------------------------------------------------------------------|

| 0     |      | The ICM_ISR.REC[i] flag is set when the descriptor with the EOM bit set is    |

|       |      | processed.                                                                    |

| 1     |      | The ICM_ISR.REC[i] flag remains cleared even if the setting condition is met. |

Bit 7 – WCIEN Wrap Condition Interrupt Disable (Default Enabled)

| Value | Name | Description                                                                         |

|-------|------|-------------------------------------------------------------------------------------|

| 0     |      | The ICM_ISR.RWC[i] flag is set when the WRAP bit is set in a descriptor of the main |

|       |      | list.                                                                               |

| 1     |      | ICM_ISR.RWC[i] flag remains cleared even if the setting condition is met.           |

### Bit 6 – BEIEN Bus Error Interrupt Disable (Default Enabled)

| Value | Name | Description                                                                    |

|-------|------|--------------------------------------------------------------------------------|

| 0     |      | The flag is set when an error is reported on the system bus by the bus matrix. |

| 1     |      | The flag remains cleared even if the setting condition is met.                 |

### Bit 5 – DMIEN Digest Mismatch Interrupt Disable (Default Enabled)

| Value | Name | Description                                                                   |

|-------|------|-------------------------------------------------------------------------------|

| 0     |      | The ICM_ISR.RBE[i] flag is set when the hash value just calculated from the   |

|       |      | processed region differs from expected hash value.                            |

| 1     |      | The ICM_ISR.RBE[i] flag remains cleared even if the setting condition is met. |

### **Bit 4 – RHIEN** Region Hash Completed Interrupt Disable (Default Enabled)

| Value | Name | Description                                                                        |

|-------|------|------------------------------------------------------------------------------------|

| 0     |      | The ICM_ISR.RHC[i] flag is set when the field NEXT = 0 in a descriptor of the main |

|       |      | or second list.                                                                    |

| 1     |      | The ICM_ISR.RHC[i] flag remains cleared even if the setting condition is met.      |

### Bit 2 – EOM End Of Monitoring

| Value | Name | Description                                                                |

|-------|------|----------------------------------------------------------------------------|

| 0     |      | The current descriptor does not terminate the monitoring.                  |

| 1     |      | The current descriptor terminates the Main List. WRAP value has no effect. |

### Bit 1 – WRAP Wrap Command

| Value | Name | Description                                                                           |

|-------|------|---------------------------------------------------------------------------------------|

| 0     |      | The next region descriptor address loaded is the current region identifier descriptor |

|       |      | address incremented by 0x10.                                                          |

| 1     |      | The next region descriptor address loaded is ICM_DSCR.                                |

### Bit 0 – CDWBN Compare Digest or Write Back Digest

| Value | Name | Description                                                         |

|-------|------|---------------------------------------------------------------------|

| 0     |      | The digest is written to the Hash area.                             |

| 1     |      | The digest value is compared to the digest stored in the Hash area. |

### 56.6.1 TRNG Control Register

| Name:     | TRNG_CR    |

|-----------|------------|

| Offset:   | 0x00       |

| Reset:    | _          |

| Property: | Write-only |

| Bit    | 31           | 30 | 29 | 28   | 27      | 26 | 25 | 24     |  |  |

|--------|--------------|----|----|------|---------|----|----|--------|--|--|

|        | WAKEY[23:16] |    |    |      |         |    |    |        |  |  |

| Access | W            | W  | W  | W    | W       | W  | W  | W      |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0      |  |  |

|        |              |    |    |      |         |    |    |        |  |  |

| Bit    | 23           | 22 | 21 | 20   | 19      | 18 | 17 | 16     |  |  |

|        | WAKEY[15:8]  |    |    |      |         |    |    |        |  |  |

| Access | W            | W  | W  | W    | W       | W  | W  | W      |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | 0      |  |  |

|        |              |    |    |      |         |    |    |        |  |  |

| Bit    | 15           | 14 | 13 | 12   | 11      | 10 | 9  | 8      |  |  |

|        |              |    |    | WAKI | EY[7:0] |    |    |        |  |  |

| Access | W            | W  | W  | W    | W       | W  | W  | W      |  |  |

| Reset  | 0            | 0  | 0  | 0    | 0       | 0  | 0  | _      |  |  |

|        |              |    |    |      |         |    |    |        |  |  |

| Bit    | 7            | 6  | 5  | 4    | 3       | 2  | 1  | 0      |  |  |

|        |              |    |    |      |         |    |    | ENABLE |  |  |

| Access |              |    |    |      |         |    |    | W      |  |  |

| Reset  |              |    |    |      |         |    |    | -      |  |  |

### Bits 31:8 - WAKEY[23:0] Register Write Access Key

| Value   | Name   | Description                                                       |

|---------|--------|-------------------------------------------------------------------|

| 0x524E4 | PASSWD | Writing any other value in this field aborts the write operation. |

| 7       |        |                                                                   |

### Bit 0 - ENABLE Enables the TRNG to Provide Random Values

| Value | Description                                                                             |  |  |  |

|-------|-----------------------------------------------------------------------------------------|--|--|--|

| 0     | Disables the TRNG.                                                                      |  |  |  |

| 1     | Enables the TRNG if 0x524E47 ("RNG" in ASCII) is written in KEY field at the same time. |  |  |  |

### Electrical Characteristics for SAM ...

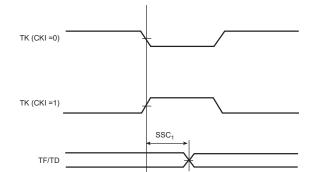

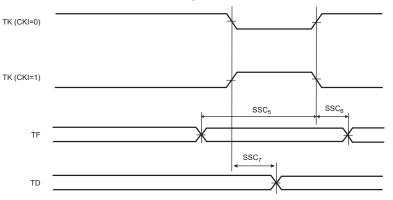

### Figure 58-34. SSC Transmitter, TK in Input and TF in Output

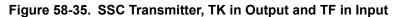

#### Figure 58-36. SSC Transmitter, TK and TF in Input

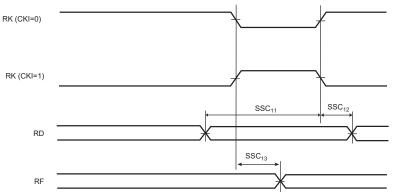

### Figure 58-37. SSC Receiver RK and RF in Input

© 2018 Microchip Technology Inc.

### **Electrical Characteristics for SAM E70/S70**

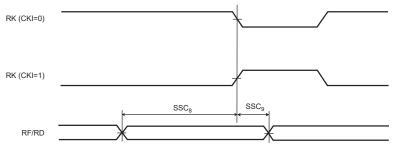

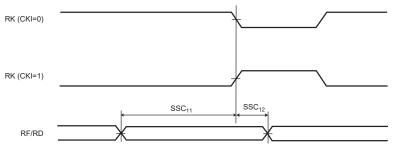

### Figure 59-38. SSC Receiver, RK in Input and RF in Output

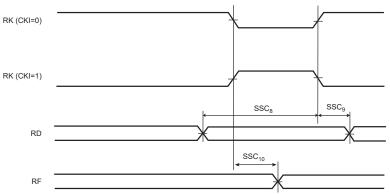

### Figure 59-40. SSC Receiver, RK in Output and RF in Input

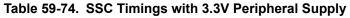

| Symbol           | Parameter                                | Condition | Min                 | Мах                 | Unit |  |  |  |  |

|------------------|------------------------------------------|-----------|---------------------|---------------------|------|--|--|--|--|

| Transmit         | Insmitter                                |           |                     |                     |      |  |  |  |  |

| SSC <sub>0</sub> | TK edge to TF/TD (TK output, TF output)  | -         | -3.9 <sup>(1)</sup> | 4.0 (1)             | ns   |  |  |  |  |

| SSC <sub>1</sub> | TK edge to TF/TD (TK input, TF output)   | -         | 3.1 <sup>(1)</sup>  | 12.7 <sup>(1)</sup> | ns   |  |  |  |  |

| SSC <sub>2</sub> | TF setup time before TK edge (TK output) | -         | 13.6                | -                   | ns   |  |  |  |  |

| SSC <sub>3</sub> | TF hold time after TK edge (TK output)   | _         | 0                   | _                   | ns   |  |  |  |  |

© 2018 Microchip Technology Inc.