#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 300MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 75                                                                         |

| Program Memory Size        | 2MB (2M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 384K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                               |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TFBGA                                                                  |

| Supplier Device Package    | 100-TFBGA (9x9)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70n21b-cnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 37.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 590                                                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 3     | 37.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 591                                                                                                                  |

| 3     | 37.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 3     | 37.4.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 3     | 37.5.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| 38. ( | GMA                                                                                                                                                                   | AC - Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 640                                                                                                                  |

| 3     | 38.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 640                                                                                                                  |

| 3     | 38.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 640                                                                                                                  |

| 3     | 38.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 641                                                                                                                  |

| 3     | 38.4.                                                                                                                                                                 | Signal Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 641                                                                                                                  |

| 3     | 38.5.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 642                                                                                                                  |

| 3     | 38.6.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 642                                                                                                                  |

| 3     | 38.7.                                                                                                                                                                 | Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 673                                                                                                                  |

| 3     | 38.8.                                                                                                                                                                 | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 678                                                                                                                  |

| 30 I  | ISB                                                                                                                                                                   | High-Speed Interface (USBHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 831                                                                                                                  |

|       |                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

|       |                                                                                                                                                                       | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

|       |                                                                                                                                                                       | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

|       |                                                                                                                                                                       | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

|       |                                                                                                                                                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| 40. ł | High                                                                                                                                                                  | -Speed Multimedia Card Interface (HSMCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                                                                                                                 |

| 40. H | <b>-ligh</b><br>10.1.                                                                                                                                                 | n-Speed Multimedia Card Interface (HSMCI)<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                                                                                                                 |

| 40. H | High<br>10.1.<br>10.2.                                                                                                                                                | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>1042<br>1042                                                                                                 |

| 40. H | <b>-ligh</b><br>10.1.<br>10.2.<br>10.3.                                                                                                                               | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>1042<br>1042<br>1043                                                                                         |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.                                                                                                                              | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.                                                                                                                     | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.                                                                                                            | Description<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.                                                                                                   | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1042<br>                                                                                                             |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.<br>10.8.                                                                                          | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.7.<br>40.8.                                                                                          | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation                                                                                                                                                                                                                                                                                                                                                                                                          | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.                                                                        | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.5.<br>40.5.<br>40.7.<br>40.10<br>40.11                                                               | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation<br>HSMCI Boot Operation Mode                                                                                                                                                                                                                                                                                                            | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11.                                                              | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13                                                     | Description<br>Embedded Characteristics.<br>Block Diagram.<br>Application Block Diagram.<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation.<br>O. CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>Register Write Protection.                                                                                                                                                                                                                                                                                                               | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14                                             | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       | 1042<br>                                                                                                             |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.3.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br>5eria                           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>CE-ATA Operation Mode</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection</li> <li>Register Summary</li> </ul>                                                                                      |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.13<br>40.14<br><b>Seria</b><br>41.1.                    | <ul> <li>Speed Multimedia Card Interface (HSMCI).</li> <li>Description.</li> <li>Embedded Characteristics.</li> <li>Block Diagram.</li> <li>Application Block Diagram.</li> <li>Pin Name List.</li> <li>Product Dependencies.</li> <li>Bus Topology.</li> <li>High-Speed Multimedia Card Operations.</li> <li>SD/SDIO Card Operation.</li> <li>CE-ATA Operation.</li> <li>HSMCI Boot Operation Mode.</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection.</li> <li>Register Summary.</li> <li>al Peripheral Interface (SPI).</li> </ul>                                                               |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> </ul>                                                          | 1042<br>1042<br>1043<br>1043<br>1043<br>1044<br>1044<br>1044<br>1044<br>1055<br>1055<br>1059<br>1095<br>1095<br>1095 |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.<br>41.2.<br>41.3. | A-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics.<br>Block Diagram<br>Application Block Diagram<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation<br>O. CE-ATA Operation.<br>CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>HSMCI Boot Operation Mode<br>Register Write Protection<br>Register Summary.<br>al Peripheral Interface (SPI)<br>Description<br>Embedded Characteristics.                                                                                                                  |                                                                                                                      |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br>41.1.<br>41.2.<br>41.3.<br>41.3.                 | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> </ul> |                                                                                                                      |

# SAM E70/S70/V70/V71 Family Bus Matrix (MATRIX)

# Name Description 16BEAT\_BURST 16-beat Burst—The undefined length burst or bursts sequence is split into 16-beat bursts or less, allowing re-arbitration every 16 beats. 32BEAT\_BURST 32-beat Burst—The undefined length burst or bursts sequence is split into 32-beat bursts or less, allowing re-arbitration every 32 beats. 64BEAT\_BURST 64-beat Burst—The undefined length burst or bursts sequence is split into 64-beat bursts or less, allowing re-arbitration every 64 beats. 128BEAT\_BURST 128-beat Burst—The undefined length burst or bursts sequence is split into 64-beat bursts or less, allowing re-arbitration every 64 beats. 128BEAT\_BURST 128-beat Burst—The undefined length burst or bursts sequence is split into 128-beat bursts or less, allowing re-arbitration every 128 beats.

| Note: Unless duly needed, the ULBT should be left at its default 0 value |

|--------------------------------------------------------------------------|

| for power saving.                                                        |

Value

4

5

6

7

# Reinforced Safety Watchdog Timer (RSWDT)

#### 25.5.2 Reinforced Safety Watchdog Timer Mode Register

| Name:     | RSWDT_MR        |

|-----------|-----------------|

| Offset:   | 0x04            |

| Reset:    | 0x3FFFAFFF      |

| Property: | Read/Write Once |

Note: The first write access prevents any further modification of the value of this register; read accesses remain possible.

Note: The WDV value must not be modified within three slow clock periods following a restart of the watchdog performed by means of a write access in the RSWDT\_CR, else the watchdog may trigger an end of period earlier than expected.

| Bit    | 31    | 30 | 29        | 28       | 27      | 26  | 25     | 24 |

|--------|-------|----|-----------|----------|---------|-----|--------|----|

|        |       |    | WDIDLEHLT | WDDBGHLT |         |     |        |    |

| Access |       |    |           |          |         |     |        |    |

| Reset  |       |    | 1         | 1        | 1       | 1   | 1      | 1  |

|        |       |    |           |          |         |     |        |    |

| Bit    | 23    | 22 | 21        | 20       | 19      | 18  | 17     | 16 |

|        |       |    |           | ALLON    | ES[7:0] |     |        |    |

| Access |       |    |           |          |         |     |        |    |

| Reset  | 1     | 1  | 1         | 1        | 1       | 1   | 1      | 1  |

|        |       |    |           |          |         |     |        |    |

| Bit    | 15    | 14 | 13        | 12       | 11      | 10  | 9      | 8  |

|        | WDDIS |    | WDRSTEN   | WDFIEN   |         | WDV | [11:8] |    |

| Access |       |    |           |          |         |     |        |    |

| Reset  | 1     |    | 1         | 0        | 1       | 1   | 1      | 1  |

|        |       |    |           |          |         |     |        |    |

| Bit    | 7     | 6  | 5         | 4        | 3       | 2   | 1      | 0  |

|        |       |    |           | WDV      | [7:0]   |     |        |    |

| Access |       |    |           |          |         |     |        |    |

| Reset  | 1     | 1  | 1         | 1        | 1       | 1   | 1      | 1  |

#### Bit 29 - WDIDLEHLT Watchdog Idle Halt

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | The RSWDT runs when the system is in idle mode.   |

| 1     | The RSWDT stops when the system is in idle state. |

#### Bit 28 - WDDBGHLT Watchdog Debug Halt

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The RSWDT runs when the processor is in debug state.  |

| 1     | The RSWDT stops when the processor is in debug state. |

#### Bits 27:16 - ALLONES[11:0] Must Always Be Written with 0xFFF

Bit 15 – WDDIS Watchdog Disable

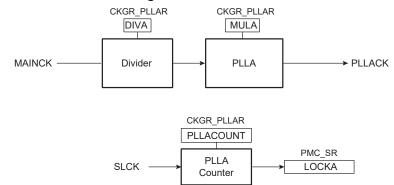

### Figure 30-4. Divider and PLLA Block Diagram

## 30.6.1 Divider and Phase Lock Loop Programming

The divider can be set between 1 and 255 in steps of 1. When a divider field (DIV) is cleared, the output of the corresponding divider and the PLL output is a continuous signal at level 0. On reset, each DIV field is cleared, thus the corresponding PLL input clock is stuck at '0'.

The PLL (PLLA) allows multiplication of the divider's outputs. The PLL clock signal has a frequency that depends on the respective source signal frequency and on the parameters DIV (DIVA) and MUL (MULA). The factor applied to the source signal frequency is (MUL + 1)/DIV. When MUL is written to '0' or DIV = 0, the PLL is disabled and its power consumption is saved. Note that there is a delay of two SLCK clock cycles between the disable command and the real disable of the PLL. Re-enabling the PLL can be performed by writing a value higher than '0' in the MUL field and DIV higher than '0'.

Whenever the PLL is re-enabled or one of its parameters is changed, the LOCK (LOCKA) bit in PMC\_SR is automatically cleared. The values written in the PLLCOUNT field (PLLACOUNT) in CKGR\_PLLR (CKGR\_PLLAR) are loaded in the PLL counter. The PLL counter then decrements at the speed of SLCK until it reaches '0'. At this time, PMC\_SR.LOCK is set and can trigger an interrupt to the processor. The user has to load the number of SLCK cycles required to cover the PLL transient time into the PLLCOUNT field.

To avoid programming the PLL with a multiplication factor that is too high, the user can saturate the multiplication factor value sent to the PLL by setting the PLLA\_MMAX field in the PLL Maximum Multiplier Value Register (PMC\_PMMR).

It is forbidden to change the MAINCK characteristics (oscillator selection, frequency adjustment of the Main RC oscillator) when:

- MAINCK is selected as the PLLA clock source, and

- MCK is sourced from PLLA.

To change the MAINCK characteristics, the user must:

- 1. Switch the MCK source to MAINCK by writing a '1' to PMC\_MCKR.CSS.

- 2. Change the Main RC oscillator frequency (MOSCRCF) or oscillator selection (MOSCSEL) in CKGR\_MOR.

- Wait for MOSCRCS (if frequency changes) or MOSCSELS (if oscillator selection changes) in PMC\_SR.

- 4. Disable and then enable the PLL.

- 5. Wait for the LOCK flag in PMC\_SR.

- 6. Switch back MCK to the PLLA by writing the appropriate value to PMC\_MCKR.CSS.

| Name:XDMAC_GOffset:0x0CReset:-Property:Write-only |      | -    |      |      |      |      |      |      |

|---------------------------------------------------|------|------|------|------|------|------|------|------|

| Bit                                               | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   |

|                                                   |      |      |      |      |      |      |      |      |

| Access                                            |      |      |      |      |      |      |      |      |

| Reset                                             |      |      |      |      |      |      |      |      |

| Bit                                               | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|                                                   | IE23 | IE22 | IE21 | IE20 | IE19 | IE18 | IE17 | IE16 |

| Access                                            | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset                                             | _    | -    | -    | -    | -    | -    | -    | -    |

| Bit                                               | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|                                                   | IE15 | IE14 | IE13 | IE12 | IE11 | IE10 | IE9  | IE8  |

| Access                                            | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset                                             | -    | -    | _    | _    | -    | _    | _    | -    |

| Bit                                               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|                                                   | IE7  | IE6  | IE5  | IE4  | IE3  | IE2  | IE1  | IE0  |

| Access                                            | W    | W    | W    | W    | W    | W    | W    | W    |

| Reset                                             |      | _    | _    | -    | -    | -    | -    | _    |

### 36.9.4 XDMAC Global Interrupt Enable Register

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23 – IE XDMAC Channel x Interrupt Enable

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | This bit has no effect. The Channel x Interrupt Mask bit (XDMAC_GIM.IMx) is not modified. |

| 1     | The corresponding mask bit is set. The XDMAC Channel x Interrupt Status register          |

|       | (XDMAC_GIS) can generate an interrupt.                                                    |

Image Sensor Interface (ISI)

| Mode      | Byte   | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

|-----------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| RGB 8:8:8 | Byte 0 | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   | R5(i)   | R6(i)   | R7(i)   |

|           | Byte 1 | G0(i)   | G1(i)   | G2(i)   | G3(i)   | G4(i)   | G5(i)   | G6(i)   | G7(i)   |

|           | Byte 2 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | B5(i)   | B6(i)   | B7(i)   |

|           | Byte 3 | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) | R5(i+1) | R6(i+1) | R7(i+1) |

| RGB 5:6:5 | Byte 0 | G3(i)   | G4(i)   | G5(i)   | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   |

|           | Byte 1 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | G0(i)   | G1(i)   | G2(i)   |

|           | Byte 2 | G3(i+1) | G4(i+1) | G5(i+1) | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) |

|           | Byte 3 | B0(i+1) | B1(i+1) | B2(i+1) | B3(i+1) | B4(i+1) | G0(i+1) | G1(i+1) | G2(i+1) |

## Table 37-5. RGB Format in Default Mode, RGB\_CFG = 00, Swap Activated

The RGB 5:6:5 input format is processed to be displayed as RGB 5:6:5 format, compliant with the 16-bit mode of the LCD controller.

#### 37.5.3 Clocks

The sensor master clock (ISI\_MCK) can be generated either by the Advanced Power Management Controller (APMC) through a Programmable Clock output or by an external oscillator connected to the sensor.

None of the sensors embed a power management controller, so providing the clock by the APMC is a simple and efficient way to control power consumption of the system.

Care must be taken when programming the system clock. The ISI has two clock domains, the sensor master clock and the pixel clock provided by sensor. The two clock domains are not synchronized, but the sensor master clock must be faster than the pixel clock.

#### 37.5.4 Preview Path

#### 37.5.4.1 Scaling, Decimation (Subsampling)

This module resizes captured 8-bit color sensor images to fit the LCD display format. The resize module performs only downscaling. The same ratio is applied for both horizontal and vertical resize, then a fractional decimation algorithm is applied.

The decimation factor is a multiple of 1/16; values 0 to 15 are forbidden.

#### Table 37-6. Decimation Factor

| Decimation Value  | 0–15 | 16 | 17    | 18    | 19    | <br>124   | 125   | 126   | 127   |

|-------------------|------|----|-------|-------|-------|-----------|-------|-------|-------|

| Decimation Factor | —    | 1  | 1.063 | 1.125 | 1.188 | <br>7.750 | 7.813 | 7.875 | 7.938 |

| OUTPUT           | INPUT | 352 × 288 | 640 × 480 | 800 × 600 | 1280 × 1024 | 1600 × 1200 | 2048 × 1536 |

|------------------|-------|-----------|-----------|-----------|-------------|-------------|-------------|

| VGA<br>640 × 480 | F     |           | 16        | 20        | 32          | 40          | 51          |

| QVGA             | F     | 16        | 32        | 40        | 64          | 80          | 102         |

The bank is really killed: USBHS DEVEPTISRx.NBUSYBK is decremented.

The bank is not cleared but sent (IN transfer): USBHS\_DEVEPTISRx.NBUSYBK is decremented.

The bank is not cleared because it was empty.

The user should wait for this bit to be cleared before trying to kill another packet.

This kill request is refused if at the same time an IN token is coming and the last bank is the current one being sent on the USB line. If at least two banks are ready to be sent, there is no problem to kill a packet even if an IN token is coming. Indeed, in this case, the current bank is sent (IN transfer) while the last bank is killed.

### Bit 12 – NBUSYBKE Number of Busy Banks Interrupt

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_DEVEPTIDRx.NBUSYBKEC = 0. This disables the Number of Busy |

|       | Banks interrupt (USBHS_DEVEPTISRx.NBUSYBK).                                   |

| 1     | Set when the USBHS_DEVEPTIERx.NBUSYBKES = 1. This enables the Number of Busy  |

|       | Banks interrupt (USBHS_DEVEPTISRx.NBUSYBK).                                   |

### Bit 7 – SHORTPACKETE Short Packet Interrupt

If this bit is set for non-control IN endpoints, a short packet transmission is guaranteed upon ending a DMA transfer, thus signaling an end of isochronous frame or a bulk or interrupt end of transfer, provided that the End of DMA Buffer Output Enable (END\_B\_EN) bit and the Automatic Switch (AUTOSW) = 1.

| Value | Description                                                                |

|-------|----------------------------------------------------------------------------|

| 0     | Cleared when USBHS_DEVEPTIDRx.SHORTPACKETEC = 1. This disables the Short   |

|       | Packet interrupt (USBHS_DEVEPTISRx.SHORTPACKET).                           |

| 1     | Set when USBHS_DEVEPTIERx.SHORTPACKETES = 1. This enables the Short Packet |

|       | interrupt (USBHS_DEVEPTISRx.SHORTPACKET).                                  |

### Bit 6 – STALLEDE STALLed Interrupt

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_DEVEPTIDRx.STALLEDEC = 1. This disables the STALLed interrupt |

|       | (USBHS_DEVEPTISRx.STALLEDI).                                                     |

| 1     | Set when USBHS_DEVEPTIERx.STALLEDES = 1. This enables the STALLed interrupt      |

|       | (USBHS_DEVEPTISRx.STALLEDI).                                                     |

### Bit 5 – OVERFE Overflow Interrupt

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_DEVEPTIDRx.OVERFEC = 1. This disables the Overflow interrupt |

|       | (USBHS_DEVEPTISRx.OVERFI).                                                      |

| 1     | Set when USBHS_DEVEPTIERx.OVERFES = 1. This enables the Overflow interrupt      |

|       | (USBHS_DEVEPTISRx.OVERFI).                                                      |

### Bit 4 - NAKINE NAKed IN Interrupt

# **USB High-Speed Interface (USBHS)**

#### 39.6.55 Host Pipe x Mask Register (Interrupt Pipes)

| Name:     | USBHS_HSTPIPIMRx (INTPIPES) |

|-----------|-----------------------------|

| Offset:   | 0x05C0 + x*0x04 [x=09]      |

| Reset:    | 0                           |

| Property: | Read/Write                  |

This register view is relevant only if PTYPE = 0x3 in "Host Pipe x Configuration Register".

| Bit    | 31         | 30        | 29      | 28       | 27    | 26       | 25      | 24       |

|--------|------------|-----------|---------|----------|-------|----------|---------|----------|

|        |            |           |         |          |       |          |         |          |

| Access |            |           |         |          |       |          | •       |          |

| Reset  |            |           |         |          |       |          |         |          |

|        |            |           |         |          |       |          |         |          |

| Bit    | 23         | 22        | 21      | 20       | 19    | 18       | 17      | 16       |

|        |            |           |         |          |       | RSTDT    | PFREEZE | PDISHDMA |

| Access |            |           |         |          |       |          |         |          |

| Reset  |            |           |         |          |       | 0        | 0       | 0        |

|        |            |           |         |          |       |          |         |          |

| Bit    | 15         | 14        | 13      | 12       | 11    | 10       | 9       | 8        |

|        |            | FIFOCON   |         | NBUSYBKE |       |          |         |          |

| Access |            |           |         |          |       |          |         |          |

| Reset  |            | 0         |         | 0        |       |          |         |          |

|        |            |           |         |          |       |          |         |          |

| Bit    | 7          | 6         | 5       | 4        | 3     | 2        | 1       | 0        |

|        | SHORTPACKE | RXSTALLDE | OVERFIE | NAKEDE   | PERRE | UNDERFIE | TXOUTE  | RXINE    |

|        | TIE        |           |         |          |       |          |         |          |

| Access |            |           |         |          |       |          |         |          |

| Reset  | 0          | 0         | 0       | 0        | 0     | 0        | 0       | 0        |

Bit 18 – RSTDT Reset Data Toggle

| Value | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| 0     | 0: No reset of the Data Toggle is ongoing.                                                                  |

| 1     | Set when USBHS_HSTPIPIER.RSTDTS = 1. This resets the Data Toggle to its initial value for the current pipe. |

## Bit 17 – PFREEZE Pipe Freeze

This freezes the pipe request generation.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTPIPIDR.PFREEZEC = 1. This enables the pipe request generation. |

| 1     | Set when one of the following conditions is met:                                     |

|       | • USBHS_HSTPIPIER.PFREEZES = 1                                                       |

|       | The pipe is not configured.                                                          |

|       | A STALL handshake has been received on the pipe.                                     |

|       | • An error has occurred on the pipe (USBHS_HSTPIPISR.PERRI = 1).                     |

## Serial Peripheral Interface (SPI)

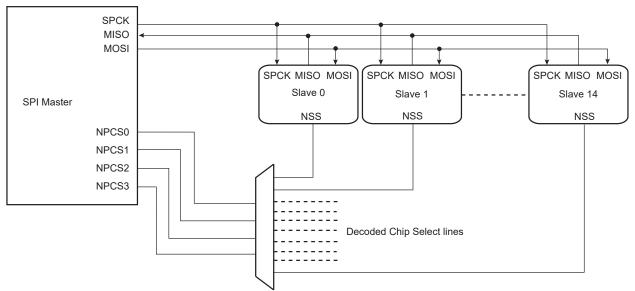

# Figure 41-10. Chip Select Decoding Application Block Diagram: Single Master/Multiple Slave Implementation

External 1-of-n Decoder/Demultiplexer

## 41.7.3.8 Peripheral Deselection without DMA

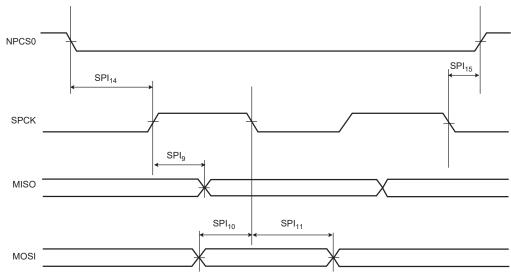

During a transfer of more than one unit of data on a chip select without the DMA, SPI\_TDR is loaded by the processor, the TDRE flag rises as soon as the content of SPI\_TDR is transferred into the internal shift register. When this flag is detected high, SPI\_TDR can be reloaded. If this reload by the processor occurs before the end of the current transfer and if the next transfer is performed on the same chip select as the current transfer, the chip select is not deasserted between the two transfers. But depending on the application software handling the SPI status register flags (by interrupt or polling method) or servicing other interrupts or other tasks, the processor may not reload SPI\_TDR in time to keep the chip select active (low). A null DLYBCT value (delay between consecutive transfers) in SPI\_CSR, gives even less time for the processor to reload SPI\_TDR. With some SPI slave peripherals, if the chip select line must remain active (low) during a full set of transfers, communication errors can occur.

To facilitate interfacing with such devices, the chip select registers [SPI\_CSR0...SPI\_CSR3] can be programmed with the Chip Select Active After Transfer (CSAAT) bit at 1. This allows the chip select lines to remain in their current state (low = active) until a transfer to another chip select is required. Even if SPI\_TDR is not reloaded, the chip select remains active. To deassert the chip select line at the end of the transfer, the Last Transfer (LASTXFER) bit in SPI\_CR must be set after writing the last data to transmit into SPI\_TDR.

### 41.7.3.9 Peripheral Deselection with DMA

DMA provides faster reloads of SPI\_TDR compared to software. However, depending on the system activity, it is not guaranteed that SPI\_TDR is written with the next data before the end of the current transfer. Consequently, data can be lost by the deassertion of the NPCS line for SPI slave peripherals requiring the chip select line to remain active between two transfers. The only way to guarantee a safe transfer in this case is the use of the CSAAT and LASTXFER bits.

When the CSAAT bit is configured to 0, the NPCS does not rise in all cases between two transfers on the same peripheral. During a transfer on a chip select, the TDRE flag rises as soon as the content of SPI\_TDR is transferred into the internal shift register. When this flag is detected, SPI\_TDR can be reloaded. If this reload occurs before the end of the current transfer and if the next transfer is performed on the same chip select as the current transfer, the chip select is not deasserted between the two

# Synchronous Serial Controller (SSC)

|        | Name:<br>Offset:<br>Reset:<br>Property: | SSC_WPSR<br>0xE8<br>0x00000000<br>Read-only |    |       |          |    |    |      |

|--------|-----------------------------------------|---------------------------------------------|----|-------|----------|----|----|------|

| Bit    | 31                                      | 30                                          | 29 | 28    | 27       | 26 | 25 | 24   |

|        |                                         |                                             |    |       |          |    |    |      |

| Access |                                         |                                             |    |       |          |    |    |      |

| Reset  |                                         |                                             |    |       |          |    |    |      |

| Bit    | 23                                      | 22                                          | 21 | 20    | 19       | 18 | 17 | 16   |

| Dit    | 23                                      | 22                                          | 21 |       | RC[15:8] | 10 | 17 | 10   |

|        |                                         |                                             |    |       |          |    |    |      |

| Access |                                         | R                                           | R  | R     | R        | R  | R  | R    |

| Reset  | 0                                       | 0                                           | 0  | 0     | 0        | 0  | 0  | 0    |

|        |                                         |                                             |    |       |          |    |    |      |

| Bit    | 15                                      | 14                                          | 13 | 12    | 11       | 10 | 9  | 8    |

|        |                                         |                                             |    | WPVSI | RC[7:0]  |    |    |      |

| Access | R                                       | R                                           | R  | R     | R        | R  | R  | R    |

| Reset  | 0                                       | 0                                           | 0  | 0     | 0        | 0  | 0  | 0    |

|        |                                         |                                             |    |       |          |    |    |      |

| Bit    | 7                                       | 6                                           | 5  | 4     | 3        | 2  | 1  | 0    |

|        |                                         |                                             |    |       |          |    |    | WPVS |

| Access |                                         |                                             |    |       |          |    |    | R    |

| Reset  |                                         |                                             |    |       |          |    |    | 0    |

|        |                                         |                                             |    |       |          |    |    |      |

### 44.9.18 SSC Write Protection Status Register

## Bits 23:8 - WPVSRC[15:0] Write Protect Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

## Bit 0 – WPVS Write Protection Violation Status

| Value | Description                                                                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No write protection violation has occurred since the last read of the SSC_WPSR.                                                                                                                                    |

| 1     | A write protection violation has occurred since the last read of the SSC_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC. |

#### 46.6.10.9 LON Errors

All these flags can be read in the Channel Status register (LON\_MODE) (US\_CSR) and will generate interrupts if configured in the Interrupt Enable register (LON\_MODE) (US\_IER).

These flags can be reset through US\_CR.RSTSTA.

#### 46.6.10.9.1 Underrun Error

If the USART is in LON mode and if a character is sent while the Transmit Holding register (US\_THR) is empty, the UNRE bit flag is set.

#### 46.6.10.9.2 Collision Detection

The LCOL flag is set whenever a valid collision has been detected and the LON node is configured to report it (see "Collision Detection").

#### 46.6.10.9.3 LON Frame Early Termination

The LFET flag is set whenever a LON frame has been terminated early due to collision detection.

#### 46.6.10.9.4 Reception Error

The LCRCE flag is set if the received frame has an erroneous CRC and the flag LSFE is set if the received frame is too short (LON frames must be at least 8 bytes long).

These flags can be read in US\_CSR.

#### 46.6.10.9.5 Backlog Overflow

The LBLOVFE flag is set if the LON node backlog estimation goes over 63 which is the maximum backlog value.

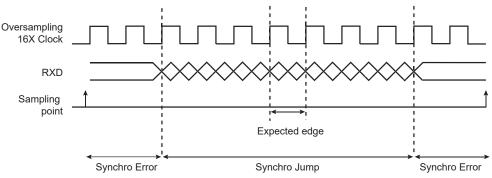

#### 46.6.10.10 Drift Compensation

While receiving a frame, the baud rate used by the sender may not be exactly the one expected. In this case, the hardware drift compensation algorithm recovers up to 16% clock drift (expected baud rate ±16% will be supported).

Drift compensation is available only in 16X Oversampling mode. To enable the hardware system, US\_MAN.DRIFT must be set. If the RXD edge is between one and three 16X clock cycles far from the expected edge, then the period is shortened or lengthened accordingly, to center the RXD edge.

The drift compensation hardware feature allows up to 16% clock drift to be handled, provided the system clock is fast enough compared to the selected baud rate.

#### Figure 46-60. Bit Resynchronization

#### 46.6.10.11 LON Frame Handling

#### 46.6.10.11.1 Sending A Frame

- 1. Write TXEN and RXEN in US\_CR to enable both the transmitter and the receiver.

- 2. Write USART\_MODE in US\_MR to select the LON mode configuration.

## Universal Synchronous Asynchronous Receiver Transc...

| Figure 46-62           | Rx Frame                                                                      |

|------------------------|-------------------------------------------------------------------------------|

|                        | Random Delay  Preamble    I2hdr  Data 1    Data 2      Data N-1      Data N-1 |

| TXRDY _                |                                                                               |

| RXRDY _                |                                                                               |

| Write _<br>US_LONL2HDR |                                                                               |

| Read                   | <u> </u>                                                                      |

| US_RHR                 | I2hdr Data 1 Data 2 Data N-1 Data N                                           |

| LRXD                   |                                                                               |

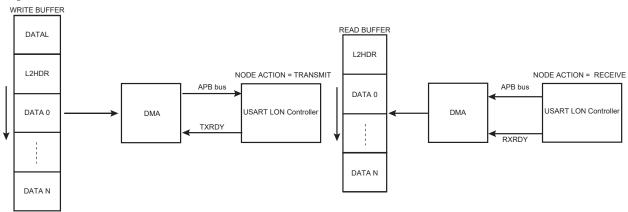

#### 46.6.10.12 LON Frame Handling with the Peripheral DMA Controller

The USART can be used in association with the DMA Controller in order to transfer data directly into/from the on- and off-chip memories without any processor intervention.

The DMA uses the trigger flags, TXRDY and RXRDY, to write or read into the USART. The DMA always writes in US\_THR and it always reads in US\_RHR. The size of the data written or read by the DMA in the USART is always a byte.

### 46.6.10.12.1 Configuration

The DMA mode is configured in USLONMR.DMAM:

- DMAM = 1: The LON frame data length (DATAL) is stored in the WRITE buffer and it is written by the DMA in US\_THR (instead of the LON Data Length register US\_LONDL).

- DMAM = 0: The LON frame data length (DATAL) is not stored in the WRITE buffer and it must be written by the user in US\_LONDL.

In both DMA modes L2HDR is considered as a data and its value must be stored in the WRITE buffer as the first data to write.

#### Figure 46-63. DMAM = 1

# SAM E70/S70/V70/V71 Family Universal Synchronous Asynchronous Receiver Transc...

## 46.7.2 USART Control Register (SPI\_MODE)

Name:US\_CR (SPI\_MODE)Offset:0x0000Property:Write-only

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

| Bit    | 31    | 30   | 29    | 28   | 27    | 26    | 25 | 24     |

|--------|-------|------|-------|------|-------|-------|----|--------|

|        |       |      |       |      |       |       |    |        |

| Access |       |      |       |      |       |       |    |        |

| Reset  |       |      |       |      |       |       |    |        |

|        |       |      |       |      |       |       |    |        |

| Bit    | 23    | 22   | 21    | 20   | 19    | 18    | 17 | 16     |

|        |       |      |       |      | RCS   | FCS   |    |        |

| Access |       | •    | •     |      | •     | •     | •  |        |

| Reset  |       |      |       |      |       |       |    |        |

|        |       |      |       |      |       |       |    |        |

| Bit    | 15    | 14   | 13    | 12   | 11    | 10    | 9  | 8      |

|        |       |      |       |      |       |       |    | RSTSTA |

| Access |       | •    |       |      |       |       |    | ·      |

| Reset  |       |      |       |      |       |       |    |        |

|        |       |      |       |      |       |       |    |        |

| Bit    | 7     | 6    | 5     | 4    | 3     | 2     | 1  | 0      |

|        | TXDIS | TXEN | RXDIS | RXEN | RSTTX | RSTRX |    |        |

| Access |       |      |       |      |       |       |    |        |

| Reset  |       |      |       |      |       |       |    |        |

### Bit 19 – RCS Release SPI Chip Select

Applicable if USART operates in SPI Master mode (USART\_MODE = 0xE):

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | No effect.                                    |

| 1     | Releases the Slave Select Line NSS (RTS pin). |

#### Bit 18 – FCS Force SPI Chip Select

Applicable if USART operates in SPI Master mode (USART\_MODE = 0xE):

| Value | Description                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No effect.                                                                                                                                                                               |

| 1     | Forces the Slave Select Line NSS (RTS pin) to 0, even if USART is not transmitting, in order to address SPI slave devices supporting the CSAAT mode (Chip Select Active After Transfer). |

#### Bit 8 – RSTSTA Reset Status Bits

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | No effect.                                   |

| 1     | Resets the status bits OVRE, UNRE in US_CSR. |

# Universal Asynchronous Receiver Transmitter (UART)

| Offset | Name           | Bit Pos. |             |  |      |          |  |  |      |

|--------|----------------|----------|-------------|--|------|----------|--|--|------|

|        | 0xE4 UART_WPMR | 7:0      |             |  |      |          |  |  | WPEN |

| 0.4    |                | 15:8     |             |  | WPKE | Y[7:0]   |  |  |      |