Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 300MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 114                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70q19a-ant       |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 1. Round-robin Arbitration (default)

- 2. Fixed Priority Arbitration

Each algorithm may be complemented by selecting a default master configuration for each slave.

When re-arbitration is required, specific conditions apply. Refer to the "Arbitration Rules" section.

### 19.3.3.1 Arbitration Rules

Each arbiter has the ability to arbitrate between requests from two or more masters. To avoid burst breaking and to provide maximum throughput for slave interfaces, arbitration should take place during the following cycles:

- Idle cycles: When a slave is not connected to any master or is connected to a master which is not currently accessing it

- Single cycles: When a slave is performing a single access

- End of Burst cycles: When the current cycle is the last cycle of a burst transfer. For a defined length burst, predicted end of burst matches the size of the transfer but is managed differently for undefined length burst. Refer to the "Undefined Length Burst Arbitration" section.

- Slot cycle limit: When the slot cycle counter has reached the limit value indicating that the current master access is too long and must be broken. Refer to the "Slot Cycle Limit Arbitration" section.

### 19.3.3.1.1 Undefined Length Burst Arbitration

In order to prevent slave handling during undefined length bursts, the user can trigger the re-arbitration before the end of the incremental bursts. The re-arbitration period can be selected from the following Undefined Length Burst Type (ULBT) possibilities:

- 1. Unlimited: no predetermined end of burst is generated. This value enables 1-Kbyte burst lengths.

- 2. 1-beat bursts: predetermined end of burst is generated at each single transfer during the INCR transfer.

- 3. 4-beat bursts: predetermined end of burst is generated at the end of each 4-beat boundary during INCR transfer.

- 4. 8-beat bursts: predetermined end of burst is generated at the end of each 8-beat boundary during INCR transfer.

- 5. 16-beat bursts: predetermined end of burst is generated at the end of each 16-beat boundary during INCR transfer.

- 6. 32-beat bursts: predetermined end of burst is generated at the end of each 32-beat boundary during INCR transfer.

- 7. 64-beat bursts: predetermined end of burst is generated at the end of each 64-beat boundary during INCR transfer.

- 8. 128-beat bursts: predetermined end of burst is generated at the end of each 128-beat boundary during INCR transfer.

The use of undefined length16-beat bursts, or less, is discouraged since this decreases the overall bus bandwidth due to arbitration and slave latencies at each first access of a burst.

If the master does not permanently and continuously request the same slave or has an intrinsically limited average throughput, the ULBT should be left at its default unlimited value, knowing that the AHB specification natively limits all word bursts to 256 beats and double-word bursts to 128 beats because of its 1-Kbyte address boundaries.

Unless duly needed, the ULBT should be left at its default value of 0 for power saving.

This selection is made through the ULBT field of the Master Configuration Registers (MATRIX\_MCFG).

## Bus Matrix (MATRIX)

| Offset | Name              | Bit Pos.       |  |                 |        |           |            |

|--------|-------------------|----------------|--|-----------------|--------|-----------|------------|

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  |                 |        | ULBT[2:0] |            |

| 0x2C   | MATRIX_MCFG11     | 15:8           |  |                 |        |           |            |

| 0/120  |                   | 23:16          |  |                 |        |           |            |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  |                 |        | ULBT[2:0] |            |

| 0x30   | MATRIX_MCFG12     | 15:8           |  |                 |        |           |            |

|        |                   | 23:16          |  |                 |        |           |            |

|        |                   | 31:24          |  |                 |        |           |            |

| 0x34   |                   |                |  |                 |        |           |            |

|        | Reserved          |                |  |                 |        |           |            |

| 0x3F   |                   |                |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x40   | MATRIX_SCFG0      | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x44   | MATRIX_SCFG1      | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        | 0x48 MATRIX_SCFG2 | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x48   |                   | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        | 0.07.0    |            |

| 0x4C   | MATRIX_SCFG3      | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x50   | MATRIX_SCFG4      | 15:8           |  |                 |        |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFMSTR   | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

| 0x54   | MATRIX_SCFG5      | 15:8           |  |                 | D[2,0] |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | R[3:0] | DEFINISTR | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        | SLOT C    |            |

| 0x58   | MATRIX_SCFG6      | 15:8           |  | FIXED_DEFMST    | D[3:0] |           | YCLE[8:7]  |

|        |                   | 23:16<br>31:24 |  | FIXED_DEFINST   | N[0.0] | DEFINISTR | _TYPE[1:0] |

|        |                   | 7:0            |  | SLOT_CYCLE[6:0] |        |           |            |

|        |                   | 15:8           |  |                 |        | SLOT O    |            |

| 0x5C   | MATRIX_SCFG7      |                |  |                 | P[3:0] |           | YCLE[8:7]  |

|        |                   | 23:16          |  | FIXED_DEFMST    | N[J.U] | DELINGIK  | _TYPE[1:0] |

|        |                   | 31:24          |  |                 |        |           |            |

| 0x60   | MATRIX_SCFG8      | 7:0            |  | SLOT_CYCLE[6:0] |        | SLOT O    |            |

|        |                   | 15:8           |  |                 |        | SLUI_C    | YCLE[8:7]  |

### **Power Management Controller (PMC)**

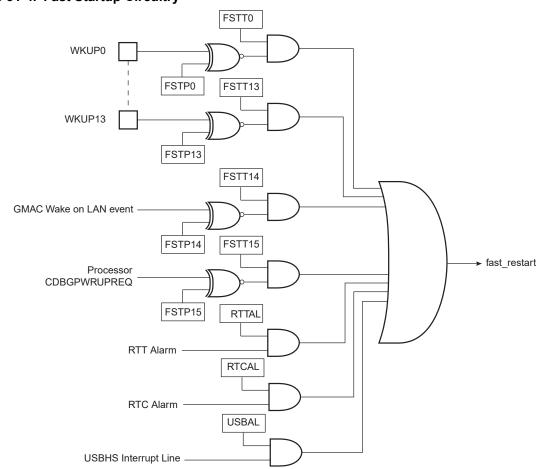

### Figure 31-4. Fast Startup Circuitry

Each wakeup input pin and alarm can be enabled to generate a fast startup event by setting the corresponding bit in PMC\_FSMR.

The user interface does not provide any status for fast startup. The status can be read in the PIO Controller and the status registers of the RTC, RTTand USB Controller.

### **Related Links**

7. Power Considerations

### 31.14 Startup from Embedded Flash

The inherent startup time of the embedded Flash cannot provide a fast startup of the system.

If system fast startup time is not required, the first instruction after a Wait mode exit can be located in the embedded Flash. Under these conditions, prior to entering Wait mode, the Flash controller must be programmed to perform access in 0 wait-state (refer to the embedded Flash controller section).

The procedure and conditions to enter Wait mode and the circuitry to exit Wait mode are strictly the same as fast startup (see "Fast Startup").

### **Related Links**

22. Enhanced Embedded Flash Controller (EEFC)

© 2018 Microchip Technology Inc.

## Power Management Controller (PMC)

| Offset | Register                                      | Name           | Access     | Reset       |

|--------|-----------------------------------------------|----------------|------------|-------------|

| 0x0130 | PLL Maximum Multiplier Value<br>Register      | PMC_PMMR       | Read/Write | 0x0000_07FF |

| 0x0134 | SleepWalking Enable Register 1                | PMC_SLPWK_ER1  | Write-only | _           |

| 0x0138 | SleepWalking Disable Register 1               | PMC_SLPWK_DR1  | Write-only | _           |

| 0x013C | SleepWalking Status Register 1                | PMC_SLPWK_SR1  | Read-only  | 0x00000000  |

| 0x0140 | SleepWalking Activity Status<br>Register 1    | PMC_SLPWK_ASR1 | Read-only  | 0x00000000  |

| 0x0144 | SleepWalking Activity In<br>Progress Register | PMC_SLPWK_AIPR | Read-only  | -           |

### Note:

- 1. If an offset is not listed in this table it must be considered as "reserved".

- 2. The reset value depends on factory settings.

### Parallel Input/Output Controller (PIO)

|                 | Name:<br>Offset:<br>Property: | PIO_PDSR<br>0x003C<br>Read-only |     |     |     |     |     |     |

|-----------------|-------------------------------|---------------------------------|-----|-----|-----|-----|-----|-----|

|                 |                               |                                 |     |     |     |     |     |     |

| Bit             |                               | 30                              | 29  | 28  | 27  | 26  | 25  | 24  |

|                 | P31                           | P30                             | P29 | P28 | P27 | P26 | P25 | P24 |

| Access          |                               |                                 |     |     |     |     |     |     |

| Reset           |                               |                                 |     |     |     |     |     |     |

| Bit             | 23                            | 22                              | 21  | 20  | 19  | 18  | 17  | 16  |

|                 | P23                           | P22                             | P21 | P20 | P19 | P18 | P17 | P16 |

| Access          |                               |                                 |     |     | 1   |     |     | 1   |

| Reset           |                               |                                 |     |     |     |     |     |     |

| Bit             | 15                            | 14                              | 13  | 12  | 11  | 10  | 9   | 8   |

|                 | P15                           | P14                             | P13 | P12 | P11 | P10 | P9  | P8  |

| Access          |                               |                                 |     | •   | •   | •   |     |     |

| Reset           |                               |                                 |     |     |     |     |     |     |

| Bit             | 7                             | 6                               | 5   | 4   | 3   | 2   | 1   | 0   |

|                 | P7                            | P6                              | P5  | P4  | P3  | P2  | P1  | P0  |

| Access<br>Reset |                               |                                 |     |     |     |     |     |     |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Output Data Status

| Value | Description                 |

|-------|-----------------------------|

| 0     | The I/O line is at level 0. |

| 1     | The I/O line is at level 1. |

32.6.1.13 PIO Pin Data Status Register

### Parallel Input/Output Controller (PIO)

#### 32.6.1.51 PIO Parallel Capture Interrupt Enable Register

| Name:     | PIO_PCIER  |

|-----------|------------|

| Offset:   | 0x0154     |

| Property: | Write-only |

The following configuration values are valid for all listed bit names of this register:

0: No effect

1: Enables the corresponding interrupt

| Bit    | 31 | 30 | 29 | 28 | 27     | 26    | 25   | 24   |

|--------|----|----|----|----|--------|-------|------|------|

|        |    |    |    |    |        |       |      |      |

| Access |    |    |    |    |        |       |      |      |

| Reset  |    |    |    |    |        |       |      |      |

|        |    |    |    |    |        |       |      |      |

| Bit    | 23 | 22 | 21 | 20 | 19     | 18    | 17   | 16   |

|        |    |    |    |    |        |       |      |      |

| Access |    |    |    |    |        |       |      |      |

| Reset  |    |    |    |    |        |       |      |      |

|        |    |    |    |    |        |       |      |      |

| Bit    | 15 | 14 | 13 | 12 | 11     | 10    | 9    | 8    |

|        |    |    |    |    |        |       |      |      |

| Access |    |    |    |    |        |       |      |      |

| Reset  |    |    |    |    |        |       |      |      |

|        |    |    |    |    |        |       |      |      |

| Bit    | 7  | 6  | 5  | 4  | 3      | 2     | 1    | 0    |

|        |    |    |    |    | RXBUFF | ENDRX | OVRE | DRDY |

| Access |    |    |    |    |        |       |      |      |

| Reset  |    |    |    |    |        |       |      |      |

Bit 3 – RXBUFF Reception Buffer Full Interrupt Enable

- **Bit 2 ENDRX** End of Reception Transfer Interrupt Enable

- Bit 1 OVRE Parallel Capture Mode Overrun Error Interrupt Enable

Bit 0 - DRDY Parallel Capture Mode Data Ready Interrupt Enable

### Static Memory Controller (SMC)

#### 35.16.1.2 SMC Pulse Register

Name:

SMC\_PULSE[0..3]

Offset:

0x00

Reset:

0

Property:

R/W

This register can only be written if the WPEN bit is cleared in the "SMC Write Protection Mode Register" .

| Bit    | 31 | 30 | 29 | 28 | 27            | 26   | 25 | 24 |

|--------|----|----|----|----|---------------|------|----|----|

|        |    |    |    | NC | S_RD_PULSE[6  | 5:0] |    |    |

| Access |    |    |    |    |               |      |    |    |

| Reset  |    | 0  | 0  | 0  | 0             | 0    | 0  | 0  |

|        |    |    |    |    |               |      |    |    |

| Bit    | 23 | 22 | 21 | 20 | 19            | 18   | 17 | 16 |

|        |    |    |    |    | NRD_PULSE[6:0 | ]    |    |    |

| Access |    |    |    |    |               |      |    |    |

| Reset  |    | 0  | 0  | 0  | 0             | 0    | 0  | 0  |

|        |    |    |    |    |               |      |    |    |

| Bit    | 15 | 14 | 13 | 12 | 11            | 10   | 9  | 8  |

|        |    |    |    | NC | S_WR_PULSE[6  | 3:0] |    |    |

| Access |    |    |    |    |               |      |    |    |

| Reset  |    | 0  | 0  | 0  | 0             | 0    | 0  | 0  |

|        |    |    |    |    |               |      |    |    |

| Bit    | 7  | 6  | 5  | 4  | 3             | 2    | 1  | 0  |

|        |    |    |    | I  | NWE_PULSE[6:0 | ]    |    |    |

| Access |    |    |    |    |               |      |    |    |

| Reset  |    | 0  | 0  | 0  | 0             | 0    | 0  | 0  |

### Bits 30:24 – NCS\_RD\_PULSE[6:0] NCS Pulse Length in READ Access

In standard read access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_RD\_PULSE[6] + NCS\_RD\_PULSE[5:0]) clock cycles

The NCS pulse length must be at least 1 clock cycle.

In Page mode read access, the NCS\_RD\_PULSE parameter defines the duration of the first access to one page.

### Bits 22:16 - NRD\_PULSE[6:0] NRD Pulse Length

In standard read access, the NRD signal pulse length is defined in clock cycles as:

NRD pulse length = (256\* NRD\_PULSE[6] + NRD\_PULSE[5:0]) clock cycles

The NRD pulse length must be at least 1 clock cycle.

In Page mode read access, the NRD\_PULSE parameter defines the duration of the subsequent accesses in the page.

### Bits 14:8 – NCS\_WR\_PULSE[6:0] NCS Pulse Length in WRITE Access

In write access, the NCS signal pulse length is defined as:

NCS pulse length = (256\* NCS\_WR\_PULSE[6] + NCS\_WR\_PULSE[5:0]) clock cycles

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TPFC<br>0x0C4<br>0x00000000<br>- | P   |     |        |     |     |     |

|--------|-----------------------------------------|---------------------------------------|-----|-----|--------|-----|-----|-----|

| Bit    | 31                                      | 30                                    | 29  | 28  | 27     | 26  | 25  | 24  |

|        |                                         |                                       |     |     |        |     |     |     |

| Access |                                         |                                       |     |     |        |     |     |     |

| Reset  |                                         |                                       |     |     |        |     |     |     |

| Bit    | 23                                      | 22                                    | 21  | 20  | 19     | 18  | 17  | 16  |

|        |                                         |                                       |     |     |        |     |     |     |

| Access |                                         |                                       |     |     | 1      |     |     |     |

| Reset  |                                         |                                       |     |     |        |     |     |     |

| Bit    | 15                                      | 14                                    | 13  | 12  | 11     | 10  | 9   | 8   |

|        |                                         |                                       |     | PQ  | [7:0]  |     |     |     |

| Access | R/W                                     | R/W                                   | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                     | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                       |     |     |        |     |     |     |

| Bit    | 7                                       | 6                                     | 5   | 4   | 3      | 2   | 1   | 0   |

|        |                                         |                                       |     |     | ([7:0] |     |     |     |

| Access |                                         | R/W                                   | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                     | 0   | 0   | 0      | 0   | 0   | 0   |

### 38.8.28 GMAC Transmit PFC Pause Register

### Bits 15:8 – PQ[7:0] Pause Quantum

When the Remove FCS bit in the GMAC Network Configuration register (GMAC\_NCFGR.RFCS) is written to '1', and one or more bits in this bit field are written to '0', the associated PFC pause frame's pause quantum field value is taken from the Transmit Pause Quantum register (GMAC\_TPQ).

For each entry equal to '1' in this bit field, the pause quantum associated with that entry will be zero.

### Bits 7:0 – PEV[7:0] Priority Enable Vector

When the Remove FCS bit in the GMAC Network Configuration register (GMAC\_NCFGR.RFCS) is written to '1', the priority enable vector of the PFC priority-based pause frame is set to the value stored in this bit field.

### 38.8.50 GMAC Greater Than 1518 Byte Frames Transmitted Register

| Name:     | GMAC_GTBFT1518 |

|-----------|----------------|

| Offset:   | 0x130          |

| Reset:    | 0x0000000      |

| Property: | Read-only      |

| Bit    | 31          | 30 | 29 | 28   | 27      | 26 | 25 | 24 |  |

|--------|-------------|----|----|------|---------|----|----|----|--|

|        | NFTX[31:24] |    |    |      |         |    |    |    |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |             |    |    |      |         |    |    |    |  |

| Bit    | 23          | 22 | 21 | 20   | 19      | 18 | 17 | 16 |  |

|        |             |    |    | NFTX | [23:16] |    |    |    |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |             |    |    |      |         |    |    |    |  |

| Bit    | 15          | 14 | 13 | 12   | 11      | 10 | 9  | 8  |  |

|        |             |    |    | NFTX | ([15:8] |    |    |    |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |             |    |    |      |         |    |    |    |  |

| Bit    | 7           | 6  | 5  | 4    | 3       | 2  | 1  | 0  |  |

|        |             |    |    | NFT  | X[7:0]  |    |    |    |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |             |    |    |      |         |    |    |    |  |

**Bits 31:0 – NFTX[31:0]** Greater than 1518 Byte Frames Transmitted without Error This register counts the number of 1518 or above byte frames successfully transmitted without error i.e., no underrun and not too many retries.

- For a single bank, a NYET handshake is always sent to the host (on Bulk-out transaction) to indicate that the current packet is acknowledged but there is no room for the next one.

- For a double bank, the USBHS responds to the OUT/DATA transaction with an ACK handshake when the endpoint accepted the data successfully and has room for another data payload (the second bank is free).

### 39.5.2.14 Underflow

This error only exists for isochronous IN/OUT endpoints. It sets the Underflow Interrupt (USBHS\_DEVEPTISRx.UNDERFI) bit, which triggers a PEP\_x interrupt if the Underflow Interrupt Enable (USBHS\_DEVEPTIMRx.UNDERFE) bit is one.

- An underflow can occur during the IN stage if the host attempts to read from an empty bank. A zero-length packet is then automatically sent by the USBHS.

- An underflow cannot occur during the OUT stage on a CPU action, since the user may only read if the bank is not empty (USBHS\_DEVEPTISRx.RXOUTI = 1 or USBHS\_DEVEPTISRx.RWALL = 1).

- An underflow can also occur during the OUT stage if the host sends a packet while the bank is already full. Typically, the CPU is not fast enough. The packet is lost.

- An underflow cannot occur during the IN stage on a CPU action, since the user may only write if the bank is not full (USBHS\_DEVEPTISRx.TXINI = 1or USBHS\_DEVEPTISRx.RWALL = 1).

### 39.5.2.15 Overflow

This error exists for all endpoint types. It sets the Overflow interrupt (USBHS\_DEVEPTISRx.OVERFI) bit, which triggers a PEP\_x interrupt if the Overflow Interrupt Enable (USBHS\_DEVEPTIMRx.OVERFE) bit is one.

- An overflow can occur during the OUT stage if the host attempts to write into a bank which is too small for the packet. The packet is acknowledged and the USBHS\_DEVEPTISRx.RXOUTI bit is set as if no overflow had occurred. The bank is filled with all the first bytes of the packet that fit in.

- An overflow cannot occur during the IN stage on a CPU action, since the user may only write if the bank is not full (USBHS\_DEVEPTISRx.TXINI = 1 or USBHS\_DEVEPTISRx.RWALL = 1).

### 39.5.2.16 HB Isoln Error

This error only exists for high-bandwidth isochronous IN endpoints.

At the end of the microframe, if at least one packet has been sent to the host and fewer banks than expected have been validated (by clearing the USBHS\_DEVEPTIMRx.USBHS\_DEVEPTIMRx.FIFOCON) for this microframe, it sets the USBHS\_DEVEPTISRx.HBISOINERRORI bit, which triggers a PEP\_x interrupt if the High Bandwidth Isochronous IN Error Interrupt Enable (HBISOINERRORE) bit is one.

For example, if the Number of Transactions per MicroFrame for Isochronous Endpoint (NBTRANS) field in USBHS\_DEVEPTCFGx is three (three transactions per microframe), only two banks are filled by the CPU (three expected) for the current microframe. Then, the HBISOINERRI interrupt is generated at the end of the microframe. Note that an UNDERFI interrupt is also generated (with an automatic zero-lengthpacket), except in the case of a missing IN token.

### 39.5.2.17 HB IsoFlush

This error only exists for high-bandwidth isochronous IN endpoints.

At the end of the microframe, if at least one packet has been sent to the host and there is a missing IN token during this microframe, the bank(s) destined to this microframe is/are flushed out to ensure a good data synchronization between the host and the device.

For example, if NBTRANS is three (three transactions per microframe) and if only the first IN token (among three) is well received by the USBHS, the last two banks are discarded.

### USB High-Speed Interface (USBHS)

### 39.6.50 Host Pipe x Clear Register (Isochronous Pipes)

Name:

USBHS\_HSTPIPICRx (ISOPIPES)

Offset:

0x0560 + x\*0x04 [x=0..9]

Reset:

0

Property:

Read/Write

This register view is relevant only if PTYPE = 0x1 in "Host Pipe x Configuration Register".

For additional information, see "Host Pipe x Status Register (Isochronous Pipes)".

This register always reads as zero.

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Clears the corresponding bit in USBHS\_HSTPIPISRx.

| Bit    | 31         | 30       | 29      | 28      | 27 | 26       | 25      | 24     |

|--------|------------|----------|---------|---------|----|----------|---------|--------|

|        |            |          |         |         |    |          |         |        |

| Access |            |          |         |         |    |          |         |        |

| Reset  |            |          |         |         |    |          |         |        |

|        |            |          |         |         |    |          |         |        |

| Bit    | 23         | 22       | 21      | 20      | 19 | 18       | 17      | 16     |

|        |            |          |         |         |    |          |         |        |

| Access |            |          | •       |         |    |          |         |        |

| Reset  |            |          |         |         |    |          |         |        |

|        |            |          |         |         |    |          |         |        |

| Bit    | 15         | 14       | 13      | 12      | 11 | 10       | 9       | 8      |

|        |            |          |         |         |    |          |         |        |

| Access |            |          |         |         | L  |          |         |        |

| Reset  |            |          |         |         |    |          |         |        |

|        |            |          |         |         |    |          |         |        |

| Bit    | 7          | 6        | 5       | 4       | 3  | 2        | 1       | 0      |

|        | SHORTPACKE | CRCERRIC | OVERFIC | NAKEDIC |    | UNDERFIC | TXOUTIC | RXINIC |

|        | TIC        |          |         |         |    |          |         |        |

| Access |            |          |         |         |    |          |         |        |

| Reset  | 0          | 0        | 0       | 0       |    | 0        | 0       | 0      |

Bit 7 - SHORTPACKETIC Short Packet Interrupt Clear

Bit 6 - CRCERRIC CRC Error Interrupt Clear

Bit 5 – OVERFIC Overflow Interrupt Clear

Bit 4 – NAKEDIC NAKed Interrupt Clear

- Bit 2 UNDERFIC Underflow Interrupt Clear

- Bit 1 TXOUTIC Transmitted OUT Data Interrupt Clear

### Two-wire Interface (TWIHS)

### Bits 22:16 - SADR[6:0] Slave Address

The slave device address is used in Slave mode in order to be accessed by master devices in Read or Write mode.

SADR must be programmed before enabling the Slave mode or after a general call. Writes at other times have no effect.

### Bits 14:8 - MASK[6:0] Slave Address Mask

A mask can be applied on the slave device address in Slave mode in order to allow multiple address answer. For each bit of the MASK field set to 1, the corresponding SADR bit is masked.

If the MASK field value is 0, no mask is applied to the SADR field.

### Bit 6 – SCLWSDIS Clock Wait State Disable

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | No effect.                                                                           |

| 1     | Clock stretching disabled in Slave mode, OVRE and UNRE indicate an overrun/underrun. |

#### Bit 3 - SMHH SMBus Host Header

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Acknowledge of the SMBus host header disabled. |

| 1     | Acknowledge of the SMBus host header enabled.  |

#### Bit 2 – SMDA SMBus Default Address

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | Acknowledge of the SMBus default address disabled. |

| 1     | Acknowledge of the SMBus default address enabled.  |

### Bit 0 – NACKEN Slave Receiver Data Phase NACK enable

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | Normal value to be returned in the ACK cycle of the data phase in Slave Receiver mode. |

| 1     | NACK value to be returned in the ACK cycle of the data phase in Slave Receiver mode.   |

### 45. Inter-IC Sound Controller (I2SC)

### 45.1 Description

The Inter-IC Sound Controller (I2SC) provides a 5-wire, bidirectional, synchronous, digital audio link to external audio devices: I2SC\_DI, I2SC\_DO, I2SC\_WS, I2SC\_CK, and I2SC\_MCK pins.

The I2SC is compliant with the Inter-IC Sound (I<sup>2</sup>S) bus specification.

The I2SC consists of a receiver, a transmitter and a common clock generator that can be enabled separately to provide Master, Slave or Controller modes with receiver and/or transmitter active.

DMA Controller channels, separate for the receiver and for the transmitter, allow a continuous high bit rate data transfer without processor intervention to the following:

- Audio CODECs in Master, Slave, or Controller mode

- Stereo DAC or ADC through a dedicated I<sup>2</sup>S serial interface

The I2SC can use either a single DMA Controller channel for both audio channels or one DMA Controller channel per audio channel.

The 8- and 16-bit compact stereo format reduces the required DMA Controller bandwidth by transferring the left and right samples within the same data word.

In Master mode, the I2SC can produce a 32  $f_s$  to 1024  $f_s$  master clock that provides an over-sampling clock to an external audio codec or digital signal processor (DSP).

### 45.2 Embedded Characteristics

- Compliant with Inter-IC Sound (I<sup>2</sup>S) Bus Specification

- Master, Slave, and Controller Modes

- Slave: Data Received/Transmitted

- Master: Data Received/Transmitted And Clocks Generated

- Controller: Clocks Generated

- Individual Enable and Disable of Receiver, Transmitter and Clocks

- Configurable Clock Generator Common to Receiver and Transmitter

- Suitable for a Wide Range of Sample Frequencies (fs), Including 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, and 192 kHz

- 32 f<sub>s</sub> to 1024 f<sub>s</sub> Master Clock Generated for External Oversampling Data Converters

- Support for Multiple Data Formats

- 32-, 24-, 20-, 18-, 16-, and 8-bit Mono or Stereo Format

- 16- and 8-bit Compact Stereo Format, with Left and Right Samples Packed in the Same Word to Reduce Data Transfers

- DMA Controller Interfaces the Receiver and Transmitter to Reduce Processor Overhead

- One DMA Controller Channel for Both Audio Channels, or

- One DMA Controller Channel Per Audio Channel

- Smart Holding Registers Management to Avoid Audio Channels Mix After Overrun or Underrun

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.45 USART IC DIFF Register

Name:US\_ICDIFFOffset:0x0088Reset:0x0Property:Read/Write

This register is relevant only if USART\_MODE = 0x9 in the USART Mode Register.

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28 | 27 | 26    | 25     | 24 |

|--------|----|----|----|----|----|-------|--------|----|

|        |    |    |    |    |    |       |        |    |

| Access |    |    |    |    |    |       |        |    |

| Reset  |    |    |    |    |    |       |        |    |

|        |    |    |    |    |    |       |        |    |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18    | 17     | 16 |

|        |    |    |    |    |    |       |        |    |

| Access |    |    |    |    |    |       |        |    |

| Reset  |    |    |    |    |    |       |        |    |

|        |    |    |    |    |    |       |        |    |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10    | 9      | 8  |

|        |    |    |    |    |    |       |        |    |

| Access |    |    |    |    |    |       |        |    |

| Reset  |    |    |    |    |    |       |        |    |

|        |    |    |    |    |    |       |        |    |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2     | 1      | 0  |

|        |    |    |    |    |    | ICDIF | F[3:0] |    |

| Access |    |    |    |    |    |       |        |    |

| Reset  |    |    |    |    | 0  | 0     | 0      | 0  |

Bits 3:0 - ICDIFF[3:0] IC Differentiator Number

### **Controller Area Network (MCAN)**

| Offset | Name        | Bit Pos. |        |           |        |        |        |           |        |        |

|--------|-------------|----------|--------|-----------|--------|--------|--------|-----------|--------|--------|

|        |             | 15:8     | TIE15  | TIE14     | TIE13  | TIE12  | TIE11  | TIE10     | TIE9   | TIE8   |

|        |             | 23:16    | TIE23  | TIE22     | TIE21  | TIE20  | TIE19  | TIE18     | TIE17  | TIE16  |

|        |             | 31:24    | TIE31  | TIE30     | TIE29  | TIE28  | TIE27  | TIE26     | TIE25  | TIE24  |

| 0xE4   |             | 7:0      | CFIE7  | CFIE6     | CFIE5  | CFIE4  | CFIE3  | CFIE2     | CFIE1  | CFIE0  |

|        | MCAN TXBCIE | 15:8     | CFIE15 | CFIE14    | CFIE13 | CFIE12 | CFIE11 | CFIE10    | CFIE9  | CFIE8  |

|        | MOAN_TABOLE | 23:16    | CFIE23 | CFIE22    | CFIE21 | CFIE20 | CFIE19 | CFIE18    | CFIE17 | CFIE16 |

|        |             | 31:24    | CFIE31 | CFIE30    | CFIE29 | CFIE28 | CFIE27 | CFIE26    | CFIE25 | CFIE24 |

| 0xE8   |             |          |        |           |        |        |        |           |        |        |

|        | Reserved    |          |        |           |        |        |        |           |        |        |

| 0xEF   |             |          |        |           |        |        |        |           |        |        |

|        |             | 7:0      |        | EFSA[5:0] |        |        |        |           |        |        |

| 0xF0   | MCAN TXEFC  | 15:8     |        |           |        | EFSA   | [13:6] |           |        |        |

| 0110   |             | 23:16    |        |           |        |        | EFS    | [5:0]     |        |        |

|        |             | 31:24    |        |           |        |        | EFWI   | M[5:0]    |        |        |

|        |             | 7:0      |        |           |        |        | EFFI   | _[5:0]    |        |        |

| 0xF4   | MCAN TXEFS  | 15:8     |        |           |        |        |        | EFGI[4:0] |        |        |

|        |             | 23:16    |        |           |        |        |        | EFPI[4:0] |        |        |

|        |             | 31:24    |        |           |        |        |        |           | TEFL   | EFF    |

|        |             | 7:0      |        |           |        |        |        | EFAI[4:0] |        |        |

| 0xF8   | MCAN TXEFA  | 15:8     |        |           |        |        |        |           |        |        |

| 0,10   |             | 23:16    |        |           |        |        |        |           |        |        |

|        |             | 31:24    |        |           |        |        |        |           |        |        |

### Pulse Width Modulation Controller (PWM)

| Value | Name         | Description           |

|-------|--------------|-----------------------|

|       | МСК          | Peripheral clock      |

| 1     | MCK_DIV_2    | Peripheral clock/2    |

| 2     | MCK_DIV_4    | Peripheral clock/4    |

| 3     | MCK_DIV_8    | Peripheral clock/8    |

| 4     | MCK_DIV_16   | Peripheral clock/16   |

| 5     | MCK_DIV_32   | Peripheral clock/32   |

| 6     | MCK_DIV_64   | Peripheral clock/64   |

| 7     | MCK_DIV_128  | Peripheral clock/128  |

| 8     | MCK_DIV_256  | Peripheral clock/256  |

| 9     | MCK_DIV_512  | Peripheral clock/512  |

| 10    | MCK_DIV_1024 | Peripheral clock/1024 |

| 11    | CLKA         | Clock A               |

| 12    | CLKB         | Clock B               |

### Advanced Encryption Standard (AES)

### 57.5.10 AES Initialization Vector Register x

| Name:     | AES_IVRx             |

|-----------|----------------------|

| Offset:   | 0x60 + x*0x04 [x=03] |

| Reset:    | -                    |

| Property: | Write-only           |

| Bit    | 31 | 30 | 29 | 28   | 27    | 26 | 25 | 24 |

|--------|----|----|----|------|-------|----|----|----|

|        |    |    |    | IV[3 | 1:24] |    |    |    |

| Access | W  | W  | W  | W    | W     | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0    | 0     | 0  | 0  | 0  |

|        |    |    |    |      |       |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19    | 18 | 17 | 16 |

|        |    |    |    | IV[2 | 3:16] |    |    |    |

| Access | W  | W  | W  | W    | W     | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0    | 0     | 0  | 0  | 0  |

|        |    |    |    |      |       |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11    | 10 | 9  | 8  |

|        |    |    |    | IV[1 | 5:8]  |    |    |    |

| Access | W  | W  | W  | W    | W     | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0    | 0     | 0  | 0  | 0  |

|        |    |    |    |      |       |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3     | 2  | 1  | 0  |

|        |    |    |    | IV[  | 7:0]  |    |    |    |

| Access | W  | W  | W  | W    | W     | W  | W  | W  |

| Reset  | 0  | 0  | 0  | 0    | 0     | 0  | 0  | _  |

### Bits 31:0 - IV[31:0] Initialization Vector

The four 32-bit Initialization Vector registers set the 128-bit Initialization Vector data block that is used by some modes of operation as an additional initial input.

AES\_IVR0 corresponds to the first word of the Initialization Vector, AES\_IVR3 to the last one.

These registers are write-only to prevent the Initialization Vector from being read by another application.

For CBC, OFB and CFB modes, the IV input value corresponds to the initialization vector.

For CTR mode, the IV input value corresponds to the initial counter value.

Note: These registers are not used in ECB mode and must not be written.

Electrical Characteristics for SAM ...

### 58.8.5 AFE Electrical Characteristics

Table 58-34. AFE INL and DNL, f<sub>AFE CLOCK</sub> = < 20 MHz Maximum, IBCTL = 10

| Symbol | Parameter                  | Conditions | Min | Тур  | Max | Unit |  |  |

|--------|----------------------------|------------|-----|------|-----|------|--|--|

|        | Differential Mode          |            |     |      |     |      |  |  |

|        |                            | Gain = 1   |     | ±0.7 |     |      |  |  |

| INL    | Integral Non-Linearity     | Gain = 2   | -4  | ±1   | 4   | LSB  |  |  |

|        |                            | Gain = 4   | -   | ±1.2 |     |      |  |  |

| DNL    | Differential Non-Linearity | -          | -2  | ±0.6 | 2   | LSB  |  |  |

|        | Single-En                  | ded Mode   |     |      |     |      |  |  |

|        | Integral Non-Linearity     | Gain = 1   |     | ±1   |     |      |  |  |

| INL    |                            | Gain = 2   | -6  | ±1.3 | 4   | LSB  |  |  |

|        |                            | Gain = 4   |     | ±1.7 |     |      |  |  |

| DNL    | Differential Non-Linearity | _          | -2  | ±0.6 | 2   | LSB  |  |  |

Note: INL/DNL given inside the linear range of the AFE: 2% to 98% of VREFP.

### Table 58-35. AFE INL and DNL, fAFE CLOCK = > 20 MHz to 40 MHz, IBCTL = 11

| Symbol | Parameter                  | Conditions | Min | Тур  | Мах | Unit |  |  |  |

|--------|----------------------------|------------|-----|------|-----|------|--|--|--|

|        | Differential Mode          |            |     |      |     |      |  |  |  |

|        |                            | Gain = 1   |     | ±2   |     |      |  |  |  |

| INL    | Integral Non-Linearity     | Gain = 2   | -12 | ±2.1 | 12  | LSB  |  |  |  |

|        |                            | Gain = 4   |     | ±2.5 |     |      |  |  |  |

| DNL    | Differential Non-Linearity | -          | -6  | ±2   | 6   | LSB  |  |  |  |

|        | Single-En                  | ded Mode   |     |      |     |      |  |  |  |

|        | Integral Non-Linearity     | Gain = 1   |     | ±2   |     |      |  |  |  |

| INL    |                            | Gain = 2   | -12 | ±2.6 | 12  | LSB  |  |  |  |

|        |                            | Gain = 4   |     | ±2.7 |     |      |  |  |  |

| DNL    | Differential Non-Linearity | _          | -6  | ±2   | 6   | LSB  |  |  |  |

**Note:** INL/DNL given inside the linear range of the AFE: 2% to 98% of VREFP.

### Table 58-36. AFE Offset and Gain Error, V<sub>VREFP</sub> = 1.7V to 3.3V

| Symbol            | Parameter                              | Conditions | Min  | Typ(1) | Мах | Unit |  |

|-------------------|----------------------------------------|------------|------|--------|-----|------|--|

| Differential Mode |                                        |            |      |        |     |      |  |

| Eo                | Differential Offset Error (see Note 1) | Gain=1     | -20  | _      | 35  | LSB  |  |

| E <sub>G</sub>    | Differential Gain Error                | Gain=1     | -0.3 | 0      | 0.7 | %    |  |

## Revision History

| Date      | Changes                                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | - Section 38.6.6 "Device Global Interrupt Status Register"                                                                                                                                      |

|           | - Section 38.6.9 "Device Global Interrupt Mask Register"                                                                                                                                        |

|           | - Section 38.6.10 "Device Global Interrupt Disable Register"                                                                                                                                    |

|           | - Section 38.6.11 "Device Global Interrupt Enable Register"                                                                                                                                     |

|           | - Section 38.6.32 "Host Global Interrupt Status Register"                                                                                                                                       |

|           | - Section 38.6.35 "Host Global Interrupt Mask Register"                                                                                                                                         |

|           | - Section 38.6.36 "Host Global Interrupt Disable Register"                                                                                                                                      |

|           | - Section 38.6.37 "Host Global Interrupt Enable Register"                                                                                                                                       |

| 08-Feb-16 | Section 39. "Ethernet MAC (GMAC)"<br>Updated Section 39.1 "Description".                                                                                                                        |

|           | Section 39.5.2 "Power Management": deleted reference to PMC_PCER.                                                                                                                               |

|           | Section 39.5.3 "Interrupt Sources": deleted reference to 'Advanced Interrupt Controller'.<br>Replaced by 'interrupt controller'. Added information on interrupt sources and priority<br>queues. |

|           | Section 39.6.14 "IEEE 1588 Support": Removed reference to 'output pins' in 2nd paragraph. Deleted reference to GMAC_TSSx.                                                                       |

|           | Section 39.6.15 "Time Stamp Unit" added information on GTSUCOMP signal in last paragraph.                                                                                                       |

|           | Updated register index range for:                                                                                                                                                               |

|           | - Section 39.8.106 "GMAC Interrupt Status Register Priority Queue x"                                                                                                                            |

|           | - Section 39.8.107 "GMAC Transmit Buffer Queue Base Address Register Priority Queue x"                                                                                                          |

|           | - Section 39.8.108 "GMAC Receive Buffer Queue Base Address Register Priority Queue x"                                                                                                           |

|           | - Section 39.8.109 "GMAC Receive Buffer Size Register Priority Queue x"                                                                                                                         |

|           | - Section 39.8.115 "GMAC Interrupt Enable Register Priority Queue x"                                                                                                                            |

|           | - Section 39.8.116 "GMAC Interrupt Disable Register Priority Queue x"                                                                                                                           |

|           | - Section 39.8.117 "GMAC Interrupt Mask Register Priority Queue x"                                                                                                                              |

|           | Section 39.8.117 "GMAC Interrupt Mask Register Priority Queue x": inverted bit value definitions ('0' means enabled, '1' means disabled.                                                        |

|           | Section 41. "Serial Peripheral Interface (SPI)"<br>Section 41.8.1 "SPI Control Register": added bits FIFODIS, FIFOEN, RXFCLR, TXFCLR<br>and REQCLR.                                             |

|           | Section 42. "Quad SPI Interface (QSPI)"                                                                                                                                                         |

|           | Section 42.7.2 "QSPI Mode Register": updated equations and NBBITS description.                                                                                                                  |

|           | Section 42.7.5 "QSPI Status Register": updated RDRF, TDRE, TXEMPTY, and OVRES field descriptions.                                                                                               |

### **Revision History**

| Date      | Changes                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Section 18.12.10 "Write Protection Status Register": in WPVS bit description, replaced two instances of "since the last read of the MATRIX_WPSR" with "since the last write of the MATRIX_WPMR".                             |

|           | Section 21. "Enhanced Embedded Flash Controller (EEFC)"<br>Section 21.4.3.2 "Write Commands": added information on DMA write accesses.                                                                                       |

|           | Section 30. "Power Management Controller (PMC)"<br>Section 30.9 "Asynchronous Partial Wake-up": inserted new sub-section "Asynchronous<br>Partial Wake-up in Wait Mode (SleepWalking)" to better describe SleepWalking.      |

|           | Section 30.10 "Free-Running Processor Clock": removed reference to MCK.                                                                                                                                                      |

|           | Section 31. "Parallel Input/Output Controller (PIO)"<br>Section 31.2 "Embedded Characteristics": added bullet on Programmable I/O Drive.                                                                                     |

|           | Added Section 31.5.12 "Programmable I/O Drive".                                                                                                                                                                              |

|           | Section 31.5.15.4 "Programming Sequence": "With DMA": in fifth step, replaced reference to BTCx with 'DMA status flag to indicate that the buffer transfer is complete'                                                      |

|           | Table 31-5 "Register Mapping": added PIO_DRIVER register at offset 0x0118 and added Section 31.6.49 "PIO I/O Drive Register".                                                                                                |

|           | Section 35. "DMA Controller (XDMAC)"<br>Added Section 35.3 "DMA Controller Peripheral Connections".                                                                                                                          |

|           | Section 37. "USB High-Speed Interface (USBHS)"<br>Table 37-1 "Description of USB Pipes/Endpoints"; corrected data in columns 'DMA' and<br>'High Bandwidth'.                                                                  |

|           | Modified signal names to HSDM/DM and HSDP/DP in Figure 37-1 "USBHS Block Diagram" and Table 37-2 "Signal Description". Updated descriptions.                                                                                 |

|           | Removed Section 37.3.1 "Application Block Diagram" and Figures 37-2, 37-3 and 37-4.                                                                                                                                          |

|           | Removed Section 37.4.1 "I/O Lines".                                                                                                                                                                                          |

|           | Modified Section 37.5.3.3 "Device Detection".                                                                                                                                                                                |

|           | Section 37.6.2 "General Status Register", Section 37.6.3 "General Status Clear Register",<br>Section 37.6.4 "General Status Set Register": removed bit VBUSRQ and bit description. Bit<br>9 now reserved in these registers. |

| 24-Feb-15 | Section 38. "Ethernet MAC (GMAC)"<br>Section 38.8.13 "GMAC Interrupt Mask Register": corrected general bit description<br>(swapped definitions provided for 0: and 1:)                                                       |

|           | Section 40. "Quad SPI Interface (QSPI)"<br>Section 40.5.4 "Direct Memory Access Controller (DMA)": added Note on 32-bit aligned<br>DMA write accesses.                                                                       |

|           | Figure 40-9 "Instruction Transmission Flow Diagram": modified text if TFRTYP = 0                                                                                                                                             |