Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 300MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 114                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LFBGA                                                                        |

| Supplier Device Package    | 144-LFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70q19a-cn        |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Input/Output Lines

| CCFG_SYSIO<br>Bit Number | Default Function<br>After Reset | Other<br>Function | Constraints for<br>Normal Start                | Configuration                                                                      |

|--------------------------|---------------------------------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------|

| 12                       | ERASE                           | PB12              | Low Level at<br>startup (see <b>Note</b><br>1) | In Matrix User Interface Registers<br>(Refer to the 19.4.7<br>CCFG_SYSIO register) |

| 7                        | TCK/SWCLK                       | PB7               | -                                              |                                                                                    |

| 6                        | TMS/SWDIO                       | PB6               | -                                              |                                                                                    |

| 5                        | TDO/<br>TRACESWO                | PB5               | -                                              |                                                                                    |

| 4                        | TDI                             | PB4               | -                                              |                                                                                    |

| -                        | PA7                             | XIN32             | -                                              | (see Note 2)                                                                       |

| -                        | PA8                             | XOUT32            | -                                              |                                                                                    |

| -                        | PB9                             | XIN               | -                                              | (see Note 3)                                                                       |

| _                        | PB8                             | XOUT              | -                                              |                                                                                    |

#### Table 8-1. System I/O Configuration Pin List

#### Note:

- 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode.

- 2. Refer to 23.4.2 Slow Clock Generator.

- 3. Refer to 30.5.3 Main Crystal Oscillator.

### 8.2.1 Serial Wire Debug Port (SW-DP) Pins

The SW-DP pins SWCLK and SWDIO are commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 4-1.

At startup, SW-DP pins are configured in SW-DP mode to allow connection with debugging probe. For more details, refer to 16. Debug and Test Features.

SW-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SW-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pulldown resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

The JTAG Debug Port TDI, TDO, TMS and TCK is inactive. It is provided for Boundary Scan Manufacturing Test purpose only.

### 8.2.2 Embedded Trace Module (ETM) Pins

The Embedded Trace Module (ETM) depends on the Trace Port Interface Unit (TPIU) to export data out of the system.

The TPUI features the following pins:

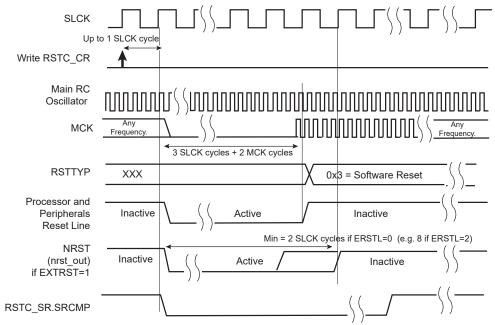

The internal reset signals are asserted as soon as the register write is performed. This is detected on the Master Clock (MCK). They are released when the software reset has ended, i.e., synchronously to SLCK.

If EXTRST is written to '1', the nrst\_out signal is asserted depending on the configuration of RSTC\_MR.ERSTL. However, the resulting falling edge on NRST does not lead to a user reset.

If and only if the RSTC\_CR.PROCRST is written to '1', the RSTC reports the software status in field RSTC\_SR.RSTTYP. Other software resets are not reported in RSTTYP.

As soon as a software operation is detected, RSTC\_SR.SRCMP is written to '1'. SRCMP is cleared at the end of the software reset. No other software reset can be performed while SRCMP is written to '1', and writing any value in the RSTC\_CR has no effect.

#### Figure 26-5. Software Reset Timing Diagram

#### 26.4.3.5 User Reset

A user reset is generated when a low level is detected on the NRST pin and RSTC\_MR.URSTEN is at '1'. The NRST input signal is resynchronized with SLCK to ensure proper behavior of the system. Thus, the NRST pin must be asserted for at least 1 SLCK clock cycle to ensure execution of a user reset.

The user reset is triggered 2 SLCK cycles after a low level is detected on NRST. The processor reset and the peripheral reset are asserted.

The user reset ends when NRST rises, after a two-cycle resynchronization time and a three-cycle processor startup. The processor clock is reenabled as soon as NRST is confirmed high.

When the processor reset signal is released, RSTC\_SR.RSTTYP is loaded with the value '4', indicating a user reset.

The NRST manager guarantees that the NRST line is asserted for External Reset Length SLCK cycles, as configured in RSTC\_MR.ERSTL. However, if NRST does not rise after External Reset Length because it is driven low externally, the internal reset lines remain asserted until NRST actually rises.

### 26.4.5 Register Summary

| Offset | Name    | Bit Pos. |          |  |         |            |             |       |         |  |

|--------|---------|----------|----------|--|---------|------------|-------------|-------|---------|--|

|        |         | 7:0      |          |  |         | EXTRST     |             |       | PROCRST |  |

| 0x00   | RSTC_CR | 15:8     |          |  |         |            |             |       |         |  |

| 0,00   | KSTC_CK | 23:16    |          |  |         |            |             |       |         |  |

|        |         | 31:24    | KEY[7:0] |  |         |            |             |       |         |  |

|        | RSTC_SR | 7:0      |          |  |         |            |             |       | URSTS   |  |

| 0x04   |         | 15:8     |          |  |         |            | RSTTYP[2:0] |       |         |  |

| 0X04   |         | 23:16    |          |  |         |            |             | SRCMP | NRSTL   |  |

|        |         | 31:24    |          |  |         |            |             |       |         |  |

|        |         | 7:0      |          |  | URSTIEN |            |             |       | URSTEN  |  |

| 0x08   | RSTC_MR | 15:8     |          |  |         | ERSTL[3:0] |             |       |         |  |

| 0,00   |         | 23:16    |          |  |         |            |             |       |         |  |

|        |         | 31:24    |          |  | KEY     | '[7:0]     |             |       |         |  |

## 29.3 Register Summary

| Offset | Name      | Bit Pos. |                   |  |         |            |  |  |  |  |  |

|--------|-----------|----------|-------------------|--|---------|------------|--|--|--|--|--|

|        |           | 7:0      | GPBR_VALUE[7:0]   |  |         |            |  |  |  |  |  |

| 0x00   | SYS_GPBRx | 15:8     | GPBR_VALUE[15:8]  |  |         |            |  |  |  |  |  |

| 0,000  |           | 23:16    | GPBR_VALUE[23:16] |  |         |            |  |  |  |  |  |

|        |           | 31:24    |                   |  | GPBR_VA | LUE[31:24] |  |  |  |  |  |

#### 34.7.1 SDRAMC Mode Register

| Name:<br>Offset:<br>Reset:<br>Property: |    | SDRAMC_MR<br>0x00<br>0x00000000<br>Read/Write | R  |    |    |     |           |     |

|-----------------------------------------|----|-----------------------------------------------|----|----|----|-----|-----------|-----|

| Bit                                     | 31 | 30                                            | 29 | 28 | 27 | 26  | 25        | 24  |

|                                         |    |                                               |    |    |    |     |           |     |

| Access                                  |    |                                               |    |    |    |     |           |     |

| Reset                                   |    |                                               |    |    |    |     |           |     |

| Bit                                     | 23 | 22                                            | 21 | 20 | 19 | 18  | 17        | 16  |

|                                         |    |                                               |    |    |    |     |           |     |

| Access                                  |    |                                               |    |    |    |     |           |     |

| Reset                                   |    |                                               |    |    |    |     |           |     |

| Bit                                     | 15 | 14                                            | 13 | 12 | 11 | 10  | 9         | 8   |

|                                         |    |                                               |    |    |    |     |           |     |

| Access                                  |    |                                               |    |    |    |     |           |     |

| Reset                                   |    |                                               |    |    |    |     |           |     |

| Bit                                     | 7  | 6                                             | 5  | 4  | 3  | 2   | 1         | 0   |

|                                         |    |                                               |    |    |    |     | MODE[2:0] |     |

| Access                                  |    |                                               |    |    |    | R/W | R/W       | R/W |

| Reset                                   |    |                                               |    |    |    | 0   | 0         | 0   |

#### Bits 2:0 - MODE[2:0] SDRAMC Command Mode

This field defines the command issued by the SDRAMC when the SDRAM device is accessed.

| Value | Name               | Description                                                                                                                                                                                         |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | NORMAL             | Normal mode. Any access to the SDRAM is decoded normally.<br>To activate this mode, the command must be followed by a write<br>to the SDRAM.                                                        |

| 1     | NOP                | The SDRAMC issues a NOP command when the SDRAM device is accessed regardless of the cycle. To activate this mode, the command must be followed by a write to the SDRAM.                             |

| 2     | ALLBANKS_PRECHARGE | The SDRAMC issues an "All Banks Precharge" command when<br>the SDRAM device is accessed regardless of the cycle. To<br>activate this mode, the command must be followed by a write to<br>the SDRAM. |

| 3     | LOAD_MODEREG       | The SDRAMC issues a "Load Mode Register" command when<br>the SDRAM device is accessed regardless of the cycle. To<br>activate this mode, the command must be followed by a write to<br>the SDRAM.   |

| 4     | AUTO_REFRESH       | The SDRAMC issues an "Autorefresh" Command when the SDRAM device is accessed regardless of the cycle. Previously,                                                                                   |

# DMA Controller (XDMAC)

| Offset | Name          | Bit Pos. |                |                        |       |       |            |        |            |       |  |  |  |  |

|--------|---------------|----------|----------------|------------------------|-------|-------|------------|--------|------------|-------|--|--|--|--|

|        |               | 15:8     |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                | ROIM                   | WBEIM | RBEIM | FIM        | DIM    | LIM        | BIM   |  |  |  |  |

|        |               | 15:8     |                |                        |       |       |            |        |            |       |  |  |  |  |

| 0x05D8 | XDMAC_CIM22   | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                | ROIS                   | WBEIS | RBEIS | FIS        | DIS    | LIS        | BIS   |  |  |  |  |

|        |               | 15:8     |                |                        |       |       |            |        |            |       |  |  |  |  |

| 0x05DC | XDMAC_CIS22   | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                |                        |       | SA[   | 7.01       |        |            |       |  |  |  |  |

|        |               | 15:8     |                | SA[15:8]               |       |       |            |        |            |       |  |  |  |  |

| 0x05E0 | XDMAC_CSA22   | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                | SA[23:16]<br>SA[31:24] |       |       |            |        |            |       |  |  |  |  |

|        |               |          |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                |                        |       | DA    |            |        |            |       |  |  |  |  |

| 0x05E4 | XDMAC_CDA22   | 15:8     |                |                        |       | DA[   |            |        |            |       |  |  |  |  |

|        |               | 23:16    |                |                        |       | DA[2  |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      | NDA[5:0] NDAIF |                        |       |       |            |        |            |       |  |  |  |  |

| 0x05E8 | XDMAC_CNDA22  | 15:8     |                | NDA[13:6]              |       |       |            |        |            |       |  |  |  |  |

|        |               | 23:16    |                |                        |       | NDA[2 |            |        |            |       |  |  |  |  |

|        |               | 31:24    | NDA[29:22]     |                        |       |       |            |        |            |       |  |  |  |  |

|        | XDMAC_CNDC22  | 7:0      |                |                        |       | NDVIE | W[1:0]     | NDDUP  | NDSUP      | NDE   |  |  |  |  |

| 0x05EC |               | 15:8     |                |                        |       |       |            |        |            |       |  |  |  |  |

| UXUJEC |               | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                | 1                      | 1     | UBLE  | N[7:0]     |        |            |       |  |  |  |  |

|        |               | 15:8     | UBLEN[15:8]    |                        |       |       |            |        |            |       |  |  |  |  |

| 0x05F0 | XDMAC_CUBC22  | 23:16    |                |                        |       | UBLEN | [23:16]    |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                |                        |       | BLEN  | N[7:0]     |        |            |       |  |  |  |  |

|        |               | 15:8     |                |                        |       |       |            | BLEN   | J[11:8]    |       |  |  |  |  |

| 0x05F4 | XDMAC_CBC22   | 23:16    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      | MEMSET         | SWREQ                  |       | DSYNC |            | MBSI   | ZE[1:0]    | TYPE  |  |  |  |  |

|        |               | 15:8     | MEMOET         | DIF                    | SIF   |       | ГН[1:0]    |        | CSIZE[2:0] |       |  |  |  |  |

| 0x05F8 | XDMAC_CC22    | 23:16    | WRIP           | RDIP                   | INITD | BWID  |            | И[1:0] |            | [1:0] |  |  |  |  |

|        |               | 31:24    | WIXII          | I COII                 | INITE |       | PERID[6:0] | /[1.0] | OAN        | [1.0] |  |  |  |  |

|        |               |          |                |                        |       |       |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                |                        |       | SDS_M |            |        |            |       |  |  |  |  |

| 0x05FC | XDMAC_CDS_MSP |          |                |                        |       |       | SP[15:8]   |        |            |       |  |  |  |  |

|        | 22            | 23:16    |                |                        |       | DDS_N |            |        |            |       |  |  |  |  |

|        |               | 31:24    |                |                        |       | DDS_M |            |        |            |       |  |  |  |  |

|        |               | 7:0      |                |                        |       | SUB   |            |        |            |       |  |  |  |  |

| 0x0600 | XDMAC_CSUS22  | 15:8     |                |                        |       | SUBS  |            |        |            |       |  |  |  |  |

|        |               | 23:16    |                |                        |       | SUBS  | [23:16]    |        |            |       |  |  |  |  |

# **GMAC - Ethernet MAC**

| <b>.</b> |                     |          |                   |                            |              |  |             |  |  |

|----------|---------------------|----------|-------------------|----------------------------|--------------|--|-------------|--|--|

| Offset   | Name                | Bit Pos. |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   |                            | DMPVAL[7:0]  |  |             |  |  |

| 0x06E0   | GMAC_ST2ER0         | 15:8     |                   | CO                         | MPVAL[15:8]  |  |             |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   |                            | DMPVAL[7:0]  |  |             |  |  |

| 0x06E4   | GMAC_ST2ER1         | 15:8     |                   | CO                         | MPVAL[15:8]  |  |             |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   |                            | DMPVAL[7:0]  |  |             |  |  |

| 0x06E8   | GMAC_ST2ER2         | 15:8     |                   | CO                         | MPVAL[15:8]  |  |             |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   |                            | DMPVAL[7:0]  |  |             |  |  |

| 0x06EC   | GMAC_ST2ER3         | 15:8     |                   | CO                         | MPVAL[15:8]  |  |             |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

| 0x06F0   |                     |          |                   |                            |              |  |             |  |  |

|          | Reserved            |          |                   |                            |              |  |             |  |  |

| 0x06FF   |                     | 7:0      |                   |                            |              |  |             |  |  |

|          | 0x0700 GMAC_ST2CW00 |          |                   |                            | ASKVAL[7:0]  |  |             |  |  |

| 0x0700   |                     |          |                   | MASKVAL[15:8] COMPVAL[7:0] |              |  |             |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   | CU                         | MPVAL[15:8]  |  |             |  |  |

|          |                     | 7:0      | OFFSSTRT[0:<br>0] |                            | OFFSVAL[6:0] |  |             |  |  |

|          |                     |          | 5]                |                            |              |  | OFFSSTRT[1: |  |  |

| 0x0704   | GMAC_ST2CW10        | 15:8     |                   |                            |              |  | 1]          |  |  |

|          |                     | 23:16    |                   |                            |              |  | ·,          |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   | M                          | ASKVAL[7:0]  |  |             |  |  |

|          |                     | 15:8     |                   |                            | SKVAL[15:8]  |  |             |  |  |

| 0x0708   | GMAC_ST2CW01        | 23:16    |                   |                            | DMPVAL[7:0]  |  |             |  |  |

|          |                     | 31:24    |                   |                            | MPVAL[15:8]  |  |             |  |  |

|          |                     | 0.1.2.1  | OFFSSTRT[0:       |                            |              |  |             |  |  |

|          |                     | 7:0      | 0]                |                            | OFFSVAL[6:0] |  |             |  |  |

|          |                     |          |                   |                            |              |  | OFFSSTRT[1: |  |  |

| 0x070C   | GMAC_ST2CW11        | 15:8     |                   |                            |              |  | 1]          |  |  |

|          |                     | 23:16    |                   |                            |              |  |             |  |  |

|          |                     | 31:24    |                   |                            |              |  |             |  |  |

|          |                     | 7:0      |                   | M                          | ASKVAL[7:0]  |  |             |  |  |

|          |                     | 15:8     |                   |                            | SKVAL[15:8]  |  |             |  |  |

| 0x0710   | GMAC_ST2CW02        | 23:16    |                   |                            | DMPVAL[7:0]  |  |             |  |  |

|          |                     | 31:24    |                   |                            | MPVAL[15:8]  |  |             |  |  |

|          |                     |          | OFFSSTRT[0:       |                            |              |  |             |  |  |

| 0x0714   | GMAC_ST2CW12        | 7:0      | 0]                |                            | OFFSVAL[6:0] |  |             |  |  |

|          |                     |          | 1                 |                            |              |  |             |  |  |

#### 38.8.26 GMAC IPG Stretch Register

| Name:<br>Offset:<br>Reset:<br>Property: |     | GMAC_IPGS<br>0x0BC<br>0x00000000<br>- |     |      |      |     |     |     |

|-----------------------------------------|-----|---------------------------------------|-----|------|------|-----|-----|-----|

| Bit                                     | 31  | 30                                    | 29  | 28   | 27   | 26  | 25  | 24  |

|                                         |     |                                       |     |      |      |     |     |     |

| Access                                  |     |                                       |     |      |      |     |     |     |

| Reset                                   |     |                                       |     |      |      |     |     |     |

| Dit                                     | 00  | 00                                    | 04  | 00   | 10   | 10  | 47  | 10  |

| Bit                                     | 23  | 22                                    | 21  | 20   | 19   | 18  | 17  | 16  |

| Access                                  |     |                                       |     |      |      |     |     |     |

| Reset                                   |     |                                       |     |      |      |     |     |     |

| Reset                                   |     |                                       |     |      |      |     |     |     |

| Bit                                     | 15  | 14                                    | 13  | 12   | 11   | 10  | 9   | 8   |

|                                         |     |                                       |     | FL[1 | 5:8] |     |     |     |

| Access                                  | R/W | R/W                                   | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset                                   | 0   | 0                                     | 0   | 0    | 0    | 0   | 0   | 0   |

|                                         |     |                                       |     |      |      |     |     |     |

| Bit                                     | 7   | 6                                     | 5   | 4    | 3    | 2   | 1   | 0   |

|                                         |     |                                       |     | FL[  | 7:0] |     |     |     |

| Access                                  | R/W | R/W                                   | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset                                   | 0   | 0                                     | 0   | 0    | 0    | 0   | 0   | 0   |

### Bits 15:0 - FL[15:0] Frame Length

Bits FL[7:0] are multiplied with the previously transmitted frame length (including preamble), and divided by FL[15:8]+1 (adding 1 to prevent division by zero). RESULT =  $\frac{FL[7:0]}{F[15+8]+1}$

If RESULT > 96 and the IP Stretch Enable bit in the Network Configuration Register (GMAC\_NCFGR.IPGSEN) is written to '1', RESULT is used for the transmit inter-packet-gap.

## USB High-Speed Interface (USBHS)

| Offset | Name                            | Bit Pos. |                    |            |          |           |        |           |          |           |

|--------|---------------------------------|----------|--------------------|------------|----------|-----------|--------|-----------|----------|-----------|

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        | USBHS_HSTPIPID<br>R0 (INTPIPES) | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0620 |                                 | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        |                                 | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        | USBHS_HSTPIPID                  | 7:0      | SHORTPACK<br>ETIEC | CRCERREC   | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0620 | R0 (ISOPIPES)                   | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        |                                 | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        | USBHS_HSTPIPID                  | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | TXSTPEC   | TXOUTEC  | RXINEC    |

| 0x0624 | R1                              | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        |                                 | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        |                                 | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0624 | USBHS_HSTPIPID                  | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        | R1 (INTPIPES)                   | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        | USBHS_HSTPIPID<br>R1 (ISOPIPES) | 7:0      | SHORTPACK<br>ETIEC | CRCERREC   | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0624 |                                 | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        |                                 | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        |                                 | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | TXSTPEC   | TXOUTEC  | RXINEC    |

| 0x0628 | USBHS_HSTPIPID                  | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        | R2                              | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        |                                 | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0628 | USBHS_HSTPIPID<br>R2 (INTPIPES) | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        |                                 | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        |                                 | 7:0      | SHORTPACK<br>ETIEC | CRCERREC   | OVERFIEC | NAKEDEC   | PERREC | UNDERFIEC | TXOUTEC  | RXINEC    |

| 0x0628 | USBHS_HSTPIPID                  | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        | R2 (ISOPIPES)                   | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

|        |                                 | 7:0      | SHORTPACK<br>ETIEC | RXSTALLDEC | OVERFIEC | NAKEDEC   | PERREC | TXSTPEC   | TXOUTEC  | RXINEC    |

| 0x062C | USBHS_HSTPIPID                  | 15:8     |                    | FIFOCONC   |          | NBUSYBKEC |        |           |          |           |

|        | R3                              | 23:16    |                    |            |          |           |        |           | PFREEZEC | PDISHDMAC |

|        |                                 | 31:24    |                    |            |          |           |        |           |          |           |

#### 40.14.12 HSMCI Status Register

| Name:     | HSMCI_SR  |

|-----------|-----------|

| Offset:   | 0x40      |

| Reset:    | 0xC0E5    |

| Property: | Read-only |

| Bit    | 31    | 30   | 29      | 28       | 27      | 26        | 25    | 24       |

|--------|-------|------|---------|----------|---------|-----------|-------|----------|

|        | UNRE  | OVRE | ACKRCVE | ACKRCV   | XFRDONE | FIFOEMPTY |       | BLKOVRE  |

| Access |       |      |         |          |         |           |       |          |

| Reset  | 0     | 0    | 0       | 0        | 0       | 0         |       | 0        |

|        |       |      |         |          |         |           |       |          |

| Bit    | 23    | 22   | 21      | 20       | 19      | 18        | 17    | 16       |

|        | CSTOE | DTOE | DCRCE   | RTOE     | RENDE   | RCRCE     | RDIRE | RINDE    |

| Access |       |      |         |          |         |           |       |          |

| Reset  | 0     | 0    | 0       | 0        | 0       | 0         | 0     | 0        |

|        |       |      |         |          |         |           |       |          |

| Bit    | 15    | 14   | 13      | 12       | 11      | 10        | 9     | 8        |

|        |       |      | CSRCV   | SDIOWAIT |         |           |       | SDIOIRQA |

| Access |       |      |         |          |         |           |       |          |

| Reset  |       |      | 0       | 0        |         |           |       | 0        |

|        |       |      |         |          |         |           |       |          |

| Bit    | 7     | 6    | 5       | 4        | 3       | 2         | 1     | 0        |

|        |       |      | NOTBUSY | DTIP     | BLKE    | TXRDY     | RXRDY | CMDRDY   |

| Access |       |      |         |          |         |           |       |          |

| Reset  |       |      | 1       | 0        | 0       | 1         | 0     | 1        |

**Bit 31 – UNRE** Underrun (if FERRCTRL = 1, cleared by writing in HSMCI\_CMDR or cleared on read if FERRCTRL = 0)

If FERRCTRL = 1 in HSMCI\_CFG, OVRE is cleared on read.

If FERRCTRL = 0 in HSMCI\_CFG, OVRE is cleared by writing HSMCI\_CMDR.

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | No error.                                                                      |

| 1     | At least one 8-bit data has been sent without valid information (not written). |

**Bit 30 – OVRE** Overrun (if FERRCTRL = 1, cleared by writing in HSMCI\_CMDR or cleared on read if FERRCTRL = 0)

If FERRCTRL = 1 in HSMCI\_CFG, OVRE is cleared on read.

If FERRCTRL = 0 in HSMCI\_CFG, OVRE is cleared by writing HSMCI\_CMDR.

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | No error.                                                  |

| 1     | At least one 8-bit received data has been lost (not read). |

**Bit 29 – ACKRCVE** Boot Operation Acknowledge Error (cleared on read)

## **Quad Serial Peripheral Interface (QSPI)**

| Name:<br>Offset:<br>Reset:<br>Property: |    | QSPI_TDR<br>0x0C<br>–<br>Write-only |    |      |       |    |    |    |

|-----------------------------------------|----|-------------------------------------|----|------|-------|----|----|----|

| Bit                                     | 31 | 30                                  | 29 | 28   | 27    | 26 | 25 | 24 |

|                                         |    |                                     |    |      |       |    |    |    |

| Access                                  |    |                                     |    |      |       |    |    |    |

| Reset                                   |    |                                     |    |      |       |    |    |    |

| Bit                                     | 23 | 22                                  | 21 | 20   | 19    | 18 | 17 | 16 |

|                                         |    |                                     |    |      |       |    |    |    |

| Access                                  |    |                                     |    |      |       |    |    |    |

| Reset                                   |    |                                     |    |      |       |    |    |    |

| Bit                                     | 15 | 14                                  | 13 | 12   | 11    | 10 | 9  | 8  |

|                                         |    |                                     |    | TD[′ | 15:8] |    |    |    |

| Access                                  | W  | W                                   | W  | W    | W     | W  | W  | W  |

| Reset                                   | 0  | 0                                   | 0  | 0    | 0     | 0  | 0  | 0  |

|                                         |    |                                     |    |      |       |    |    |    |

| Bit                                     | 7  | 6                                   | 5  | 4    | 3     | 2  | 1  | 0  |

|                                         |    |                                     |    | TD[  | 7:0]  |    |    |    |

| Access                                  | W  | W                                   | W  | W    | W     | W  | W  | W  |

| Reset                                   | 0  | 0                                   | 0  | 0    | 0     | 0  | 0  | -  |

#### 42.7.4 QSPI Transmit Data Register

### Bits 15:0 - TD[15:0] Transmit Data

Data to be transmitted by the QSPI is stored in this register. Information to be transmitted must be written to the Transmit Data register in a right-justified format.

#### 43.7.9 TWIHS Interrupt Enable Register

Name:TWIHS\_IEROffset:0x24Reset:-Property:Write-only

The following configuration values are valid for all listed bit names of this register:

0: No effect.

1: Enables the corresponding interrupt.

| Bit    | 31   | 30   | 29     | 28     | 27     | 26     | 25     | 24     |

|--------|------|------|--------|--------|--------|--------|--------|--------|

|        |      |      |        |        |        |        |        |        |

| Access |      |      |        |        |        |        |        |        |

| Reset  |      |      |        |        |        |        |        |        |

|        |      |      |        |        |        |        |        |        |

| Bit    | 23   | 22   | 21     | 20     | 19     | 18     | 17     | 16     |

|        |      |      | SMBHHM | SMBDAM | PECERR | TOUT   |        | MCACK  |

| Access |      |      | W      | W      | W      | W      |        | W      |

| Reset  |      |      | -      | -      | -      | -      |        | -      |

|        |      |      |        |        |        |        |        |        |

| Bit    | 15   | 14   | 13     | 12     | 11     | 10     | 9      | 8      |

|        |      |      |        |        | EOSACC | SCL_WS | ARBLST | NACK   |

| Access |      |      |        |        | W      | W      | W      | W      |

| Reset  |      |      |        |        | -      | -      | _      | _      |

|        |      |      |        |        |        |        |        |        |

| Bit    | 7    | 6    | 5      | 4      | 3      | 2      | 1      | 0      |

|        | UNRE | OVRE | GACC   | SVACC  |        | TXRDY  | RXRDY  | TXCOMP |

| Access | W    | W    | W      | W      |        | W      | W      | W      |

| Reset  | _    | -    | _      | _      |        | -      | _      | _      |

Bit 21 – SMBHHM SMBus Host Header Address Match Interrupt Enable

Bit 20 – SMBDAM SMBus Default Address Match Interrupt Enable

- Bit 19 PECERR PEC Error Interrupt Enable

- **Bit 18 TOUT** Timeout Error Interrupt Enable

- Bit 16 MCACK Master Code Acknowledge Interrupt Enable

- Bit 11 EOSACC End Of Slave Access Interrupt Enable

- Bit 10 SCL\_WS Clock Wait State Interrupt Enable

- Bit 9 ARBLST Arbitration Lost Interrupt Enable

- Bit 8 NACK Not Acknowledge Interrupt Enable

## Inter-IC Sound Controller (I2SC)

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                       |

| 1     | Writing a zone to this bit disables the I2SC clock generation. |

#### Bit 2 – CKEN Clocks Enable

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                                           |

| 1     | Writing a '1' to this bit enables the I2SC clocks generation, if CKDIS is not one. |

#### Bit 1 – RXDIS Receiver Disable

| Value | Description                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                                                                        |

| 1     | Writing a '1' to this bit disables the I2SC receiver. Bit I2SC_SR.RXEN is cleared when the receiver is stopped. |

#### Bit 0 – RXEN Receiver Enable

| Value | Description                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0     | Writing a '0' to this bit has no effect.                                                                                          |

| 1     | Writing a '1' to this bit enables the I2SC receiver, if RXDIS is not one. Bit I2SC_SR.RXEN is set when the receiver is activated. |

**Controller Area Network (MCAN)**

| _      |            |              |            |             |      |        |           |                          |      |      |  |  |

|--------|------------|--------------|------------|-------------|------|--------|-----------|--------------------------|------|------|--|--|

| Offset | Name       | Bit Pos.     |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            |             | FLSS | A[5:0] |           |                          |      |      |  |  |

| 0x84   | MCAN_SIDFC | 15:8         |            | FLSSA[13:6] |      |        |           |                          |      |      |  |  |

| 0,04   |            | 23:16        |            | LSS[7:0]    |      |        |           |                          |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            |             | FLES | A[5:0] |           |                          |      |      |  |  |

| 0x88   | MCAN_XIDFC | 15:8         |            | FLESA[13:6] |      |        |           |                          |      |      |  |  |

| 0x00   |            | 23:16        |            |             |      |        | LSE[6:0]  |                          |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

| 0x8C   |            |              |            |             |      |        |           |                          |      |      |  |  |

|        | Reserved   |              |            |             |      |        |           |                          |      |      |  |  |

| 0x8F   |            |              |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            |             |      |        | Л[7:0]    |                          |      |      |  |  |

| 0x90   | MCAN XIDAM | 15:8         |            |             |      |        | I[15:8]   |                          |      |      |  |  |

|        | _          | 23:16        |            |             | 1    | EIDM   | [23:16]   | EIDM[28:24]<br>BIDX[5:0] |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            | [1:0]       |      |        |           | <[5:0]                   |      |      |  |  |

| 0x94   | MCAN_HPMS  | 15:8         | FLST       |             |      |        | FIDX[6:0] |                          |      |      |  |  |

|        |            | 23:16        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

|        | MCAN_NDAT1 | 7:0          | ND7        | ND6         | ND5  | ND4    | ND3       | ND2                      | ND1  | ND0  |  |  |

| 0x98   |            | 15:8         | ND15       | ND14        | ND13 | ND12   | ND11      | ND10                     | ND9  | ND8  |  |  |

|        |            | 23:16        | ND23       | ND22        | ND21 | ND20   | ND19      | ND18                     | ND17 | ND16 |  |  |

|        |            | 31:24        | ND31       | ND30        | ND29 | ND28   | ND27      | ND26                     | ND25 | ND24 |  |  |

|        |            | 7:0          | ND39       | ND38        | ND37 | ND36   | ND35      | ND34                     | ND33 | ND32 |  |  |

| 0x9C   | MCAN_NDAT2 | 15:8         | ND47       | ND46        | ND45 | ND44   | ND43      | ND42                     | ND41 | ND40 |  |  |

|        |            | 23:16        | ND55       | ND54        | ND53 | ND52   | ND51      | ND50                     | ND49 | ND48 |  |  |

|        |            | 31:24        | ND63       | ND62        | ND61 | ND60   | ND59      | ND58                     | ND57 | ND56 |  |  |

|        |            | 7:0          | F0SA[5:0]  |             |      |        |           |                          |      |      |  |  |

| 0xA0   | MCAN_RXF0C | 15:8         | F0SA[13:6] |             |      |        |           |                          |      |      |  |  |

|        |            | 23:16        |            | F0S[6:0]    |      |        |           |                          |      |      |  |  |

|        |            | 31:24        | F0OM       |             |      |        | F0WM[6:0] |                          |      |      |  |  |

|        |            | 7:0<br>15:8  |            |             |      |        | F0FL[6:0] | 1(5.0)                   |      |      |  |  |

| 0xA4   | MCAN_RXF0S |              |            |             |      |        |           | I[5:0]                   |      |      |  |  |

|        |            | 23:16        |            |             |      |        | FUP       | I[5:0]                   | RF0L | F0F  |  |  |

|        |            | 31:24<br>7:0 |            |             |      |        | EOA       | 1(5:0)                   | REUL | FUF  |  |  |

|        |            | 15:8         |            |             |      |        | FUA       | I[5:0]                   |      |      |  |  |

| 0xA8   | MCAN_RXF0A | 23:16        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            |             | RBC  | A[5:0] |           |                          |      |      |  |  |

|        |            | 15:8         |            |             | 100  |        | A[13:6]   |                          |      |      |  |  |

| 0xAC   | MCAN_RXBC  | 23:16        |            |             |      | ND3F   | ų io.oj   |                          |      |      |  |  |

|        |            | 31:24        |            |             |      |        |           |                          |      |      |  |  |

|        |            | 7:0          |            |             | F19  | A[5:0] |           |                          |      |      |  |  |

| 0xB0   | MCAN_RXF1C | 15:8         |            |             | 110/ |        | [13:6]    |                          |      |      |  |  |

| 0,00   |            | 23:16        |            |             |      | 1134   | F1S[6:0]  |                          |      |      |  |  |

|        |            | 20.10        |            |             |      |        | 1 10[0.0] |                          |      |      |  |  |

## **Controller Area Network (MCAN)**

#### 49.6.35 MCAN Tx Buffer Configuration

| Name:     | MCAN_TXBC  |

|-----------|------------|

| Offset:   | 0xC0       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the bits CCE and INIT are set in MCAN CC Control Register.

The sum of TFQS and NDTB may not exceed 32. There is no check for erroneous configurations. The Tx Buffers section in the Message RAM starts with the dedicated Tx Buffers.

| Bit    | 31  | 30   | 29  | 28     | 27     | 26     | 25  | 24  |

|--------|-----|------|-----|--------|--------|--------|-----|-----|

|        |     | TFQM |     |        | TFQS   | S[5:0] |     |     |

| Access |     | R/W  | R/W | R/W    | R/W    | R/W    | R/W | R/W |

| Reset  |     | 0    | 0   | 0      | 0      | 0      | 0   | 0   |

|        |     |      |     |        |        |        |     |     |

| Bit    | 23  | 22   | 21  | 20     | 19     | 18     | 17  | 16  |

|        |     |      |     |        | NDTE   | B[5:0] |     |     |

| Access |     |      | R/W | R/W    | R/W    | R/W    | R/W | R/W |

| Reset  |     |      | 0   | 0      | 0      | 0      | 0   | 0   |

|        |     |      |     |        |        |        |     |     |

| Bit    | 15  | 14   | 13  | 12     | 11     | 10     | 9   | 8   |

|        |     |      |     | TBSA   | [13:6] |        |     |     |

| Access | R/W | R/W  | R/W | R/W    | R/W    | R/W    | R/W | R/W |

| Reset  | 0   | 0    | 0   | 0      | 0      | 0      | 0   | 0   |

|        |     |      |     |        |        |        |     |     |

| Bit    | 7   | 6    | 5   | 4      | 3      | 2      | 1   | 0   |

|        |     |      | TBS | A[5:0] |        |        |     |     |

| Access | R/W | R/W  | R/W | R/W    | R/W    | R/W    |     |     |

| Reset  | 0   | 0    | 0   | 0      | 0      | 0      |     |     |

#### Bit 30 – TFQM Tx FIFO/Queue Mode

| Value | Description         |

|-------|---------------------|

| 0     | Tx FIFO operation.  |

| 1     | Tx Queue operation. |

#### Bits 29:24 - TFQS[5:0] Transmit FIFO/Queue Size

| Value | Description                                   |  |

|-------|-----------------------------------------------|--|

| 0     | No Tx FIFO/Queue.                             |  |

| 1-32  | Number of Tx Buffers used for Tx FIFO/Queue.  |  |

| >32   | Values greater than 32 are interpreted as 32. |  |

#### Bits 21:16 - NDTB[5:0] Number of Dedicated Transmit Buffers

| Value | Description                                   |  |

|-------|-----------------------------------------------|--|

| 0     | No dedicated Tx Buffers.                      |  |

| 1-32  | lumber of dedicated Tx Buffers.               |  |

| >32   | Values greater than 32 are interpreted as 32. |  |

## **Timer Counter (TC)**

| Value | Name      | Description                                         |

|-------|-----------|-----------------------------------------------------|

| 0     | UP        | UP mode without automatic trigger on RC Compare     |

| 1     | UPDOWN    | UPDOWN mode without automatic trigger on RC Compare |

| 2     | UP_RC     | UP mode with automatic trigger on RC Compare        |

| 3     | UPDOWN_RC | UPDOWN mode with automatic trigger on RC Compare    |

#### Bit 12 – ENETRG External Event Trigger Enable

Whatever the value programmed in ENETRG, the selected external event only controls the TIOAx output and TIOBx if not used as input (trigger event input or other input used).

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The external event has no effect on the counter and its clock.      |

| 1     | The external event resets the counter and starts the counter clock. |

#### Bits 11:10 – EEVT[1:0] External Event Selection

Signal selected as external event.

| Value | Name | Description | TIOB Direction |

|-------|------|-------------|----------------|

| 0     | TIOB | TIOB        | Input          |

| 1     | XC0  | XC0         | Output         |

| 2     | XC1  | XC1         | Output         |

| 3     | XC2  | XC2         | Output         |

**Note:** If TIOB is chosen as the external event signal, it is configured as an input and no longer generates waveforms and subsequently no IRQs.

#### Bits 9:8 – EEVTEDG[1:0] External Event Edge Selection

| Value | Name    | Description  |

|-------|---------|--------------|

| 0     | NONE    | None         |

| 1     | RISING  | Rising edge  |

| 2     | FALLING | Falling edge |

| 3     | EDGE    | Each edge    |

**Bit 7 – CPCDIS** Counter Clock Disable with RC Compare

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Counter clock is not disabled when counter reaches RC. |

| 1     | Counter clock is disabled when counter reaches RC.     |

#### **Bit 6 – CPCSTOP** Counter Clock Stopped with RC Compare

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Counter clock is not stopped when counter reaches RC. |

| 1     | Counter clock is stopped when counter reaches RC.     |

Bits 5:4 – BURST[1:0] Burst Signal Selection

## Pulse Width Modulation Controller (PWM)

#### 51.7.25 PWM Fault Status Register

| Name:     | PWM_FSR    |  |  |

|-----------|------------|--|--|

| Offset:   | 0x60       |  |  |

| Reset:    | 0x00000000 |  |  |

| Property: | Read-only  |  |  |

#### Refer to Fault Inputs for details on fault generation.

| Bit    | 31 | 30 | 29 | 28  | 27    | 26 | 25 | 24 |

|--------|----|----|----|-----|-------|----|----|----|

|        |    |    |    |     |       |    |    |    |

| Access |    |    |    |     |       |    |    |    |

| Reset  |    |    |    |     |       |    |    |    |

|        |    |    |    |     |       |    |    |    |

| Bit    | 23 | 22 | 21 | 20  | 19    | 18 | 17 | 16 |

|        |    |    |    |     |       |    |    |    |

| Access |    |    |    |     |       |    |    |    |

| Reset  |    |    |    |     |       |    |    |    |

|        |    |    |    |     |       |    |    |    |

| Bit    | 15 | 14 | 13 | 12  | 11    | 10 | 9  | 8  |

|        |    |    |    | FS[ | 7:0]  |    |    |    |

| Access | R  | R  | R  | R   | R     | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0   | 0     | 0  | 0  | 0  |

|        |    |    |    |     |       |    |    |    |

| Bit    | 7  | 6  | 5  | 4   | 3     | 2  | 1  | 0  |

|        |    |    |    | FIV | [7:0] |    |    |    |

| Access | R  | R  | R  | R   | R     | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0   | 0     | 0  | 0  | 0  |

#### Bits 15:8 - FS[7:0] Fault Status

For each bit y of FS, where y is the fault input number:

0: The fault y is not currently active.

1: The fault y is currently active.

#### Bits 7:0 - FIV[7:0] Fault Input Value

For each bit y of FIV, where y is the fault input number:

0: The current sampled value of the fault input y is 0 (after filtering if enabled).

1: The current sampled value of the fault input y is 1 (after filtering if enabled).

not fully deactivated while no conversion is requested, thereby providing lower power savings but faster wakeup.

The conversion sequencer allows automatic processing with minimum processor intervention and optimized power consumption. Conversion sequences are performed periodically using a Timer/Counter output or the PWM event line.

The DMA can automatically process the periodic acquisition of several samples without processor intervention.

The sequence can be customized by programming the Channel Sequence registers AFEC\_SEQ1R and AFEC\_SEQ2R and setting AFEC\_MR.USEQ. The user selects a specific order of channels and can program up to 12 conversions by sequence. The user may create a personal sequence by writing channel numbers in AFEC\_SEQ1R and AFEC\_SEQ2R. Channel numbers can be written in any order and repeated several times. Only enabled USCHx fields are converted. Thus, to program a 15-conversion sequence, the user disables AFEC\_CHSR.CH15, thus disabling AFEC\_SEQ2R.USCH15.

Note: The reference voltage pins always remain connected in Normal mode as in Sleep mode.

#### **Related Links**

58. Electrical Characteristics for SAM V70/V71

#### 52.6.8 Comparison Window

The AFEC features automatic comparison functions. It compares converted values to a low threshold, a high threshold or both, depending on the value of AFEC\_EMR.CMPMODE. The comparison can be done on all channels or only on the channel specified in AFEC\_EMR.CMPSEL. To compare all channels, AFEC\_EMR.CMPALL must be set.

Moreover, a filtering option can be set by writing the number of consecutive comparison errors needed to raise the flag. This number can be written and read in AFEC\_EMR.CMPFILTER.

The flag can be read on AFEC\_ISR.COMPE and can trigger an interrupt.

The high threshold and the low threshold can be read/written in the Compare Window Register (AFEC\_CWR).

Depending on the sign of the conversion, chosen by setting the SIGNMODE bit in the AFEC Extended Mode Register, the high threshold and low threshold values must be signed or unsigned to maintain consistency during the comparison. If the conversion is signed, both thresholds must also be signed; if the conversion is unsigned, both thresholds must be unsigned. If comparison occurs on all channels, the SIGNMODE bit must be set to ALL\_UNSIGNED or ALL\_SIGNED and thresholds must be set accordingly.

#### 52.6.9 Differential Inputs

The AFE can be used either as a single-ended AFE (AFEC\_DIFFR.DIFF = 0) or as a fully differential AFE (AFEC\_DIFFR.DIFF = 1). By default, after a reset, the AFE is in Single-ended mode.

The AFEC can apply a different mode on each channel.

The same inputs are used in Single-ended or Differential mode.

Depending on the AFE mode, the analog multiplexer selects one or two inputs to map to a channel. The table below provides input mapping for both modes.

## Analog Front-End Controller (AFEC)

| V | /alue | Description                                                       |  |

|---|-------|-------------------------------------------------------------------|--|

| 0 |       | Clears CHNB in AFEC_LCDR.                                         |  |

| 1 |       | Appends the channel number to the conversion result in AFEC_LCDR. |  |

#### Bits 18:16 - RES[2:0] Resolution

| Value | Name       | Description                                                    |

|-------|------------|----------------------------------------------------------------|

| 0     | NO_AVERAGE | 12-bit resolution, AFE sample rate is maximum (no averaging).  |

| 1     | LOW_RES    | 10-bit resolution, AFE sample rate is maximum (no averaging).  |

| 2     | OSR4       | 13-bit resolution, AFE sample rate divided by 4 (averaging).   |

| 3     | OSR16      | 14-bit resolution, AFE sample rate divided by 16 (averaging).  |

| 4     | OSR64      | 15-bit resolution, AFE sample rate divided by 64 (averaging).  |

| 5     | OSR256     | 16-bit resolution, AFE sample rate divided by 256 (averaging). |

#### Bits 13:12 - CMPFILTER[1:0] Compare Event Filtering

Number of consecutive compare events necessary to raise the flag = CMPFILTER+1.

When programmed to '0', the flag rises as soon as an event occurs.

#### Bit 9 – CMPALL Compare All Channels

| Value | Description                                             |  |  |

|-------|---------------------------------------------------------|--|--|

| 0     | Only the channel indicated in CMPSEL field is compared. |  |  |

| 1     | All channels are compared.                              |  |  |

#### Bits 7:3 – CMPSEL[4:0] Comparison Selected Channel

If CMPALL = 0: CMPSEL indicates which channel has to be compared.

If CMPALL = 1: No effect.

#### Bits 1:0 – CMPMODE[1:0] Comparison Mode

| Value | Name | Description                                                                                 |

|-------|------|---------------------------------------------------------------------------------------------|

| 0     | LOW  | Generates an event when the converted data is lower than the low threshold of the window.   |

| 1     | HIGH | Generates an event when the converted data is higher than the high threshold of the window. |

| 2     | IN   | Generates an event when the converted data is in the comparison window.                     |

| 3     | OUT  | Generates an event when the converted data is out of the comparison window.                 |

# 53. Digital-to-Analog Converter Controller (DACC)

### 53.1 Description

The Digital-to-Analog Converter Controller (DACC) offers up to two single-ended analog outputs or one differential analog output, making it possible for the digital-to-analog conversion to drive up to two independent analog lines.

The DACC supports 12-bit resolution.

The DACC operates in Free-running mode, Max speed mode, Trigger mode or Interpolation mode.

The DACC integrates a Bypass mode which minimizes power consumption in case of a limited sampling rate conversion.

Each channel connects with a separate DMA channel. This feature reduces both power consumption and processor intervention.

### 53.2 Embedded Characteristics

- Up to Two Independent Single-Ended Analog Outputs or One Differential Analog Output

- 12-bit Resolution

- Integrated Interpolation Filter with 2×, 4×, 8×, 16× or 32× Oversampling Ratio (OSR)

- Reduced Number of System Bus Accesses (Word Transfer Mode)

- Individual Control of Each Analog Channel

- Hardware Triggers

- One Trigger Selection Per Channel

- External trigger pin

- Internal events

- DMA Support

- One Internal FIFO per Channel

- Register Write Protection