#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | ARM® Cortex®-M7                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 300MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 114                                                                              |

| Program Memory Size        | 1MB (1M × 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 384K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-UFBGA                                                                        |

| Supplier Device Package    | 144-UFBGA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70q20a-cfnt      |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Low-Power Features

- Low-power Sleep, Wait and Backup modes, with typical power consumption down to 1.1 μA in Backup mode with RTC, RTT and wakeup logic enabled

- Ultra low-power RTC and RTT

- 1 Kbyte of backup RAM (BRAM) with dedicated regulator

## Peripherals

- One Ethernet MAC (GMAC) 10/100 Mbps in MII mode and RMII with dedicated DMA. IEEE1588 PTP frames and 802.3az Energy-efficiency support. Ethernet AVB support with IEEE802.1AS Timestamping and IEEE802.1Qav credit-based traffic-shaping hardware support.

- USB 2.0 Device/Mini Host High-speed (USBHS) at 480 Mbps, 4-Kbyte FIFO, up to 10 bidirectional endpoints, dedicated DMA

- 12-bit ITU-R BT. 601/656 Image Sensor Interface (ISI)

- Two master Controller Area Networks (MCAN) with Flexible Data Rate (CAN-FD) with SRAM-based mailboxes, time- and event-triggered transmission

- MediaLB<sup>®</sup> device with 3-wire mode, up to 1024 x Fs speed, supporting MOST25 and MOST50 networks

- Three USARTs. USART0/1/2 support LIN mode, ISO7816, IrDA<sup>®</sup>, RS-485, SPI, Manchester and Modem modes; USART1 supports LON mode.

- Five 2-wire UARTs with SleepWalking<sup>™</sup> support

- Three Two-Wire Interfaces (TWIHS) (I<sup>2</sup>C-compatible) with SleepWalking support

- Quad I/O Serial Peripheral Interface (QSPI) interfacing up to 256 MB Flash and with eXecute-In-Place and on-the-fly scrambling

- Two Serial Peripheral Interfaces (SPI)

- One Serial Synchronous Controller (SSC) with I<sup>2</sup>S and TDM support

- Two Inter-IC Sound Controllers (I2SC)

- One High-speed Multimedia Card Interface (HSMCI) (SDIO/SD Card/e.MMC)

- Four Three-Channel 16-bit Timer/Counters (TC) with Capture, Waveform, Compare and PWM modes, constant on time. Quadrature decoder logic and 2-bit Gray Up/Down Counter for stepper motor

- Two 4-channel 16-bit PWMs with complementary outputs, Dead Time Generator and eight fault inputs per PWM for motor control, two external triggers to manage power factor correction (PFC), DC-DC and lighting control.

- Two Analog Front-End Controllers (AFEC), each supporting up to 12 channels with differential input mode and programmable gain stage, allowing dual sample-and-hold at up to 1.7 Msps. Offset and gain error correction feature.

- One 2-channel 12-bit 1 Msps-per-channel Digital-to-Analog Controller (DAC) with Differential and Over Sampling modes

- One Analog Comparator Controller (ACC) with flexible input selection, selectable input hysteresis

## Cryptography

- True Random Number Generator (TRNG)

- AES: 256-, 192-, 128-bit Key Algorithm, Compliant with FIPS PUB-197 Specifications

- Integrity Check Monitor (ICM). Supports Secure Hash Algorithm SHA1, SHA224 and SHA256.

## I/O

- Up to 114 I/O lines with external interrupt capability (edge- or level-sensitivity), debouncing, glitch filtering and On-die Series Resistor Termination

- Five Parallel Input/Output Controllers (PIO)

## **Chip Identifier (CHIPID)**

| Value | Name  | Description |

|-------|-------|-------------|

| 0     | NONE  | None        |

| 1     | 8K    | 8 Kbytes    |

| 2     | 16K   | 16 Kbytes   |

| 3     | 32K   | 32 Kbytes   |

| 4     | -     | Reserved    |

| 5     | 64K   | 64 Kbytes   |

| 6     | -     | Reserved    |

| 7     | 128K  | 128 Kbytes  |

| 8     | 160K  | 160 Kbytes  |

| 9     | 256K  | 256 Kbytes  |

| 10    | 512K  | 512 Kbytes  |

| 11    | -     | Reserved    |

| 12    | 1024K | 1024 Kbytes |

| 13    | -     | Reserved    |

| 14    | 2048K | 2048 Kbytes |

| 15    | -     | Reserved    |

## Bits 7:5 – EPROC[2:0] Embedded Processor

| Value | Name      | Description |

|-------|-----------|-------------|

| 0     | SAM x7    | Cortex-M7   |

| 1     | ARM946ES  | ARM946ES    |

| 2     | ARM7TDMI  | ARM7TDMI    |

| 3     | CM3       | Cortex-M3   |

| 4     | ARM920T   | ARM920T     |

| 5     | ARM926EJS | ARM926EJS   |

| 6     | CA5       | Cortex-A5   |

| 7     | CM4       | Cortex-M4   |

Bits 4:0 – VERSION[4:0] Version of the Device

Current version of the device.

## 22. Enhanced Embedded Flash Controller (EEFC)

## 22.1 Description

The Enhanced Embedded Flash Controller (EEFC) provides the interface of the Flash block with the 32bit internal bus.

Its 128-bit wide memory interface increases performance. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands. One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

## 22.2 Embedded Characteristics

- Increases Performance in Thumb-2 Mode with 128-bit-wide Memory Interface up to 150 MHz

- Code Loop Optimization

- 128 Lock Bits, Each Protecting a Lock Region

- 9 General-purpose GPNVM Bits

- One-by-one Lock Bit Programming

- Commands Protected by a Keyword

- Erase the Entire Flash

- Erase by Plane

- Erase by Sector

- Erase by Page

- Provides Unique Identifier

- Provides 512-byte User Signature Area

- Supports Erasing before Programming

- Locking and Unlocking Operations

- ECC Single and Multiple Error Flags Report

- Supports Read of the Calibration Bits

- Register Write Protection

## 22.3 Product Dependencies

## 22.3.1 Power Management

The Enhanced Embedded Flash Controller (EEFC) is continuously clocked. The Power Management Controller has no effect on its behavior.

## 22.3.2 Interrupt Sources

The EEFC interrupt line is connected to the interrupt controller. Using the EEFC interrupt requires the interrupt controller to be programmed first. The EEFC interrupt is generated only if the value of EEFC\_FMR.FRDY is '1'.

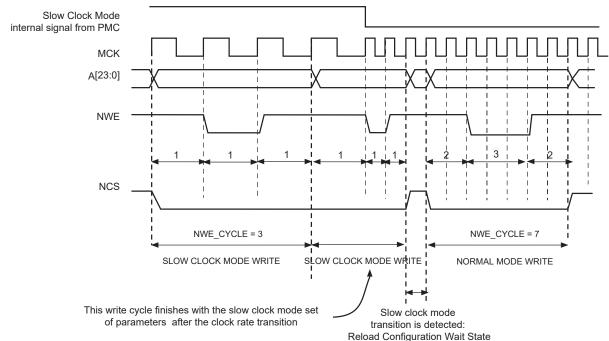

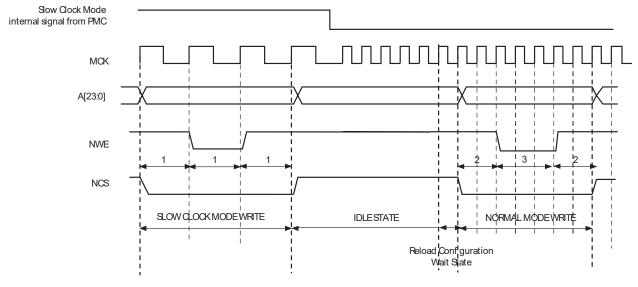

## Static Memory Controller (SMC)

#### Figure 35-33. Clock Rate Transition Occurs while the SMC is Performing a Write Operation

## 35.15 Asynchronous Page Mode

The SMC supports asynchronous burst reads in Page mode, provided that the Page mode is enabled (SMC\_MODE.PMEN =1). The page size must be configured in the SMC\_MODE register (PS field) to 4, 8, 16 or 32 bytes.

The page defines a set of consecutive bytes into memory. A 4-byte page (resp. 8-, 16-, 32-byte page) is always aligned to 4-byte boundaries (resp. 8-, 16-, 32-byte boundaries) of memory. The MSB of data address defines the address of the page in memory, the LSB of address define the address of the data in the page as detailed in the following table.

## Image Sensor Interface (ISI)

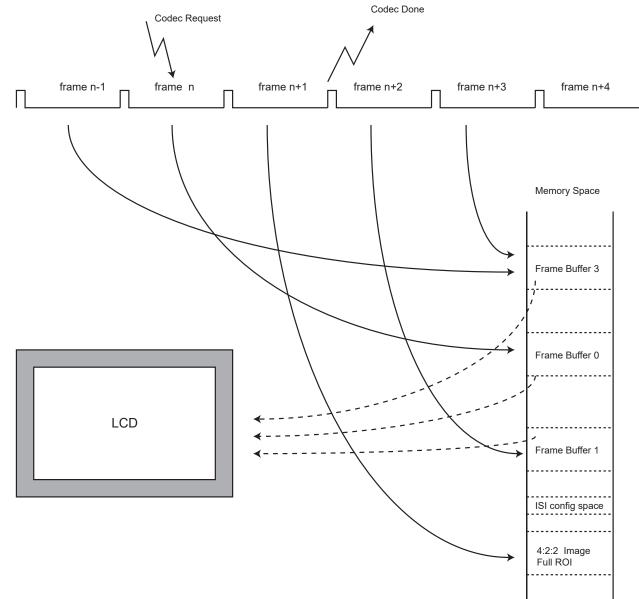

Using this technique, several frame buffers can be configured through the linked list. The following figure illustrates a typical three-frame buffer application. Frame n is mapped to frame buffer 0, frame n+1 is mapped to frame buffer 1, frame n+2 is mapped to frame buffer 2 and further frames wrap. A codec request occurs, and the full-size 4:2:2 encoded frame is stored in a dedicated memory space.

## 37.5.5 Codec Path

## 37.5.5.1 Color Space Conversion

Depending on user selection, this module can be bypassed so that input YCrCb stream is directly connected to the format converter module. If the RGB input stream is selected, this module converts RGB to YCrCb color space with the formulas given below:

## **GMAC - Ethernet MAC**

| Frame Segment                 | Value          |

|-------------------------------|----------------|

| Type (Octets 12–13)           | 86dd           |

| IP stuff (Octets 14–19)       | —              |

| UDP (Octet 20)                | 11             |

| IP stuff (Octets 21–37)       | —              |

| IP DA (Octets 38–53)          | FF0X0000000018 |

| Source IP port (Octets 54–55) | —              |

| Dest IP port (Octets 56–57)   | 013F           |

| Other stuff (Octets 58–61)    | —              |

| Message type (Octet 62)       | 00             |

| Other stuff (Octets 63–93)    |                |

| Version PTP (Octet 94)        | 02             |

## Table 38-11. Example of Pdelay\_Resp Frame in 1588 Version 2 (UDP/IPv6) Format

| Frame Segment                 | Value                                  |

|-------------------------------|----------------------------------------|

| Preamble/SFD                  | 55555555555555555555555555555555555555 |

| DA (Octets 0–5)               | -                                      |

| SA (Octets 6–11)              |                                        |

| Type (Octets 12–13)           | 86dd                                   |

| IP stuff (Octets 14–19)       |                                        |

| UDP (Octet 20)                | 11                                     |

| IP stuff (Octets 21–37)       |                                        |

| IP DA (Octets 38–53)          | FF020000000006B                        |

| Source IP port (Octets 54–55) |                                        |

| Dest IP port (Octets 56–57)   | 013F                                   |

| Other stuff (Octets 58–61)    |                                        |

| Message type (Octet 62)       | 03                                     |

| Other stuff (Octets 63–93)    |                                        |

| Version PTP (Octet 94)        | 02                                     |

For the multicast address 011B19000000 sync and delay request frames are recognized depending on the message type field, 00 for sync and 01 for delay request.

## Bit 12 – RTY Retry Test

This bit must be written to '0' for normal operation.

When writing a '1' to this bit, the back-off between collisions will always be one slot time. This setting helps testing the too many retries condition. This setting is also useful for pause frame tests by reducing the pause counter's decrement time from "512 bit times" to "every GRXCK cycle".

### Bit 8 – MAXFS 1536 Maximum Frame Size

Writing a '1' to this bit increases the maximum accepted frame size to 1536 bytes in length. When written to '0', any frame above 1518 bytes in length is rejected.

### Bit 7 – UNIHEN Unicast Hash Enable

When writing a '1' to this bit, unicast frames will be accepted when the 6-bit hash function of the destination address points to a bit that is set in the Hash Register.

Writing a '0' to this bit disables unicast hashing.

#### Bit 6 - MTIHEN Multicast Hash Enable

When writing a '1' to this bit, multicast frames will be accepted when the 6-bit hash function of the destination address points to a bit that is set in the Hash Register.

Writing a '0' to this bit disables multicast hashing.

#### Bit 5 – NBC No Broadcast

Writing a '0' to this bit allows broadcasting to 0xFFFFFFFFFFF.

#### Bit 4 – CAF Copy All Frames

When writing a '1' to this bit, all valid frames will be accepted.

#### Bit 3 – JFRAME Jumbo Frame Size

Writing a '1' to this bit enables jumbo frames of up to 10240 bytes to be accepted. The default length is 10240 bytes.

#### Bit 2 – DNVLAN Discard Non-VLAN Frames

Writing a '1' to this bit allows only VLAN-tagged frames to pass to the address matching logic.

Writing a '0' to this bit allows both VLAN\_tagged and untagged frames to pass to the address matching logic.

### Bit 1 – FD Full Duplex

Writing a '1' enables full duplex operation, so the transmit block ignores the state of collision and carrier sense and allows receive while transmitting.

Writing a '0' disables full duplex operation.

#### Bit 0 - SPD Speed

Writing a '1' selects 100Mbps operation.

Writing a '0' to this bit selects 10Mbps operation.

## USB High-Speed Interface (USBHS)

#### 39.6.35 Host Global Interrupt Mask Register

|        | Name:<br>Offset:<br>Reset:<br>Property: | USBHS_HST<br>0x0410<br>0x00000000<br>Read-only | IMR    |         |         |       |         |         |

|--------|-----------------------------------------|------------------------------------------------|--------|---------|---------|-------|---------|---------|

| Bit    | 31                                      | 30                                             | 29     | 28      | 27      | 26    | 25      | 24      |

|        | DMA_6                                   | DMA_5                                          | DMA_4  | DMA_3   | DMA_2   | DMA_1 | DMA_0   |         |

| Access |                                         |                                                |        |         |         |       |         |         |

| Reset  | 0                                       | 0                                              | 0      | 0       | 0       | 0     | 0       |         |

|        |                                         |                                                |        |         |         |       |         |         |

| Bit    | 23                                      | 22                                             | 21     | 20      | 19      | 18    | 17      | 16      |

|        |                                         |                                                |        |         |         |       | PEP_9   | PEP_8   |

| Access |                                         |                                                |        |         |         |       |         |         |

| Reset  |                                         |                                                |        |         |         |       | 0       | 0       |

|        |                                         |                                                |        |         |         |       |         |         |

| Bit    |                                         | 14                                             | 13     | 12      | 11      | 10    | 9       | 8       |

|        | PEP_7                                   | PEP_6                                          | PEP_5  | PEP_4   | PEP_3   | PEP_2 | PEP_1   | PEP_0   |

| Access |                                         |                                                |        |         |         |       |         |         |

| Reset  | 0                                       | 0                                              | 0      | 0       | 0       | 0     | 0       | 0       |

|        | _                                       |                                                | _      |         |         | -     |         |         |

| Bit    | 7                                       | 6                                              | 5      | 4       | 3       | 2     | 1       | 0       |

|        |                                         | HWUPIE                                         | HSOFIE | RXRSMIE | RSMEDIE | RSTIE | DDISCIE | DCONNIE |

| Access |                                         |                                                |        |         |         |       |         |         |

| Reset  |                                         | 0                                              | 0      | 0       | 0       | 0     | 0       | 0       |

### Bits 25, 26, 27, 28, 29, 30, 31 – DMA\_ DMA Channel x Interrupt Enable

| Value | Description                                                                        |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|--|--|

| 0     | Cleared when the corresponding bit in USBHS_HSTIDR = 1. This disables the DMA      |  |  |  |  |  |

|       | Channel x Interrupt (USBHS_HSTISR.DMA_x).                                          |  |  |  |  |  |

| 1     | Set when the corresponding bit in USBHS_HSTIER = 1. This enables the DMA Channel x |  |  |  |  |  |

|       | Interrupt (USBHS_HSTISR.DMA_x).                                                    |  |  |  |  |  |

### Bits 8, 9, 10, 11, 12, 13, 14, 15, 16, 17 – PEP\_ Pipe x Interrupt Enable

| V | alue | Description                                                                                                 |

|---|------|-------------------------------------------------------------------------------------------------------------|

| 0 |      | Cleared when $PEP_x = 1$ . This disables the Pipe x Interrupt ( $PEP_x$ ).                                  |

| 1 |      | Set when the corresponding bit in USBHS_HSTIER = 1. This enables the Pipe x Interrupt (USBHS_HSTISR.PEP_x). |

### Bit 6 – HWUPIE Host Wakeup Interrupt Enable

| Value | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 0     | Cleared when USBHS_HSTIDR.HWUPIEC = 1. This disables the Host Wakeup Interrupt                  |

|       | (USBHS_HSTISR.HWUPI).                                                                           |

| 1     | Set when USBHS_HSTIER.HWUPIES = 1. This enables the Host Wakeup Interrupt (USBHS_HSTISR.HWUPI). |

## USB High-Speed Interface (USBHS)

## 39.6.65 Host DMA Channel x Next Descriptor Address Register

| Name:     | USBHS_HSTDMANXTDSCx    |

|-----------|------------------------|

| Offset:   | 0x0700 + x*0x10 [x=06] |

| Reset:    | 0                      |

| Property: | Read/Write             |

| Bit    | 31 | 30 | 29 | 28       | 27          | 26 | 25 | 24 |

|--------|----|----|----|----------|-------------|----|----|----|

|        |    |    |    | NXT_DSC  | ADD[31:24]  |    |    |    |

| Access |    |    |    |          |             |    |    |    |

| Reset  | 0  | 0  | 0  | 0        | 0           | 0  | 0  | 0  |

|        |    |    |    |          |             |    |    |    |

| Bit    | 23 | 22 | 21 | 20       | 19          | 18 | 17 | 16 |

|        |    |    |    | NXT_DSC_ | _ADD[23:16] |    |    |    |

| Access |    |    |    |          |             |    |    |    |

| Reset  | 0  | 0  | 0  | 0        | 0           | 0  | 0  | 0  |

|        |    |    |    |          |             |    |    |    |

| Bit    | 15 | 14 | 13 | 12       | 11          | 10 | 9  | 8  |

|        |    |    |    | NXT_DSC  | _ADD[15:8]  |    |    |    |

| Access | L  |    |    |          |             |    |    |    |

| Reset  | 0  | 0  | 0  | 0        | 0           | 0  | 0  | 0  |

|        |    |    |    |          |             |    |    |    |

| Bit    | 7  | 6  | 5  | 4        | 3           | 2  | 1  | 0  |

|        |    |    |    | NXT_DSC  | _ADD[7:0]   |    |    |    |

| Access |    |    |    |          |             |    |    |    |

| Reset  | 0  | 0  | 0  | 0        | 0           | 0  | 0  | 0  |

## Bits 31:0 – NXT\_DSC\_ADD[31:0] Next Descriptor Address

This field points to the next channel descriptor to be processed. This channel descriptor must be aligned, so bits 0 to 3 of the address must be equal to zero.

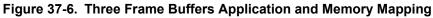

## **Quad Serial Peripheral Interface (QSPI)**

## 42.3 Block Diagram

Figure 42-1. Block Diagram

## 42.4 Signal Description Table 42-1. Signal Description

| Pin Name                      | Pin Description                   | Туре                  |

|-------------------------------|-----------------------------------|-----------------------|

| QSCK                          | Serial Clock                      | Output                |

| MOSI (QIO0) <sup>(1)(2)</sup> | Data Output (Data Input Output 0) | Output (Input/Output) |

| MISO (QIO1) <sup>(1)(2)</sup> | Data Input (Data Input Output 1)  | Input (Input/Output)  |

| QIO2 <sup>(3)</sup>           | Data Input Output 2               | Input/Output          |

| QIO3 <sup>(3)</sup>           | Data Input Output 3               | Input/Output          |

| QCS                           | Peripheral Chip Select            | Output                |

## Note:

- 1. MOSI and MISO are used for single-bit SPI operation.

- 2. QIO0–QIO1 are used for Dual SPI operation.

- 3. QIO0–QIO3 are used for Quad SPI operation.

## 42.5 **Product Dependencies**

## 42.5.1 I/O Lines

The pins used for interfacing the compliant external devices may be multiplexed with PIO lines. The programmer must first program the PIO controllers to assign the QSPI pins to their peripheral functions.

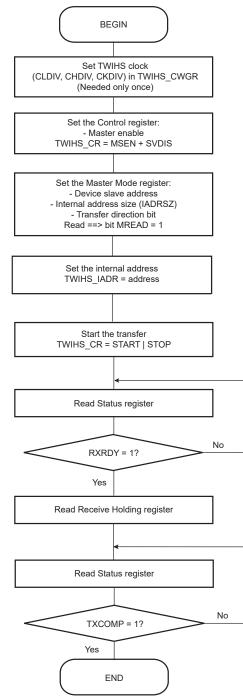

## Two-wire Interface (TWIHS)

## Synchronous Serial Controller (SSC)

### 44.9.11 SSC Receive Compare 0 Register

| Name:     | SSC_RC0R   |

|-----------|------------|

| Offset:   | 0x38       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27    | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-------|-----|-----|-----|

|        |     |     |     |     |       |     |     |     |

| Access |     |     |     |     |       | -   |     |     |

| Reset  |     |     |     |     |       |     |     |     |

|        |     |     |     |     |       |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19    | 18  | 17  | 16  |

|        |     |     |     |     |       |     |     |     |

| Access |     |     |     |     |       |     |     |     |

| Reset  |     |     |     |     |       |     |     |     |

|        |     |     |     |     |       |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9   | 8   |

|        |     |     |     |     | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

|        |     |     |     |     |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|        |     |     |     | CP0 | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

Bits 15:0 – CP0[15:0] Receive Compare Data 0

## Figure 48-22. Single-packet Asynchronous or Control System Memory Structure

| Table 48-23. | Single-packet As   | vnchronous and  | Control Entry Format |

|--------------|--------------------|-----------------|----------------------|

|              | olingio publicitio | ynoni onoao ana |                      |

| Bit Offset | 15       | 14         | 13   | 12    | 11   | 10  | 9    | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----------|------------|------|-------|------|-----|------|----|---|---|---|---|---|---|---|---|

| 0          | CE       | LE         | PG   | Reser | ved  |     |      |    |   |   |   |   |   |   |   |   |

| 16         | Reserved | Reserved   |      |       |      |     |      |    |   |   |   |   |   |   |   |   |

| 32         | RDY1     | DNE1       | ERR1 | PS1   | MEP1 | BD1 | [10: | 0] |   |   |   |   |   |   |   |   |

| 48         | RDY2     | DNE2       | ERR2 | PS2   | MEP2 | BD2 | [10: | 0] |   |   |   |   |   |   |   |   |

| 64         | BA1[15:0 | ני         |      |       |      |     |      |    |   |   |   |   |   |   |   |   |

| 80         | BA1[31:1 | BA1[31:16] |      |       |      |     |      |    |   |   |   |   |   |   |   |   |

| 96         | BA2[15:0 | BA2[15:0]  |      |       |      |     |      |    |   |   |   |   |   |   |   |   |

| 112        | BA2[31:1 | BA2[31:16] |      |       |      |     |      |    |   |   |   |   |   |   |   |   |

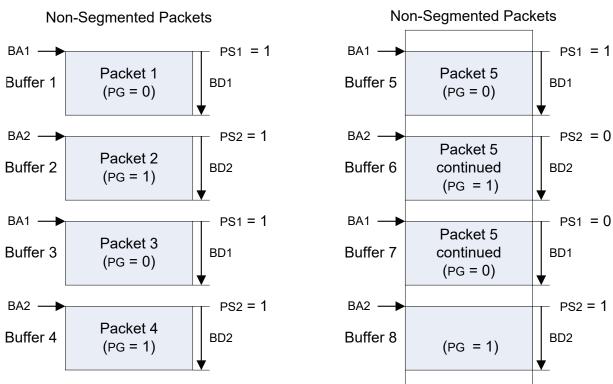

## Multiple-packet Mode

The multiple-packet mode asynchronous and control buffering scheme supports more than one packet per system memory buffer, as shown in the following figure. Multiple- packet mode reduces the interrupt rate for packet channels at the cost of increasing buffering and latency.

For Tx packet channels in multiple-packet mode, software sets the packet start bit (PSn) for every buffer. Setting PSn informs hardware that the first two bytes of the buffer contains the port message length (PML) of the first packet. After the first packet, hardware keeps track of where packets start and end within the current buffer. Software should not write to PSn while the buffer is active (RDYn = 1 and DNEn = 0). For Tx packet channels, the buffer is done (DNEn= 1) when the last byte of the last packet in the

© 2018 Microchip Technology Inc.

## **Controller Area Network (MCAN)**

#### 49.6.36 MCAN Tx FIFO/Queue Status

| Name:     | MCAN_TXFQS |

|-----------|------------|

| Offset:   | 0xC4       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

The Tx FIFO/Queue status is related to the pending Tx requests listed in register MCAN\_TXBRP. Therefore the effect of Add/Cancellation requests may be delayed due to a running Tx scan (MCAN\_TXBRP not yet updated).

In case of mixed configurations where dedicated Tx Buffers are combined with a Tx FIFO or a Tx Queue, the Put and Get Indices indicate the number of the Tx Buffer starting with the first dedicated Tx Buffers. Example: For a configuration of 12 dedicated Tx Buffers and a Tx FIFO of 20 Buffers a Put Index of 15 points to the fourth buffer of the Tx FIFO.

| Bit    | 31 | 30 | 29   | 28 | 27   | 26         | 25 | 24 |

|--------|----|----|------|----|------|------------|----|----|

|        |    |    |      |    |      |            |    |    |

| Access |    |    |      |    |      |            |    |    |

| Reset  |    |    |      |    |      |            |    |    |

|        |    |    |      |    |      |            |    |    |

| Bit    | 23 | 22 | 21   | 20 | 19   | 18         | 17 | 16 |

|        |    |    | TFQF |    |      | TFQPI[4:0] |    |    |

| Access |    |    | R    | R  | R    | R          | R  | R  |

| Reset  |    |    | 0    | 0  | 0    | 0          | 0  | 0  |

|        |    |    |      |    |      |            |    |    |

| Bit    | 15 | 14 | 13   | 12 | 11   | 10         | 9  | 8  |

|        |    |    |      |    |      | TFGI[4:0]  |    |    |

| Access |    | •  | 1    | R  | R    | R          | R  | R  |

| Reset  |    |    |      | 0  | 0    | 0          | 0  | 0  |

|        |    |    |      |    |      |            |    |    |

| Bit    | 7  | 6  | 5    | 4  | 3    | 2          | 1  | 0  |

|        |    |    |      |    | TFFI | _[5:0]     |    |    |

| Access | -  |    | R    | R  | R    | R          | R  | R  |

| Reset  |    |    | 0    | 0  | 0    | 0          | 0  | 0  |

|        |    |    |      |    |      |            |    |    |

Bit 21 – TFQF Tx FIFO/Queue Full

| Value | Description             |

|-------|-------------------------|

| 0     | Tx FIFO/Queue not full. |

| 1     | Tx FIFO/Queue full.     |

**Bits 20:16 – TFQPI[4:0]** Tx FIFO/Queue Put Index Tx FIFO/Queue write index pointer, range 0 to 31.

#### Bits 12:8 - TFGI[4:0] Tx FIFO Get Index

Tx FIFO read index pointer, range 0 to 31. Read as zero when Tx Queue operation is configured (MCAN\_TXBC.TFQM = '1').

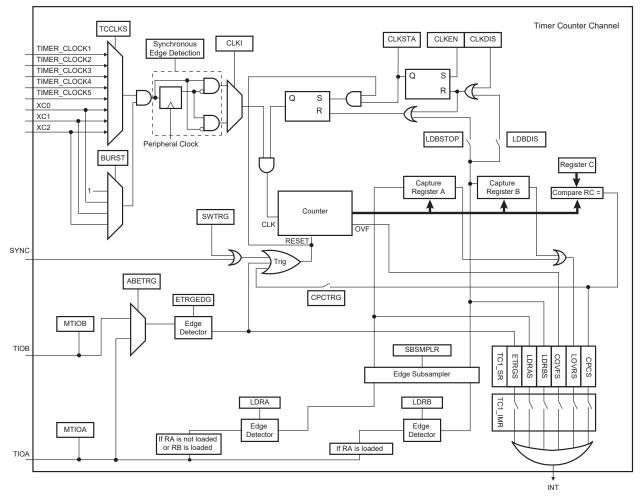

## **Timer Counter (TC)**

### Figure 50-6. Capture Mode

### 50.6.11 Waveform Mode

Waveform mode is entered by setting the TC\_CMRx.WAVE bit.

In Waveform mode, the TC channel generates one or two PWM signals with the same frequency and independently programmable duty cycles, or generates different types of one-shot or repetitive pulses.

In this mode, TIOAx is configured as an output and TIOBx is defined as an output if it is not used as an external event (EEVT parameter in TC\_CMR).

Waveform Mode shows the configuration of the TC channel when programmed in Waveform operating mode.

#### 50.6.12 Waveform Selection

Depending on the WAVSEL parameter in TC\_CMR, the behavior of TC\_CV varies.

With any selection, TC\_RA, TC\_RB and TC\_RC can all be used as compare registers.

RA Compare is used to control the TIOAx output, RB Compare is used to control the TIOBx output (if correctly configured) and RC Compare is used to control TIOAx and/or TIOBx outputs.

## Pulse Width Modulation Controller (PWM)

### 51.7.37 PWM Comparison x Value Update Register

| Name:     | PWM_CMPVUPDx           |

|-----------|------------------------|

| Offset:   | 0x0134 + x*0x10 [x=07] |

| Reset:    | _                      |

| Property: | Write-only             |

This register acts as a double buffer for the CV and CVM values. This prevents an unexpected comparison x match.

Only the first 16 bits (channel counter size) of field CVUPD are significant.

The write of the register PWM\_CMPVUPDx must be followed by a write of the register PWM\_CMPMUPDx.

| Bit    | 31 | 30 | 29 | 28    | 27       | 26 | 25 | 24     |

|--------|----|----|----|-------|----------|----|----|--------|

|        |    |    |    |       |          |    |    | CVMUPD |

| Access |    |    |    |       |          |    |    | W      |

| Reset  |    |    |    |       |          |    |    | _      |

|        |    |    |    |       |          |    |    |        |

| Bit    | 23 | 22 | 21 | 20    | 19       | 18 | 17 | 16     |

|        |    |    |    | CVUPE | 0[23:16] |    |    |        |

| Access | W  | W  | W  | W     | W        | W  | W  | W      |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0      |

|        |    |    |    |       |          |    |    |        |

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9  | 8      |

|        |    |    |    | CVUP  | D[15:8]  |    |    |        |

| Access | W  | W  | W  | W     | W        | W  | W  | W      |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0      |

|        |    |    |    |       |          |    |    |        |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0      |

|        |    |    |    | CVUP  | D[7:0]   |    |    |        |

| Access | W  | W  | W  | W     | W        | W  | W  | W      |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | _      |

|        | 2  | -  | 2  | -     | 3        | 2  | 2  |        |

## Bit 24 – CVMUPD Comparison x Value Mode Update

**Note:** This bit is not relevant if the counter of the channel 0 is left-aligned (CALG = 0 in PWM Channel Mode Register)

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | The comparison x between the counter of the channel 0 and the comparison x value is |

|       | performed when this counter is incrementing.                                        |

| 1     | The comparison x between the counter of the channel 0 and the comparison x value is |

|       | performed when this counter is decrementing.                                        |

## Bits 23:0 - CVUPD[23:0] Comparison x Value Update

Define the comparison x value to be compared with the counter of the channel 0.

## Integrity Check Monitor (ICM)

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Automatic monitoring mode is disabled.                                           |

| 1     | The ICM passes through the Main List once to calculate the message digest of the |

|       | monitored area. When WRAP = 1 in ICM_RCFG, the ICM begins monitoring.            |

## Bits 7:4 – BBC[3:0] Bus Burden Control

This field is used to control the burden of the ICM system bus. The number of system clock cycles between the end of the current processing and the next block transfer is set to 2<sup>BBC</sup>. Up to 32,768 cycles can be inserted.

## Bit 2 – SLBDIS Secondary List Branching Disable

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | Branching to the Secondary List is permitted.                                           |

| 1     | Branching to the Secondary List is forbidden. The NEXT field of the ICM_RNEXT structure |

|       | member has no effect and is always considered as zero.                                  |

### Bit 1 – EOMDIS End of Monitoring Disable

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | End of Monitoring is permitted.                                                             |

| 1     | End of Monitoring is forbidden. The EOM bit of the ICM_RCFG structure member has no effect. |

### Bit 0 – WBDIS Write Back Disable

When ASCD is set, WBDIS has no effect.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Write Back operations are permitted.                                                         |

| 1     | Write Back operations are forbidden. Context register CDWBN bit is internally set to one and |

|       | cannot be modified by a linked list element. ICM_RCFG.CDWBN has no effect.                   |

## **Advanced Encryption Standard (AES)**

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | No unspecified register access has been detected since the last SWRST.           |

| 1     | At least one unspecified register access has been detected since the last SWRST. |

**Bit 0 – DATRDY** Data Ready (cleared by setting bit START or bit SWRST in AES\_CR or by reading AES\_ODATARx)

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Output data not valid.                         |

| 1     | Encryption or decryption process is completed. |

**Note:** If AES\_MR.LOD = 1: In Manual and Auto mode, the DATRDY flag can also be cleared by writing at least one AES\_IDATARx.

## Electrical Characteristics for SAM ...

| FWS | Read Operations | Maximum Operating<br>Frequency (MHz) - VDDIO 3.0V |

|-----|-----------------|---------------------------------------------------|

| 0   | 1 cycle         | 23                                                |

| 1   | 2 cycles        | 46                                                |

| 2   | 3 cycles        | 69                                                |

| 3   | 4 cycles        | 92                                                |

| 4   | 5 cycles        | 115                                               |

| 5   | 6 cycles        | 138                                               |

| 6   | 7 cycles        | 150                                               |

## Table 58-51. Embedded Flash Wait States for Worst-Case Conditions

## 58.13 Timings for STH Conditions

## 58.13.1 AC Characteristics

## 58.13.1.1 Processor Clock Characteristics

## Table 58-52. Processor Clock Waveform Parameters

| Symbol                  | Parameter                 | Conditions | Min | Max | Unit |

|-------------------------|---------------------------|------------|-----|-----|------|

| 1/(t <sub>CPPCK</sub> ) | Processor Clock Frequency | Worst case | _   | 300 | MHz  |

## 58.13.1.2 Master Clock Characteristics

#### Table 58-53. Master Clock Waveform Parameters

| Syn               | nbol   | Parameter              | Conditions | Min | Max | Unit |

|-------------------|--------|------------------------|------------|-----|-----|------|

| 1/(t <sub>c</sub> | срмск) | Master Clock Frequency | Worst case | -   | 150 | MHz  |

## 58.13.1.3 I/O Characteristics

Criteria used to define the maximum frequency of the I/Os:

- Output duty cycle (40%-60%)

- Minimum output swing: 100 mV to  $V_{\text{DDIO}}$  100 mV

- Addition of rising and falling time inferior to 75% of the period

## Table 58-54. I/O Characteristics

| Symbol   | arameter Conditions                                 |       |                   | Min            | Max | Unit |     |

|----------|-----------------------------------------------------|-------|-------------------|----------------|-----|------|-----|

|          |                                                     | Load  | V <sub>DDIO</sub> | Drive<br>Level |     |      |     |

| FreqMax1 | Pin Group 1 <sup>(1)</sup> Maximum output frequency | 10 pF | 3.0V              | Low            | -   | 65   | MHz |

|          |                                                     |       |                   | High           | -   | 115  |     |

|          |                                                     | 25 pF |                   | Low            | _   | 28   |     |

## Revision History

| Date | Changes                                                                                                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | AFEC_TEMPCWR.                                                                                                                                                                                                                                           |

|      | Section 52.7.2 "AFEC Mode Register": updated TRACKTIM description.                                                                                                                                                                                      |

|      | Section 53. "Digital-to-Analog Converter Controller (DACC)"<br>Table 53-1 "DACC Signal Description" : corrected pin names to VREFP and VREFN (were<br>ADVREFP and ADVREFN).                                                                             |

|      | Section 54. "Analog Comparator Controller (ACC)"<br>Table 54-1 "ACC Signal Description" : modified Description for DAC0, DAC1 signals.                                                                                                                  |

|      | Section 54.7.7 "ACC Analog Control Register": updated HYST definition.                                                                                                                                                                                  |

|      | Section 57. "Advanced Encryption Standard (AES)"<br>Section 57.2 "Embedded Characteristics": replaced "12/14/16 Clock Cycles Encryption/<br>Decryption Processing Time" with "10/12/14 Clock Cycles Encryption/Decryption Inherent<br>Processing Time". |

|      | Section 58. "Electrical Characteristics"<br>Table 58-3 "DC Characteristics" : removed Note 2 on current injection.                                                                                                                                      |

|      | Table 58-4 "DC Characteristics" : voltage input level defined for the RST and TEST I/O types. Updated max values for IIL and IIH.                                                                                                                       |

|      | Updated Table 58-15 "Typical Current Consumption in Wait Mode" .                                                                                                                                                                                        |

|      | Table 58-30 "VREFP Electrical Characteristics" : updated $V_{VREFP}$ parameter values.                                                                                                                                                                  |

|      | Added new Table 58-34 "AFE INL and DNL, fAFE Clock =<20 MHz max, IBCTL=10" and Table 58-35 "AFE INL and DNL, fAFE Clock >20 MHz to 40 MHz, IBCTL=11" .                                                                                                  |

|      | Inserted new Table 58-36 "AFE Offset and Gain Error, VVREFP = $1.7V$ to $3.3V$ ".                                                                                                                                                                       |

|      | Updated Table 58-40 "DAC Static Performances (1)" .                                                                                                                                                                                                     |

|      | Updated Table 58-46 "Static Performance Characteristics"                                                                                                                                                                                                |

|      | Added Section 58.13.1.10: "USART in Asynchronous Mode".                                                                                                                                                                                                 |

|      | Section 62. "Ordering Information"<br>Added Note <sup>(2)</sup> on availability.                                                                                                                                                                        |

|      | Section 63. "Errata"<br>Added:                                                                                                                                                                                                                          |

|      | - Section 63.1.16 "Universal Synchronous Asynchronous Receiver Transmitter (USART)":<br>"Bad frame detection issue"                                                                                                                                     |

|      | - Section 63.2.4 "ARM Cortex-M7": "All issues related to the ARM r1p1 core are described on the ARM site"                                                                                                                                               |

|      | - Section 63.2.6 "Inter-IC Sound Controller (I2SC)": "I2SC first sent data corrupted"                                                                                                                                                                   |

|      | - Section 63.2.12 "Universal Synchronous Asynchronous Receiver Transmitter (USART)":<br>"Bad frame detection issue"                                                                                                                                     |

|      | Deleted:                                                                                                                                                                                                                                                |