Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 300MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 114                                                                              |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 384K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70q21b-an        |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 13. System Controller

The System Controller is a set of peripherals that handles key elements of the system, such as power, resets, clocks, time, interrupts, watchdog, and so on..

## 13.1 System Controller and Peripherals Mapping

Refer to the "Product Mapping" section.

## 13.2 Power-on-Reset, Brownout and Supply Monitor

The SAM E70/S70/V70/V71 embeds three features to monitor, warn and/or reset the chip:

- Power-on-Reset (POR) on VDDIO

- POR on VDDCORE

- Brown-out-Detector (BOD) on VDDCORE

- Supply Monitor on VDDIO

## 13.2.1 Power-on-Reset

The Power-on-Reset (POR) monitors VDDIO and VDDCORE. It is always activated and monitors voltage at start up but also during power down. If VDDIO or VDDCORE goes below the threshold voltage, the entire chip is Reset. For more information, refer to 58. Electrical Characteristics for SAM V70/V71.

## 13.2.2 Brownout Detector on VDDCORE

The Brown-out-Detector(BOD) monitors VDDCORE. It is active by default. It can be deactivated by software through the Supply Controller (SUPC\_MR). It is especially recommended to disable it during low-power modes, such as wait or sleep modes.

If VDDCORE goes below the threshold voltage, the reset of the core is asserted. For more information, refer to 23. Supply Controller (SUPC) and 58. Electrical Characteristics for SAM V70/V71.

## 13.2.3 Supply Monitor on VDDIO

The Supply Monitor monitors VDDIO. It is not active by default. It can be activated by software and is fully programmable with 16 steps for the threshold (between 1.6V to 3.4V). It is controlled by the Supply Controller (SUPC). A sample mode is possible, which allows the supply monitor power consumption to be divided by a factor of up to 2048. For more information, refer to 23. Supply Controller (SUPC) and 58. Electrical Characteristics for SAM V70/V71.

## 13.3 Reset Controller

The Reset Controller is based on two POR cells, one on VDDIO and one on VDDCORE, and a Supply Monitor on VDDIO.

The Reset Controller returns the source of the last reset to the software. This may be a general reset, a wakeup reset, a software reset, a user reset or a watchdog reset.

The Reset Controller controls the internal resets of the system and the pin input/output. It can shape a reset signal for the external devices, simplifying the connection of a push-button on the NRST pin to implement a manual reset.

## Bit 1 – UPDCAL Update Request Calendar Register

Calendar counting consists of day, date, month, year and century counters. Calendar counters can be programmed once this bit is set and acknowledged by the bit ACKUPD of the RTC\_SR.

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | No effect or, if UPDCAL has been previously written to 1, stops the update procedure. |

| 1     | Stops the RTC calendar counting.                                                      |

### Bit 0 – UPDTIM Update Request Time Register

Time counting consists of second, minute and hour counters. Time counters can be programmed once this bit is set and acknowledged by the bit ACKUPD of the RTC\_SR.

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | No effect or, if UPDTIM has been previously written to 1, stops the update procedure. |

| 1     | Stops the RTC time counting.                                                          |

## **Power Management Controller (PMC)**

### 31.20.18 PMC Fast Startup Mode Register

| Name:     | PMC_FSMR   |

|-----------|------------|

| Offset:   | 0x0070     |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31     | 30     | 29     | 28     | 27     | 26     | 25    | 24    |

|--------|--------|--------|--------|--------|--------|--------|-------|-------|

|        |        |        |        |        |        |        |       |       |

| Access |        |        |        |        |        |        |       |       |

| Reset  |        |        |        |        |        |        |       |       |

|        |        |        |        |        |        |        |       |       |

| Bit    | 23     | 22     | 21     | 20     | 19     | 18     | 17    | 16    |

|        | FFLPM  | FLPN   | /[1:0] | LPM    |        | USBAL  | RTCAL | RTTAL |

| Access |        |        |        |        |        |        |       |       |

| Reset  | 0      | 0      | 0      | 0      |        | 0      | 0     | 0     |

|        |        |        |        |        |        |        |       |       |

| Bit    | 15     | 14     | 13     | 12     | 11     | 10     | 9     | 8     |

|        | FSTT15 | FSTT14 | FSTT13 | FSTT12 | FSTT11 | FSTT10 | FSTT9 | FSTT8 |

| Access |        |        |        |        |        |        |       |       |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

|        |        |        |        |        |        |        |       |       |

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|        | FSTT7  | FSTT6  | FSTT5  | FSTT4  | FSTT3  | FSTT2  | FSTT1 | FSTT0 |

| Access |        |        | •      | •      |        |        |       |       |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

### Bit 23 – FFLPM Force Flash Low-power Mode

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Flash Low-power mode, defined in the FLPM field, is automatically applied when in Wait |

|       | mode and released when going back to Active mode.                                          |

| 1     | The Flash Low-power mode is user defined by the FLPM field and immediately applied.        |

### Bits 22:21 - FLPM[1:0] Flash Low-power Mode

| Value | Name                 | Description                                           |

|-------|----------------------|-------------------------------------------------------|

| 0     | FLASH_STANDBY        | Flash is in Standby Mode when system enters Wait Mode |

| 1     | FLASH_DEEP_POWERDOWN | Flash is in Deep-powerdown mode when system enters    |

|       |                      | Wait Mode                                             |

| 2     | FLASH_IDLE           | Idle mode                                             |

## Bit 20 - LPM Low-power Mode

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The WaitForInterrupt (WFI) or the WaitForEvent (WFE) instruction of the processor makes |

|       | the processor enter Sleep mode.                                                         |

| 1     | The WaitForEvent (WFE) instruction of the processor makes the system enter Wait mode.   |

## Parallel Input/Output Controller (PIO)

### 32.6.1.8 PIO Input Filter Disable Register

| Name:     | PIO_IFDR   |

|-----------|------------|

| Offset:   | 0x0024     |

| Property: | Write-only |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Input Filter Disable

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | No effect.                                        |

| 1     | Disables the input glitch filter on the I/O line. |

## Static Memory Controller (SMC)

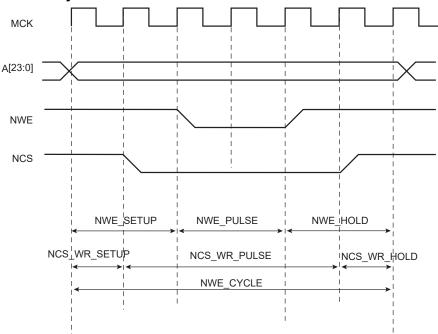

- NWE\_SETUP—the NWE setup time is defined as the setup of address and data before the NWE falling edge;

- NWE\_PULSE—the NWE pulse length is the time between NWE falling edge and NWE rising edge;

- NWE\_HOLD—the NWE hold time is defined as the hold time of address and data after the NWE rising edge.

### 35.9.3.2 NCS Waveforms

The NCS signal waveforms in write operation are not the same that those applied in read operations, but are separately defined:

- ncs\_wr\_setup—the NCS setup time is defined as the setup time of address before the NCS falling edge.

- ncs\_wr\_pulse—the NCS pulse length is the time between NCS falling edge and NCS rising edge;

- ncs\_wr\_hold—the NCS hold time is defined as the hold time of address after the NCS rising edge. **Figure 35-13. Write Cycle**

### 35.9.3.3 Write Cycle

The write\_cycle time is defined as the total duration of the write cycle; that is, from the time where address is set on the address bus to the point where address may change. The total write cycle time is defined as:

NWE\_CYCLE = NWE\_SETUP + NWE\_PULSE + NWE\_HOLD,

as well as

NWE\_CYCLE = NCS\_WR\_SETUP + NCS\_WR\_PULSE + NCS\_WR\_HOLD

All NWE and NCS (write) timings are defined separately for each chip select as an integer number of Master Clock cycles. The NWE\_CYCLE field is common to both the NWE and NCS signals, thus the timing period is of the same duration.

NWE\_CYCLE, NWE\_SETUP, and NWE\_PULSE implicitly define the NWE\_HOLD value as:

NWE\_HOLD = NWE\_CYCLE - NWE\_SETUP - NWE\_PULSE

## Static Memory Controller (SMC)

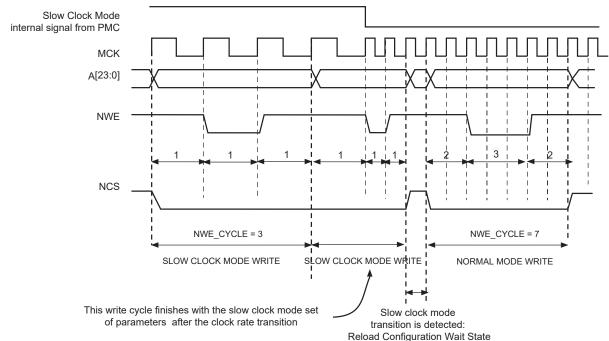

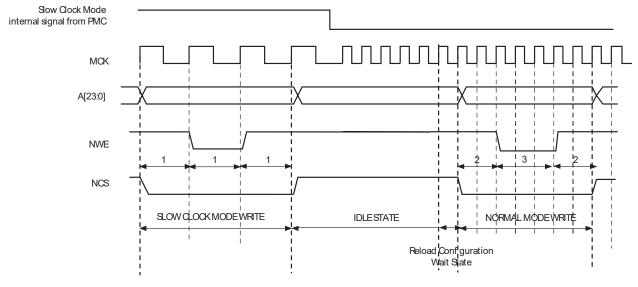

### Figure 35-33. Clock Rate Transition Occurs while the SMC is Performing a Write Operation

## 35.15 Asynchronous Page Mode

The SMC supports asynchronous burst reads in Page mode, provided that the Page mode is enabled (SMC\_MODE.PMEN =1). The page size must be configured in the SMC\_MODE register (PS field) to 4, 8, 16 or 32 bytes.

The page defines a set of consecutive bytes into memory. A 4-byte page (resp. 8-, 16-, 32-byte page) is always aligned to 4-byte boundaries (resp. 8-, 16-, 32-byte boundaries) of memory. The MSB of data address defines the address of the page in memory, the LSB of address define the address of the data in the page as detailed in the following table.

# **DMA Controller (XDMAC)**

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | End of flush condition has not occurred.                                        |

| 1     | End of flush condition has occurred since the last read of the Status register. |

### Bit 2 – DIS End of Disable Interrupt Status Bit

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | End of disable condition has not occurred.                                        |

| 1     | End of disable condition has occurred since the last read of the Status register. |

### **Bit 1 – LIS** End of Linked List Interrupt Status Bit

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | End of linked list condition has not occurred.                                        |

| 1     | End of linked list condition has occurred since the last read of the Status register. |

## Bit 0 – BIS End of Block Interrupt Status Bit

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | End of block interrupt has not occurred.                                        |

| 1     | End of block interrupt has occurred since the last read of the Status register. |

## Image Sensor Interface (ISI)

## 37.6.22 DMA Codec Control Register

| Name:<br>Offset:<br>Reset:<br>Property: |    | ISI_DMA_C_0<br>0x54<br>0x00000000<br>Read/Write | CTRL |    |        |       |      |         |

|-----------------------------------------|----|-------------------------------------------------|------|----|--------|-------|------|---------|

| Bit                                     | 31 | 30                                              | 29   | 28 | 27     | 26    | 25   | 24      |

|                                         |    |                                                 |      |    |        |       |      |         |

| Access                                  |    | ·                                               |      |    |        |       |      |         |

| Reset                                   |    |                                                 |      |    |        |       |      |         |

| Bit                                     | 23 | 22                                              | 21   | 20 | 19     | 18    | 17   | 16      |

| Dit                                     | 20 |                                                 | 21   | 20 | 15     | 10    | 17   | 10      |

| Access                                  |    |                                                 |      |    |        |       |      |         |

| Reset                                   |    |                                                 |      |    |        |       |      |         |

|                                         |    |                                                 |      |    |        |       |      |         |

| Bit                                     | 15 | 14                                              | 13   | 12 | 11     | 10    | 9    | 8       |

|                                         |    |                                                 |      |    |        |       |      |         |

| Access                                  |    |                                                 |      |    |        |       |      |         |

| Reset                                   |    |                                                 |      |    |        |       |      |         |

| <b>D</b> :4                             | 7  | G                                               | F    | 4  | 2      | 2     | 4    | 0       |

| Bit                                     | 7  | 6                                               | 5    | 4  | 3      |       | 1    |         |

|                                         |    |                                                 |      |    | C_DONE | C_IEN | C_WB | C_FETCH |

| Access                                  |    |                                                 |      |    | R/W    | R/W   | R/W  | R/W     |

| Reset                                   |    |                                                 |      |    | 0      | 0     | 0    | 0       |

**Bit 3 – C\_DONE** Codec Transfer Done This bit is only updated in the memory.

| Value | Description                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The transfer related to this descriptor has not been performed.                                                                                      |

| 1     | The transfer related to this descriptor has completed. This bit is updated in memory at the end of the transfer when writeback operation is enabled. |

### Bit 2 – C\_IEN Transfer Done Flag Control

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Codec transfer done flag generation is enabled.  |

| 1     | Codec transfer done flag generation is disabled. |

## Bit 1 – C\_WB Descriptor Writeback Control Bit

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Codec channel writeback operation is disabled. |

| 1     | Codec channel writeback operation is enabled.  |

## Bit 0 – C\_FETCH Descriptor Fetch Control Bit

# **GMAC** - Ethernet MAC

| Offset | Name        | Bit Pos. |     |      |       |         |         |      |

|--------|-------------|----------|-----|------|-------|---------|---------|------|

|        |             | 7:0      |     | ,    | TCKE  | R[7:0]  |         |      |

| 0x01AC | GMAC_TCE    | 15:8     |     |      |       |         |         |      |

| UXUTAC | GINAC_TCE   | 23:16    |     |      |       |         |         |      |

|        |             | 31:24    |     |      |       |         |         |      |

|        |             | 7:0      |     |      | UCKE  | R[7:0]  |         |      |

| 0x01B0 |             | 15:8     |     |      |       |         |         |      |

| UXUIBU | GMAC_UCE    | 23:16    |     |      |       |         |         |      |

|        |             | 31:24    |     |      |       |         |         |      |

| 0x01B4 |             |          |     |      |       |         |         |      |

|        | Reserved    |          |     |      |       |         |         |      |

| 0x01BB |             |          |     |      |       |         |         |      |

|        |             | 7:0      |     |      | LSBT  | IR[7:0] |         |      |

| 0x01BC | GMAC_TISUBN | 15:8     |     |      | LSBTI | R[15:8] |         |      |

| UNUTED |             | 23:16    |     |      |       |         |         |      |

|        |             | 31:24    |     |      |       |         |         |      |

|        |             | 7:0      |     |      | TCS   | [7:0]   |         |      |

| 0x01C0 | GMAC_TSH    | 15:8     |     |      | TCS   | [15:8]  |         |      |

| 0,0100 | GMAC_ISH    | 23:16    |     |      |       |         |         |      |

|        |             | 31:24    |     |      |       |         |         |      |

| 0x01C4 |             |          |     |      |       |         |         |      |

|        | Reserved    |          |     |      |       |         |         |      |

| 0x01CF |             |          |     |      |       |         |         |      |

|        |             | 7:0      |     |      | TCS   |         |         |      |

| 0x01D0 | GMAC_TSL    | 15:8     |     |      |       | [15:8]  |         |      |

|        |             | 23:16    |     |      | TCS[2 |         |         |      |

|        |             | 31:24    |     |      | TCS[  |         |         |      |

|        |             | 7:0      |     |      |       | [7:0]   |         |      |

| 0x01D4 | GMAC_TN     | 15:8     |     |      |       | [15:8]  |         |      |

|        | _           | 23:16    |     |      | TNS[2 |         |         |      |

|        |             | 31:24    |     |      |       |         | [29:24] |      |

|        |             | 7:0      |     |      | ITDT  |         |         |      |

| 0x01D8 | GMAC_TA     | 15:8     |     |      | ITDT  |         |         |      |

|        |             | 23:16    |     |      | ITDT[ |         |         |      |

|        |             | 31:24    | ADJ |      |       |         | [29:24] |      |

|        |             | 7:0      |     |      |       | 5[7:0]  |         |      |

| 0x01DC | GMAC_TI     | 15:8     |     |      |       | S[7:0]  |         |      |

| -      |             | 23:16    |     |      | NIT   | [7:0]   |         | <br> |

|        |             | 31:24    |     |      |       |         |         |      |

|        |             | 7:0      |     |      |       | 0[7:0]  |         |      |

| 0x01E0 | GMAC_EFTSL  | 15:8     |     |      |       | [15:8]  |         |      |

|        | _           | 23:16    |     | <br> |       | 23:16]  |         |      |

|        |             | 31:24    |     |      |       | 31:24]  |         |      |

|        |             | 7:0      |     |      |       | 0[7:0]  |         |      |

| 0x01E4 | GMAC_EFTN   | 15:8     |     |      |       | [15:8]  |         |      |

|        | GMAC_EFTN   | 23:16    |     |      | RUD[  | 23:16]  |         |      |

|        |             | 31:24    |     |      |       |         | [29:24] |      |

### 38.8.59 GMAC Octets Received High Register

| Name:     | GMAC_ORHI  |

|-----------|------------|

| Offset:   | 0x154      |

| Reset:    | 0x00000000 |

| Property: | -          |

When reading the Octets Transmitted and Octets Received Registers, bits 31:0 should be read prior to bits 47:32 to ensure reliable operation.

| Bit    | 31 | 30 | 29 | 28  | 27     | 26 | 25 | 24 |

|--------|----|----|----|-----|--------|----|----|----|

|        |    |    |    |     |        |    |    |    |

| Access |    |    |    |     |        |    |    |    |

| Reset  |    |    |    |     |        |    |    |    |

|        |    |    |    |     |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20  | 19     | 18 | 17 | 16 |

|        |    |    |    |     |        |    |    |    |

| Access |    |    |    |     |        |    |    |    |

| Reset  |    |    |    |     |        |    |    |    |

|        |    |    |    |     |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12  | 11     | 10 | 9  | 8  |

|        |    |    |    | RXO | [15:8] |    |    |    |

| Access | R  | R  | R  | R   | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0   | 0      | 0  | 0  | 0  |

|        |    |    |    |     |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4   | 3      | 2  | 1  | 0  |

|        |    |    |    | RXC | [7:0]  |    |    |    |

| Access | R  | R  | R  | R   | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0   | 0      | 0  | 0  | 0  |

## Bits 15:0 - RXO[15:0] Received Octets

Received octets in frame without errors [47:32]. The number of octets received in valid frames of any type. This counter is 48-bits and is read through two registers. This count does not include octets from pause frames, and is only incremented if the frame is successfully filtered and copied to memory.

# USB High-Speed Interface (USBHS)

| Offset | Name | Bit Pos. |  |  |  |  |

|--------|------|----------|--|--|--|--|

|        |      | 23:16    |  |  |  |  |

|        |      | 31:24    |  |  |  |  |

## High-Speed Multimedia Card Interface (HSMCI)

| Tuble 40-2. Bus topology |                          |           |                       |                                           |  |  |  |  |  |  |

|--------------------------|--------------------------|-----------|-----------------------|-------------------------------------------|--|--|--|--|--|--|

| Pin Number               | Name Type <sup>(1)</sup> |           | Description           | HSMCI Pin Name <sup>(2)</sup><br>(Slot z) |  |  |  |  |  |  |

| 1                        | DAT[3]                   | I/O/PP    | Data                  | MCDz3                                     |  |  |  |  |  |  |

| 2                        | CMD                      | I/O/PP/OD | Command/response      | MCCDz                                     |  |  |  |  |  |  |

| 3                        | VSS1                     | S         | Supply voltage ground | VSS                                       |  |  |  |  |  |  |

| 4                        | VDD                      | S         | Supply voltage        | VDD                                       |  |  |  |  |  |  |

| 5                        | CLK                      | I/O       | Clock                 | MCCK                                      |  |  |  |  |  |  |

| 6                        | VSS2                     | S         | Supply voltage ground | VSS                                       |  |  |  |  |  |  |

| 7                        | DAT[0]                   | I/O/PP    | Data 0                | MCDz0                                     |  |  |  |  |  |  |

| 8                        | DAT[1]                   | I/O/PP    | Data 1                | MCDz1                                     |  |  |  |  |  |  |

| 9                        | DAT[2]                   | I/O/PP    | Data 2                | MCDz2                                     |  |  |  |  |  |  |

### Table 40-2. Bus Topology

Notes: 1. I: Input, O: Output, PP: Push/Pull, OD: Open Drain, S: Supply

2. When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA, MCDAy to HSMCIx\_DAy.

Figure 40-4. MMC Bus Connections (One Slot)

Note: When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA MCDAy to HSMCIx\_DAy.

## Figure 40-5. SD Memory Card Bus Topology

| 1 2 3 4 5 6 7 8<br>9 SD CARD | · · _ |          |

|------------------------------|-------|----------|

|                              | 9     | 12345678 |

The SD Memory Card bus includes the signals listed in Table 1-6.

## Serial Peripheral Interface (SPI)

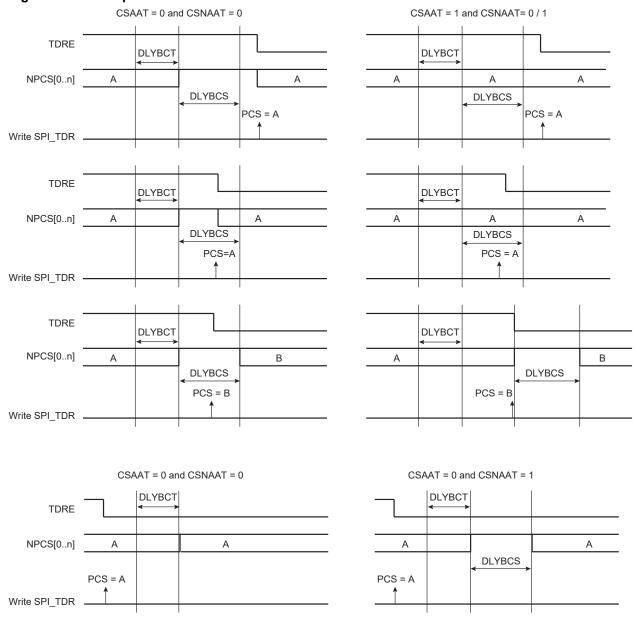

transfers. This can lead to difficulties to interface with some serial peripherals requiring the chip select to be deasserted after each transfer. To facilitate interfacing with such devices, SPI\_CSR can be programmed with the Chip Select Not Active After Transfer (CSNAAT) bit at 1. This allows the chip select lines to be deasserted systematically during a time "DLYBCS" (the value of the CSNAAT bit is processed only if the CSAAT bit is configured to 0 for the same chip select).

The following figure shows different peripheral deselection cases and the effect of the CSAAT and CSNAAT bits.

### Figure 41-11. Peripheral Deselection

## 41.7.3.10 Mode Fault Detection

The SPI has the capability to operate in multimaster environment. Consequently, the NPCS0/NSS line must be monitored. If one of the masters on the SPI bus is currently transmitting, the NPCS0/NSS line is low and the SPI must not transmit any data. A mode fault is detected when the SPI is programmed in Master mode and a low level is driven by an external master on the NPCS0/NSS signal. In multimaster

| Peripheral Clock | Baud Rate (bit/s) | CD  | Baud Rate Error | Pulse Time (µs) |

|------------------|-------------------|-----|-----------------|-----------------|

| 20,000,000       | 9,600             | 130 | 0.16%           | 19.53           |

| 32,768,000       | 9,600             | 213 | 0.16%           | 19.53           |

| 40,000,000       | 9,600             | 260 | 0.16%           | 19.53           |

| 3,686,400        | 2,400             | 96  | 0.00%           | 78.13           |

| 20,000,000       | 2,400             | 521 | 0.03%           | 78.13           |

| 32,768,000       | 2,400             | 853 | 0.04%           | 78.13           |

## Universal Synchronous Asynchronous Receiver Transc...

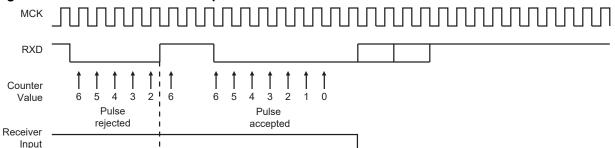

### 46.6.5.3 IrDA Demodulator

The demodulator is based on the IrDA Receive filter comprised of an 8-bit down counter which is loaded with the value programmed in US\_IF. When a falling edge is detected on the RXD pin, the Filter Counter starts counting down at the peripheral clock speed. If a rising edge is detected on the RXD pin, the counter stops and is reloaded with US\_IF. If no rising edge is detected when the counter reaches 0, the input of the receiver is driven low during one bit time.

The following figure illustrates the operations of the IrDA demodulator.

### Figure 46-34. IrDA Demodulator Operations

The programmed value in the US\_IF register must always meet the following criterion:

t<sub>peripheral clock</sub> × (IRDA\_FILTER + 3) < 1.41 μs

As the IrDA mode uses the same logic as the ISO7816, note that the FI\_DI\_RATIO field in US\_FIDI must be set to a value higher than 0 in order to ensure IrDA communications operate correctly.

### 46.6.6 RS485 Mode

The USART features the RS485 mode to enable line driver control. While operating in RS485 mode, the USART behaves as though in Asynchronous or Synchronous mode and configuration of all the parameters is possible. The difference is that the RTS pin is driven high when the transmitter is operating. The behavior of the RTS pin is controlled by the TXEMPTY bit. A typical connection of the USART to an RS485 bus is shown in Figure 46-35.

The isochronous buffering scheme allows each ping or pong buffer to contain a single block or a multiple number of blocks. For this reason, the isochronous buffer depth (BDn) must be defined in terms of an integer number (n) and block size (BS) (e.g. BDn =  $n \times (BS + 1) - 1$ ).

Table 48-22 shows the format for an isochronous ADT entry. The field definitions are defined in Table48-23. Each isochronous channel buffer can be up to 8k-bytes deep.

| Bit Offset | 15        | 14   | 13   | 12   | 11     | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|-----------|------|------|------|--------|----|---|---|---|---|---|---|---|---|---|---|

| 0          | CE        | LE   | PG   | Rese | erved  |    |   |   |   |   |   |   |   |   |   |   |

| 16         | Reserved  |      |      |      |        |    |   |   |   |   |   |   |   |   |   |   |

| 32         | RDY1      | DNE1 | ERR1 | BD1[ | [12:0] |    |   |   |   |   |   |   |   |   |   |   |

| 48         | RDY2      | DNE2 | ERR2 | BD2[ | [12:0] |    |   |   |   |   |   |   |   |   |   |   |

| 64         | BA1[15:0] |      |      |      |        |    |   |   |   |   |   |   |   |   |   |   |

| 80         | BA1[31:16 | 6]   |      |      |        |    |   |   |   |   |   |   |   |   |   |   |

| 96         | BA2[15:0] |      |      |      |        |    |   |   |   |   |   |   |   |   |   |   |

| 112        | BA2[31:16 | 6]   |      |      |        |    |   |   |   |   |   |   |   |   |   |   |

Table 48-22. Isochronous ADT Entry Format

## AHB Asynchronous and Control Channel Descriptors

Every asynchronous and control packet adheres to the Port Message Protocol (PMP), which designates the first two bytes of each packet as the packet length (PML). Each packet must be no more than 2048 bytes.

Software must set the buffer ready bit (RDYn) for each buffer as it programs the DMA. As hardware processes each buffer, it sets the done bit (DNEn) and generates an interrupt to inform HC. When hardware finishes processing a buffer it can begin processing another buffer if RDYn is set. The application is responsible for setting up and configuring the channel buffer descriptor prior to every DMA access on the channel.

Two packet modes are supported by hardware for programming the DMA, single-packet mode and multiple-packet mode.

## Single-packet Mode

The single-packet mode asynchronous and control buffering scheme supports a maximum of one packet per buffer (e.g. ping or pong). Both non-segmented and segmented data packets are allowed while using single-packet mode.

Non-segmented packets are exchanged when only one buffer (e.g. ping or pong) is needed for packet transfer. Segmented packets are exchanged when a single packet is too long for one buffer and the packet must span multiple buffers. The following figure shows the memory space usage for both non-segmented and segmented asynchronous or control packets along with the packet start bit (PSn). While using single-packet mode, buffer done (DNEn) is set in hardware when a packet is done or the buffer is full.

shows the format for single-packet mode asynchronous and control ADT entries. The field definitions are defined in Table 48-23.

## Controller Area Network (MCAN)

#### 49.6.1 MCAN Core Release Register

| Name:     | MCAN_CREL  |

|-----------|------------|

| Offset:   | 0x00       |

| Reset:    | 0xrrrddddd |

| Property: | Read-only  |

Due to clock domain crossing, there is a delay between when a register bit or field is written and when the related status register bits are updated.

| Bit    | 31 | 30    | 29      | 28  | 27             | 26   | 25     | 24 |

|--------|----|-------|---------|-----|----------------|------|--------|----|

|        |    | REL   | [3:0]   |     |                | STEF | P[3:0] |    |

| Access | R  | R     | R       | R   | R              | R    | R      | R  |

| Reset  | x  | x     | x       | x   | x              | х    | x      | x  |

|        |    |       |         |     |                |      |        |    |

| Bit    | 23 | 22    | 21      | 20  | 19             | 18   | 17     | 16 |

|        |    | SUBST | EP[3:0] |     |                | YEAF | R[3:0] |    |

| Access | R  | R     | R       | R   | R              | R    | R      | R  |

| Reset  | х  | x     | x       | x   | x              | х    | x      | x  |

|        |    |       |         |     |                |      |        |    |

| Bit    | 15 | 14    | 13      | 12  | 11             | 10   | 9      | 8  |

|        |    |       |         | MON | <b>I</b> [7:0] |      |        |    |

| Access | R  | R     | R       | R   | R              | R    | R      | R  |

| Reset  | x  | x     | х       | x   | х              | x    | x      | x  |

|        |    |       |         |     |                |      |        |    |

| Bit    | 7  | 6     | 5       | 4   | 3              | 2    | 1      | 0  |

|        |    |       |         | DAY | [7:0]          |      |        |    |

| Access | R  | R     | R       | R   | R              | R    | R      | R  |

| Reset  | х  | x     | x       | x   | x              | x    | х      | x  |

Bits 31:28 – REL[3:0] Core Release

One digit, BCD-coded.

**Bits 27:24 – STEP[3:0]** Step of Core Release One digit, BCD-coded.

**Bits 23:20 – SUBSTEP[3:0]** Sub-step of Core Release One digit, BCD-coded.

### Bits 19:16 – YEAR[3:0] Timestamp Year

One digit, BCD-coded. This field is set by generic parameter on MCAN synthesis.

### Bits 15:8 - MON[7:0] Timestamp Month

Two digits, BCD-coded. This field is set by generic parameter on MCAN synthesis.

### Bits 7:0 - DAY[7:0] Timestamp Day

Two digits, BCD-coded. This field is set by generic parameter on MCAN synthesis.

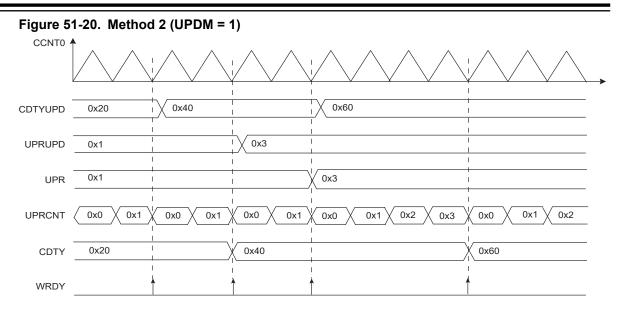

## Pulse Width Modulation Controller (PWM)

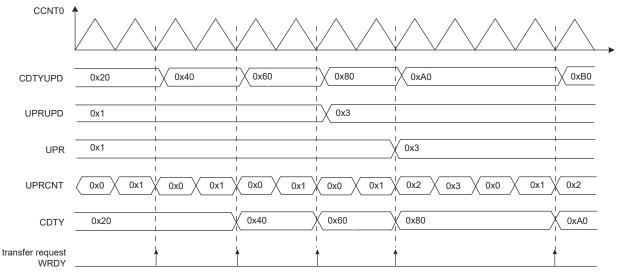

### 51.6.2.9.3 Method 3: Automatic write of duty-cycle values and automatic trigger of the update

In this mode, the update of the duty cycle values is made automatically by the DMA Controller. The update of the period value, the dead-time values and the update period value must be done by writing in their respective update registers with the processor (respectively PWM\_CPRDUPDx, PWM\_DTUPDx and PWM\_SCUPUPD).

To trigger the update of the period value and the dead-time values, the user must use the bit UPDULOCK which allows to update synchronously (at the same PWM period) the synchronous channels:

- If the bit UPDULOCK is set to '1', the update is done at the next PWM period of the synchronous channels.

- If the UPDULOCK bit is not set to '1', the update is locked and cannot be performed.

After writing the UPDULOCK bit to '1', it is held at this value until the update occurs, then it is read 0.

The update of the duty-cycle values and the update period value is triggered automatically after an update period.

To configure the automatic update, the user must define a value for the Update Period by the field UPR in the PWM\_SCUP register. The PWM controller waits UPR+1 periods of synchronous channels before updating automatically the duty values and the update period value.

Using the DMA Controller removes processor overhead by reducing its intervention during the transfer. This significantly reduces the number of clock cycles required for a data transfer, which improves microcontroller performance.

The DMA Controller must write the duty-cycle values in the synchronous channels index order. For example if the channels 0, 1 and 3 are synchronous channels, the DMA Controller must write the duty-cycle of the channel 0 first, then the duty-cycle of the channel 1, and finally the duty-cycle of the channel 3.

The status of the DMA Controller transfer is reported in PWM\_ISR2 by the following flags:

• WRDY: this flag is set to '1' when the PWM Controller is ready to receive new duty-cycle values and a new update period value. It is reset to '0' when PWM\_ISR2 is read. The user can choose to synchronize the WRDY flag and the DMA Controller transfer request with a comparison match (see PWM Comparison Units), by the fields PTRM and PTRCS in the PWM\_SCM register. ٠

• UNRE: this flag is set to '1' when the update period defined by the UPR field has elapsed while the whole data has not been written by the DMA Controller. It is reset to '0' when PWM\_ISR2 is read.

Depending on the interrupt mask in PWM\_IMR2, an interrupt can be generated by these flags.

Sequence for Method 3:

- 1. Select the automatic write of duty-cycle values and automatic update by setting the field UPDM to 2 in the PWM\_SCM register.

- 2. Define the synchronous channels by the bits SYNCx in the PWM\_SCM register.

- 3. Define the update period by the field UPR in the PWM\_SCUP register.

- 4. Define when the WRDY flag and the corresponding DMA Controller transfer request must be set in the update period by the PTRM bit and the PTRCS field in the PWM\_SCM register (at the end of the update period or when a comparison matches).

- 5. Define the DMA Controller transfer settings for the duty-cycle values and enable it in the DMA Controller registers

- 6. Enable the synchronous channels by writing CHID0 in the PWM\_ENA register.

- 7. If an update of the period value and/or of the dead-time values is required, write registers that need to be updated (PWM\_CPRDUPDx, PWM\_DTUPDx), else go to Step 10.

- 8. Set UPDULOCK to '1' in PWM\_SCUC.

- 9. The update of these registers will occur at the beginning of the next PWM period. At this moment the bit UPDULOCK is reset, go to Step 7. for new values.

- 10. If an update of the update period value is required, check first that write of a new update value is possible by polling the flag WRDY (or by waiting for the corresponding interrupt) in PWM\_ISR2, else go to Step 14.

- 11. Write the register that needs to be updated (PWM\_SCUPUPD).

- 12. The update of this register will occur at the next PWM period of the synchronous channels when the Update Period is elapsed. Go to Step 10. for new values.

- 13. Wait for the DMA status flag indicating that the buffer transfer is complete. If the transfer has ended, define a new DMA transfer for new duty-cycle values. Go to Step 5.

### Figure 51-21. Method 3 (UPDM = 2 and PTRM = 0)

# Analog Comparator Controller (ACC)

| Value | Description                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------|

| 0     | No edge occurred (defined by EDGETYP) on analog comparator output since the last read of ACC_ISR.         |

| 1     | A selected edge (defined by EDGETYP) on analog comparator output occurred since the last read of ACC_ISR. |

# **Worldwide Sales and Service**

| AMERICAS                      | ASIA/PACIFIC                             | ASIA/PACIFIC                                  | EUROPE                |

|-------------------------------|------------------------------------------|-----------------------------------------------|-----------------------|

| Corporate Office              | Australia - Sydney                       | India - Bangalore                             | Austria - Wels        |

| 2355 West Chandler Blvd.      | Tel: 61-2-9868-6733                      | Tel: 91-80-3090-4444                          | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199       | China - Beijing                          | India - New Delhi                             | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200             | Tel: 86-10-8569-7000                     | Tel: 91-11-4160-8631                          | Denmark - Copenhagen  |

| <sup>-</sup> ax: 480-792-7277 | China - Chengdu                          | India - Pune                                  | Tel: 45-4450-2828     |

| Fechnical Support:            | Tel: 86-28-8665-5511                     | Tel: 91-20-4121-0141                          | Fax: 45-4485-2829     |

| http://www.microchip.com/     | China - Chongqing                        | Japan - Osaka                                 | Finland - Espoo       |

| support                       | Tel: 86-23-8980-9588                     | Tel: 81-6-6152-7160                           | Tel: 358-9-4520-820   |

| Neb Address:                  | China - Dongguan                         | Japan - Tokyo                                 | France - Paris        |

| www.microchip.com             | Tel: 86-769-8702-9880                    | Tel: 81-3-6880- 3770                          | Tel: 33-1-69-53-63-20 |

| Atlanta                       | China - Guangzhou                        | Korea - Daegu                                 | Fax: 33-1-69-30-90-79 |

| Duluth, GA                    | Tel: 86-20-8755-8029                     | Tel: 82-53-744-4301                           | Germany - Garching    |

| Tel: 678-957-9614             | China - Hangzhou                         | Korea - Seoul                                 | Tel: 49-8931-9700     |

| Fax: 678-957-1455             | Tel: 86-571-8792-8115                    | Tel: 82-2-554-7200                            | Germany - Haan        |

| Austin, TX                    | China - Hong Kong SAR                    | Malaysia - Kuala Lumpur                       | Tel: 49-2129-3766400  |

| Tel: 512-257-3370             | Tel: 852-2943-5100                       | Tel: 60-3-7651-7906                           | Germany - Heilbronn   |

| Boston                        | China - Nanjing                          | Malaysia - Penang                             | Tel: 49-7131-67-3636  |

| Westborough, MA               | Tel: 86-25-8473-2460                     | Tel: 60-4-227-8870                            | Germany - Karlsruhe   |

| Tel: 774-760-0087             | China - Qingdao                          | Philippines - Manila                          | Tel: 49-721-625370    |

| Fax: 774-760-0088             | Tel: 86-532-8502-7355                    | Tel: 63-2-634-9065                            | Germany - Munich      |

|                               |                                          |                                               | Tel: 49-89-627-144-0  |

| Chicago                       | China - Shanghai<br>Tel: 86-21-3326-8000 | Singapore                                     |                       |

| tasca, IL                     |                                          | Tel: 65-6334-8870                             | Fax: 49-89-627-144-44 |

| Tel: 630-285-0071             | China - Shenyang                         | Taiwan - Hsin Chu                             | Germany - Rosenheim   |

| Fax: 630-285-0075             | Tel: 86-24-2334-2829                     | Tel: 886-3-577-8366                           | Tel: 49-8031-354-560  |

| Dallas                        | China - Shenzhen                         | Taiwan - Kaohsiung                            | Israel - Ra'anana     |

| Addison, TX                   | Tel: 86-755-8864-2200                    | Tel: 886-7-213-7830                           | Tel: 972-9-744-7705   |

| Tel: 972-818-7423             | China - Suzhou<br>Tel: 86-186-6233-1526  | Taiwan - Taipei                               | Italy - Milan         |

| Fax: 972-818-2924             | China - Wuhan                            | Tel: 886-2-2508-8600                          | Tel: 39-0331-742611   |

| Detroit                       | Tel: 86-27-5980-5300                     | Thailand - Bangkok                            | Fax: 39-0331-466781   |

| Novi, MI                      | China - Xian                             | Tel: 66-2-694-1351                            | Italy - Padova        |

| Tel: 248-848-4000             | Tel: 86-29-8833-7252                     | Vietnam - Ho Chi Minh<br>Tel: 84-28-5448-2100 | Tel: 39-049-7625286   |

| Houston, TX                   | China - Xiamen                           | 161. 04-20-3440-2100                          | Netherlands - Drunen  |

| Tel: 281-894-5983             | Tel: 86-592-2388138                      |                                               | Tel: 31-416-690399    |

| ndianapolis                   | China - Zhuhai                           |                                               | Fax: 31-416-690340    |

| Noblesville, IN               | Tel: 86-756-3210040                      |                                               | Norway - Trondheim    |

| Tel: 317-773-8323             | Tel. 80-750-5210040                      |                                               | Tel: 47-7289-7561     |

| Fax: 317-773-5453             |                                          |                                               | Poland - Warsaw       |

| Tel: 317-536-2380             |                                          |                                               | Tel: 48-22-3325737    |

| Los Angeles                   |                                          |                                               | Romania - Bucharest   |

| Mission Viejo, CA             |                                          |                                               | Tel: 40-21-407-87-50  |

| Tel: 949-462-9523             |                                          |                                               | Spain - Madrid        |

| <sup>=</sup> ax: 949-462-9608 |                                          |                                               | Tel: 34-91-708-08-90  |

| Tel: 951-273-7800             |                                          |                                               | Fax: 34-91-708-08-91  |

| Raleigh, NC                   |                                          |                                               | Sweden - Gothenberg   |

| Tel: 919-844-7510             |                                          |                                               | Tel: 46-31-704-60-40  |

| New York, NY                  |                                          |                                               | Sweden - Stockholm    |

| Tel: 631-435-6000             |                                          |                                               | Tel: 46-8-5090-4654   |

| San Jose, CA                  |                                          |                                               | UK - Wokingham        |

| Tel: 408-735-9110             |                                          |                                               | Tel: 44-118-921-5800  |

| Tel: 408-436-4270             |                                          |                                               | Fax: 44-118-921-5820  |

| Canada - Toronto              |                                          |                                               |                       |

| Tel: 905-695-1980             |                                          |                                               |                       |

|                               |                                          |                                               |                       |

Fax: 905-695-2078