Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 300MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 114                                                                              |

| Program Memory Size        | 2MB (2M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 384K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.08V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LFBGA                                                                        |

| Supplier Device Package    | 144-LFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsams70q21b-cnt       |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- RTC Mode Register

- RTC Time Alarm Register

- RTC Calendar Alarm Register

- General Purpose Backup Registers

- Supply Controller Control Register

- Supply Controller Supply Monitor Mode Register

- Supply Controller Mode Register

- Supply Controller Wakeup Mode Register

- Supply Controller Wakeup Inputs Register

### 23.4.11 Register Bits in Backup Domain (VDDIO)

The following configuration registers, or certain bits of the registers, are physically located in the product backup domain:

- RSTC Mode Register (all bits)

- RTT Mode Register (all bits)

- RTT Alarm Register (all bits)

- RTC Control Register (all bits)

- RTC Mode Register (all bits)

- RTC Time Alarm Register (all bits)

- RTC Calendar Alarm Register (all bits)

- General Purpose Backup Registers (all bits)

- Supply Controller Control Register (see register description for details)

- Supply Controller Supply Monitor Mode Register (all bits)

- Supply Controller Mode Register (see register description for details)

- Supply Controller Wakeup Mode Register (all bits)

- Supply Controller Wakeup Inputs Register (all bits)

- Supply Controller Status Register (all bits)

## Static Memory Controller (SMC)

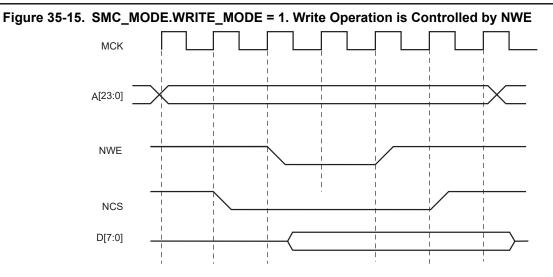

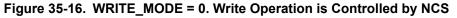

#### 35.9.4.2 Write is Controlled by NCS (SMC.MODE.WRITE\_MODE = 0)

The following figure shows the waveforms of a write operation with SMC\_MODE.WRITE\_MODE cleared. The data is put on the bus during the pulse and hold steps of the NCS signal. The internal data buffers are switched to Output mode after the NCS\_WR\_SETUP time, and until the end of the write cycle, regardless of the programmed waveform on NWE.

#### 35.9.5 Register Write Protection

To prevent any single software error that may corrupt SMC behavior, the registers listed below can be write-protected by setting the WPEN bit in the SMC Write Protection Mode register (SMC\_WPMR).

If a write access in a write-protected register is detected, the WPVS flag in the SMC Write Protection Status register (SMC\_WPSR) is set and the field WPVSRC indicates in which register the write access has been attempted.

The WPVS flag is automatically cleared after reading the SSMC\_WPSR.

The following registers can be write-protected:

- "SMC Setup Register"

- "SMC Pulse Register"

### Static Memory Controller (SMC)

| Parameter    | Value           | Definition                                      |

|--------------|-----------------|-------------------------------------------------|

| NCS_RD_PULSE | t <sub>pa</sub> | Access time of first access to the page.        |

| NRD_SETUP    | 'x'             | No impact.                                      |

| NRD_PULSE    | t <sub>sa</sub> | Access time of subsequent accesses in the page. |

| NRD_CYCLE    | 'X'             | No impact.                                      |

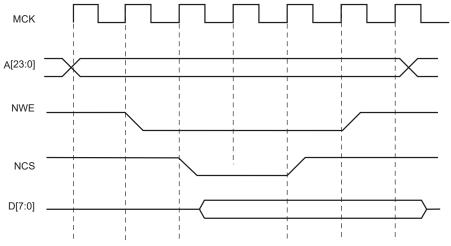

The SMC does not check the coherency of timings. It will always apply the NCS\_RD\_PULSE timings as page access timing ( $t_{pa}$ ) and the NRD\_PULSE for accesses to the page ( $t_{sa}$ ), even if the programmed value for  $t_{pa}$  is shorter than the programmed value for  $t_{sa}$ .

#### 35.15.2 Page Mode Restriction

The Page mode is not compatible with the use of the NWAIT signal. Using the Page mode and the NWAIT signal may lead to unpredictable behavior.

#### 35.15.3 Sequential and Non-sequential Accesses

If the chip select and the MSB of addresses as defined in Table 35-7 are identical, then the current access lies in the same page as the previous one, and no page break occurs.

Using this information, all data within the same page, sequential or not sequential, are accessed with a minimum access time ( $t_{sa}$ ). The following figure illustrates access to an 8-bit memory device in Page mode, with 8-byte pages. Access to D1 causes a page access with a long access time ( $t_{pa}$ ). Accesses to D3 and D7, though they are not sequential accesses, only require a short access time ( $t_{sa}$ ).

If the MSB of addresses are different, the SMC performs the access of a new page. In the same way, if the chip select is different from the previous access, a page break occurs. If two sequential accesses are made to the Page mode memory, but separated by an other internal or external peripheral access, a page break occurs on the second access because the chip select of the device was deasserted between both accesses.

Figure 35-36. Access to Non-Sequential Data within the Same Page

# Static Memory Controller (SMC)

# 35.16 Register Summary

| Offset   | Name           | Bit Pos. |       |            |              |            |            |                   |

|----------|----------------|----------|-------|------------|--------------|------------|------------|-------------------|

|          |                | 7:0      |       |            | NWE_SE       | TUP[5:0]   |            |                   |

| 0x00     | SMC SETUDIO 31 | 15:8     |       |            | NCS_WR_      | SETUP[5:0] |            |                   |

| 0,00     | SMC_SETUP[03]  | 23:16    |       |            | NRD_SE       | TUP[5:0]   |            |                   |

|          |                | 31:24    |       |            | NCS_RD_      | SETUP[5:0] |            |                   |

|          |                | 7:0      |       | N          | IWE_PULSE[6: | 0]         |            |                   |

| 0x00     |                | 15:8     |       | NC         | S_WR_PULSE   | [6:0]      |            |                   |

| 0,00     | SMC_PULSE[03]  | 23:16    |       | Ν          | IRD_PULSE[6: | 0]         |            |                   |

|          |                | 31:24    |       | NC         | S_RD_PULSE   | [6:0]      |            |                   |

|          |                | 7:0      |       | NWE_C)     | /CLE[7:0]    |            |            |                   |

|          |                | 15:8     |       |            |              |            |            | NWE_CYCLE<br>8:8] |

| 0x00     | SMC_CYCLE[03]  | 23:16    |       | NRD CY     | /CLE[7:0]    |            |            | ,                 |

|          |                |          |       | _          |              |            |            | NRD_CYCLE[        |

|          |                | 31:24    |       |            |              |            |            | 8:8]              |

|          |                | 7:0      | EXNW_ | _MODE[1:0] |              |            | WRITE_MOD  |                   |

| 0x00     | SMC_MODE[03]   | 15:8     |       | DBW        |              |            |            | BAT               |

| 0X00     | omo_mobilionol | 23:16    |       | TDF_MODE   |              | TDE C      | /CLES[3:0] |                   |

|          |                | 31:24    | p     | S[1:0]     |              |            | 0120[0:0]  | PMEN              |

| 0x04     |                |          |       | -[]        |              |            |            |                   |

| <br>0x7F | Reserved       |          |       |            |              |            |            |                   |

|          |                | 7:0      |       |            |              |            |            | SMSE              |

|          |                | 15:8     |       |            | CS3SE        | CS2SE      | CS1SE      | CS0SE             |

| 0x80     | SMC_OCMS       | 23:16    |       |            |              |            |            |                   |

|          |                | 31:24    |       |            |              |            |            |                   |

|          |                | 7:0      |       | KEY        | 1[7:0]       |            |            |                   |

|          |                | 15:8     |       |            | [15:8]       |            |            |                   |

| 0x84     | SMC_KEY1       | 23:16    |       | KEY1       | [23:16]      |            |            |                   |

|          |                | 31:24    |       | KEY1       | [31:24]      |            |            |                   |

|          |                | 7:0      |       | KEY        | 2[7:0]       |            |            |                   |

|          |                | 15:8     |       |            | 2[15:8]      |            |            |                   |

| 0x88     | SMC_KEY2       | 23:16    |       |            | [23:16]      |            |            |                   |

|          |                | 31:24    |       |            | [31:24]      |            |            |                   |

| 0x8C     |                |          |       |            |              |            |            |                   |

| <br>0xE3 | Reserved       |          |       |            |              |            |            |                   |

|          |                | 7:0      |       |            |              |            |            | WPEN              |

| . –      |                | 15:8     |       | WPKE       | EY[7:0]      |            |            |                   |

| 0xE4     | SMC_WPMR       | 23:16    |       |            | Y[15:8]      |            |            |                   |

|          |                | 31:24    |       |            | Y[23:16]     |            |            |                   |

|          |                | 7:0      |       |            |              |            |            | WPVS              |

| 0xE8     | SMC_WPSR       | 15:8     |       | WPVS       |              |            |            |                   |

## Static Memory Controller (SMC)

The NCS pulse length must be at least 1 clock cycle.

**Bits 6:0 – NWE\_PULSE[6:0]** NWE Pulse Length The NWE signal pulse length is defined as:

NWE pulse length = (256\* NWE\_PULSE[6] + NWE\_PULSE[5:0]) clock cycles

The NWE pulse length must be at least 1 clock cycle.

# **GMAC - Ethernet MAC**

| Offset  | Name             | Bit Pos. |                   |                   |  |  |  |  |

|---------|------------------|----------|-------------------|-------------------|--|--|--|--|

|         |                  | 7:0      |                   | MASKVAL[7:0]      |  |  |  |  |

|         |                  | 15:8     |                   | MASKVAL[15:8]     |  |  |  |  |

| 0x07A8  | GMAC_ST2CW021    | 23:16    |                   | COMPVAL[7:0]      |  |  |  |  |

|         |                  | 31:24    |                   | COMPVAL[15:8]     |  |  |  |  |

|         |                  | 7:0      | OFFSSTRT[0:<br>0] | OFFSVAL[6:0]      |  |  |  |  |

| 0x07AC  | GMAC_ST2CW121    | 15:8     |                   | OFFSSTRT[1:<br>1] |  |  |  |  |

|         |                  | 23:16    |                   |                   |  |  |  |  |

|         |                  | 31:24    |                   |                   |  |  |  |  |

|         |                  | 7:0      |                   | MASKVAL[7:0]      |  |  |  |  |

| 0x07B0  | GMAC_ST2CW022    | 15:8     |                   | MASKVAL[15:8]     |  |  |  |  |

| 0,07,00 | GIVIAC_ST2CVV022 | 23:16    |                   | COMPVAL[7:0]      |  |  |  |  |

|         |                  | 31:24    |                   | COMPVAL[15:8]     |  |  |  |  |

|         | GMAC_ST2CW122    | 7:0      | OFFSSTRT[0:<br>0] | OFFSVAL[6:0]      |  |  |  |  |

| 0x07B4  |                  | 15:8     |                   | OFFSSTRT[1:<br>1] |  |  |  |  |

|         |                  | 23:16    |                   |                   |  |  |  |  |

|         |                  | 31:24    |                   |                   |  |  |  |  |

|         |                  | 7:0      |                   | MASKVAL[7:0]      |  |  |  |  |

| 0x07B8  | GMAC_ST2CW023    | 15:8     |                   | MASKVAL[15:8]     |  |  |  |  |

| 0.07 00 | GNAC_31200023    | 23:16    |                   | COMPVAL[7:0]      |  |  |  |  |

|         |                  | 31:24    |                   | COMPVAL[15:8]     |  |  |  |  |

|         | GMAC_ST2CW123    | 7:0      | OFFSSTRT[0:<br>0] | OFFSVAL[6:0]      |  |  |  |  |

| 0x07BC  |                  | 15:8     |                   | OFFSSTRT[1:<br>1] |  |  |  |  |

|         |                  | 23:16    |                   |                   |  |  |  |  |

|         |                  | 31:24    |                   |                   |  |  |  |  |

#### 38.8.14 GMAC PHY Maintenance Register

| Name:     | GMAC_MAN   |

|-----------|------------|

| Offset:   | 0x034      |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register is a shift register. Writing to it starts a shift operation which is signaled completed when bit 2 is set in the Network Status Register (GMAC\_NSR). It takes about 2000 MCK cycles to complete, when MDC is set for MCK divide by 32 in the Network Configuration Register. An interrupt is generated upon completion.

During this time, the MSB of the register is output on the MDIO pin and the LSB updated from the MDIO pin with each MDC cycle. This causes transmission of a PHY management frame on MDIO. Refer also to section 22.2.4.5 of the IEEE 802.3 standard.

Reading during the shift operation returns the current contents of the shift register. At the end of management operation, the bits will have shifted back to their original locations. For a read operation, the data bits are updated with data read from the PHY. It is important to write the correct values to the register to ensure a valid PHY management frame is produced.

The MDIO interface can read IEEE 802.3 clause 45 PHYs, as well as clause 22 PHYs. To read clause 45 PHYs, bit 30 should be written with a '0' rather than a '1'. To write clause 45 PHYs, bits 31:28 should be written as 0x1:

| РНҮ       | Access         | Bit Value |       |       |       |

|-----------|----------------|-----------|-------|-------|-------|

|           |                | wzo       | CLTTO | OP[1] | OP[0] |

| Clause 22 | Read           | 0         | 1     | 1     | 0     |

|           | Write          | 0         | 1     | 0     | 1     |

| Clause 45 | Read           | 0         | 0     | 1     | 1     |

|           | Write          | 0         | 0     | 0     | 1     |

|           | Read + Address | 0         | 0     | 1     | 0     |

For a description of MDC generation, see also the 'GMAC Network Configuration Register' (GMAC\_NCR) description.

## **USB High-Speed Interface (USBHS)**

| Value | Name | Description                                                             | I |

|-------|------|-------------------------------------------------------------------------|---|

|       |      | • for OUT endpoint, USBHS_DEVEPTIMRx.NBUSYBKE = 1 and all the banks are | 1 |

|       |      | busy.                                                                   |   |

#### Bits 9:8 – DTSEQ[1:0] Data Toggle Sequence

This field is set to indicate the PID of the current bank:

For IN transfers, it indicates the data toggle sequence that should be used for the next packet to be sent. This is not relative to the current bank.

For OUT transfers, this value indicates the last data toggle sequence received on the current bank.

By default, DTSEQ is 0b01, as if the last data toggle sequence was Data1, so the next sent or expected data toggle sequence should be Data0.

| Value | Name  | Description                                      |

|-------|-------|--------------------------------------------------|

| 0     | DATA0 | Data0 toggle sequence                            |

| 1     | DATA1 | Data1 toggle sequence                            |

| 2     | DATA2 | Reserved for high-bandwidth isochronous endpoint |

| 3     | MDATA | Reserved for high-bandwidth isochronous endpoint |

#### Bit 7 - SHORTPACKET Short Packet Interrupt

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Cleared when SHORTPACKETC = 1. This acknowledges the interrupt.                           |

| 1     | Set for non-control OUT endpoints, when a short packet has been received. This triggers a |

|       | PEP_x interrupt if USBHS_DEVEPTIMRx.SHORTPACKETE = 1.                                     |

#### Bit 6 - STALLEDI STALLed Interrupt

| Value | Description                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Cleared when STALLEDIC = 1. This acknowledges the interrupt.                                                                                                                                     |

| 1     | Set to signal that a STALL handshake has been sent. To do that, the software has to set the STALLRQ bit (by writing a one to the STALLRQS bit). This triggers a PEP_x interrupt if STALLEDE = 1. |

#### Bit 5 – OVERFI Overflow Interrupt

For all endpoint types, an overflow can occur during the OUT stage if the host attempts to write into a bank that is too small for the packet. The packet is acknowledged and the

USBHS\_DEVEPTISRx.RXOUTI bit is set as if no overflow had occurred. The bank is filled with all the first bytes of the packet that fit in.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | Cleared when the OVERFIC bit is written to one. This acknowledges the interrupt.  |

| 1     | Set when an overflow error occurs. This triggers a PEP_x interrupt if OVERFE = 1. |

#### Bit 4 – NAKINI NAKed IN Interrupt

| Value | Description                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0     | Cleared when NAKINIC = 1. This acknowledges the interrupt.                                                                        |

| 1     | Set when a NAK handshake has been sent in response to an IN request from the host. This triggers a PEP_x interrupt if NAKINE = 1. |

# USB High-Speed Interface (USBHS)

USBHS\_DEVEPTISRx.TXINI and USBHS\_DEVEPTIMRx.FIFOCON bits are set/cleared in accordance with the status of the next bank.

This bit is inactive (cleared) for bulk and interrupt OUT endpoints.

## **USB High-Speed Interface (USBHS)**

- Bit 2 RXSTPIS Received SETUP Interrupt Set

- Bit 1 RXOUTIS Received OUT Data Interrupt Set

- Bit 0 TXINIS Transmitted IN Data Interrupt Set

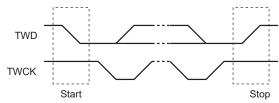

#### 43.4.1 I/O Lines Description

#### Table 43-3. I/O Lines Description

| Pin Name | Pin Description       | Туре         |

|----------|-----------------------|--------------|

| TWD      | Two-wire Serial Data  | Input/Output |

| TWCK     | Two-wire Serial Clock | Input/Output |

#### 43.5 **Product Dependencies**

#### 43.5.1 I/O Lines

Both TWD and TWCK are bidirectional lines, connected to a positive supply voltage via a current source or pullup resistor. When the bus is free, both lines are high. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function.

TWD and TWCK pins may be multiplexed with PIO lines. To enable the TWIHS, the user must program the PIO Controller to dedicate TWD and TWCK as peripheral lines. When High-speed Slave mode is enabled, the analog pad filter must be enabled.

The user must not program TWD and TWCK as open-drain. This is already done by the hardware.

#### 43.5.2 Power Management

Enable the peripheral clock.

The TWIHS may be clocked through the Power Management Controller (PMC), thus the user must first configure the PMC to enable the TWIHS clock.

#### 43.5.3 Interrupt Sources

The TWIHS has an interrupt line connected to the Interrupt Controller. In order to handle interrupts, the Interrupt Controller must be programmed before configuring the TWIHS.

### 43.6 Functional Description

#### 43.6.1 Transfer Format

The data put on the TWD line must be 8 bits long. Data is transferred MSB first; each byte must be followed by an acknowledgement. The number of bytes per transfer is unlimited, shown in Transfer Format.

Each transfer begins with a START condition and terminates with a STOP condition, as shown in Figure 43-2.

- A high-to-low transition on the TWD line while TWCK is high defines the START condition.

- A low-to-high transition on the TWD line while TWCK is high defines the STOP condition.

#### Figure 43-2. START and STOP Conditions

#### 46.6.9.14.7 Header Timeout Error

This error is generated in slave node configuration, if the Header is not entirely received within the time given by the maximum length of the Header, t<sub>Header Maximum</sub>.

This error is reported by flag US\_CSR.LINHTE.

#### 46.6.9.15 LIN Frame Handling

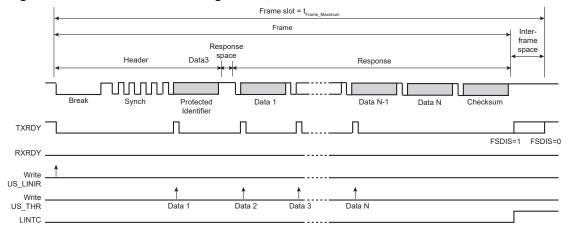

#### 46.6.9.15.1 Master Node Configuration

- Write TXEN and RXEN in US\_CR to enable both the transmitter and the receiver.

- Write USART\_MODE in US\_MR to select the LIN mode and the master node configuration.

- Write CD and FP in US\_BRGR to configure the baud rate.

- Write NACT, PARDIS, CHKDIS, CHKTYPE, DLCM, FSDIS and DLC in US\_LINMR to configure the frame transfer.

- Check that TXRDY in US\_CSR is set to 1.

- Write IDCHR in US\_LINIR to send the header.

What comes next depends on the NACT configuration:

- Case 1: NACT = PUBLISH, the USART sends the response

- Wait until TXRDY in US\_CSR rises.

- Write TCHR in US\_THR to send a byte.

- If all the data have not been written, redo the two previous steps.

- Wait until LINTC in US\_CSR rises.

- Check the LIN errors.

- Case 2: NACT = SUBSCRIBE, the USART receives the response

- Wait until RXRDY in US\_CSR rises.

- Read RCHR in US\_RHR.

- If all the data have not been read, redo the two previous steps.

- Wait until LINTC in US\_CSR rises.

- Check the LIN errors.

- Case 3: NACT = IGNORE, the USART is not concerned by the response.

- Wait until LINTC in US\_CSR rises.

- Check the LIN errors.

#### Figure 46-45. Master Node Configuration, NACT = PUBLISH

# Universal Synchronous Asynchronous Receiver Transc...

|        | Name:<br>Offset:<br>Reset:<br>Property: | US_RHR<br>0x0018<br>0x0<br>Read-only |    |    |         |    |    |            |

|--------|-----------------------------------------|--------------------------------------|----|----|---------|----|----|------------|

| Bit    | 31                                      | 30                                   | 29 | 28 | 27      | 26 | 25 | 24         |

|        |                                         |                                      |    |    |         |    |    |            |

| Access |                                         | -                                    |    |    |         |    |    |            |

| Reset  |                                         |                                      |    |    |         |    |    |            |

|        |                                         |                                      |    |    |         |    |    |            |

| Bit    | 23                                      | 22                                   | 21 | 20 | 19      | 18 | 17 | 16         |

|        |                                         |                                      |    |    |         |    |    |            |

| Access |                                         |                                      |    |    |         |    |    |            |

| Reset  |                                         |                                      |    |    |         |    |    |            |

| -      |                                         |                                      | 10 | 10 |         | 10 |    |            |

| Bit    |                                         | 14                                   | 13 | 12 | 11      | 10 | 9  | 8          |

|        | RXSYNH                                  |                                      |    |    |         |    |    | RXCHR[8:8] |

| Access |                                         |                                      |    |    |         |    |    |            |

| Reset  | 0                                       |                                      |    |    |         |    |    | 0          |

| Bit    | 7                                       | 6                                    | 5  | 4  | 3       | 2  | 1  | 0          |

| DIL    | I                                       | 0                                    | 5  |    | IR[7:0] | ۷  | 1  |            |

| Access |                                         |                                      |    |    |         |    |    |            |

| Reset  | 0                                       | 0                                    | 0  | 0  | 0       | 0  | 0  | 0          |

| NESEL  | U                                       | 0                                    | 0  | U  | U       | U  | U  | 0          |

### 46.7.21 USART Receive Holding Register

Bit 15 - RXSYNH Received Sync

| Value | Description                           |

|-------|---------------------------------------|

| 0     | Last character received is a data.    |

| 1     | Last character received is a command. |

**Bits 8:0 – RXCHR[8:0]** Received Character Last character received if RXRDY is set.

# Media Local Bus (MLB)

| Field | No. of<br>Bits | Description                                                                                                                             | Accessibility                            |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|       |                | 1 = Enabled                                                                                                                             |                                          |

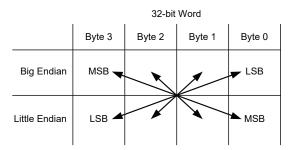

| LE    | 1              | Endianess select:<br>0 = Big Endian<br>1 = Little Endian                                                                                | r,w                                      |

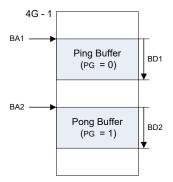

| PG    | 1              | Page pointer. Software initializes to zero, hardware<br>writes thereafter.<br>0 = Ping buffer<br>1 = Pong buffer                        | r,w,u <sup>(1)</sup>                     |

| RDY1  | 1              | Buffer ready bit for ping buffer page:<br>0 = Not ready<br>1 = Ready                                                                    | r,w                                      |

| RDY2  | 1              | Buffer ready bit for pong buffer page:<br>0 = Not ready<br>1 = Ready                                                                    | r,w                                      |

| DNE1  | 1              | Buffer done bit for ping buffer page:<br>0 = Not done<br>1 = Done                                                                       | r,u <sup>(1)</sup> ,c0                   |

| DNE2  | 1              | Buffer done bit for pong buffer page:<br>0 = Not done<br>1 = Done                                                                       | r,u <sup>(1)</sup> ,c0                   |

| ERR1  | 1              | <ul><li>AHB error response detected for ping buffer page:</li><li>0 = No error</li><li>1 = Error</li></ul>                              | r,u <sup>(1)</sup> ,c0 <sup>(2)</sup>    |

| ERR2  | 1              | AHB error response detected for pong buffer page:<br>0 = No error<br>1 = Error                                                          | r,u <sup>(1)</sup> ,c0 <sup>(2)</sup>    |

| PS1   | 1              | Packet start bit for ping buffer page:<br>0 = No packet start<br>1 = Packet start<br>Reserved for synchronous and isochronous channels. | r,w,u <sup>(1)</sup> (both Tx and<br>Rx) |

| PS2   | 1              | Packet start bit for pong buffer page:<br>0 = No packet start<br>1 = Packet start                                                       | r,w,u <sup>(1)</sup> (both Tx and<br>Rx) |

#### Figure 48-20. Endianness Overview

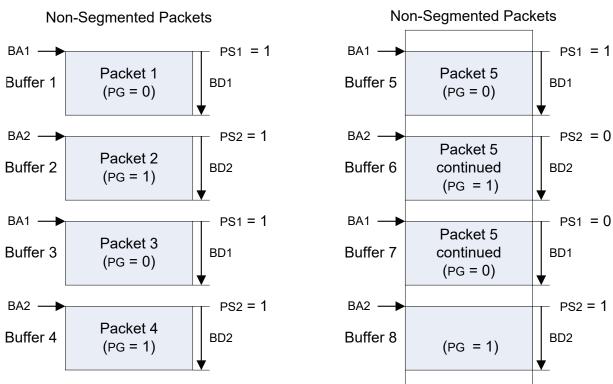

The following figure shows an example of the ping-pong system memory structure. This system memory structure is similar for all channel types and shows the relationship between the BAn, BDn, and PG descriptor fields.

#### Figure 48-21. Ping-Pong System Memory Structure

Each ADT entry holds a 32-bit BAn field which defines the start of each ping or pong buffer within system memory. The BDn field is used to indicate the size for the respective ping or pong page. The maximum size is 2k-entries for asynchronous and control channels; 8k-entries for isochronous and synchronous channels.

### AHB Synchronous Channel Descriptors

Table 48-21 shows the format for a synchronous ADT entry. The field definitions are defined in Table48-22. Each synchronous channel buffer can be up to 8k-bytes deep.

| Table 48-21. | Synchronous | S ADT Entr | y Format |  |

|--------------|-------------|------------|----------|--|

|              |             |            |          |  |

| Bit Offset | 15        | 14         | 13   | 12        | 11       | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|-----------|------------|------|-----------|----------|----|---|---|---|---|---|---|---|---|---|---|

| 0          | CE        | LE         | PG   | Rese      | Reserved |    |   |   |   |   |   |   |   |   |   |   |

| 16         | Reserved  | Reserved   |      |           |          |    |   |   |   |   |   |   |   |   |   |   |

| 32         | RDY1      | DNE1       | ERR1 | BD1[      | 12:0]    |    |   |   |   |   |   |   |   |   |   |   |

| 48         | RDY2      | DNE2       | ERR2 | BD2[12:0] |          |    |   |   |   |   |   |   |   |   |   |   |

| 64         | BA1[15:0] |            |      |           |          |    |   |   |   |   |   |   |   |   |   |   |

| 80         | BA1[31:16 | BA1[31:16] |      |           |          |    |   |   |   |   |   |   |   |   |   |   |

| 96         | BA2[15:0] | 3A2[15:0]  |      |           |          |    |   |   |   |   |   |   |   |   |   |   |

| 112        | BA2[31:16 | 3A2[31:16] |      |           |          |    |   |   |   |   |   |   |   |   |   |   |

### **AHB** Isochronous Channel Descriptors

### Figure 48-22. Single-packet Asynchronous or Control System Memory Structure

| Table 48-23. | Single-packet As   | vnchronous and  | Control Entry Format |

|--------------|--------------------|-----------------|----------------------|

|              | olingio publicitio | ynoni onoao ana |                      |

| Bit Offset | 15       | 14         | 13   | 12                 | 11       | 10  | 9    | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----------|------------|------|--------------------|----------|-----|------|----|---|---|---|---|---|---|---|---|

| 0          | CE       | LE         | PG   | Reser              | Reserved |     |      |    |   |   |   |   |   |   |   |   |

| 16         | Reserved | Reserved   |      |                    |          |     |      |    |   |   |   |   |   |   |   |   |

| 32         | RDY1     | DNE1       | ERR1 | PS1                | MEP1     | BD1 | [10: | 0] |   |   |   |   |   |   |   |   |

| 48         | RDY2     | DNE2       | ERR2 | PS2 MEP2 BD2[10:0] |          |     |      |    |   |   |   |   |   |   |   |   |

| 64         | BA1[15:0 | ני         |      |                    |          |     |      |    |   |   |   |   |   |   |   |   |

| 80         | BA1[31:1 | BA1[31:16] |      |                    |          |     |      |    |   |   |   |   |   |   |   |   |

| 96         | BA2[15:0 | BA2[15:0]  |      |                    |          |     |      |    |   |   |   |   |   |   |   |   |

| 112        | BA2[31:1 | BA2[31:16] |      |                    |          |     |      |    |   |   |   |   |   |   |   |   |

#### Multiple-packet Mode

The multiple-packet mode asynchronous and control buffering scheme supports more than one packet per system memory buffer, as shown in the following figure. Multiple- packet mode reduces the interrupt rate for packet channels at the cost of increasing buffering and latency.

For Tx packet channels in multiple-packet mode, software sets the packet start bit (PSn) for every buffer. Setting PSn informs hardware that the first two bytes of the buffer contains the port message length (PML) of the first packet. After the first packet, hardware keeps track of where packets start and end within the current buffer. Software should not write to PSn while the buffer is active (RDYn = 1 and DNEn = 0). For Tx packet channels, the buffer is done (DNEn= 1) when the last byte of the last packet in the

© 2018 Microchip Technology Inc.

### **Controller Area Network (MCAN)**

| Filter<br>Element | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |

|-------------------|----------------------------|----------------------------|--------------------------|

| 0                 | ID message 1               | 0                          | 0                        |

| 1                 | ID message 2               | 0                          | 1                        |

| 2                 | ID message 3               | 0                          | 2                        |

#### Table 49-3. Example Filter Configuration for Rx Buffers

After the last word of a matching received message has been written to the Message RAM, the respective New Data flag in the New Data 1 register (MCAN\_NDAT1) and New Data 2 register (MCAN\_NDAT2) is set. As long as the New Data flag is set, the respective Rx Buffer is locked against updates from received matching frames. The New Data flags have to be reset by the processor by writing a '1' to the respective bit position.

While an Rx Buffer's New Data flag is set, a Message ID Filter Element referencing this specific Rx Buffer will not match, causing the acceptance filtering to continue. Following Message ID Filter Elements may cause the received message to be stored into another Rx Buffer, or into an Rx FIFO, or the message may be rejected, depending on filter configuration.

#### 49.5.4.3.1 Rx Buffer Handling

- Reset interrupt flag IR.DRX

- Read New Data registers

- Read messages from Message RAM

- Reset New Data flags of processed messages

#### 49.5.4.4 Debug on CAN Support

Debug messages are stored into Rx Buffers. For debug handling three consecutive Rx buffers (e.g. #61, #62, #63) have to be used for storage of debug messages A, B, and C. The format is the same as for an Rx Buffer or an Rx FIFO element (see Rx Buffer and FIFO Element).

Advantage: Fixed start address for the DMA transfers (relative to MCAN\_RXBC.RBSA), no additional configuration required.

For filtering of debug messages Standard / Extended Filter Elements with SFEC / EFEC = '111' have to be set up. Messages matching these filter elements are stored into the Rx Buffers addressed by SFID2 / EFID2[5:0].

After message C has been stored, the DMA request output m\_can\_dma\_req is activated and the three messages can be read from the Message RAM under DMA control. The RAM words holding the debug messages will not be changed by the MCAN while m\_can\_dma\_req is activated. The behavior is similar to that of an Rx Buffer with its New Data flag set.

After the DMA has completed, the MCAN is prepared to receive the next set of debug messages.

#### 49.5.4.4.1 Filtering for Debug Messages

Filtering for debug messages is done by configuring one Standard / Extended Message ID Filter Element for each of the three debug messages. To enable a filter element to filter for debug messages SFEC / EFEC has to be programmed to "111". In this case fields SFID1 / SFID2 and EFID1 / EFID2 have a different meaning. While SFID2 / EFID2[10:9] controls the debug message handling state machine, SFID2 / EFID2[5:0] controls the location for storage of a received debug message.

When a debug message is stored, neither the respective New Data flag nor MCAN\_IR.DRX are set. The reception of debug messages can be monitored via RXF1S.DMS.

## Pulse Width Modulation Controller (PWM)

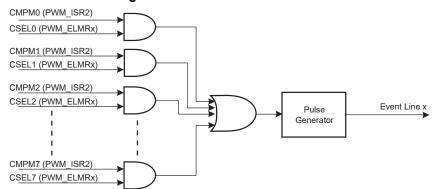

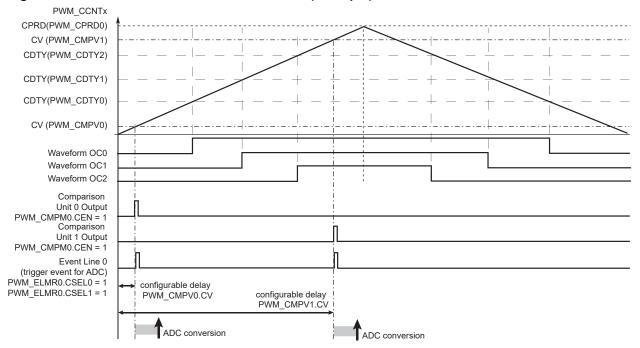

#### Figure 51-25. Event Line Block Diagram

#### Figure 51-26. Event Line Generation Waveform (Example)

#### 51.6.5 PWM External Trigger Mode

The PWM channels 1 and 2 can be configured to use an external trigger for generating specific PWM signals. The external trigger source can be selected through the bit TRGSRC of the PWM External Trigger Register (see the table below).

| Table 51-5. External Event Source Selection |

|---------------------------------------------|

|---------------------------------------------|

| Channel | Trigger Source Selection | Trigger Source                    |

|---------|--------------------------|-----------------------------------|

| 1       | PWM_ETRG1.TRGSRC = 0     | From PWMEXTRG1 input              |

|         | PWM_ETRG1.TRGSRC = 1     | From Analog Comparator Controller |

| 2       | PWM_ETRG2.TRGSRC = 0     | From PWMEXTRG2 input              |

|         | PWM_ETRG2.TRGSRC = 1     | From Analog Comparator Controller |

Each external trigger source can be filtered by writing a one to the TRGFILT bit in the corresponding PWM External Trigger Register (PWM\_ETRGx).

## **Advanced Encryption Standard (AES)**

Encryption or Decryption Process

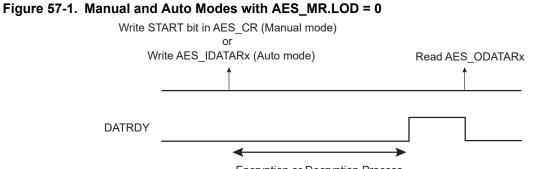

If the user does not want to read AES\_ODATARx between each encryption/decryption, the DATRDY flag will not be cleared. If the DATRDY flag is not cleared, the user cannot know the end of the following encryptions/decryptions.

#### 57.4.3.1.2 If AES\_MR.LOD = 1

This mode is optimized to process AES CBC-MAC operating mode.

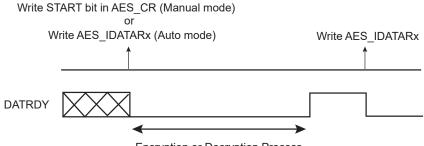

The DATRDY flag is cleared when at least one AES\_IDATAR is written (see the figure below). No additional AES\_ODATAR reads are necessary between consecutive encryptions/decryptions.

#### Figure 57-2. Manual and Auto Modes with AES\_MR.LOD = 1

Encryption or Decryption Process

#### 57.4.3.2 DMA Mode

#### 57.4.3.2.1 If AES\_MR.LOD = 0

This mode may be used for all AES operating modes except CBC-MAC where AES\_MR.LOD = 1 mode is recommended.

The end of the encryption/decryption is indicated by the end of DMA transfer associated to AES\_ODATARx (see the figure below). Two DMA channels are required: one for writing message blocks to AES\_IDATARx and one to obtain the result from AES\_ODATARx.

#### Figure 57-3. DMA Transfer with AES\_MR.LOD = 0

Enable DMA Channels associated to AES\_IDATARx and AES\_ODATARx

Multiple Encryption or Decryption Processes

Multiple Encryption or Decryption Processes

Write accesses into AES\_IDATARx

Write accesses into AES\_IDATARx

Message fully processed

(cipher or decipher) last

block can be read

# **59.** Electrical Characteristics for SAM E70/S70

## 59.1 Absolute Maximum Ratings

## Table 59-1. Absolute Maximum Ratings\*

| Storage Temperature -60°C to + 150°C<br>Voltage on Input Pins<br>with Respect to Ground -0.3V to + 4.0V<br>Maximum Operating Voltage<br>VDDPLL, VDDUTMIC, VDDCORE 1.4V<br>Maximum Operating Voltage<br>VDDIO, VDDUTMII, VDDPLLUSB, VDDIN | *Notice: Stresses beyond those listed under "Absolute<br>Maximum Ratings" may cause permanent damage to<br>the device. This is a stress rating only and functional<br>operation of the device at these or other conditions<br>beyond those indicated in the operational sections of<br>this specification is not implied. Exposure to absolute<br>maximum rating conditions for extended periods may<br>affect device reliability. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0V                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Total DC Output Current on all I/O lines: 150 mA                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 59-2. Recommended Thermal Operating Conditions

| Symbol          | Parameter                                        | Conditions                               | Minimum | Typical | Maximum | Unit |

|-----------------|--------------------------------------------------|------------------------------------------|---------|---------|---------|------|

| T <sub>A</sub>  | Operating<br>Temperature                         | -                                        | -40     | -       | 105     | °C   |

| TJ              | Junction<br>Temperature                          | -                                        | -40     | -       | 125     | °C   |

| R <sub>JA</sub> | Junction-to-<br>ambient<br>Thermal<br>Resistance | TFBGA144                                 | -       | 45      | _       | °C/W |

|                 |                                                  | LQFP144                                  | -       | 36      | -       |      |

|                 |                                                  | TFBGA100                                 | -       | 47      | _       |      |

|                 |                                                  | LQFP100                                  | -       | 41      | -       |      |

|                 |                                                  | LQFP64                                   | -       | 46      | _       |      |

| P <sub>D</sub>  | Power<br>Dissipation                             | AtT <sub>A</sub> = 85°C,<br>TFBGA144     | -       | -       | _       | mW   |

|                 |                                                  | AtT <sub>A</sub> = 105°C<br>TFBGA144     | -       | -       | 425     |      |

| P <sub>D</sub>  | Power<br>Dissipation                             | At T <sub>A</sub> =<br>85°C,LQFP1<br>44  | _       | _       | 1047    | mW   |

|                 |                                                  | At T <sub>A</sub> =<br>105°C,LQFP<br>144 | _       | _       | 523     | mW   |