Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 300MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 114                                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                         |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 144-LQFP                                                                                      |

| Supplier Device Package    | 144-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamv70q19b-aabt                   |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Reinforced Safety Watchdog Timer (RSWDT)

| Bit       31       30       29       28       27       26       25       24         Access<br>Reset       Image: Constraint of the set of th                                                                                       |        | Name:<br>Offset:<br>Reset:<br>Property: | RSWDT_SR<br>0x08<br>0x00000000<br>Read-only |    |    |    |    |    |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|---------------------------------------------|----|----|----|----|----|-------|

| Reset       Bit       23       22       21       20       19       18       17       16         Access<br>Reset       Image: Constraint of the set of the                                                                                                | Bit    | 31                                      | 30                                          | 29 | 28 | 27 | 26 | 25 | 24    |

| Reset       Bit       23       22       21       20       19       18       17       16         Access<br>Reset       Image: Constraint of the set of the                                                                                                |        |                                         |                                             |    |    |    |    |    |       |

| Bit     23     22     21     20     19     18     17     16       Access<br>Reset     Image: Constraint of the second secon                                                                     |        |                                         |                                             |    |    |    |    |    |       |

| Access       Reset       Image: state of the st | Reset  |                                         |                                             |    |    |    |    |    |       |

| Access       Reset       Image: state of the st |        |                                         |                                             |    |    |    |    |    |       |

| Reset       Bit       15       14       13       12       11       10       9       8         Access<br>Reset       Image: Constraint of the second seco                                                                                                | Bit    | 23                                      | 22                                          | 21 | 20 | 19 | 18 | 17 | 16    |

| Reset       Bit       15       14       13       12       11       10       9       8         Access<br>Reset       Image: Constraint of the second seco                                                                                                |        |                                         |                                             |    |    |    |    |    |       |

| Bit     15     14     13     12     11     10     9     8       Access<br>Reset     Image: Constraint of the second                                                                      |        |                                         |                                             |    |    |    |    |    |       |

| Access<br>Reset<br>Bit 7 6 5 4 3 2 1 0<br>MOUNF<br>Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reset  |                                         |                                             |    |    |    |    |    |       |

| Access<br>Reset<br>Bit 7 6 5 4 3 2 1 0<br>MOUNF<br>Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                         |                                             |    |    |    |    |    |       |

| Bit         7         6         5         4         3         2         1         0           Image: Access         Im                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit    | 15                                      | 14                                          | 13 | 12 | 11 | 10 | 9  | 8     |

| Bit         7         6         5         4         3         2         1         0           Image: Access         Im                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                         |                                             |    |    |    |    |    |       |

| Bit       7       6       5       4       3       2       1       0         Image:                                                                                  |        |                                         |                                             |    |    |    |    |    |       |

| Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reset  |                                         |                                             |    |    |    |    |    |       |

| Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                         |                                             |    |    |    |    |    |       |

| Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit    | 7                                       | 6                                           | 5  | 4  | 3  | 2  | 1  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                         |                                             |    |    |    |    |    | WDUNF |

| Reset 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Access |                                         |                                             |    |    |    |    |    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reset  |                                         |                                             |    |    |    |    |    | 0     |

# 25.5.3 Reinforced Safety Watchdog Timer Status Register

Bit 0 - WDUNF Watchdog Underflow

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | No watchdog underflow occurred since the last read of RSWDT_SR.           |

| 1     | At least one watchdog underflow occurred since the last read of RSWDT_SR. |

## Static Memory Controller (SMC)

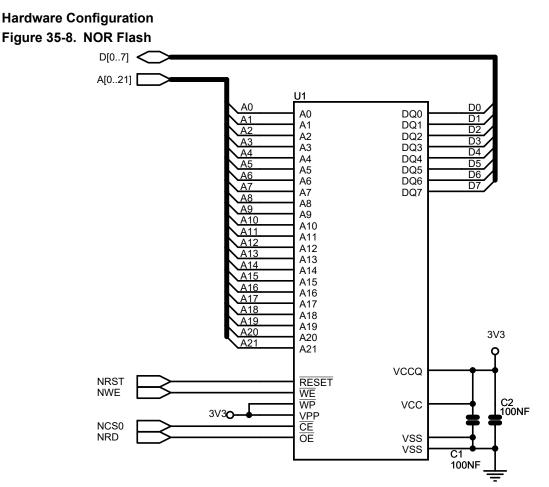

### 35.8.1.2 NOR Flash

### Software Configuration

Configure the SMC CS0 Setup, Pulse, Cycle, and Mode, depending on Flash timings and system bus frequency.

## 35.9 Standard Read and Write Protocols

In the following sections, the byte access type is not considered. Byte select lines (NBS0 to NBS1) always have the same timing as the A address bus. NWE represents either the NWE signal in byte select access type or one of the byte write lines (NWR0 to NWR1) in byte write access type. NWR0 to NWR1 have the same timings and protocol as NWE. If D[15:8] are used, they have the same timing as D[7:0]. In the same way, NCS represents one of the NCS[0..3] chip select lines.

### 35.9.1 Read Waveforms

The read cycle is shown in the following figure.

The read cycle starts with the address setting on the memory address bus.

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_RPSF<br>0x044<br>0x00000FFF<br>- |     |     |         |        |     |     |

|--------|-----------------------------------------|---------------------------------------|-----|-----|---------|--------|-----|-----|

| Bit    | 31                                      | 30                                    | 29  | 28  | 27      | 26     | 25  | 24  |

|        | ENRXP                                   |                                       |     |     |         |        |     |     |

| Access | R                                       |                                       |     |     |         |        |     |     |

| Reset  | 0                                       |                                       |     |     |         |        |     |     |

| Bit    | 23                                      | 22                                    | 21  | 20  | 19      | 18     | 17  | 16  |

| Dit    | 20                                      |                                       | 21  | 20  | 15      | 10     | 17  |     |

| Access |                                         |                                       |     |     |         |        |     |     |

| Reset  |                                         |                                       |     |     |         |        |     |     |

|        |                                         |                                       |     |     |         |        |     |     |

| Bit    | 15                                      | 14                                    | 13  | 12  | 11      | 10     | 9   | 8   |

|        |                                         |                                       |     |     |         | RPB1AD |     |     |

| Access |                                         |                                       |     |     | R/W     | R/W    | R/W | R/W |

| Reset  |                                         |                                       |     |     | 1       | 1      | 1   | 1   |

| Dit    | -                                       | 0                                     | -   |     | 0       | 0      | 4   | 0   |

| Bit    | 7                                       | 6                                     | 5   | 4   | 3       | 2      | 1   | 0   |

|        |                                         |                                       |     |     | DR[7:0] |        |     |     |

| Access | R/W                                     | R/W                                   | R/W | R/W | R/W     | R/W    | R/W | R/W |

| Reset  | 1                                       | 1                                     | 1   | 1   | 1       | 1      | 1   | 1   |

### 38.8.18 GMAC RX Partial Store and Forward Register

Bit 31 – ENRXP Enable RX Partial Store and Forward Operation

**Bits 11:0 – RPB1ADR[11:0]** Receive Partial Store and Forward Address Watermark value. Reset = 1.

# USB High-Speed Interface (USBHS)

- Bit 5 OVERFIES Overflow Interrupt Enable

- Bit 4 NAKEDES NAKed Interrupt Enable

- Bit 3 PERRES Pipe Error Interrupt Enable

- Bit 2 UNDERFIES Underflow Interrupt Enable

- Bit 1 TXOUTES Transmitted OUT Data Interrupt Enable

- Bit 0 RXINES Received IN Data Interrupt Enable

## Two-wire Interface (TWIHS)

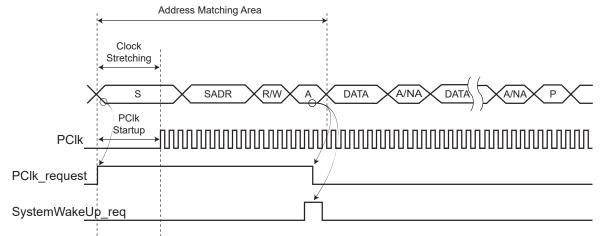

### 43.6.5.8 Asynchronous Partial Wakeup (SleepWalking)

The TWIHS includes an asynchronous start condition detector. It is capable of waking the device up from a Sleep mode upon an address match (and optionally an additional data match), including Sleep modes where the TWIHS peripheral clock is stopped.

After detecting the START condition on the bus, the TWIHS stretches TWCK until the TWIHS peripheral clock has started. The time required for starting the TWIHS depends on which Sleep mode the device is in. After the TWIHS peripheral clock has started, the TWIHS releases its TWCK stretching and receives one byte of data (slave address) on the bus. At this time, only a limited part of the device, including the TWIHS module, receives a clock, thus saving power. If the address phase causes a TWIHS address match (and, optionally, if the first data byte causes data match as well), the entire device is woken up and normal TWIHS address matching actions are performed. Normal TWIHS transfer then follows. If the TWIHS is not addressed (or if the optional data match fails), the TWIHS peripheral clock is automatically stopped and the device returns to its original Sleep mode.

The TWIHS has the capability to match on more than one address. The SADR1EN, SADR2EN and SADR3EN bits in TWIHS\_SMR enable address matching on additional addresses which can be configured through SADR1, SADR2 and SADR3 fields in the TWIHS\_SWMR. The SleepWalking matching process can be extended to the first received data byte if TWIHS\_SMR.DATAMEN is set and, in this case, a complete matching includes address matching and first received data matching. TWIHS\_SWMR.DATAM configures the data to match on the first received byte.

When the system is in Active mode and the TWIHS enters Asynchronous Partial Wakeup mode, the flag SVACC must be programmed as the unique source of the TWIHS interrupt and the data match comparison must be disabled.

When the system exits Wait mode as the result of a matching condition, the SVACC flag is used to determine if the TWIHS is the source of exit.

### Figure 43-39. Address Match Only (Data Matching Disabled)

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.23 USART Baud Rate Generator Register

| Name:     | US_BRGR    |

|-----------|------------|

| Offset:   | 0x0020     |

| Reset:    | 0x0        |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

| Bit    | 31 | 30 | 29 | 28               | 27    | 26 | 25      | 24 |

|--------|----|----|----|------------------|-------|----|---------|----|

|        |    |    |    |                  |       |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  |    |    |    |                  |       |    |         |    |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 23 | 22 | 21 | 20               | 19    | 18 | 17      | 16 |

|        |    |    |    |                  |       |    | FP[2:0] |    |

| Access | L  |    |    |                  |       |    |         |    |

| Reset  |    |    |    |                  |       | 0  | 0       | 0  |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 15 | 14 | 13 | 12               | 11    | 10 | 9       | 8  |

|        |    |    |    | CD[ <sup>*</sup> | 15:8] |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0  | 0       | 0  |

|        |    |    |    |                  |       |    |         |    |

| Bit    | 7  | 6  | 5  | 4                | 3     | 2  | 1       | 0  |

|        |    |    |    | CD               | 7:0]  |    |         |    |

| Access |    |    |    |                  |       |    |         |    |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0  | 0       | 0  |

### Bits 18:16 - FP[2:0] Fractional Part

▲ WARNING When the value of field FP is greater than 0, the SCK (oversampling clock) generates nonconstant duty cycles. The SCK high duration is increased by "selected clock" period from time to time. The duty cycle depends on the value of the CD field.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Fractional divider is disabled.            |

| 1-7   | Baud rate resolution, defined by FP × 1/8. |

### Bits 15:0 – CD[15:0] Clock Divider

| CD | USART_MODE ≠ IS | USART_MODE ≠ ISO7816 |                   |         |  |  |  |  |  |

|----|-----------------|----------------------|-------------------|---------|--|--|--|--|--|

|    | SYNC = 0        |                      | SYNC = 1          | ISO7816 |  |  |  |  |  |

|    | OVER = 0        | OVER = 1             | or                |         |  |  |  |  |  |

|    |                 |                      | USART_MODE = SPI  |         |  |  |  |  |  |

|    |                 |                      | (Master or Slave) |         |  |  |  |  |  |

Universal Synchronous Asynchronous Receiver Transc...

### 46.7.32 USART LIN Mode Register

| Name:     | US_LINMR   |

|-----------|------------|

| Offset:   | 0x0054     |

| Reset:    | 0x0        |

| Property: | Read/Write |

This register is relevant only if USART\_MODE = 0xA or 0xB in the USART Mode Register.

| Bit    | 31      | 30                                    | 29  | 28     | 27     | 26     | 25      | 24    |

|--------|---------|---------------------------------------|-----|--------|--------|--------|---------|-------|

|        |         |                                       |     |        |        |        |         |       |

| Access |         |                                       |     |        | -      |        |         |       |

| Reset  |         |                                       |     |        |        |        |         |       |

|        |         |                                       |     |        |        |        |         |       |

| Bit    | 23      | 22                                    | 21  | 20     | 19     | 18     | 17      | 16    |

|        |         |                                       |     |        |        |        | SYNCDIS | PDCM  |

| Access |         |                                       |     |        |        |        |         |       |

| Reset  |         |                                       |     |        |        |        | 0       | 0     |

|        |         |                                       |     |        |        |        |         |       |

| Bit    | 15      | 14                                    | 13  | 12     | 11     | 10     | 9       | 8     |

|        |         |                                       |     | DLC    | [7:0]  |        |         |       |

| Access |         |                                       |     |        |        |        |         |       |

| Reset  | 0       | 0                                     | 0   | 0      | 0      | 0      | 0       | 0     |

|        |         |                                       |     |        |        |        |         |       |

| Bit    | 7       | 6                                     | 5   | 4      | 3      | 2      | 1       | 0     |

|        | WKUPTYP | FSDIS                                 | DLM | CHKTYP | CHKDIS | PARDIS | NACT    | [1:0] |

| Access |         | · · · · · · · · · · · · · · · · · · · |     |        |        |        |         |       |

| Reset  | 0       | 0                                     | 0   | 0      | 0      | 0      | 0       | 0     |

### Bit 17 – SYNCDIS Synchronization Disable

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | The synchronization procedure is performed in LIN slave node configuration.     |

| 1     | The synchronization procedure is not performed in LIN slave node configuration. |

### Bit 16 - PDCM DMAC Mode

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | The LIN mode register US_LINMR is not written by the DMAC.                   |

| 1     | The LIN mode register US_LINMR (excepting that flag) is written by the DMAC. |

### Bits 15:8 - DLC[7:0] Data Length Control

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0-255 | Defines the response data length if DLM = 0, in that case the response data length is equal to |

|       | DLC+1 bytes.                                                                                   |

## Bit 7 – WKUPTYP Wakeup Signal Type

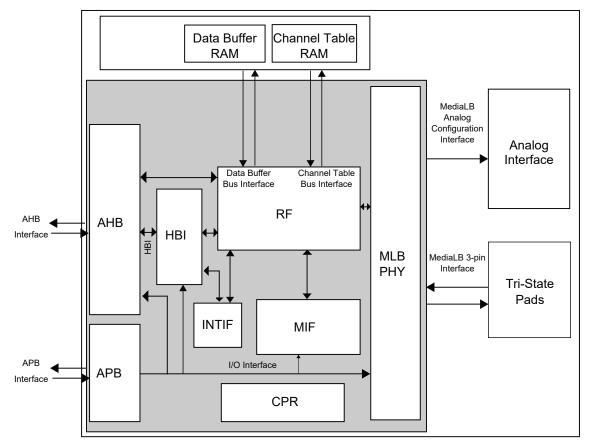

# 48.4 Signal Description

## 48.4.1 Definition of Terms

The following terms will be used when referring to specific implementations of MediaLB.

Table 48-1. MediaLB Definition of Terms

| Names          | Description                                                                                                            |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Media Local Bu | us:                                                                                                                    |  |  |  |  |  |  |

| MLBC           | General reference to the Clock line of a Media Local Bus:<br>on a 3-pin MediaLB interface, connects to the MLBCLK pin  |  |  |  |  |  |  |

| MLBS           | General reference to the Signal line of a Media Local Bus:<br>on a 3-pin MediaLB interface, connects to the MLBSIG pin |  |  |  |  |  |  |

| MLBD           | General reference to the Data line of a Media Local Bus:<br>on a 3-pin MediaLB interface, connects to the MLBDAT pin   |  |  |  |  |  |  |

| 3-pin MediaLB  | 3-pin MediaLB Interface:                                                                                               |  |  |  |  |  |  |

| MLBCLK         | MediaLB Controller (output) pin connected to MLBC.                                                                     |  |  |  |  |  |  |

© 2018 Microchip Technology Inc.

## **Controller Area Network (MCAN)**

### Table 49-9. Tx Event FIFO Element

|    | 31      |     |     | 24      | 23          |     |     |       | 16  | 15 8      | 7 0 |

|----|---------|-----|-----|---------|-------------|-----|-----|-------|-----|-----------|-----|

| E0 | ESI     | XTD | RTR | ID[28:  | 0]          |     |     |       |     |           |     |

| E1 | MM[7:0] |     |     | <u></u> | ET<br>[1:0] | FDF | BRS | DLC[3 | :0] | TXTS[15:0 | D]  |

• E0 Bit 31 ESI: Error State Indicator

- 0: Transmitting node is error active.

- 1: Transmitting node is error passive.

- E0 Bit 30 XTD: Extended Identifier

- 0: 11-bit standard identifier.

- 1: 29-bit extended identifier.

- E0 Bit 29 RTR: Remote Transmission Request

- 0: Data frame transmitted.

- 1: Remote frame transmitted.

- E0 Bits 28:0 ID[28:0]: Identifier

Standard or extended identifier depending on bit XTD. A standard identifier is stored into ID[28:18].

• E1 Bits 31:24 MM[7:0]: Message Marker

Copied from Tx Buffer into Tx Event FIFO element for identification of Tx message status.

- E1 Bit 23:22 ET[1:0]: Event Type

- 0: Reserved

- 1: Tx event

- 2: Transmission in spite of cancellation (always set for transmissions in DAR mode)

- 3: Reserved

- E1 Bit 21 FDF: FD Format

- 0: Standard frame format.

- 1: CAN FD frame format (new DLC-coding and CRC).

- E1 Bit 20 BRS: Bit Rate Switch

- 0: Frame transmitted without bit rate switching.

- 1: Frame transmitted with bit rate switching.

- E1 Bits 19:16 DLC[3:0]: Data Length Code

- 0-8: CAN + CAN FD: frame with 0-8 data bytes transmitted.

- 9-15: CAN: frame with 8 data bytes transmitted.

- 9-15: CAN FD: frame with 12/16/20/24/32/48/64 data bytes transmitted

- E1 Bits 15:0 TXTS[15:0]: Tx Timestamp

## Controller Area Network (MCAN)

### 49.6.21 MCAN Standard ID Filter Configuration

| Name:     | MCAN_SIDFC |

|-----------|------------|

| Offset:   | 0x84       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

Settings for 11-bit standard Message ID filtering. The Standard ID Filter Configuration controls the filter path for standard messages as illustrated in Standard Message ID Filter Path.

This register can only be written if the bits CCE and INIT are set in MCAN CC Control Register.

| Bit    | 31         | 30  | 29  | 28    | 27      | 26  | 25  | 24  |

|--------|------------|-----|-----|-------|---------|-----|-----|-----|

|        |            |     |     |       |         |     |     |     |

| Access |            |     |     |       |         |     |     |     |

| Reset  |            |     |     |       |         |     |     |     |

|        |            |     |     |       |         |     |     |     |

| Bit    | 23         | 22  | 21  | 20    | 19      | 18  | 17  | 16  |

|        |            |     |     | LSS   | [7:0]   |     |     |     |

| Access | R/W        | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

|        |            |     |     |       |         |     |     |     |

| Bit    | 15         | 14  | 13  | 12    | 11      | 10  | 9   | 8   |

|        |            |     |     | FLSSA | A[13:6] |     |     |     |

| Access | R/W        | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

|        |            |     |     |       |         |     |     |     |

| Bit    | 7          | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|        | FLSSA[5:0] |     |     |       |         |     |     |     |

| Access | R/W        | R/W | R/W | R/W   | R/W     | R/W |     |     |

| Reset  | 0          | 0   | 0   | 0     | 0       | 0   |     |     |

| Reset  | 0          | 0   | 0   | 0     | 0       | 0   |     |     |

#### Bits 23:16 - LSS[7:0] List Size Standard

>128: Values greater than 128 are interpreted as 128.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | No standard Message ID filter.                 |

| 1-128 | Number of standard Message ID filter elements. |

#### Bits 15:2 - FLSSA[13:0] Filter List Standard Start Address

Start address of standard Message ID filter list (32-bit word address, see Message RAM Configuration).

Write FLSSA with the bits [15:2] of the 32-bit address.

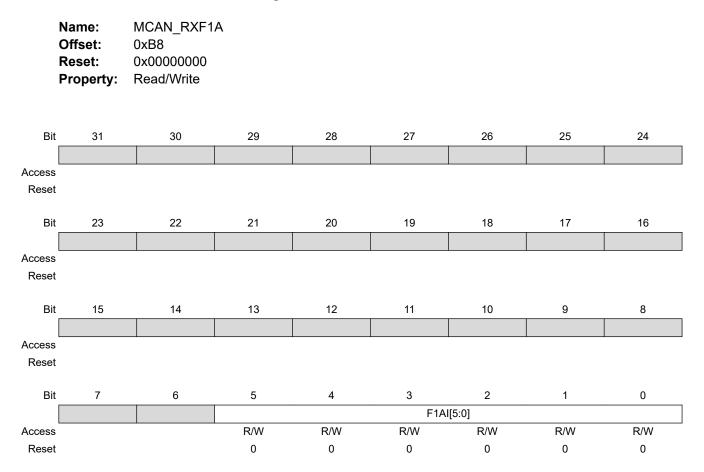

# **Controller Area Network (MCAN)**

#### 49.6.33 MCAN Receive FIFO 1 Acknowledge

Bits 5:0 - F1AI[5:0] Receive FIFO 1 Acknowledge Index

After the processor has read a message or a sequence of messages from Receive FIFO 1 it has to write the buffer index of the last element read from Receive FIFO 1 to F1AI. This will set the Receive FIFO 1 Get Index MCAN\_RXF1S.F1GI to F1AI + 1 and update the FIFO 1 Fill Level MCAN\_RXF1S.F1FL.

Each linear divider can independently divide one of the clocks of the modulo n counter. The selection of the clock to be divided is made according to the PREA (PREB) field of the PWM Clock register (PWM\_CLK). The resulting clock clkA (clkB) is the clock selected divided by DIVA (DIVB) field value.

After a reset of the PWM controller, DIVA (DIVB) and PREA (PREB) are set to '0'. This implies that after reset clkA (clkB) are turned off.

At reset, all clocks provided by the modulo n counter are turned off except the peripheral clock. This situation is also true when the PWM peripheral clock is turned off through the Power Management Controller.

**Δ CAUTION** Before using the PWM controller, the programmer must first enable the peripheral clock in the Power Management Controller (PMC).

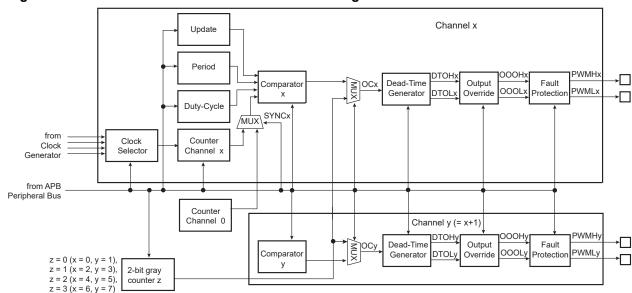

### 51.6.2 PWM Channel

### 51.6.2.1 Channel Block Diagram

### Figure 51-3. Functional View of the Channel Block Diagram

Each of the 4 channels is composed of six blocks:

- A clock selector which selects one of the clocks provided by the clock generator (described in PWM Clock Generator ).

- A counter clocked by the output of the clock selector. This counter is incremented or decremented according to the channel configuration and comparators matches. The size of the counter is 16 bits.

- A comparator used to compute the OCx output waveform according to the counter value and the configuration. The counter value can be the one of the channel counter or the one of the channel 0 counter according to SYNCx bit in the PWM Sync Channels Mode Register (PWM\_SCM).

- A 2-bit configurable gray counter enables the stepper motor driver. One gray counter drives 2 channels.

- A dead-time generator providing two complementary outputs (DTOHx/DTOLx) which allows to drive external power control switches safely.

# Pulse Width Modulation Controller (PWM)

| Value | Name  | Description                                                                                                                           |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0     | MODE0 | Manual write of double buffer registers and manual update of synchronous channels 1 <sup>(1)</sup> .                                  |

| 1     | MODE1 | Manual write of double buffer registers and automatic update of synchronous channels $2^{(2)}$ .                                      |

| 2     | MODE2 | The WRDY flag in PWM Interrupt Status Register 2 and the DMA transfer request are set to '1' as soon as the update period is elapsed. |

### Note:

- 1. The update occurs at the beginning of the next PWM period, when the UPDULOCK bit in PWM Sync Channels Update Control Register is set.

- 2. The update occurs when the Update Period is elapsed.

### Bits 0, 1, 2, 3 – SYNCx Synchronous Channel x

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Channel x is not a synchronous channel. |

| 1     | Channel x is a synchronous channel.     |

### 51.7.17 PWM Interrupt Status Register 2

| Name:     | PWM_ISR2   |

|-----------|------------|

| Offset:   | 0x40       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

Reading PWM\_ISR2 automatically clears flags WRDY, UNRE and CMPSx.

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       |       |       |       |       |       |       |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

|        |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|        | CMPU7 | CMPU6 | CMPU5 | CMPU4 | CMPU3 | CMPU2 | CMPU1 | CMPU0 |

| Access | R     | R     | R     | R     | R     | R     | R     | R     |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

|        | CMPM7 | CMPM6 | CMPM5 | CMPM4 | CMPM3 | CMPM2 | CMPM1 | CMPM0 |

| Access | R     | R     | R     | R     | R     | R     | R     | R     |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|        |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        |       |       |       |       | UNRE  |       |       | WRDY  |

| Access |       |       |       |       | R     |       |       | R     |

| Reset  |       |       |       |       | 0     |       |       | 0     |

#### Bits 16, 17, 18, 19, 20, 21, 22, 23 – CMPUx Comparison x Update

| Value | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 0     | The comparison x has not been updated since the last read of the PWM_ISR2 register.               |

| 1     | The comparison x has been updated at least one time since the last read of the PWM_ISR2 register. |

### Bits 8, 9, 10, 11, 12, 13, 14, 15 – CMPMx Comparison x Match

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The comparison x has not matched since the last read of the PWM_ISR2 register.               |

| 1     | The comparison x has matched at least one time since the last read of the PWM_ISR2 register. |

### Bit 3 – UNRE Synchronous Channels Update Underrun Error

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | No Synchronous Channels Update Underrun has occurred since the last read of the           |

|       | PWM_ISR2 register.                                                                        |

| 1     | At least one Synchronous Channels Update Underrun has occurred since the last read of the |

|       | PWM_ISR2 register.                                                                        |

### 51.7.35 PWM Write Protection Status Register

| Name:     | PWM_WPSR   |

|-----------|------------|

| Offset:   | 0xE8       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

| Bit    | 31           | 30 | 29     | 28     | 27      | 26     | 25     | 24     |

|--------|--------------|----|--------|--------|---------|--------|--------|--------|

|        | WPVSRC[15:8] |    |        |        |         |        |        |        |

| Access | R            | R  | R      | R      | R       | R      | R      | R      |

| Reset  | 0            | 0  | 0      | 0      | 0       | 0      | 0      | 0      |

|        |              |    |        |        |         |        |        |        |

| Bit    | 23           | 22 | 21     | 20     | 19      | 18     | 17     | 16     |

|        |              |    |        | WPVS   | RC[7:0] |        |        |        |

| Access | R            | R  | R      | R      | R       | R      | R      | R      |

| Reset  | 0            | 0  | 0      | 0      | 0       | 0      | 0      | 0      |

|        |              |    |        |        |         |        |        |        |

| Bit    | 15           | 14 | 13     | 12     | 11      | 10     | 9      | 8      |

|        |              |    | WPHWS5 | WPHWS4 | WPHWS3  | WPHWS2 | WPHWS1 | WPHWS0 |

| Access |              |    | R      | R      | R       | R      | R      | R      |

| Reset  |              |    | 0      | 0      | 0       | 0      | 0      | 0      |

|        |              |    |        |        |         |        |        |        |

| Bit    | 7            | 6  | 5      | 4      | 3       | 2      | 1      | 0      |

|        | WPVS         |    | WPSWS5 | WPSWS4 | WPSWS3  | WPSWS2 | WPSWS1 | WPSWS0 |

| Access | R            |    | R      | R      | R       | R      | R      | R      |

| Reset  | 0            |    | 0      | 0      | 0       | 0      | 0      | 0      |

### Bits 31:16 - WPVSRC[15:0] Write Protect Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

### Bits 8, 9, 10, 11, 12, 13 - WPHWSx Write Protect HW Status

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | The HW write protection x of the register group x is disabled. |

| 1     | The HW write protection x of the register group x is enabled.  |

### Bit 7 – WPVS Write Protect Violation Status

| Value | Description                                                                                                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No write protection violation has occurred since the last read of PWM_WPSR.                                                                                                                   |

| 1     | At least one write protection violation has occurred since the last read of PWM_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is |

|       | reported into field WPVSRC.                                                                                                                                                                   |

### Bits 0, 1, 2, 3, 4, 5 - WPSWSx Write Protect SW Status

### 52.7.15 AFEC Compare Window Register

| Name:     | AFEC_CWR   |

|-----------|------------|

| Offset:   | 0x50       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the AFEC Write Protection Mode Register.

| Bit    | 31              | 30  | 29  | 28     | 27       | 26  | 25  | 24  |

|--------|-----------------|-----|-----|--------|----------|-----|-----|-----|

|        | HIGHTHRES[15:8] |     |     |        |          |     |     |     |

| Access | R/W             | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0               | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

|        |                 |     |     |        |          |     |     |     |

| Bit    | 23              | 22  | 21  | 20     | 19       | 18  | 17  | 16  |

|        |                 |     |     | HIGHTH | RES[7:0] |     |     |     |

| Access | R/W             | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0               | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

|        |                 |     |     |        |          |     |     |     |

| Bit    | 15              | 14  | 13  | 12     | 11       | 10  | 9   | 8   |

|        | LOWTHRES[15:8]  |     |     |        |          |     |     |     |

| Access | R/W             | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0               | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

|        |                 |     |     |        |          |     |     |     |

| Bit    | 7               | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|        | LOWTHRES[7:0]   |     |     |        |          |     |     |     |

| Access | R/W             | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Reset  | 0               | 0   | 0   | 0      | 0        | 0   | 0   | 0   |

|        |                 |     |     |        |          |     |     |     |

### Bits 31:16 – HIGHTHRES[15:0] High Threshold

High threshold associated to compare settings of AFEC\_EMR. For comparisons lower than 16 bits and signed, the sign should be extended up to the bit 15.

### Bits 15:0 – LOWTHRES[15:0] Low Threshold

Low threshold associated to compare settings of AFEC\_EMR. For comparisons lower than 16 bits and signed, the sign should be extended up to the bit 15.

# Integrity Check Monitor (ICM)

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Automatic monitoring mode is disabled.                                           |

| 1     | The ICM passes through the Main List once to calculate the message digest of the |

|       | monitored area. When WRAP = 1 in ICM_RCFG, the ICM begins monitoring.            |

### Bits 7:4 – BBC[3:0] Bus Burden Control

This field is used to control the burden of the ICM system bus. The number of system clock cycles between the end of the current processing and the next block transfer is set to 2<sup>BBC</sup>. Up to 32,768 cycles can be inserted.

### Bit 2 – SLBDIS Secondary List Branching Disable

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | Branching to the Secondary List is permitted.                                           |

| 1     | Branching to the Secondary List is forbidden. The NEXT field of the ICM_RNEXT structure |

|       | member has no effect and is always considered as zero.                                  |

### Bit 1 – EOMDIS End of Monitoring Disable

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | End of Monitoring is permitted.                                                             |

| 1     | End of Monitoring is forbidden. The EOM bit of the ICM_RCFG structure member has no effect. |

### Bit 0 – WBDIS Write Back Disable

When ASCD is set, WBDIS has no effect.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Write Back operations are permitted.                                                         |

| 1     | Write Back operations are forbidden. Context register CDWBN bit is internally set to one and |

|       | cannot be modified by a linked list element. ICM_RCFG.CDWBN has no effect.                   |

# Integrity Check Monitor (ICM)

| Register Address  | Address Offset / Byte Lane |             |            |           |  |  |

|-------------------|----------------------------|-------------|------------|-----------|--|--|

|                   | 0x3 / 31:24                | 0x2 / 23:16 | 0x1 / 15:8 | 0x0 / 7:0 |  |  |

| 0x000 ICM_UIHVAL0 | 01                         | 23          | 45         | 67        |  |  |

| 0x004 ICM_UIHVAL1 | 89                         | ab          | cd         | ef        |  |  |

| 0x008 ICM_UIHVAL2 | fe                         | dc          | ba         | 98        |  |  |

| 0x00C ICM_UIHVAL3 | 76                         | 54          | 32         | 10        |  |  |

| 0x010 ICM_UIHVAL4 | fO                         | e1          | d2         | c3        |  |  |

# **Electrical Characteristics for SAM E70/S70**

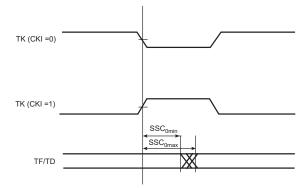

### Figure 59-41. Min and Max Access Time of Output Signals

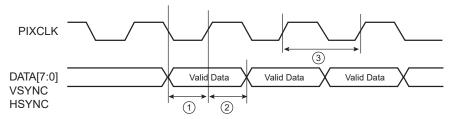

### 59.13.1.15 ISI Timings

### 59.13.1.15.1 Timing Conditions

Timings are given assuming the load capacitance in the following table.

### Table 59-76. Load Capacitance

| Supply | C <sub>L</sub> Max |

|--------|--------------------|

| 3.3V   | 30 pF              |

| 1.7V   | 20 pF              |

## 59.13.1.15.2 Timing Extraction

### Table 59-77. ISI Timings with Peripheral Supply 3.3V

| Symbol           | Parameter                   | Min  | Мах | Unit |

|------------------|-----------------------------|------|-----|------|

| ISI <sub>1</sub> | DATA/VSYNC/HSYNC setup time | 1.5  | -   | ns   |

| ISI <sub>2</sub> | DATA/VSYNC/HSYNC hold time  | -1.2 | -   | ns   |

| ISI <sub>3</sub> | PIXCLK frequency            | -    | 75  | MHz  |

### Figure 59-42.

### Table 59-78. ISI Timings with Peripheral Supply 1.8V

| Symbol           | Parameter                   | Min  | Max | Unit |

|------------------|-----------------------------|------|-----|------|

| ISI <sub>1</sub> | DATA/VSYNC/HSYNC setup time | 1.8  | -   | ns   |

| ISI <sub>2</sub> | DATA/VSYNC/HSYNC hold time  | -1.4 | -   | ns   |

| ISI <sub>3</sub> | PIXCLK frequency            | -    | 75  | MHz  |

### Figure 59-43. ISI Timing Diagram

# Revision History

| Date      | Changes                                                                                                                                                                             |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|           | Section 42.7.9 "QSPI Serial Clock Register": updated equations.                                                                                                                     |  |  |  |  |

|           | Section 42.7.12 "QSPI Instruction Frame Register": updated INSTEN bit description.                                                                                                  |  |  |  |  |

|           | Section 43. "Two-wire Interface (TWIHS)"<br>Section 43.6.3.4 "Master Transmitter Mode" and "Read Sequence": added sentence on<br>clearing TXRDY flag.                               |  |  |  |  |

|           | Section 43.6.5.7 "High-Speed Slave Mode": updated 11-MHz limit information.                                                                                                         |  |  |  |  |

|           | Updated Section 43.6.7 "Register Write Protection".                                                                                                                                 |  |  |  |  |

|           | Updated Section 43.7.1 "TWIHS Control Register": added bit FIFODIS, FIFOEN, LOCKCLR and THRCLR.                                                                                     |  |  |  |  |

|           | Added Section 45. "Inter-IC Sound Controller (I2SC)".                                                                                                                               |  |  |  |  |

| 08-Feb-16 | Section 46. "Universal Synchronous Asynchronous Receiver Transceiver (USART)"<br>Added descriptions of Modem mode and ISO7816 mode throughout.                                      |  |  |  |  |

|           | Updated Section 46.1 "Description" and Section 46.2 "Embedded Characteristics".                                                                                                     |  |  |  |  |

|           | Table 46-1 "I/O Line Description" updated and added lines RI, DSR, DCD, and DTR.                                                                                                    |  |  |  |  |

|           | Section 46.6.1 "Baud Rate Generator": corrected value in "The frequency of the signal provided on SCK must be at least"                                                             |  |  |  |  |

|           | Updated Figure 46-2, "Baud Rate Generator".                                                                                                                                         |  |  |  |  |

|           | "Baud Rate Calculation Example", corrected formula.                                                                                                                                 |  |  |  |  |

|           | Section 46.6.1.2 "Fractional Baud Rate in Asynchronous Mode" and Section 46.7.23 "USART Baud Rate Generator Register": added warning "When the value of field FP is greater than 0" |  |  |  |  |

|           | Updated Figure 46-3, "Fractional Baud Rate Generator".                                                                                                                              |  |  |  |  |

|           | Section 46.6.1.3 "Baud Rate in Synchronous Mode or SPI Mode": corrected formula.<br>Corrected external clock frequency. Corrected SCK maximum frequency.                            |  |  |  |  |

|           | Added Section 46.6.4 "ISO7816 Mode".                                                                                                                                                |  |  |  |  |

|           | Inserted new Figure 46-27, "RTS Line Software Control when USART_MR.USART_MODE = 2".                                                                                                |  |  |  |  |

|           | Section 46.6.3.4 "Manchester Decoder": corrected "MANE flag" with "MANERR" flag.                                                                                                    |  |  |  |  |

|           | Added Section 46.6.7 "Modem Mode".                                                                                                                                                  |  |  |  |  |

|           | Section 46.6.8.5 "Character Transmission": added content to 1st paragraph. Corrected occurrences of RTSEN to RCS, RTSDIS to FCS.                                                    |  |  |  |  |

|           | Section 46.6.9.8 "Slave Node Synchronization": updated bullet on oversampling.                                                                                                      |  |  |  |  |

|           | Updated Figure 46-42, "Slave Node Synchronization".                                                                                                                                 |  |  |  |  |

|           | Section 46.7.1 "USART Control Register": added bits/fields RSTIT, RSTNACK, DTREN and DTRDIS. Updated RTSDIS bit description.                                                        |  |  |  |  |