Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 300MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 114                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 384K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                         |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 144-LQFP                                                                                      |

| Supplier Device Package    | 144-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamv70q20b-aabt                   |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.1.2 144-ball LFBGA/TFBGA Package Outline Figure 6-2. Orientation of the 144-ball LFBGA/TFBGA Package

## 6.1.3 144-ball UFBGA Package Outline Figure 6-3. Orientation of the 144-ball UFBGA Package

## 6.2 144-lead Package Pinout

## Table 6-1. 144-lead Package Pinout

| LQFP<br>Pin | LFBGA/<br>TFBGA<br>Ball | UFBGA<br>Ball | Power<br>Rail | I/O Type    | Primary |     | Alternate     |     | PIO<br>Peripher<br>al A |     | PIO<br>Peripher<br>al B |     | PIO<br>Peripher<br>al C |     | PIO<br>Peripher<br>al D |     | Reset<br>State                        |

|-------------|-------------------------|---------------|---------------|-------------|---------|-----|---------------|-----|-------------------------|-----|-------------------------|-----|-------------------------|-----|-------------------------|-----|---------------------------------------|

|             |                         |               |               |             | Signal  | Dir | Signal        | Dir | Signal                  | Dir | Signal                  | Dir | Signal                  | Dir | Signal                  | Dir | Signal,<br>Dir, PU,<br>PD, HiZ,<br>ST |

| 102         | C11                     | E11           | VDDIO         | GPIO_A<br>D | PA0     | I/O | WKUP0(<br>1)  | I   | PWMC0_<br>PWMH0         | 0   | TIOA0                   | I/O | A17/BA1                 | 0   | I2SC0_M<br>CK           | 0   | PIO, I,<br>PU, ST                     |

| 99          | D12                     | F11           | VDDIO         | GPIO_A<br>D | PA1     | I/O | WKUP1(<br>1)  | I   | PWMC0_<br>PWML0         | 0   | TIOB0                   | I/O | A18                     | 0   | I2SC0_C<br>K            | I/O | PIO, I,<br>PU, ST                     |

| 93          | E12                     | G12           | VDDIO         | GPIO        | PA2     | I/O | WKUP2(<br>1)  | I   | PWMC0_<br>PWMH1         | 0   | -                       | -   | DATRG                   | I   | -                       | -   | PIO, I,<br>PU, ST                     |

| 91          | F12                     | G11           | VDDIO         | GPIO_A<br>D | PA3     | I/O | PIODC0(<br>2) | 1   | TWD0                    | I/O | LONCOL<br>1             | I   | PCK2                    | 0   | -                       | -   | PIO, I,<br>PU, ST                     |

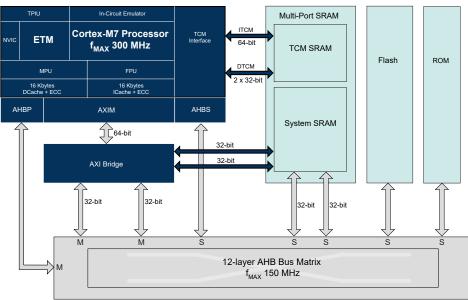

## 9. Interconnect

The system architecture is based on the ARM Cortex-M7 processor connected to the main AHB Bus Matrix, the embedded Flash, the multi-port SRAM and the ROM.

The 32-bit AHBP interface is a single 32-bit wide interface that accesses the peripherals connected on the main Bus Matrix. It is used only for data access. Instruction fetches are never performed on the AHBP interface. The bus, AHBP or AXIM, accessing the peripheral memory area [0x40000000 to 0x60000000] is selected in the AHBP control register.

The 32-bit AHBS interface provides system access to the ITCM, D1TCM, and D0TCM. It is connected on the main Bus Matrix and allows the XDMA to transfer from memory or peripherals to the instruction or data TCMs.

The 64-bit AXIM interface is a single 64-bit wide interface connected through two ports of the AXI Bridge to the main AHB Bus Matrix and to two ports of the multi-port SRAM. The AXIM interface allows:

- Instruction fetches

- Data cache linefills and evictions

- Non-cacheable normal-type memory data accesses

- Device and strongly-ordered type data accesses, generally to peripherals

The interleaved multi-port SRAM optimizes the Cortex-M7 accesses to the internal SRAM.

The interconnect of the other masters and slaves is described in 19. Bus Matrix (MATRIX).

The figure below shows the connections of the different Cortex-M7 ports.

### Figure 9-1. Interconnect Block Diagram

- 1. Round-robin Arbitration (default)

- 2. Fixed Priority Arbitration

Each algorithm may be complemented by selecting a default master configuration for each slave.

When re-arbitration is required, specific conditions apply. Refer to the "Arbitration Rules" section.

### 19.3.3.1 Arbitration Rules

Each arbiter has the ability to arbitrate between requests from two or more masters. To avoid burst breaking and to provide maximum throughput for slave interfaces, arbitration should take place during the following cycles:

- Idle cycles: When a slave is not connected to any master or is connected to a master which is not currently accessing it

- Single cycles: When a slave is performing a single access

- End of Burst cycles: When the current cycle is the last cycle of a burst transfer. For a defined length burst, predicted end of burst matches the size of the transfer but is managed differently for undefined length burst. Refer to the "Undefined Length Burst Arbitration" section.

- Slot cycle limit: When the slot cycle counter has reached the limit value indicating that the current master access is too long and must be broken. Refer to the "Slot Cycle Limit Arbitration" section.

### 19.3.3.1.1 Undefined Length Burst Arbitration

In order to prevent slave handling during undefined length bursts, the user can trigger the re-arbitration before the end of the incremental bursts. The re-arbitration period can be selected from the following Undefined Length Burst Type (ULBT) possibilities:

- 1. Unlimited: no predetermined end of burst is generated. This value enables 1-Kbyte burst lengths.

- 2. 1-beat bursts: predetermined end of burst is generated at each single transfer during the INCR transfer.

- 3. 4-beat bursts: predetermined end of burst is generated at the end of each 4-beat boundary during INCR transfer.

- 4. 8-beat bursts: predetermined end of burst is generated at the end of each 8-beat boundary during INCR transfer.

- 5. 16-beat bursts: predetermined end of burst is generated at the end of each 16-beat boundary during INCR transfer.

- 6. 32-beat bursts: predetermined end of burst is generated at the end of each 32-beat boundary during INCR transfer.

- 7. 64-beat bursts: predetermined end of burst is generated at the end of each 64-beat boundary during INCR transfer.

- 8. 128-beat bursts: predetermined end of burst is generated at the end of each 128-beat boundary during INCR transfer.

The use of undefined length16-beat bursts, or less, is discouraged since this decreases the overall bus bandwidth due to arbitration and slave latencies at each first access of a burst.

If the master does not permanently and continuously request the same slave or has an intrinsically limited average throughput, the ULBT should be left at its default unlimited value, knowing that the AHB specification natively limits all word bursts to 256 beats and double-word bursts to 128 beats because of its 1-Kbyte address boundaries.

Unless duly needed, the ULBT should be left at its default value of 0 for power saving.

This selection is made through the ULBT field of the Master Configuration Registers (MATRIX\_MCFG).

## Power Management Controller (PMC)

| Offset           | Register                                   | Name           | Access     | Reset        |

|------------------|--------------------------------------------|----------------|------------|--------------|

| 0x0028           | PLLA Register                              | CKGR_PLLAR     | Read/Write | 0x0000_3F00  |

| 0x002C           | Reserved                                   | -              | _          | _            |

| 0x0030           | Master Clock Register                      | PMC_MCKR       | Read/Write | 0x0000_0001  |

| 0x0034           | Reserved                                   | -              | _          | _            |

| 0x0038           | USB Clock Register                         | PMC_USB        | Read/Write | 0x0000_0000  |

| 0x003C           | Reserved                                   | -              | _          | _            |

| 0x0040+chid*0x04 | Programmable Clock Register                | PMC_PCK        | Read/Write | 0x0000_0000  |

| 0x005C           | Reserved                                   | -              | _          | _            |

| 0x0060           | Interrupt Enable Register                  | PMC_IER        | Write-only | _            |

| 0x0064           | Interrupt Disable Register                 | PMC_IDR        | Write-only | _            |

| 0x0068           | Status Register                            | PMC_SR         | Read-only  | 0x0003_0008  |

| 0x006C           | Interrupt Mask Register                    | PMC_IMR        | Read-only  | 0x0000_0000  |

| 0x0070           | Fast Startup Mode Register                 | PMC_FSMR       | Read/Write | 0x0000_0000  |

| 0x0074           | Fast Startup Polarity Register             | PMC_FSPR       | Read/Write | 0x0000_0000  |

| 0x0078           | Fault Output Clear Register                | PMC_FOCR       | Write-only | _            |

| 0x007C-0x00E0    | Reserved                                   | -              | _          | _            |

| 0x00E4           | Write Protection Mode Register             | PMC_WPMR       | Read/Write | 0x0          |

| 0x00E8           | Write Protection Status Register           | PMC_WPSR       | Read-only  | 0x0          |

| 0x00EC-0x00FC    | Reserved                                   | -              | _          | _            |

| 0x0100           | Peripheral Clock Enable<br>Register 1      | PMC_PCER1      | Write-only | -            |

| 0x0104           | Peripheral Clock Disable<br>Register 1     | PMC_PCDR1      | Write-only | _            |

| 0x0108           | Peripheral Clock Status Register<br>1      | PMC_PCSR1      | Read-only  | 0x0000_0000  |

| 0x010C           | Peripheral Control Register                | PMC_PCR        | Read/Write | 0x0000_0000  |

| 0x0110           | Oscillator Calibration Register            | PMC_OCR        | Read/Write | (See Note 2) |

| 0x0114           | SleepWalking Enable Register 0             | PMC_SLPWK_ER0  | Write-only | _            |

| 0x0118           | SleepWalking Disable Register 0            | PMC_SLPWK_DR0  | Write-only | -            |

| 0x011C           | SleepWalking Status Register 0             | PMC_SLPWK_SR0  | Read-only  | 0x00000000   |

| 0x0120           | SleepWalking Activity Status<br>Register 0 | PMC_SLPWK_ASR0 | Read-only  | 0x00000000   |

## Parallel Input/Output Controller (PIO)

### 32.6.1.49 PIO I/O Drive Register 1

| Name:     | PIO_DRIVER1 |

|-----------|-------------|

| Offset:   | 0x0118      |

| Property: | Read/Write  |

### Register Reset value: 0x00000000xAAAAAAAA

| Bit    | 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|        | LINE31 | LINE30 | LINE29 | LINE28 | LINE27 | LINE26 | LINE25 | LINE24 |

| Access |        | ·      |        |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |        |

| Bit    | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|        | LINE23 | LINE22 | LINE21 | LINE20 | LINE19 | LINE18 | LINE17 | LINE16 |

| Access |        | •      |        |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |        |

| Bit    | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |

|        | LINE15 | LINE14 | LINE13 | LINE12 | LINE11 | LINE10 | LINE9  | LINE8  |

| Access |        | •      | •      |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |        |

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|        | LINE7  | LINE6  | LINE5  | LINE4  | LINE3  | LINE2  | LINE1  | LINE0  |

| Access |        |        |        |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – LINE Drive of PIO Line

| Value | Name       | Description   |

|-------|------------|---------------|

| 0     | LOW_DRIVE  | Lowest drive  |

| 1     | HIGH_DRIVE | Highest drive |

Image Sensor Interface (ISI)

| Mode      | Byte   | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

|-----------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| RGB 8:8:8 | Byte 0 | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   | R5(i)   | R6(i)   | R7(i)   |

|           | Byte 1 | G0(i)   | G1(i)   | G2(i)   | G3(i)   | G4(i)   | G5(i)   | G6(i)   | G7(i)   |

|           | Byte 2 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | B5(i)   | B6(i)   | B7(i)   |

|           | Byte 3 | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) | R5(i+1) | R6(i+1) | R7(i+1) |

| RGB 5:6:5 | Byte 0 | G3(i)   | G4(i)   | G5(i)   | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   |

|           | Byte 1 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | G0(i)   | G1(i)   | G2(i)   |

|           | Byte 2 | G3(i+1) | G4(i+1) | G5(i+1) | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) |

|           | Byte 3 | B0(i+1) | B1(i+1) | B2(i+1) | B3(i+1) | B4(i+1) | G0(i+1) | G1(i+1) | G2(i+1) |

## Table 37-5. RGB Format in Default Mode, RGB\_CFG = 00, Swap Activated

The RGB 5:6:5 input format is processed to be displayed as RGB 5:6:5 format, compliant with the 16-bit mode of the LCD controller.

### 37.5.3 Clocks

The sensor master clock (ISI\_MCK) can be generated either by the Advanced Power Management Controller (APMC) through a Programmable Clock output or by an external oscillator connected to the sensor.

None of the sensors embed a power management controller, so providing the clock by the APMC is a simple and efficient way to control power consumption of the system.

Care must be taken when programming the system clock. The ISI has two clock domains, the sensor master clock and the pixel clock provided by sensor. The two clock domains are not synchronized, but the sensor master clock must be faster than the pixel clock.

### 37.5.4 Preview Path

### 37.5.4.1 Scaling, Decimation (Subsampling)

This module resizes captured 8-bit color sensor images to fit the LCD display format. The resize module performs only downscaling. The same ratio is applied for both horizontal and vertical resize, then a fractional decimation algorithm is applied.

The decimation factor is a multiple of 1/16; values 0 to 15 are forbidden.

### Table 37-6. Decimation Factor

| Decimation Value  | 0–15 | 16 | 17    | 18    | 19    | <br>124   | 125   | 126   | 127   |

|-------------------|------|----|-------|-------|-------|-----------|-------|-------|-------|

| Decimation Factor | —    | 1  | 1.063 | 1.125 | 1.188 | <br>7.750 | 7.813 | 7.875 | 7.938 |

| OUTPUT           | INPUT | 352 × 288 | 640 × 480 | 800 × 600 | 1280 × 1024 | 1600 × 1200 | 2048 × 1536 |

|------------------|-------|-----------|-----------|-----------|-------------|-------------|-------------|

| VGA<br>640 × 480 | F     |           | 16        | 20        | 32          | 40          | 51          |

| QVGA             | F     | 16        | 32        | 40        | 64          | 80          | 102         |

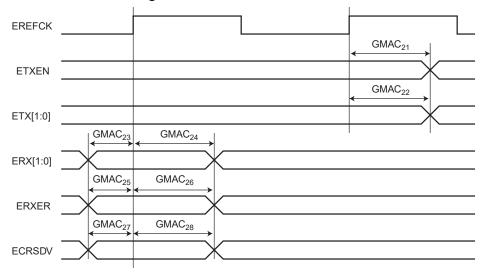

## SAM E70/S70/V70/V71 Family **GMAC - Ethernet MAC**

### 38.8.70 GMAC 1519 to Maximum Byte Frames Received Register

| Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TMXBFR<br>0x180<br>0x00000000<br>-                                                                  |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31                                      | 30                                                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                      | NFRX[                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31:24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R                                       | R                                                                                                        | R                                                                                                                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0                                       | 0                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 23                                      | 22                                                                                                       | 21                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                      | NFRX[                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R                                       | R                                                                                                        | R                                                                                                                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0                                       | 0                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |