Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 300MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 114                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 384K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                     |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                         |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 144-TFBGA                                                                                     |

| Supplier Device Package    | 144-TFBGA (10x10)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamv70q20b-cbt                    |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Supply Controller (SUPC)

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | (ONREG_UNUSED): Internal voltage regulator is not used (external power supply is used). |

| 1     | (ONREG_USED): Internal voltage regulator is used.                                       |

#### Bit 13 – BODDIS Brownout Detector Disable

**Note:** This bit is located in the VDDIO domain.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | (ENABLE): The core brownout detector is enabled.   |

| 1     | (DISABLE): The core brownout detector is disabled. |

#### Bit 12 – BODRSTEN Brownout Detector Reset Enable

**Note:** This bit is located in the VDDIO domain.

| Value | Description                                                                                          |

|-------|------------------------------------------------------------------------------------------------------|

| 0     | (NOT_ENABLE): The core reset signal vddcore_nreset is not affected when a brownout detection occurs. |

| 1     | (ENABLE): The core reset signal, vddcore_nreset is asserted when a brownout detection                |

|       | occurs.                                                                                              |

### Parallel Input/Output Controller (PIO)

#### Name: PIO SODR Offset: 0x0030 **Property:** Write-only Bit 31 30 29 28 27 26 25 24 P24 P31 P30 P29 P28 P27 P26 P25 Access Reset 17 Bit 23 22 21 20 19 18 16 P23 P22 P21 P19 P18 P17 P16 P20 Access Reset Bit 15 14 13 12 11 10 9 8 P15 P14 P13 P12 P11 P10 P9 P8 Access Reset Bit 7 5 3 2 6 4 1 0 P7 P6 P5 P4 P3 P2 P1 P0 Access Reset

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Set Output Data

| Va | lue | Description                                 |

|----|-----|---------------------------------------------|

| 0  |     | No effect.                                  |

| 1  |     | Sets the data to be driven on the I/O line. |

32.6.1.10 PIO Set Output Data Register

Writing a '0' to this bit disables the Management Port, and forces MDIO to high impedance state and MDC to low impedance.

| Value | Description                  |

|-------|------------------------------|

| 0     | Management Port is disabled. |

| 1     | Management Port is enabled.  |

#### Bit 3 – TXEN Transmit Enable

Writing a '1' to this bit enables the GMAC transmitter to send data.

Writing a '0' to this bit stops transmission immediately, the transmit pipeline and control registers is cleared, and the Transmit Queue Pointer Register will be set to point to the start of the transmit descriptor list.

| Value | Description           |

|-------|-----------------------|

| 0     | Transmit is disabled. |

| 1     | Transmit is enabled.  |

#### Bit 2 – RXEN Receive Enable

Writing a '1' to this bit enables the GMAC to receive data.

Writing a '0' to this bit stops frame reception immediately, and the receive pipeline is cleared. The Receive Queue Pointer Register is not affected.

| Value | Description          |

|-------|----------------------|

| 0     | Receive is disabled. |

| 1     | Receive is enabled.  |

#### Bit 1 – LBL Loop Back Local

Writing '1' to this bit connects GTX to GRX, GTXEN to GRXDV, and forces full duplex mode.

GRXCK and GTXCK may malfunction as the GMAC is switched into and out of internal loop back. It is important that receive and transmit circuits have already been disabled when making the switch into and out of internal loop back.

| Value | Description                  |

|-------|------------------------------|

| 0     | Loop back local is disabled. |

| 1     | Loop back local is enabled.  |

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TI<br>0x1DC<br>0x00000000<br>- |     |     |        |     |     |     |

|--------|-----------------------------------------|-------------------------------------|-----|-----|--------|-----|-----|-----|

| Bit    | 31                                      | 30                                  | 29  | 28  | 27     | 26  | 25  | 24  |

|        |                                         |                                     |     |     |        |     |     |     |

| Access |                                         |                                     |     |     |        |     |     |     |

| Reset  |                                         |                                     |     |     |        |     |     |     |

| 5.4    |                                         |                                     |     |     |        |     |     | 10  |

| Bit    | 23                                      | 22                                  | 21  | 20  | 19     | 18  | 17  | 16  |

|        |                                         |                                     |     | NIT | [7:0]  |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

| Bit    | 15                                      | 14                                  | 13  | 12  | 11     | 10  | 9   | 8   |

|        |                                         | ·                                   |     | ACN | S[7:0] |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

| Bit    | 7                                       | 6                                   | 5   | 4   | 3      | 2   | 1   | 0   |

|        |                                         |                                     |     | CNS | [7:0]  |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

#### 38.8.88 GMAC IEEE 1588 Timer Increment Register

#### Bits 23:16 - NIT[7:0] Number of Increments

The number of increments after which the alternative increment is used.

#### Bits 15:8 – ACNS[7:0] Alternative Count Nanoseconds

Alternative count of nanoseconds by which the 1588 Timer Nanoseconds Register will be incremented each clock cycle.

#### Bits 7:0 - CNS[7:0] Count Nanoseconds

A count of nanoseconds by which the IEEE 1588 Timer Nanoseconds Register will be incremented each clock cycle.

## USB High-Speed Interface (USBHS)

| Offset | Name | Bit Pos. |  |  |  |  |

|--------|------|----------|--|--|--|--|

|        |      | 23:16    |  |  |  |  |

|        |      | 31:24    |  |  |  |  |

### USB High-Speed Interface (USBHS)

- Bit 5 OVERFIES Overflow Interrupt Enable

- Bit 4 NAKEDES NAKed Interrupt Enable

- Bit 3 PERRES Pipe Error Interrupt Enable

- Bit 2 UNDERFIES Underflow Interrupt Enable

- Bit 1 TXOUTES Transmitted OUT Data Interrupt Enable

- Bit 0 RXINES Received IN Data Interrupt Enable

## High-Speed Multimedia Card Interface (HSMCI)

#### Bit 0 – FIFOMODE HSMCI Internal FIFO control mode

When the block length is greater than or equal to 3/4 of the HSMCI internal FIFO size, then the write transfer starts as soon as half the FIFO is filled. When the block length is greater than or equal to half the internal FIFO size, then the write transfer starts as soon as one quarter of the FIFO is filled. In other cases, the transfer starts as soon as the total amount of data is written in the internal FIFO.

| V | /alue | Description                                                                        |

|---|-------|------------------------------------------------------------------------------------|

| 0 | )     | A write transfer starts when a sufficient amount of data is written into the FIFO. |

| 1 |       | A write transfer starts as soon as one data is written into the FIFO.              |

### Serial Peripheral Interface (SPI)

last character transfer. Then, another DMA transfer can be started if SPI\_CR.SPIEN has previously been written.

#### 41.7.3.6 SPI Direct Access Memory Controller (DMAC)

In both Fixed and Variable modes, the Direct Memory Access Controller (DMAC) can be used to reduce processor overhead.

The fixed peripheral selection allows buffer transfers with a single peripheral. Using the DMAC is an optimal means, as the size of the data transfer between the memory and the SPI is either 8 bits or 16 bits. However, if the peripheral selection is modified, SPI\_MR must be reprogrammed.

The variable peripheral selection allows buffer transfers with multiple peripherals without reprogramming SPI\_MR. Data written in SPI\_TDR is 32 bits wide and defines the real data to be transmitted and the destination peripheral. Using the DMAC in this mode requires 32-bit wide buffers, with the data in the LSBs and the PCS and LASTXFER fields in the MSBs. However, the SPI still controls the number of bits (8 to 16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in terms of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

#### 41.7.3.7 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 slave peripherals by decoding the four chip select lines, NPCS0 to NPCS3 with an external decoder/demultiplexer (see figure below). This can be enabled by setting SPI\_MR.PCSDEC.

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e., one NPCS line driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field on the NPCS lines of either SPI\_MR or SPI\_TDR (depending on PS).

As the SPI sets a default value of 0xF on the chip select lines (i.e., all chip select lines at 1) when not processing any transfer, only 15 peripherals can be decoded.

The SPI has four chip select registers (SPI\_CSR0...SPI\_CSR3). As a result, when external decoding is activated, each NPCS chip select defines the characteristics of up to four peripherals. As an example, SPI\_CRS0 defines the characteristics of the externally decoded peripherals 0 to 3, corresponding to the PCS values 0x0 to 0x3. Consequently, the user has to make sure to connect compatible peripherals on the decoded chip select lines 0 to 3, 4 to 7, 8 to 11 and 12 to 14. The following figure shows this type of implementation.

If SPI\_CSRx.CSAAT bit is used, with or without the DMAC, the Mode Fault detection for NPCS0 line must be disabled. This is not needed for all other chip select lines since Mode Fault detection is only on NPCS0.

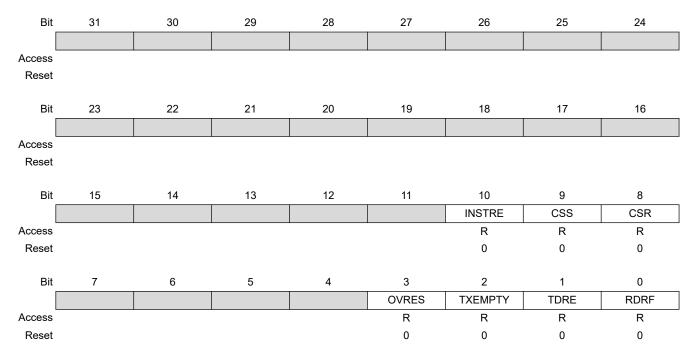

## 42.7.8 QSPI Interrupt Mask Register

| Name:     | QSPI_IMR   |

|-----------|------------|

| Offset:   | 0x1C       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

The following configuration values are valid for all listed bit names of this register:

- 0: The corresponding interrupt is not enabled.

- 1: The corresponding interrupt is enabled.

Bit 10 - INSTRE Instruction End Interrupt Mask

- Bit 9 CSS Chip Select Status Interrupt Mask

- Bit 8 CSR Chip Select Rise Interrupt Mask

- Bit 3 OVRES Overrun Error Interrupt Mask

- Bit 2 TXEMPTY Transmission Registers Empty Mask

- **Bit 1 TDRE** Transmit Data Register Empty Interrupt Mask

- Bit 0 RDRF Receive Data Register Full Interrupt Mask

### Inter-IC Sound Controller (I2SC)

#### 45.8.2 I2SC Mode Register

| Name:     | I2SC_MR    |

|-----------|------------|

| Offset:   | 0x04       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

The I2SC\_MR must be written when the I2SC is stopped. The proper sequence is to write to I2SC\_MR, then write to I2SC\_CR to enable the I2SC or to disable the I2SC before writing a new value to I2SC\_MR.

| Bit    | 31   | 30       | 29          | 28              | 27    | 26       | 25    | 24     |

|--------|------|----------|-------------|-----------------|-------|----------|-------|--------|

|        | IWS  | IMCKMODE | IMCKFS[5:0] |                 |       |          |       |        |

| Access | R/W  | R/W      | R/W         | R/W             | R/W   | R/W      | R/W   | R/W    |

| Reset  | 0    | 0        | 0           | 0               | 0     | 0        | 0     | 0      |

|        |      |          |             |                 |       |          |       |        |

| Bit    | 23   | 22       | 21          | 20              | 19    | 18       | 17    | 16     |

|        |      |          |             |                 | IMCKI | DIV[5:0] |       |        |

| Access |      |          | R/W         | R/W             | R/W   | R/W      | R/W   | R/W    |

| Reset  |      |          | 0           | 0               | 0     | 0        | 0     | 0      |

|        |      |          |             |                 |       |          |       |        |

| Bit    | 15   | 14       | 13          | 12              | 11    | 10       | 9     | 8      |

|        |      | TXSAME   | TXDMA       | TXMONO          |       | RXLOOP   | RXDMA | RXMONO |

| Access |      | R/W      | R/W         | R/W             |       | R/W      | R/W   | R/W    |

| Reset  |      | 0        | 0           | 0               |       | 0        | 0     | 0      |

|        |      |          |             |                 |       |          |       |        |

| Bit    | 7    | 6        | 5           | 4               | 3     | 2        | 1     | 0      |

|        | FORM | AT[1:0]  |             | DATALENGTH[2:0] |       |          |       | MODE   |

| Access | R/W  | R/W      |             | R/W             | R/W   | R/W      |       | R/W    |

| Reset  | 0    | 0        |             | 0               | 0     | 0        |       | 0      |

#### Bit 31 - IWS I2SC\_WS Slot Width

Refer to table Slot Length (I2S format).

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | I2SC_WS slot is 32 bits wide for DATALENGTH = 18/20/24 bits. |

| 1     | I2SC_WS slot is 24 bits wide for DATALENGTH = 18/20/24 bits. |

#### Bit 30 – IMCKMODE Master Clock Mode

**WARNING** If I2SC\_MCK frequency is the same as I2SC\_CK, IMCKMODE must be cleared. Refer to section Serial Clock and Word Select Generation and table Slot Length.

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | No master clock generated (Selected Clock drives I2SC_CK output).               |

| 1     | Master clock generated (internally generated clock is used as I2SC_MCK output). |

### Inter-IC Sound Controller (I2SC)

#### Bits 29:24 – IMCKFS[5:0] Master Clock to f<sub>s</sub> Ratio

Master clock frequency is [2 x 16 × (IMCKFS + 1)] / (IMCKDIV + 1) times the sample rate, i.e., I2SC\_WS frequency.

| Value | Name     | Description                        |

|-------|----------|------------------------------------|

| 0     | M2SF32   | Sample frequency ratio set to 32   |

| 1     | M2SF64   | Sample frequency ratio set to 64   |

| 2     | M2SF96   | Sample frequency ratio set to 96   |

| 3     | M2SF128  | Sample frequency ratio set to 128  |

| 5     | M2SF192  | Sample frequency ratio set to 192  |

| 7     | M2SF256  | Sample frequency ratio set to 256  |

| 11    | M2SF384  | Sample frequency ratio set to 384  |

| 15    | M2SF512  | Sample frequency ratio set to 512  |

| 23    | M2SF768  | Sample frequency ratio set to 768  |

| 31    | M2SF1024 | Sample frequency ratio set to 1024 |

| 47    | M2SF1536 | Sample frequency ratio set to 1536 |

| 63    | M2SF2048 | Sample frequency ratio set to 2048 |

Bits 21:16 – IMCKDIV[5:0] Selected Clock to I2SC Master Clock Ratio

I2SC\_MCK Master clock output frequency is Selected Clock divided by (IMCKDIV + 1). Refer to the IMCKFS field description.

#### Note:

- 1. This field is write-only. Always read as '0'.

- 2. Do not write a '0' to this field.

#### Bit 14 – TXSAME Transmit Data when Underrun

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | Zero sample transmitted when underrun.    |

| 1     | Previous sample transmitted when underrun |

**Bit 13 – TXDMA** Single or Multiple DMA Controller Channels for TransmitterDMA Controller Channels for Transmitter

| Val | lue | Description                                                                  |

|-----|-----|------------------------------------------------------------------------------|

| 0   |     | The transmitter uses only one DMA Controller channel for all audio channels. |

| 1   |     | The transmitter uses one DMA Controller channel per audio channel.           |

#### Bit 12 – TXMONO Transmit Mono

| Value | Description                                                                  |

|-------|------------------------------------------------------------------------------|

| 0     | Stereo                                                                       |

| 1     | Mono, with left audio samples duplicated to right audio channel by the I2SC. |

#### Bit 10 – RXLOOP Loopback Test Mode

| Value | Description                                                      |

|-------|------------------------------------------------------------------|

| 0     | Normal mode                                                      |

| 1     | I2SC_DO output of I2SC is internally connected to I2SC_DI input. |

US\_MR.MAX\_ITERATION. As soon as MAX\_ITERATION is reached, no error signal is driven on the I/O line and US\_CSR.ITER is set.

#### 46.6.4.3 Protocol T = 1

When operating in ISO7816 protocol T = 1, the transmission is similar to an asynchronous format with only one stop bit. The parity is generated when transmitting and checked when receiving. Parity error detection sets US\_CSR.PARE.

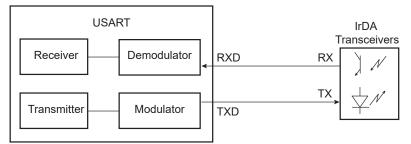

#### 46.6.5 IrDA Mode

The USART features an IrDA mode supplying half-duplex point-to-point wireless communication. It embeds the modulator and demodulator which allows a glueless connection to the infrared transceivers, as shown in the following figure. The modulator and demodulator are compliant with the IrDA specification version 1.1 and support data transfer speeds ranging from 2.4 kbit/s to 115.2 kbit/s.

The IrDA mode is enabled by writing the value 0x8 to US\_MR.USART\_MODE. The IrDA Filter register (US\_IF) is used to configure the demodulator filter. The USART transmitter and receiver operate in a normal Asynchronous mode and all parameters are accessible. Note that the modulator and the demodulator are activated.

#### Figure 46-32. Connection to IrDA Transceivers

The receiver and the transmitter must be enabled or disabled depending on the direction of the transmission to be managed.

To receive IrDA signals, the following needs to be done:

- Disable TX and Enable RX

- Configure the TXD pin as PIO and set it as an output to 0 (to avoid LED emission). Disable the internal pull-up (better for power consumption).

- Receive data

#### 46.6.5.1 IrDA Modulation

For baud rates up to and including 115.2 kbit/s, the RZI modulation scheme is used. "0" is represented by a light pulse of 3/16th of a bit time. Some examples of signal pulse duration are shown in the following table.

#### Table 46-9. IrDA Pulse Duration

| Baud Rate   | Pulse Duration (3/16) |

|-------------|-----------------------|

| 2.4 kbit/s  | 78.13 μs              |

| 9.6 kbit/s  | 19.53 µs              |

| 19.2 kbit/s | 9.77 µs               |

| 38.4 kbit/s | 4.88 μs               |

**Controller Area Network (MCAN)**

| _      |            |              |           |            |      |        |           |                |      |      |

|--------|------------|--------------|-----------|------------|------|--------|-----------|----------------|------|------|

| Offset | Name       | Bit Pos.     |           |            |      |        |           |                |      |      |

|        |            | 7:0          |           |            | FLSS | A[5:0] |           |                |      |      |

| 0x84   | MCAN_SIDFC | 15:8         |           |            |      | FLSS   | A[13:6]   |                |      |      |

| 0,04   |            | 23:16        |           |            |      | LSS    | [7:0]     |                |      |      |

|        |            | 31:24        |           |            |      |        |           |                |      |      |

|        |            | 7:0          |           |            | FLES | A[5:0] |           |                |      |      |

| 0x88   | MCAN_XIDFC | 15:8         |           |            |      | FLES   | A[13:6]   |                |      |      |

| 0x00   |            | 23:16        |           |            |      |        | LSE[6:0]  |                |      |      |

|        |            | 31:24        |           |            |      |        |           |                |      |      |

| 0x8C   |            |              |           |            |      |        |           |                |      |      |

|        | Reserved   |              |           |            |      |        |           |                |      |      |

| 0x8F   |            |              |           |            |      |        |           |                |      |      |

|        |            | 7:0          |           |            |      |        | Л[7:0]    |                |      |      |

| 0x90   | MCAN XIDAM | 15:8         |           |            |      |        | I[15:8]   |                |      |      |

|        | _          | 23:16        |           |            | 1    | EIDM   | [23:16]   |                |      |      |

|        |            | 31:24        |           |            |      |        |           | EIDM[28:24]    |      |      |

|        |            | 7:0          |           | [1:0]      |      |        |           | <b>(</b> [5:0] |      |      |

| 0x94   | MCAN_HPMS  | 15:8         | FLST      |            |      |        | FIDX[6:0] |                |      |      |

|        |            | 23:16        |           |            |      |        |           |                |      |      |

|        |            | 31:24        |           |            |      |        |           |                |      |      |

|        |            | 7:0          | ND7       | ND6        | ND5  | ND4    | ND3       | ND2            | ND1  | ND0  |

| 0x98   | MCAN_NDAT1 | 15:8         | ND15      | ND14       | ND13 | ND12   | ND11      | ND10           | ND9  | ND8  |

|        |            | 23:16        | ND23      | ND22       | ND21 | ND20   | ND19      | ND18           | ND17 | ND16 |

|        |            | 31:24        | ND31      | ND30       | ND29 | ND28   | ND27      | ND26           | ND25 | ND24 |

|        |            | 7:0          | ND39      | ND38       | ND37 | ND36   | ND35      | ND34           | ND33 | ND32 |

| 0x9C   | MCAN_NDAT2 | 15:8         | ND47      | ND46       | ND45 | ND44   | ND43      | ND42           | ND41 | ND40 |

|        |            | 23:16        | ND55      | ND54       | ND53 | ND52   | ND51      | ND50           | ND49 | ND48 |

|        |            | 31:24        | ND63      | ND62       | ND61 | ND60   | ND59      | ND58           | ND57 | ND56 |

|        |            | 7:0          | F0SA[5:0] |            |      |        |           |                |      |      |

| 0xA0   | MCAN_RXF0C | 15:8         |           | F0SA[13:6] |      |        |           |                |      |      |

|        |            | 23:16        |           | F0S[6:0]   |      |        |           |                |      |      |

|        |            | 31:24        | F0OM      |            |      |        | F0WM[6:0] |                |      |      |

|        |            | 7:0<br>15:8  |           |            |      |        | F0FL[6:0] | 1[5:0]         |      |      |

| 0xA4   | MCAN_RXF0S |              |           |            |      |        |           | I[5:0]         |      |      |

|        |            | 23:16        |           |            |      |        | FUP       | I[5:0]         | RF0L | F0F  |

|        |            | 31:24<br>7:0 |           |            |      |        | EOA       | 1(5:0)         | REVL | FUF  |

|        |            | 15:8         |           |            |      |        | FUA       | I[5:0]         |      |      |

| 0xA8   | MCAN_RXF0A | 23:16        |           |            |      |        |           |                |      |      |

|        |            | 31:24        |           |            |      |        |           |                |      |      |

|        |            | 7:0          |           |            | RBC  | A[5:0] |           |                |      |      |

|        |            | 15:8         |           |            | 100  |        | A[13:6]   |                |      |      |

| 0xAC   | MCAN_RXBC  | 23:16        |           |            |      | ND3F   | ų io.oj   |                |      |      |

|        |            | 31:24        |           |            |      |        |           |                |      |      |

|        |            | 7:0          |           |            | F19  | A[5:0] |           |                |      |      |

| 0xB0   | MCAN RXF1C | 15:8         |           |            | 110/ |        | [13:6]    |                |      |      |

| 0,00   | MCAN_RXF1C | 23:16        |           |            |      | 1134   | F1S[6:0]  |                |      |      |

|        |            | 20.10        |           |            |      |        | 1 10[0.0] |                |      |      |

- SYNC: Each channel has a synchronization signal SYNC. When asserted, this signal has the same effect as a software trigger. The SYNC signals of all channels are asserted simultaneously by writing TC\_BCR with SYNC set.

- Compare RC Trigger: RC is implemented in each channel and can provide a trigger when the counter value matches the RC value if TC\_CMRx.CPCTRG is set .

The channel can also be configured to have an external trigger. In Capture mode, the external trigger signal can be selected between TIOAx and TIOBx. In Waveform mode, an external event can be programmed on one of the following signals: TIOBx, XC0, XC1 or XC2. This external event can then be programmed to perform a trigger by setting TC\_CMRx.ENETRG.

If an external trigger is used, the duration of the pulses must be longer than the peripheral clock period in order to be detected.

#### 50.6.7 Capture Mode

Capture mode is entered by clearing TC\_CMRx.WAVE.

Capture mode allows the TC channel to perform measurements such as pulse timing, frequency, period, duty cycle and phase on TIOAx and TIOBx signals which are considered as inputs.

The figure Figure 50-6 shows the configuration of the TC channel when programmed in Capture mode.

#### 50.6.8 Capture Registers A and B

Registers A and B (TC\_RA and TC\_RB) are used as capture registers. They can be loaded with the counter value when a programmable event occurs on the signal TIOAx.

TC\_CMRx.LDRA defines the TIOAx selected edge for the loading of TC\_RA, and TC\_CMRx.LDRB defines the TIOAx selected edge for the loading of TC\_RB.

The subsampling ratio defined by TC\_CMRx.SBSMPLR is applied to these selected edges, so that the loading of Register A and Register B occurs once every 1, 2, 4, 8 or 16 selected edges.

TC\_RA is loaded only if it has not been loaded since the last trigger or if TC\_RB has been loaded since the last loading of TC\_RA.

TC\_RB is loaded only if TC\_RA has been loaded since the last trigger or the last loading of TC\_RB.

Loading TC\_RA or TC\_RB before the read of the last value loaded sets TC\_SR.LOVRS. In this case, the old value is overwritten.

When DMA is used (on channel 0), the Register AB (TC\_RAB) address must be configured as source address of the transfer. TC\_RAB provides the next unread value from TC\_RA and TC\_RB. It may be read by the DMA after a request has been triggered upon loading TC\_RA or TC\_RB.

#### 50.6.9 Transfer with DMAC in Capture Mode

The DMAC can perform access from the TC to system memory in Capture mode only.

The following figure illustrates how TC\_RA and TC\_RB can be loaded in the system memory without processor intervention.

٠

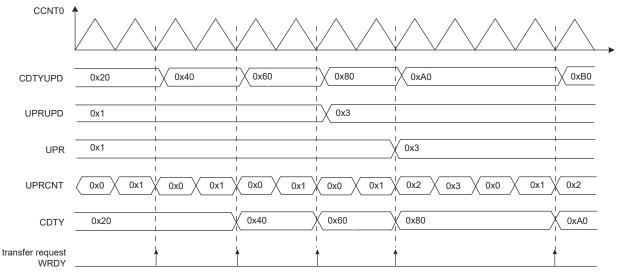

• UNRE: this flag is set to '1' when the update period defined by the UPR field has elapsed while the whole data has not been written by the DMA Controller. It is reset to '0' when PWM\_ISR2 is read.

Depending on the interrupt mask in PWM\_IMR2, an interrupt can be generated by these flags.

Sequence for Method 3:

- 1. Select the automatic write of duty-cycle values and automatic update by setting the field UPDM to 2 in the PWM\_SCM register.

- 2. Define the synchronous channels by the bits SYNCx in the PWM\_SCM register.

- 3. Define the update period by the field UPR in the PWM\_SCUP register.

- 4. Define when the WRDY flag and the corresponding DMA Controller transfer request must be set in the update period by the PTRM bit and the PTRCS field in the PWM\_SCM register (at the end of the update period or when a comparison matches).

- 5. Define the DMA Controller transfer settings for the duty-cycle values and enable it in the DMA Controller registers

- 6. Enable the synchronous channels by writing CHID0 in the PWM\_ENA register.

- 7. If an update of the period value and/or of the dead-time values is required, write registers that need to be updated (PWM\_CPRDUPDx, PWM\_DTUPDx), else go to Step 10.

- 8. Set UPDULOCK to '1' in PWM\_SCUC.

- 9. The update of these registers will occur at the beginning of the next PWM period. At this moment the bit UPDULOCK is reset, go to Step 7. for new values.

- 10. If an update of the update period value is required, check first that write of a new update value is possible by polling the flag WRDY (or by waiting for the corresponding interrupt) in PWM\_ISR2, else go to Step 14.

- 11. Write the register that needs to be updated (PWM\_SCUPUPD).

- 12. The update of this register will occur at the next PWM period of the synchronous channels when the Update Period is elapsed. Go to Step 10. for new values.

- 13. Wait for the DMA status flag indicating that the buffer transfer is complete. If the transfer has ended, define a new DMA transfer for new duty-cycle values. Go to Step 5.

#### Figure 51-21. Method 3 (UPDM = 2 and PTRM = 0)

#### 51.7.1 PWM Clock Register

| Name:     | PWM_CLK    |

|-----------|------------|

| Offset:   | 0x00       |

| Reset:    | 0x00000000 |

| Property: | Read/Write |

This register can only be written if bits WPSWS0 and WPHWS0 are cleared in the PWM Write Protection Status Register.

| Bit    | 31  | 30  | 29  | 28   | 27        | 26  | 25     | 24  |

|--------|-----|-----|-----|------|-----------|-----|--------|-----|

|        |     |     |     |      | PREB[3:0] |     |        |     |

| Access |     | •   |     |      | R/W       | R/W | R/W    | R/W |

| Reset  |     |     |     |      | 0         | 0   | 0      | 0   |

|        |     |     |     |      |           |     |        |     |

| Bit    | 23  | 22  | 21  | 20   | 19        | 18  | 17     | 16  |

|        |     |     |     | DIVE | 8[7:0]    |     |        |     |

| Access | R/W | R/W | R/W | R/W  | R/W       | R/W | R/W    | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0         | 0   | 0      | 0   |

|        |     |     |     |      |           |     |        |     |

| Bit    | 15  | 14  | 13  | 12   | 11        | 10  | 9      | 8   |

|        |     |     |     |      |           | PRE | A[3:0] |     |

| Access |     |     |     |      | R/W       | R/W | R/W    | R/W |

| Reset  |     |     |     |      | 0         | 0   | 0      | 0   |

|        |     |     |     |      |           |     |        |     |

| Bit    | 7   | 6   | 5   | 4    | 3         | 2   | 1      | 0   |

|        |     |     |     | DIVA | [7:0]     |     |        |     |

| Access | R/W | R/W | R/W | R/W  | R/W       | R/W | R/W    | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0         | 0   | 0      | 0   |

Bits 27:24 – PREB[3:0] CLKB Source Clock Selection

| Value | Name        | Description           |

|-------|-------------|-----------------------|

| 0     | CLK         | Peripheral clock      |

| 1     | CLK_DIV2    | Peripheral clock/2    |

| 2     | CLK_DIV4    | Peripheral clock/4    |

| 3     | CLK_DIV8    | Peripheral clock/8    |

| 4     | CLK_DIV16   | Peripheral clock/16   |

| 5     | CLK_DIV32   | Peripheral clock/32   |

| 6     | CLK_DIV64   | Peripheral clock/64   |

| 7     | CLK_DIV128  | Peripheral clock/128  |

| 8     | CLK_DIV256  | Peripheral clock/256  |

| 9     | CLK_DIV512  | Peripheral clock/512  |

| 10    | CLK_DIV1024 | Peripheral clock/1024 |

| Other | -           | Reserved              |

Bits 23:16 - DIVB[7:0] CLKB Divide Factor

## Pulse Width Modulation Controller (PWM)

### 51.7.4 PWM Status Register

|        | Name:<br>Offset:<br>Reset:<br>Property: | PWM_SR<br>0x0C<br>0x00000000<br>Read-only |    |    |       |       |       |       |

|--------|-----------------------------------------|-------------------------------------------|----|----|-------|-------|-------|-------|

| Bit    | 31                                      | 30                                        | 29 | 28 | 27    | 26    | 25    | 24    |

|        |                                         |                                           |    |    |       |       |       |       |

| Access |                                         |                                           |    |    |       |       |       |       |

| Reset  |                                         |                                           |    |    |       |       |       |       |

|        |                                         |                                           |    |    |       |       |       |       |

| Bit    | 23                                      | 22                                        | 21 | 20 | 19    | 18    | 17    | 16    |

|        |                                         |                                           |    |    |       |       |       |       |

| Access |                                         |                                           |    |    |       |       |       |       |

| Reset  |                                         |                                           |    |    |       |       |       |       |

|        |                                         |                                           |    |    |       |       |       |       |

| Bit    | 15                                      | 14                                        | 13 | 12 | 11    | 10    | 9     | 8     |

|        |                                         |                                           |    |    |       |       |       |       |

| Access |                                         |                                           |    |    |       |       |       |       |

| Reset  |                                         |                                           |    |    |       |       |       |       |

|        |                                         |                                           |    |    |       |       |       |       |

| Bit    | 7                                       | 6                                         | 5  | 4  | 3     | 2     | 1     | 0     |

|        |                                         |                                           |    |    | CHID3 | CHID2 | CHID1 | CHID0 |

| Access |                                         |                                           |    |    | R     | R     | R     | R     |

| Reset  |                                         |                                           |    |    | 0     | 0     | 0     | 0     |

|        |                                         |                                           |    |    |       |       |       |       |

#### Bits 0, 1, 2, 3 - CHIDx Channel ID

| Value | Description                           |

|-------|---------------------------------------|

| 0     | PWM output for channel x is disabled. |

| 1     | PWM output for channel x is enabled.  |

- By using the PWM peripheral clock divided by a given prescaler value "X" (where  $X = 2^{PREA}$  is 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, or 1024). The resulting period formula is:

#### $(2 \times X \times CPRD)$

$f_{\text{peripheral clock}}$

- By using the PWM peripheral clock divided by a given prescaler value "X" (see above) and by either the DIVA or the DIVB divider. The formula becomes, respectively:

$\frac{(2 \times X \times \text{CPRD} \times \text{DIVA})}{f_{\text{peripheral clock}}} \text{ or } \frac{(2 \times X \times \text{CPRD} \times \text{DIVB})}{f_{\text{peripheral clock}}}$

## **Electrical Characteristics for SAM E70/S70**

| Symbol                | Parameter                                             | Conditions                       | Min  | Тур | Мах  | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------|------|-----|------|------|

|                       | Allowable<br>Voltage<br>Ripple                        | rms value 10<br>kHz to 20<br>MHz | -    | _   | 20   | mv   |

|                       | PLL A and<br>Main<br>Oscillator<br>Supply             | _                                | 1.08 | 1.2 | 1.32 | V    |

| V <sub>DDPLL</sub>    | Allowable<br>Voltage                                  | rms value 10<br>kHz to 10<br>MHz | _    | _   | 20   | mV   |

|                       | Ripple                                                | rms value ><br>10 MHz            | -    | -   | 10   |      |

| V <sub>DDUTMIC</sub>  | DC Supply<br>UDPHS and<br>UHPHS<br>UTMI+ Core         | _                                | 1.08 | 1.2 | 1.32 | V    |

|                       | Allowable<br>Voltage<br>Ripple                        | rms value 10<br>kHz to 10<br>MHz | _    | _   | 10   | mV   |

| V <sub>DDUTMII</sub>  | DC Supply<br>UDPHS and<br>UHPHS<br>UTMI+<br>Interface | _                                | 3.0  | 3.3 | 3.6  | V    |

|                       | Allowable<br>Voltage<br>Ripple                        | rms value 10<br>kHz to 10<br>MHz | _    | _   | 20   | mV   |

|                       | DC Supply<br>UTMI PLL                                 | -                                | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DDPLLUSB</sub> | Allowable<br>Voltage<br>Ripple                        | rms value 10<br>kHz to 10<br>MHz | _    | _   | 10   | mV   |

#### Note:

1.  $V_{DDIO}$  voltage must be equal to  $V_{DDIN}$  voltage.

### Table 59-4. DC Characteristics

| Symbol | Parameter               | Conditions             | Min  | Тур | Мах                | Unit |

|--------|-------------------------|------------------------|------|-----|--------------------|------|

| VIL    | Low-level Input Voltage | GPIO_MLB               | -0.3 | _   | 0.7                | V    |

|        |                         | GPIO_AD, GPIO_CLK      | -0.3 | _   | 0.8                |      |

|        |                         | GPIO, CLOCK, RST, TEST | -0.3 | _   | $V_{DDIO} \ge 0.3$ |      |

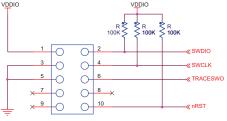

#### 60.2.2 Serial Wire Debug Interface

| Signal Name      | Recommended Pin Connection                                                                                                                                      | Description                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWCLK/TCK        | Pullup (100 kOhm) <sup>(1)</sup><br>If debug mode is not required, this pin<br>can be used as GPIO.                                                             | Serial Wire Clock / Test Clock (Boundary<br>scan mode only)<br>This pin is a Schmitt trigger input.<br>No internal pullup resistor at reset.                                          |

| SWDIO/TMS        | Pullup (100 kOhm) <sup>(1)</sup><br>If debug mode is not required, this pin<br>can be used as GPIO.                                                             | Serial Wire Input-Output / Test Mode<br>Select (Boundary scan mode only).<br>This pin is a Schmitt trigger input.<br>No internal pullup resistor at reset.                            |

| TDI              | Floating.<br>If boundary mode is not required, this pin<br>can be used as GPIO.                                                                                 | Test Data In (Boundary scan mode only)<br>This pin is a Schmitt trigger input.<br>No internal pullup resistor at reset.                                                               |

| TRACESWO/TD<br>O | Floating.<br>If boundary mode is not required, this pin<br>can be used as GPIO.                                                                                 | Test Data Out (Boundary scan mode only)<br>Output driven at up to VDDIO                                                                                                               |

| JTAGSEL          | In harsh environments <sup>(2)</sup> , it is strongly recommended to tie this pin to GND if not used or to add an external low-value resistor (such as 1 kOhm). | JTAG Selection.<br>Internal permanent pulldown resistor to<br>GNDBU (15 kOhm).<br>Must be tied to VDDIO to enter JTAG<br>Boundary Scan with TST tied to VDDIO<br>and PD0 tied to GND. |

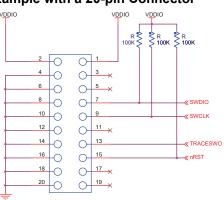

#### Figure 60-1. SWD Schematic Example with a 10-pin Connector

#### Figure 60-2. SWD Schematic Example with a 20-pin Connector