#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 300MHz                                                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 75                                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 256K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                      |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 100-LQFP                                                                                       |

| Supplier Device Package    | 100-LQFP (14x14)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamv71n19b-aab                     |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 18.3.4.1 Write Handshaking

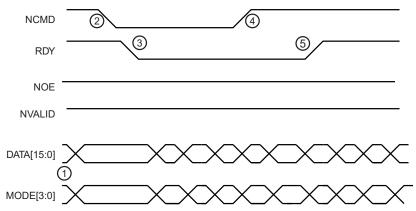

For details on the write handshaking sequence, refer to the following figure and table.

#### Figure 18-2. Parallel Programming Timing, Write Sequence

#### Table 18-4. Write Handshake

| Step | Programmer Action              | Device Action                        | Data I/O |

|------|--------------------------------|--------------------------------------|----------|

| 1    | Sets MODE and DATA signals     | Waits for NCMD low                   | Input    |

| 2    | Clears NCMD signal             | Latches MODE and DATA                | Input    |

| 3    | Waits for RDY low              | Clears RDY signal                    | Input    |

| 4    | Releases MODE and DATA signals | Executes command and polls NCMD high | Input    |

| 5    | Sets NCMD signal               | Executes command and polls NCMD high | Input    |

| 6    | Waits for RDY high             | Sets RDY                             | Input    |

#### 18.3.4.2 Read Handshaking

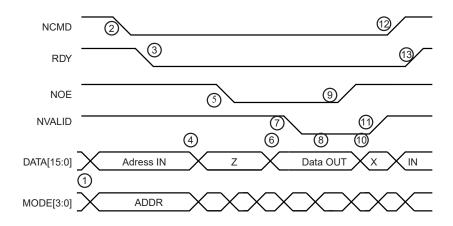

For details on the read handshaking sequence, refer to the following figure and table.

#### Figure 18-3. Parallel Programming Timing, Read Sequence

- 1. Round-robin Arbitration (default)

- 2. Fixed Priority Arbitration

Each algorithm may be complemented by selecting a default master configuration for each slave.

When re-arbitration is required, specific conditions apply. Refer to the "Arbitration Rules" section.

#### 19.3.3.1 Arbitration Rules

Each arbiter has the ability to arbitrate between requests from two or more masters. To avoid burst breaking and to provide maximum throughput for slave interfaces, arbitration should take place during the following cycles:

- Idle cycles: When a slave is not connected to any master or is connected to a master which is not currently accessing it

- Single cycles: When a slave is performing a single access

- End of Burst cycles: When the current cycle is the last cycle of a burst transfer. For a defined length burst, predicted end of burst matches the size of the transfer but is managed differently for undefined length burst. Refer to the "Undefined Length Burst Arbitration" section.

- Slot cycle limit: When the slot cycle counter has reached the limit value indicating that the current master access is too long and must be broken. Refer to the "Slot Cycle Limit Arbitration" section.

#### 19.3.3.1.1 Undefined Length Burst Arbitration

In order to prevent slave handling during undefined length bursts, the user can trigger the re-arbitration before the end of the incremental bursts. The re-arbitration period can be selected from the following Undefined Length Burst Type (ULBT) possibilities:

- 1. Unlimited: no predetermined end of burst is generated. This value enables 1-Kbyte burst lengths.

- 2. 1-beat bursts: predetermined end of burst is generated at each single transfer during the INCR transfer.

- 3. 4-beat bursts: predetermined end of burst is generated at the end of each 4-beat boundary during INCR transfer.

- 4. 8-beat bursts: predetermined end of burst is generated at the end of each 8-beat boundary during INCR transfer.

- 5. 16-beat bursts: predetermined end of burst is generated at the end of each 16-beat boundary during INCR transfer.

- 6. 32-beat bursts: predetermined end of burst is generated at the end of each 32-beat boundary during INCR transfer.

- 7. 64-beat bursts: predetermined end of burst is generated at the end of each 64-beat boundary during INCR transfer.

- 8. 128-beat bursts: predetermined end of burst is generated at the end of each 128-beat boundary during INCR transfer.

The use of undefined length16-beat bursts, or less, is discouraged since this decreases the overall bus bandwidth due to arbitration and slave latencies at each first access of a burst.

If the master does not permanently and continuously request the same slave or has an intrinsically limited average throughput, the ULBT should be left at its default unlimited value, knowing that the AHB specification natively limits all word bursts to 256 beats and double-word bursts to 128 beats because of its 1-Kbyte address boundaries.

Unless duly needed, the ULBT should be left at its default value of 0 for power saving.

This selection is made through the ULBT field of the Master Configuration Registers (MATRIX\_MCFG).

## **Power Management Controller (PMC)**

#### 31.20.2 PMC System Clock Disable Register

Name:PMC\_SCDROffset:0x0004Property:Write-only

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31   | 30   | 29     | 28   | 27   | 26   | 25   | 24   |

|--------|------|------|--------|------|------|------|------|------|

|        |      |      |        |      |      |      |      |      |

| Access |      |      |        |      |      |      |      |      |

| Reset  |      |      |        |      |      |      |      |      |

|        |      |      |        |      |      |      |      |      |

| Bit    | 23   | 22   | 21     | 20   | 19   | 18   | 17   | 16   |

|        |      |      |        |      |      |      |      |      |

| Access |      |      |        |      |      |      |      |      |

| Reset  |      |      |        |      |      |      |      |      |

|        |      |      |        |      |      |      |      |      |

| Bit    | 15   | 14   | 13     | 12   | 11   | 10   | 9    | 8    |

|        | PCK7 | PCK6 | PCK5   | PCK4 | PCK3 | PCK2 | PCK1 | PCK0 |

| Access |      |      |        |      |      |      |      |      |

| Reset  |      |      |        |      |      |      |      |      |

|        |      |      |        |      |      |      |      |      |

| Bit    | 7    | 6    | 5      | 4    | 3    | 2    | 1    | 0    |

|        |      |      | USBCLK |      |      |      |      |      |

| Access |      |      |        |      |      |      |      |      |

| Reset  |      |      |        |      |      |      |      |      |

#### Bits 8, 9, 10, 11, 12, 13, 14, 15 – PCK Programmable Clock x Output Disable

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | No effect.                                            |

| 1     | Disables the corresponding Programmable Clock output. |

#### Bit 5 – USBCLK Disable USB FS Clock

| Value | Description            |

|-------|------------------------|

| 0     | No effect.             |

| 1     | Disables USB FS clock. |

## Power Management Controller (PMC)

|        | Name:<br>Offset:<br>Reset:<br>Property: | PMC_SCSR<br>0x0008<br>0x00000001<br>Read-only |        |      |      |      |      |       |

|--------|-----------------------------------------|-----------------------------------------------|--------|------|------|------|------|-------|

| Bit    | 31                                      | 30                                            | 29     | 28   | 27   | 26   | 25   | 24    |

|        |                                         |                                               |        |      |      |      |      |       |

| Access |                                         |                                               |        |      |      |      |      |       |

| Reset  |                                         |                                               |        |      |      |      |      |       |

| Bit    | 23                                      | 22                                            | 21     | 20   | 19   | 18   | 17   | 16    |

|        |                                         |                                               |        |      |      |      |      |       |

| Access |                                         | -                                             | 1      | 1    |      |      |      |       |

| Reset  |                                         |                                               |        |      |      |      |      |       |

| Bit    | 15                                      | 14                                            | 13     | 12   | 11   | 10   | 9    | 8     |

|        | PCK7                                    | PCK6                                          | PCK5   | PCK4 | PCK3 | PCK2 | PCK1 | PCK0  |

| Access |                                         | ŀ                                             |        |      |      |      |      |       |

| Reset  | 0                                       | 0                                             | 0      | 0    | 0    | 0    | 0    | 0     |

| Bit    | 7                                       | 6                                             | 5      | 4    | 3    | 2    | 1    | 0     |

|        |                                         |                                               | USBCLK |      |      |      |      | HCLKS |

| Access |                                         |                                               |        |      |      |      |      |       |

| Reset  |                                         |                                               | 0      |      |      |      |      | 1     |

#### 31.20.3 PMC System Clock Status Register

#### Bits 8, 9, 10, 11, 12, 13, 14, 15 - PCK Programmable Clock x Output Status

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | The corresponding Programmable Clock output is disabled. |

| 1     | The corresponding Programmable Clock output is enabled.  |

#### Bit 5 - USBCLK USB FS Clock Status

| Value | Description                   |

|-------|-------------------------------|

| 0     | The USB FS clock is disabled. |

| 1     | The USB FS clock is enabled.  |

#### Bit 0 - HCLKS HCLK Status

| Value | Description       |

|-------|-------------------|

| 0     | HCLK is disabled. |

| 1     | HCLK is enabled.  |

### **Power Management Controller (PMC)**

#### 31.20.11 PMC Master Clock Register

| Name:     | PMC_MCKR   |

|-----------|------------|

| Offset:   | 0x0030     |

| Reset:    | 0x00000001 |

| Property: | Read/Write |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

|        | UPLLDIV2 |    | UPLL Clock Division               |               |            |    |     |        |  |

|--------|----------|----|-----------------------------------|---------------|------------|----|-----|--------|--|

|        | 0        |    | UPLLCK frequency is divided by 1. |               |            |    |     |        |  |

|        | 1        |    | UPLLCK fre                        | quency is div | ided by 2. |    |     |        |  |

| Bit    | 31       | 30 | 29                                | 28            | 27         | 26 | 25  | 24     |  |

| Access |          |    |                                   |               |            |    |     |        |  |

| Reset  |          |    |                                   |               |            |    |     |        |  |

| Bit    | 23       | 22 | 21                                | 20            | 19         | 18 | 17  | 16     |  |

| Access |          |    |                                   |               |            |    |     |        |  |

| Reset  |          |    |                                   |               |            |    |     |        |  |

| Bit    | 15       | 14 | 13                                | 12            | 11         | 10 | 9   | 8      |  |

|        |          |    | UPLLDIV2                          |               |            |    | MDI | /[1:0] |  |

| Access |          |    |                                   |               |            |    |     |        |  |

| Reset  |          |    | 0                                 |               |            |    | 0   | 0      |  |

| Bit    | 7        | 6  | 5                                 | 4             | 3          | 2  | 1   | 0      |  |

|        |          |    | PRES[2:0]                         |               |            |    | CSS | [1:0]  |  |

| Access |          |    |                                   |               |            |    |     |        |  |

| Reset  |          | 0  | 0                                 | 0             |            |    | 0   | 1      |  |

Bit 13 – UPLLDIV2 UPLL Divider by 2

#### Bits 9:8 - MDIV[1:0] Master Clock Division

| Value | Name     | Description               |

|-------|----------|---------------------------|

| 0     | EQ_PCK   | MCK is FCLK divided by 1. |

| 1     | PCK_DIV2 | MCK is FCLK divided by 2. |

| 2     | PCK_DIV4 | MCK is FCLK divided by 4. |

| 3     | PCK_DIV3 | MCK is FCLK divided by 3. |

#### Bits 6:4 - PRES[2:0] Processor Clock Prescaler

| Value | Name  | Description                 |

|-------|-------|-----------------------------|

| 0     | CLK_1 | Selected clock              |

| 1     | CLK_2 | Selected clock divided by 2 |

| 2     | CLK_4 | Selected clock divided by 4 |

#### 34.7.3 SDRAMC Configuration Register

| Name:     | SDRAMC_CR  |

|-----------|------------|

| Offset:   | 0x08       |

| Reset:    | 0x852372C0 |

| Property: | Read/Write |

|        |     | Bit 7 (DBW) r | nust always b | e set when p | rogramming t | he SDRAMC | CR.               |     |

|--------|-----|---------------|---------------|--------------|--------------|-----------|-------------------|-----|

| Bit    | 31  | 30            | 29            | 28           | 27           | 26        | 25                | 24  |

|        |     | TXSI          | ٦[3:0]        |              |              | TRA       | S[3:0]            |     |

| Access | R/W | R/W           | R/W           | R/W          | R/W          | R/W       | R/W               | R/W |

| Reset  | 1   | 0             | 0             | 0            | 0            | 1         | 0                 | 1   |

| Bit    | 23  | 22            | 21            | 20           | 19           | 18        | 17                | 16  |

|        |     | TRC           | D[3:0]        |              |              | TRI       | <b>&gt;</b> [3:0] |     |

| Access | R/W | R/W           | R/W           | R/W          | R/W          | R/W       | R/W               | R/W |

| Reset  | 0   | 0             | 1             | 0            | 0            | 0         | 1                 | 1   |

| Bit    | 15  | 14            | 13            | 12           | 11           | 10        | 9                 | 8   |

|        |     | TRC_TI        | RFC[3:0]      |              | TWR[3:0]     |           |                   |     |

| Access | R/W | R/W           | R/W           | R/W          | R/W          | R/W       | R/W               | R/W |

| Reset  | 0   | 1             | 1             | 1            | 0            | 0         | 1                 | 0   |

| Bit    | 7   | 6             | 5             | 4            | 3            | 2         | 1                 | 0   |

|        | DBW | CAS[1:0]      |               | NB           | NR[1:0]      |           | NC[1:0]           |     |

| Access | R/W | R/W           | R/W           | R/W          | R/W          | R/W       | R/W               | R/W |

| Reset  | 1   | 1             | 0             | 0            | 0            | 0         | 0                 | 0   |

## Bits 31:28 – TXSR[3:0] Exit Self-Refresh to Active Delay

Reset value is eight cycles.

This field defines the delay between SCKE set high and an Activate Command in number of cycles. Number of cycles is between 0 and 15.

#### Bits 27:24 - TRAS[3:0] Active to Precharge Delay

Reset value is five cycles.

This field defines the delay between an Activate Command and a Precharge Command in number of cycles. Number of cycles is between 0 and 15.

Bits 23:20 – TRCD[3:0] Row to Column Delay

Reset value is two cycles.

This field defines the delay between an Activate Command and a Read/Write Command in number of cycles. Number of cycles is between 0 and 15.

## Bits 19:16 – TRP[3:0] Row Precharge Delay

Reset value is three cycles.

© 2018 Microchip Technology Inc.

## Static Memory Controller (SMC)

#### 35.16.1.7 SMC Off-Chip Memory Scrambling Key2 Register

| Name:     | SMC_KEY2   |

|-----------|------------|

| Offset:   | 0x88       |

| Reset:    | 0x00000000 |

| Property: | Write-once |

Notes: 1. 'Write-once' access indicates that the first write access after a system reset prevents any further modification of the value of this register.

| Bit    | 31 | 30 | 29 | 28   | 27      | 26 | 25 | 24 |

|--------|----|----|----|------|---------|----|----|----|

|        |    |    |    | KEY2 | [31:24] |    |    |    |

| Access | L  |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 23 | 22 | 21 | 20   | 19      | 18 | 17 | 16 |

|        |    |    |    | KEY2 | [23:16] |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 15 | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|        |    |    |    | KEY2 | [15:8]  |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

|        |    |    |    |      |         |    |    |    |

| Bit    | 7  | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        |    |    |    | KEY  | 2[7:0]  |    |    |    |

| Access |    |    |    |      |         |    |    |    |

| Reset  | 0  | 0  | 0  | 0    | 0       | 0  | 0  | 0  |

**Bits 31:0 – KEY2[31:0]** Off-Chip Memory Scrambling (OCMS) Key Part 2 When off-chip memory scrambling is enabled, KEY1 and KEY2 values determine data scrambling.

| Bit       31       30       29       28       27       26       25       24         Access<br>Reset       Image: Constraint of the stress of the st |        | Name:<br>Offset:<br>Reset:<br>Property: | XDMAC_GSW<br>0x3C<br>0x00000000<br>Read-only | IS     |        |        |        |       |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|----------------------------------------------|--------|--------|--------|--------|-------|--------|

| Reset           Bit         23         22         21         20         19         18         17         16           SWRS23         SWRS22         SWRS21         SWRS20         SWRS19         SWRS18         SWRS17         SWRS16           Access         R         R         R         R         R         R         R         R           Access         R         N         R         R         R         R         R         R           Meset         0         0         0         0         0         0         0         0           Bit         15         14         13         12         11         10         9         8           SWRS15         SWRS14         SWRS13         SWRS12         SWRS11         SWRS10         SWRS9         SWRS8           Access         R         R         R         R         R         R         R         R           Access         I         R         R         R         R         R         R         R           Access         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit    | 31                                      | 30                                           | 29     | 28     | 27     | 26     | 25    | 24     |

| Reset           Bit         23         22         21         20         19         18         17         16           SWRS23         SWRS22         SWRS21         SWRS20         SWRS19         SWRS18         SWRS17         SWRS16           Access         R         R         R         R         R         R         R         R           Access         R         N         R         R         R         R         R         R           Meset         0         0         0         0         0         0         0         0           Bit         15         14         13         12         11         10         9         8           SWRS15         SWRS14         SWRS13         SWRS12         SWRS11         SWRS10         SWRS9         SWRS8           Access         R         R         R         R         R         R         R         R           Access         I         R         R         R         R         R         R         R           Access         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                         |                                              |        |        |        |        |       |        |

| Bit       23       22       21       20       19       18       17       16         SWRS23       SWRS22       SWRS21       SWRS20       SWRS19       SWRS18       SWRS17       SWRS16         Access       R       R       R       R       R       R       R       R       R         Reset       0       0       0       0       0       0       0       0       0         Bit       15       14       13       12       11       10       9       8         SWRS15       SWRS14       SWRS13       SWRS12       SWRS11       SWRS10       SWRS9       SWRS8         Access       R       R       R       R       R       R       R       R         Access       Image: SWRS15       SWRS14       SWRS13       SWRS12       SWRS11       SWRS10       SWRS9       SWRS8         Access       R       R       R       R       R       R       R       R         Reset       0       0       0       0       0       0       0       0       0         Bit       7       6       5       4       3       2 <td>Access</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Access |                                         |                                              |        |        |        |        |       |        |

| SWRS23SWRS22SWRS21SWRS20SWRS19SWRS18SWRS17SWRS16AccessRRRRRRRRRRReset0000000000Bit15141312111098SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset  |                                         |                                              |        |        |        |        |       |        |

| SWRS23SWRS22SWRS21SWRS20SWRS19SWRS18SWRS17SWRS16AccessRRRRRRRRRRReset0000000000Bit15141312111098SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                         |                                              |        |        |        |        |       |        |

| Access       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R <td>Bit</td> <td>-</td> <td></td> <td></td> <td>-</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit    | -                                       |                                              |        | -      |        |        |       |        |

| Reset0000000Bit15141312111098SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        | SWRS23                                  | SWRS22                                       |        | SWRS20 | SWRS19 | SWRS18 |       | SWRS16 |

| Bit15141312111098SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Access | R                                       | R                                            | R      | R      | R      | R      | R     | R      |

| SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reset  | 0                                       | 0                                            | 0      | 0      | 0      | 0      | 0     | 0      |

| SWRS15SWRS14SWRS13SWRS12SWRS11SWRS10SWRS9SWRS8AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                         |                                              |        |        |        |        |       |        |

| AccessRRRRRRRRReset00000000Bit76543210SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit    | 15                                      | 14                                           | 13     | 12     | 11     | 10     | 9     | 8      |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td></td> <td>SWRS15</td> <td>SWRS14</td> <td>SWRS13</td> <td>SWRS12</td> <td>SWRS11</td> <td>SWRS10</td> <td>SWRS9</td> <td>SWRS8</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | SWRS15                                  | SWRS14                                       | SWRS13 | SWRS12 | SWRS11 | SWRS10 | SWRS9 | SWRS8  |

| Bit         7         6         5         4         3         2         1         0           SWRS7         SWRS6         SWRS5         SWRS4         SWRS3         SWRS2         SWRS1         SWRS0           Access         R         R         R         R         R         R         R         R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Access | R                                       | R                                            | R      | R      | R      | R      | R     | R      |

| SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reset  | 0                                       | 0                                            | 0      | 0      | 0      | 0      | 0     | 0      |

| SWRS7SWRS6SWRS5SWRS4SWRS3SWRS2SWRS1SWRS0AccessRRRRRRRR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                         |                                              |        |        |        |        |       |        |

| Access R R R R R R R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit    | 7                                       | 6                                            | 5      | 4      | 3      | 2      | 1     | 0      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | SWRS7                                   | SWRS6                                        | SWRS5  | SWRS4  | SWRS3  | SWRS2  | SWRS1 | SWRS0  |

| Reset 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Access | R                                       | R                                            | R      | R      | R      | R      | R     | R      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reset  | 0                                       | 0                                            | 0      | 0      | 0      | 0      | 0     | 0      |

#### 36.9.16 XDMAC Global Channel Software Request Status Register

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23 – SWRS XDMAC Channel x Software Request Status

| Value | Description                           |

|-------|---------------------------------------|

| 0     | Channel x source request is serviced. |

| 1     | Channel x source request is pending.  |

## SAM E70/S70/V70/V71 Family GMAC - Ethernet MAC

#### 38.8.48 GMAC 512 to 1023 Byte Frames Transmitted Register

| Name:     | GMAC_TBFT1023 |

|-----------|---------------|

| Offset:   | 0x128         |

| Reset:    | 0x0000000     |

| Property: | -             |

| Bit             | 31          | 30     | 29     | 28                 | 27                     | 26     | 25     | 24     |

|-----------------|-------------|--------|--------|--------------------|------------------------|--------|--------|--------|

|                 |             |        |        | NFTX               | [31:24]                |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Reset           | 0           | 0      | 0      | 0                  | 0                      | 0      | 0      | 0      |

|                 |             |        |        |                    |                        |        |        |        |

| Bit             | 23          | 22     | 21     | 20                 | 19                     | 18     | 17     | 16     |

|                 |             |        |        | NFTX               | [23:16]                |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Reset           | 0           | 0      | 0      | 0                  | 0                      | 0      | 0      | 0      |

|                 |             |        |        |                    |                        |        |        |        |

| Bit             | 15          | 14     | 13     | 12                 | 11                     | 10     | 9      | 8      |

|                 | NFTX[15:8]  |        |        |                    |                        |        |        |        |

|                 |             |        |        |                    | [15.6]                 |        |        |        |

| Access          | R           | R      | R      | R                  | R                      | R      | R      | R      |

| Access<br>Reset |             | R<br>0 | R<br>0 |                    |                        | R<br>0 | R<br>0 | R<br>0 |

|                 |             |        |        | R                  | R                      |        |        |        |

|                 | 0           |        |        | R                  | R                      |        |        |        |

| Reset           | 0           | 0      | 0      | R<br>0<br>4        | R<br>0                 | 0      |        | 0      |

| Reset           | 0<br>7      | 0      | 0      | R<br>0<br>4        | R<br>0<br>3            | 0      |        | 0      |

| Reset<br>Bit    | 0<br>7<br>R | 0<br>6 | 0<br>5 | R<br>0<br>4<br>NFT | R<br>0<br>3<br><([7:0] | 0<br>2 | 0      | 0      |

Bits 31:0 – NFTX[31:0] 512 to 1023 Byte Frames Transmitted without Error

This register counts the number of 512 to 1023 byte frames successfully transmitted without error, i.e., no underrun and not too many retries.

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_CBSC<br>0x4BC<br>0x00000000<br>Read/Write | R  |    |    |    |     |     |

|--------|-----------------------------------------|------------------------------------------------|----|----|----|----|-----|-----|

| Bit    | 31                                      | 30                                             | 29 | 28 | 27 | 26 | 25  | 24  |

|        |                                         |                                                |    |    |    |    |     |     |

| Access |                                         |                                                |    |    |    |    |     |     |

| Reset  |                                         |                                                |    |    |    |    |     |     |

| Bit    | 23                                      | 22                                             | 21 | 20 | 19 | 18 | 17  | 16  |

| •      |                                         |                                                |    |    |    |    |     |     |

| Access |                                         |                                                |    |    |    |    |     |     |

| Reset  |                                         |                                                |    |    |    |    |     |     |

| Bit    | 15                                      | 14                                             | 13 | 12 | 11 | 10 | 9   | 8   |

|        |                                         |                                                |    |    |    |    | -   | -   |

| Access |                                         |                                                |    |    |    |    |     |     |

| Reset  |                                         |                                                |    |    |    |    |     |     |

|        |                                         |                                                |    |    |    |    |     |     |

| Bit    | 7                                       | 6                                              | 5  | 4  | 3  | 2  | 1   | 0   |

|        |                                         |                                                |    |    |    |    | QAE | QBE |

| Access |                                         |                                                |    |    |    |    |     |     |

| Reset  |                                         |                                                |    |    |    |    | 0   | 0   |

### 38.8.105 GMAC Credit-Based Shaping Control Register

#### Bit 1 – QAE Queue A CBS Enable

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Credit-based shaping on the second highest priority queue (queue A) is disabled. |

| 1     | Credit-based shaping on the second highest priority queue (queue A) is enabled.  |

#### Bit 0 – QBE Queue B CBS Enable

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | Credit-based shaping on the highest priority queue (queue B) is disabled. |

| 1     | Credit-based shaping on the highest priority queue (queue B) is enabled.  |

### High-Speed Multimedia Card Interface (HSMCI)

| Table 40-2. Bus repelogy |        |                 |                       |                                           |  |

|--------------------------|--------|-----------------|-----------------------|-------------------------------------------|--|

| Pin Number               | Name   | Type <u>(1)</u> | Description           | HSMCI Pin Name <sup>(2)</sup><br>(Slot z) |  |

| 1                        | DAT[3] | I/O/PP          | Data                  | MCDz3                                     |  |

| 2                        | CMD    | I/O/PP/OD       | Command/response      | MCCDz                                     |  |

| 3                        | VSS1   | S               | Supply voltage ground | VSS                                       |  |

| 4                        | VDD    | S               | Supply voltage        | VDD                                       |  |

| 5                        | CLK    | I/O             | Clock                 | MCCK                                      |  |

| 6                        | VSS2   | S               | Supply voltage ground | VSS                                       |  |

| 7                        | DAT[0] | I/O/PP          | Data 0                | MCDz0                                     |  |

| 8                        | DAT[1] | I/O/PP          | Data 1                | MCDz1                                     |  |

| 9                        | DAT[2] | I/O/PP          | Data 2                | MCDz2                                     |  |

#### Table 40-2. Bus Topology

Notes: 1. I: Input, O: Output, PP: Push/Pull, OD: Open Drain, S: Supply

2. When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA, MCDAy to HSMCIx\_DAy.

Figure 40-4. MMC Bus Connections (One Slot)

Note: When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA MCDAy to HSMCIx\_DAy.

#### Figure 40-5. SD Memory Card Bus Topology

| 1 2 3 4 5 6 7 8<br>9 SD CARD | · · _ |          |

|------------------------------|-------|----------|

|                              | 9     | 12345678 |

The SD Memory Card bus includes the signals listed in Table 1-6.

### Serial Peripheral Interface (SPI)

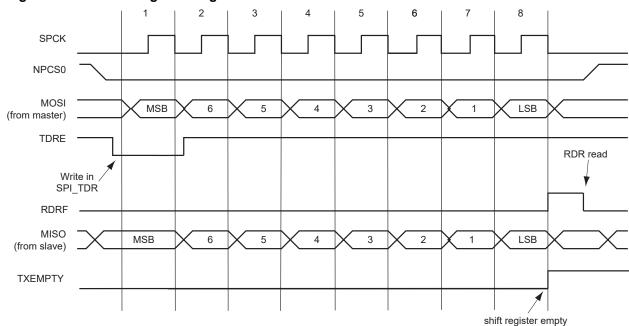

The figure below shows the behavior of Transmit Data Register Empty (TDRE), Receive Data Register (RDRF) and Transmission Register Empty (TXEMPTY) status flags within SPI\_SR during an 8-bit data transfer in Fixed mode without the DMA involved.

#### 41.7.3.3 Clock Generation

The SPI Baud rate clock is generated by dividing the peripheral clock by a value between 1 and 255.

If SPI\_CSRx.SCBR is programmed to 1, the operating baud rate is peripheral clock (refer to the section "Electrical Characteristics" for the SPCK maximum frequency). Triggering a transfer while SPI\_CSRx.SCBR is at 0 can lead to unpredictable results.

At reset, SPI\_CSRx.SCBR=0 and the user has to program it to a valid value before performing the first transfer.

The divisor can be defined independently for each chip select, as it has to be programmed in SPI\_CSRx.SCBR. This allows the SPI to automatically adapt the baud rate for each interfaced peripheral without reprogramming.

#### **Related Links**

58. Electrical Characteristics for SAM V70/V71

#### 41.7.3.4 Transfer Delays

The following figure shows a chip select transfer change and consecutive transfers on the same chip select. Three delays can be programmed to modify the transfer waveforms:

Delay between the chip selects—programmable only once for all chip selects by writing field SPI\_MR.DLYBCS. The SPI slave device deactivation delay is managed through DLYBCS. If there is only one SPI slave device connected to the master, DLYBCS does not need to be configured. If several slave devices are connected to a master, DLYBCS must be configured depending on the highest deactivation delay. Refer to details on the SPI slave device in the section "Electrical Characteristics".

### Serial Peripheral Interface (SPI)

#### 41.8.3 SPI Receive Data Register

| Name:     | SPI_RDR   |

|-----------|-----------|

| Offset:   | 0x08      |

| Reset:    | 0x0       |

| Property: | Read-only |

| Bit    | 31 | 30 | 29 | 28               | 27    | 26  | 25    | 24 |

|--------|----|----|----|------------------|-------|-----|-------|----|

|        |    |    |    |                  |       |     |       |    |

| Access |    |    |    |                  |       |     |       |    |

| Reset  |    |    |    |                  |       |     |       |    |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 23 | 22 | 21 | 20               | 19    | 18  | 17    | 16 |

|        |    |    |    |                  |       | PCS | [3:0] |    |

| Access |    |    |    |                  | R     | R   | R     | R  |

| Reset  |    |    |    |                  | 0     | 0   | 0     | 0  |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 15 | 14 | 13 | 12               | 11    | 10  | 9     | 8  |

|        |    |    |    | RD[ <sup>2</sup> | 15:8] |     |       |    |

| Access | R  | R  | R  | R                | R     | R   | R     | R  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

|        |    |    |    |                  |       |     |       |    |

| Bit    | 7  | 6  | 5  | 4                | 3     | 2   | 1     | 0  |

|        |    |    |    | RD[              | [7:0] |     |       |    |

| Access | R  | R  | R  | R                | R     | R   | R     | R  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

| Reset  | 0  | 0  | 0  | 0                | 0     | 0   | 0     | 0  |

#### Bits 19:16 – PCS[3:0] Peripheral Chip Select

In Master mode only, these bits indicate the value on the NPCS pins at the end of a transfer. Otherwise, these bits are read as zero.

When using Variable Peripheral Select mode (PS = 1 in SPI\_MR), it is mandatory to set SPI\_MR.WDRBT bit if the PCS field must be processed in SPI\_RDR.

#### Bits 15:0 - RD[15:0] Receive Data

Data received by the SPI Interface is stored in this register in a right-justified format. Unused bits are read as zero.

### **Two-wire Interface (TWIHS)**

#### Bit 17 – ACMDIS Alternative Command Mode Disable

| Value | Description                        |

|-------|------------------------------------|

| 0     | No effect.                         |

| 1     | Alternative Command mode disabled. |

#### Bit 16 – ACMEN Alternative Command Mode Enable

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No effect.                        |

| 1     | Alternative Command mode enabled. |

#### Bit 15 – CLEAR Bus CLEAR Command

|   | /alue | Description                                           |

|---|-------|-------------------------------------------------------|

| ( | )     | No effect.                                            |

| - | L     | If Master mode is enabled, sends a bus clear command. |

#### Bit 14 - PECRQ PEC Request

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | No effect.                                |

| 1     | A PEC check or transmission is requested. |

#### Bit 13 – PECDIS Packet Error Checking Disable

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | No effect.                                     |

| 1     | SMBus PEC (CRC) generation and check disabled. |

#### Bit 12 – PECEN Packet Error Checking Enable

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | No effect.                                    |