#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 300MHz                                                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 75                                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 256K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                      |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                          |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 100-TFBGA                                                                                      |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamv71n19b-cbt                     |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 37.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 590                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3     | 37.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 591                          |

| 3     | 37.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

| 3     | 37.4.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

| 3     | 37.5.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 38. ( | GMA                                                                                                                                                                   | AC - Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 640                          |

| 3     | 38.1.                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 640                          |

| 3     | 38.2.                                                                                                                                                                 | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 640                          |

| 3     | 38.3.                                                                                                                                                                 | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 641                          |

| 3     | 38.4.                                                                                                                                                                 | Signal Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 641                          |

| 3     | 38.5.                                                                                                                                                                 | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 642                          |

| 3     | 38.6.                                                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 642                          |

| 3     | 38.7.                                                                                                                                                                 | Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 673                          |

| 3     | 38.8.                                                                                                                                                                 | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 678                          |

| 30 I  | ISB                                                                                                                                                                   | High-Speed Interface (USBHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 831                          |

|       |                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |

|       |                                                                                                                                                                       | Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |

|       |                                                                                                                                                                       | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|       |                                                                                                                                                                       | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|       |                                                                                                                                                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

|       |                                                                                                                                                                       | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

|       |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 40. ł | High                                                                                                                                                                  | -Speed Multimedia Card Interface (HSMCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                         |

| 40. H | <b>-ligh</b><br>10.1.                                                                                                                                                 | n-Speed Multimedia Card Interface (HSMCI)<br>Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1042                         |

| 40. H | High<br>10.1.<br>10.2.                                                                                                                                                | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>1042<br>1042         |

| 40. H | <b>-ligh</b><br>10.1.<br>10.2.<br>10.3.                                                                                                                               | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>1042<br>1042<br>1043 |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.                                                                                                                              | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1042<br>                     |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.                                                                                                                     | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.                                                                                                            | Description<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1042<br>                     |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.                                                                                                   | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1042<br>                     |

| 40. H | High<br>10.1.<br>10.2.<br>10.3.<br>10.4.<br>10.5.<br>10.6.<br>10.7.<br>10.8.                                                                                          | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations                                                                                                                                                                                                                                                                                                                                                                                       | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.7.<br>40.8.                                                                                          | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation                                                                                                                                                                                                                                                                                                                                                                                                          | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.                                                                        | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation                                                                                                                                                                                                                                                                                                                                                                                      | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.5.<br>40.5.<br>40.5.<br>40.7.<br>40.10<br>40.11                                                               | n-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>CE-ATA Operation<br>HSMCI Boot Operation Mode                                                                                                                                                                                                                                                                                                            | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11.                                                              | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13                                                     | Description<br>Embedded Characteristics.<br>Block Diagram.<br>Application Block Diagram.<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation.<br>O. CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>Register Write Protection.                                                                                                                                                                                                                                                                                                               | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14                                             | Description<br>Embedded Characteristics<br>Block Diagram<br>Application Block Diagram<br>Pin Name List<br>Product Dependencies<br>Bus Topology<br>High-Speed Multimedia Card Operations<br>SD/SDIO Card Operation<br>C CE-ATA Operation<br>HSMCI Boot Operation Mode<br>HSMCI Transfer Done Timings.                                                                                                                                                                                                                                                                                                                       | 1042<br>                     |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br>5eria                           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>CE-ATA Operation Mode</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection</li> <li>Register Summary</li> </ul>                                                                                      |                              |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.13<br>40.14<br><b>Seria</b><br>41.1.                    | <ul> <li>Speed Multimedia Card Interface (HSMCI).</li> <li>Description.</li> <li>Embedded Characteristics.</li> <li>Block Diagram.</li> <li>Application Block Diagram.</li> <li>Pin Name List.</li> <li>Product Dependencies.</li> <li>Bus Topology.</li> <li>High-Speed Multimedia Card Operations.</li> <li>SD/SDIO Card Operation.</li> <li>CE-ATA Operation.</li> <li>HSMCI Boot Operation Mode.</li> <li>HSMCI Transfer Done Timings.</li> <li>Register Write Protection.</li> <li>Register Summary.</li> <li>al Peripheral Interface (SPI).</li> </ul>                                                               |                              |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.9.<br>40.10<br>40.11<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.           | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> </ul>                                                          |                              |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.4.<br>40.5.<br>40.6.<br>40.7.<br>40.8.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br><b>Seria</b><br>41.1.<br>41.2.<br>41.3. | A-Speed Multimedia Card Interface (HSMCI)<br>Description<br>Embedded Characteristics.<br>Block Diagram<br>Application Block Diagram<br>Pin Name List.<br>Product Dependencies.<br>Bus Topology.<br>High-Speed Multimedia Card Operations.<br>SD/SDIO Card Operation<br>O. CE-ATA Operation.<br>CE-ATA Operation.<br>HSMCI Boot Operation Mode<br>HSMCI Boot Operation Mode<br>Register Write Protection<br>Register Summary.<br>al Peripheral Interface (SPI)<br>Description<br>Embedded Characteristics.                                                                                                                  |                              |

| 40. H | High<br>40.1.<br>40.2.<br>40.3.<br>40.5.<br>40.6.<br>40.7.<br>40.9.<br>40.10<br>40.11.<br>40.12<br>40.13<br>40.14<br>41.1.<br>41.2.<br>41.3.<br>41.3.                 | <ul> <li>Speed Multimedia Card Interface (HSMCI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> <li>Application Block Diagram</li> <li>Pin Name List</li> <li>Product Dependencies</li> <li>Bus Topology</li> <li>High-Speed Multimedia Card Operations</li> <li>SD/SDIO Card Operation</li> <li>CE-ATA Operation</li> <li>HSMCI Boot Operation Mode</li> <li>HSMCI Transfer Done Timings</li> <li>Register Write Protection</li> <li>Register Summary</li> <li>al Peripheral Interface (SPI)</li> <li>Description</li> <li>Embedded Characteristics</li> <li>Block Diagram</li> </ul> |                              |

## **Package and Pinout**

| LQFP<br>Pin                  | VFBGA<br>Ball     | TFBGA<br>Ball     | Power Rail | I/O Type | Primary   |     | Alternate |     | PIO Peripheral A | PIO Peripheral B |        | PIO Peripheral C |        |     | PIO Peripheral D |     | Reset<br>State                        |

|------------------------------|-------------------|-------------------|------------|----------|-----------|-----|-----------|-----|------------------|------------------|--------|------------------|--------|-----|------------------|-----|---------------------------------------|

|                              |                   |                   |            |          | Signal    | Dir | Signal    | Dir | Signal           | Dir              | Signal | Dir              | Signal | Dir | Signal           | Dir | Signal,<br>Dir, PU,<br>PD, HiZ,<br>ST |

| 73                           | A10               | A10               | VDDIO      | TEST     | JTAGSEL   | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | I, PD                                 |

| 18,<br>22,<br>39,<br>76      | C6, D6,<br>G6     | C6, D6,<br>G6     | VDDCORE    | Power    | VDDCORE   | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 86                           | D7                | D7                | VDDPLL     | Power    | VDDPLL    | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 93                           | E5                | E5                | VDDUTMII   | Power    | VDDUTMII  | I.  | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 94                           | A4                | A4                | VDDUTMII   | USBHS    | HSDM      | I/O | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 95                           | B4                | В4                | VDDUTMII   | USBHS    | HSDP      | I/O | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 3, 7,<br>8, 10,<br>29,<br>67 | E7, F4,<br>F5, F6 | E7, F4,<br>F5, F6 | GND        | Ground   | GND       | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

|                              | D4                | D4                | GNDANA     | Ground   | GNDANA    | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

|                              | A6                | A8                | GNDUTMI    | Ground   | GNDUTMI   | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

|                              | C4                | C4                | GNDPLLUSB  | Ground   | GNDPLLUSB | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

|                              | E6                | E4                | GNDPLL     | Ground   | GNDPLL    | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 96                           | В3                | В3                | VDDUTMIC   | Power    | VDDUTMIC  | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 97                           | A3                | A3                | -          | VBG      | VBG       | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

| 90                           | E4                | E6                | VDDPLLUSB  | Power    | VDDPLLUSB | I   | -         | -   | -                | -                | -      | -                | -      | -   | -                | -   | -                                     |

## Note:

- 1. WKUPx can be used if the PIO Controller defines the I/O line as "input".

- 2. To select this extra function, refer to the 32.5.14 Parallel Capture Modesection in the Parallel Input/ Output Controller (PIO) chapter.

- 3. PIODCEN1/PIODCx has priority over WKUPx. Refer to the 32.5.14 Parallel Capture Mode section in the PIO chapter.

- 4. Refer to the 23.4.2 Slow Clock Generator section in the Supply Controller (SUPC) chapter.

- To select this extra function, refer to the 33.5.2.1 I/O Lines section in the External Bus Interface (EBI) chapter. This selection is independent of the PIO line configuration. PIO lines must be configured according to required settings (PU or PD).

- Analog input has priority over WKUPx pin. To select the analog input, refer to the 33.5.2.1 I/O Lines section in the EBI chapter. WKUPx can be used if the PIO controller defines the I/O line as "input".

- Analog input has priority over RTCOUTx pin. To select the analog input, refer to the 33.5.2.1 I/O Lines section in the EBI chapter. Refer to the 27.5.8 Waveform Generation section in the Real-Time Clock (RTC) chapter to select RTCOUTx.

- 8. Analog input has priority over WKUPx pin. To select the analog input, refer to the 33.5.2.1 I/O Lines section in the EBI chapter. To select PIODCEN2, refer to the 32.5.14 Parallel Capture Mode in the PIO chapter.

- 9. Refer to the System I/O Configuration Register (19.4.7 CCFG\_SYSIO) in the Bus Matrix (MATRIX) chapter.

- Refer to the 30.5.3 Main Crystal Oscillator section in the Clock Generator chapter. This selection is independent of the PIO line configuration. PIO lines must be configured according to XINxx (I) and XOUTxx (O).

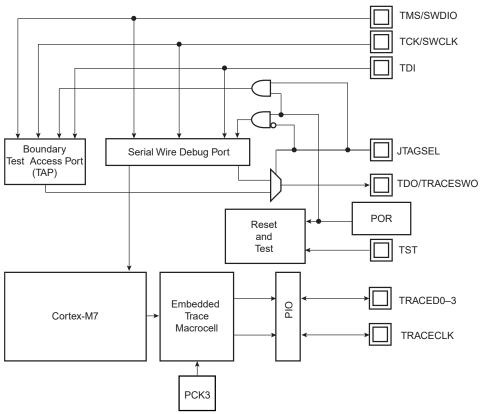

## 16.4 Debug and Test Block Diagram Figure 16-1. Debug and Test Block Diagram

## 16.5 Debug and Test Pin Description Table 16-1. Debug and Test Signal List

| Signal Name                               | Function                                  | Туре         | Active Level |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------|--------------|--------------|--|--|--|--|--|

| Reset/Test                                |                                           |              |              |  |  |  |  |  |

| NRST                                      | Microcontroller Reset                     | Input/Output | Low          |  |  |  |  |  |

| TST                                       | Test Select                               | Input        | -            |  |  |  |  |  |

| Serial Wire Debug Port/JTAG Boundary Scan |                                           |              |              |  |  |  |  |  |

| TCK/SWCLK                                 | Test Clock/Serial Wire Clock              | Input        | -            |  |  |  |  |  |

| TDI                                       | Test Data In                              | Input        | -            |  |  |  |  |  |

| TDO/TRACESWO                              | Test Data Out/Trace Asynchronous Data Out | Output       | -            |  |  |  |  |  |

| TMS/SWDIO                                 | Input                                     | -            |              |  |  |  |  |  |

| JTAGSEL                                   | Input                                     | High         |              |  |  |  |  |  |

| Trace Debug Port                          | Trace Debug Port                          |              |              |  |  |  |  |  |

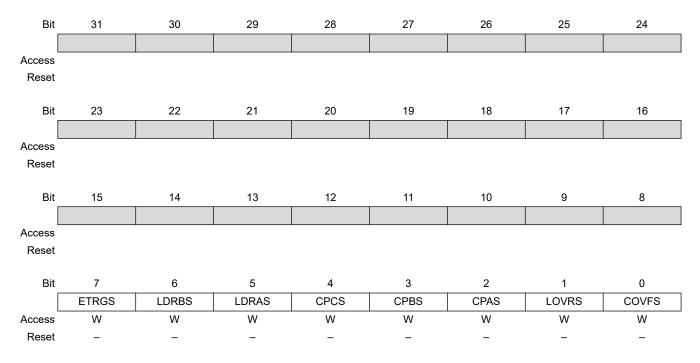

## 27.6.11 RTC Interrupt Mask Register

| Name:<br>Offset:<br>Reset:<br>Property: |    | RTC_IMR<br>0x28<br>0x00000000<br>Read-only |            |     |     |     |     |     |

|-----------------------------------------|----|--------------------------------------------|------------|-----|-----|-----|-----|-----|

| Bit                                     | 31 | 30                                         | 29         | 28  | 27  | 26  | 25  | 24  |

|                                         |    |                                            |            |     |     |     |     |     |

| Access                                  |    | •                                          |            |     |     |     |     |     |

| Reset                                   |    |                                            |            |     |     |     |     |     |

| 5.4                                     |    |                                            | <b>0</b> ( |     |     |     |     | 10  |

| Bit                                     | 23 | 22                                         | 21         | 20  | 19  | 18  | 17  | 16  |

|                                         |    |                                            |            |     |     |     |     |     |

| Access                                  |    |                                            |            |     |     |     |     |     |

| Reset                                   |    |                                            |            |     |     |     |     |     |

| Bit                                     | 15 | 14                                         | 13         | 12  | 11  | 10  | 9   | 8   |

| BR                                      |    |                                            | 10         | 12  |     | 10  |     |     |

| Access                                  |    |                                            |            |     |     |     |     |     |

| Reset                                   |    |                                            |            |     |     |     |     |     |

|                                         |    |                                            |            |     |     |     |     |     |

| Bit                                     | 7  | 6                                          | 5          | 4   | 3   | 2   | 1   | 0   |

|                                         |    |                                            | TDERR      | CAL | TIM | SEC | ALR | ACK |

| Access                                  |    |                                            | R          | R   | R   | R   | R   | R   |

| Reset                                   |    |                                            | 0          | 0   | 0   | 0   | 0   | 0   |

#### Bit 5 – TDERR Time and/or Date Error Mask

| N | /alue | Description                                   |

|---|-------|-----------------------------------------------|

| С |       | The time and/or date error event is disabled. |

| 1 |       | The time and/or date error event is enabled.  |

### Bit 4 – CAL Calendar Event Interrupt Mask

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The selected calendar event interrupt is disabled. |

| 1     | The selected calendar event interrupt is enabled.  |

## Bit 3 – TIM Time Event Interrupt Mask

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The selected time event interrupt is disabled. |

| 1     | The selected time event interrupt is enabled.  |

#### Bit 2 – SEC Second Event Interrupt Mask

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The second periodic interrupt is disabled. |

| 1     | The second periodic interrupt is enabled.  |

## Bit 1 – ALR Alarm Interrupt Mask

| I | Value | Description                      |

|---|-------|----------------------------------|

|   | 0     | The alarm interrupt is disabled. |

|   | 1     | The alarm interrupt is enabled.  |

## Bit 0 – ACK Acknowledge Update Interrupt Mask

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | The acknowledge for update interrupt is disabled. |

| 1     | The acknowledge for update interrupt is enabled.  |

## **Power Management Controller (PMC)**

## 31.20.31 PMC SleepWalking Disable Register 1

Name:PMC\_SLPWK\_DR1Offset:0x0138Property:Write-only

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

| Bit    | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |       | PID62 |       | PID60 | PID59 | PID58 | PID57 | PID56 |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

|        |       |       | PID53 | PID52 | PID51 | PID50 | PID49 | PID48 |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

|        | PID47 | PID46 | PID45 | PID44 | PID43 | PID42 | PID41 | PID40 |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|        | PID39 |       | PID37 |       | PID35 | PID34 | PID33 | PID32 |

| Access |       |       |       |       |       |       |       |       |

| Reset  |       |       |       |       |       |       |       |       |

#### Bits 0:3,5,7:28,30 - PID Peripheral Clock x Disable

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | No effect.                                   |

| 1     | Disables the corresponding peripheral clock. |

## Parallel Input/Output Controller (PIO)

### 32.6.1.21 PIO Pull-Up Disable Register

| Name:     | PIO_PUDR   |

|-----------|------------|

| Offset:   | 0x0060     |

| Property: | Write-only |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Access |     |     |     |     |     |     |     |     |

| Reset  |     |     |     |     |     |     |     |     |

# Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31 – P PIO Pull-Up Disable

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | No effect.                                    |

| 1     | Disables the pullup resistor on the I/O line. |

## SDRAM Controller (SDRAMC)

| Table 34-3. | SDRAM Confi | guration Mappin | a: 4K Rows. | 256/512/1024/2048 Columns |

|-------------|-------------|-----------------|-------------|---------------------------|

|             |             | galadon mappin  | g,          |                           |

| СР | U A                            | ddre | ss L | ine  |                           |                       |     |      |     |    |    |    |    |    |    |    |    |   |    |      |    |      |    |   |   |   |    |

|----|--------------------------------|------|------|------|---------------------------|-----------------------|-----|------|-----|----|----|----|----|----|----|----|----|---|----|------|----|------|----|---|---|---|----|

| 27 | 26                             | 25   | 24   | 23   | 22                        | 21                    | 20  | 19   | 18  | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7    | 6  | 5    | 4  | 3 | 2 | 1 | 0  |

|    |                                |      |      |      | Bk[′                      | 1:0]                  | Rov | w[11 | :0] |    |    |    |    |    |    |    |    |   | Сс | olur | nn | [7:0 | )] |   |   |   | M0 |

|    |                                |      |      | Bk[′ | 1:0]                      | Row[11:0] Column[8:0] |     |      |     |    |    |    |    |    | M0 |    |    |   |    |      |    |      |    |   |   |   |    |

|    |                                |      | Bk[′ | 1:0] | :0] Row[11:0] Column[9:0] |                       |     |      |     |    |    |    |    | M0 |    |    |    |   |    |      |    |      |    |   |   |   |    |

|    | Bk[1:0] Row[11:0] Column[10:0] |      |      |      |                           |                       |     |      |     |    |    |    | M0 |    |    |    |    |   |    |      |    |      |    |   |   |   |    |

**Note:** M0 is the byte address inside a 16-bit half-word and Bk[1] = BA1, Bk[0] = BA0.

| Table 34-4.         SDRAM Configuration Mapping: 8K Rows, 256/512/1024/2048 Columns |

|-------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------|

| СР | CPU Address Line                 |     |      |     |      |     |      |     |    |    |    |    |    |    |    |    |     |    |      |      |    |      |    |   |   |   |    |

|----|----------------------------------|-----|------|-----|------|-----|------|-----|----|----|----|----|----|----|----|----|-----|----|------|------|----|------|----|---|---|---|----|

| 27 | 26                               | 25  | 24   | 23  | 22   | 21  | 20   | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10  | 9  | 8    | 7    | 6  | 5    | 4  | 3 | 2 | 1 | 0  |

|    |                                  |     |      | Bk[ | 1:0] | Ro  | w[12 | :0] |    |    |    |    |    |    |    |    |     |    | Сс   | olui | mn | [7:( | D] |   |   |   | M0 |

|    | Bk[1:0] Row[12:0] Column[8:0]    |     |      |     |      |     |      |     |    |    | M0 |    |    |    |    |    |     |    |      |      |    |      |    |   |   |   |    |

|    |                                  | Bk[ | 1:0] | Rov | v[12 | :0] |      |     |    |    |    |    |    |    |    |    | Col | um | nn[9 | 9:0] |    |      |    |   |   |   | M0 |

|    | Bk[1:0] Row[12:0] Column[10:0] N |     |      |     |      |     |      |     |    |    |    | M0 |    |    |    |    |     |    |      |      |    |      |    |   |   |   |    |

**Note:** M0 is the byte address inside a 16-bit half-word and Bk[1] = BA1, Bk[0] = BA0.

## 34.5 **Product Dependencies**

## 34.5.1 SDRAM Device Initialization

The initialization sequence is generated by software. The sequence to initialize SDRAM devices is the following:

- 1. Set the SDRAM features in the SDRAMC\_CR: asynchronous timings (TRC, TRAS, etc.), number of columns, number of rows, CAS latency and data bus width. Set UNAL bit in SDRAMC\_CFR1.

- 2. For mobile SDRAM, configure temperature-compensated self-refresh (TCSR), drive strength (DS) and partial array self-refresh (PASR) in the Low Power register (SDRAMC\_LPR).

- 3. Select the SDRAM memory device type in the Memory Device register (SDRAMC\_MDR).

- 4. A pause of at least 200 µs must be observed before a signal toggle.

- 5. A NOP command is issued to the SDRAM devices. The application must write a 1 to the MODE field in the Mode register (SDRAMC\_MR) (see **Note**). Read the SDRAMC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any SDRAM address.

- 6. An All Banks Precharge command is issued to the SDRAM. The application must write a 2 to the MODE field in the SDRAMC\_MR. Read the SDRAMC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any SDRAM address.

- 7. Eight autorefresh (CBR) cycles are provided. The application must set the MODE field to 4 in the SDRAMC\_MR. Read the SDRAMC\_MR and add a memory barrier assembler instruction just after the read. Perform a write access to any SDRAM location eight times.

# DMA Controller (XDMAC)

|        |                 |          | 1    | 1     | 1              |          | 1     |        |       |

|--------|-----------------|----------|------|-------|----------------|----------|-------|--------|-------|

| Offset | Name            | Bit Pos. |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      |      |       | DUB            | S[7:0]   |       |        |       |

| 0x0604 | XDMAC_CDUS22    | 15:8     |      |       | DUBS           | 6[15:8]  |       |        |       |

| 0,0004 | ADIVIAC_CD0322  | 23:16    |      |       | DUBS           | [23:16]  |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

| 0x0608 |                 |          |      |       |                |          |       |        |       |

|        | Reserved        |          |      |       |                |          |       |        |       |

| 0x060F |                 |          |      |       |                |          |       |        |       |

|        |                 | 7:0      | ROIE | WBIE  | RBIE           | FIE      | DIE   | LIE    | BIE   |

| 0x0610 | XDMAC_CIE23     | 15:8     |      |       |                |          |       |        |       |

| 0,0010 | ADWAG_CIE23     | 23:16    |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      | ROID | WBEID | RBEID          | FID      | DID   | LID    | BID   |

| 0x0614 | XDMAC_CID23     | 15:8     |      |       |                |          |       |        |       |

| 070014 |                 | 23:16    |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      | ROIM | WBEIM | RBEIM          | FIM      | DIM   | LIM    | BIM   |

| 0x0618 | XDMAC_CIM23     | 15:8     |      |       |                |          |       |        |       |

| 0X0010 | ADIVIAC_CIIVI23 | 23:16    |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      | ROIS | WBEIS | RBEIS          | FIS      | DIS   | LIS    | BIS   |

| 0x061C | XDMAC_CIS23     | 15:8     |      |       |                |          |       |        |       |

| 0x001C | ADIVIAC_CI323   | 23:16    |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      |      |       | SA             | [7:0]    |       |        |       |

| 0x0620 | XDMAC_CSA23     | 15:8     |      |       | SA[            | 15:8]    |       |        |       |

| 0X0020 | ADIVIAC_COA23   | 23:16    |      |       | SA[2           | 3:16]    |       |        |       |

|        |                 | 31:24    |      |       | SA[3           | 1:24]    |       |        |       |

|        |                 | 7:0      |      |       | DA             | [7:0]    |       |        |       |

| 0x0624 | XDMAC_CDA23     | 15:8     |      |       | DA[            | 15:8]    |       |        |       |

| 070024 |                 | 23:16    |      |       | DA[2           | 3:16]    |       |        |       |

|        |                 | 31:24    |      |       | DA[3           | 1:24]    |       |        |       |

|        |                 | 7:0      |      | NDA   | <b>\</b> [5:0] |          |       |        | NDAIF |

| 0x0628 | XDMAC_CNDA23    | 15:8     |      |       | NDA            | [13:6]   |       |        |       |

| 070020 |                 | 23:16    |      |       | NDA[           | 21:14]   |       |        |       |

|        |                 | 31:24    |      |       | NDA[           | 29:22]   |       |        |       |

|        |                 | 7:0      |      |       | NDVIE          | EW[1:0]  | NDDUP | NDSUP  | NDE   |

| 0x062C | XDMAC_CNDC23    | 15:8     |      |       |                |          |       |        |       |

| 070020 |                 | 23:16    |      |       |                |          |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

|        |                 | 7:0      |      |       | UBLE           | N[7:0]   |       |        |       |

| 0x0630 | XDMAC_CUBC23    | 15:8     |      |       | UBLEI          | N[15:8]  |       |        |       |

| 070030 |                 | 23:16    |      |       | UBLEN          | I[23:16] |       |        |       |

|        |                 | 31:24    |      |       |                |          |       |        |       |

| 0x0634 | XDMAC_CBC23     | 7:0      |      |       | BLE            | N[7:0]   |       |        |       |

| 070034 |                 | 15:8     |      |       |                |          | BLEN  | [11:8] |       |

## **DMA Controller (XDMAC)**

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | End of flush condition has not occurred.                                        |

| 1     | End of flush condition has occurred since the last read of the Status register. |

## Bit 2 – DIS End of Disable Interrupt Status Bit

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | End of disable condition has not occurred.                                        |

| 1     | End of disable condition has occurred since the last read of the Status register. |

## **Bit 1 – LIS** End of Linked List Interrupt Status Bit

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | End of linked list condition has not occurred.                                        |

| 1     | End of linked list condition has occurred since the last read of the Status register. |

## Bit 0 – BIS End of Block Interrupt Status Bit

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | End of block interrupt has not occurred.                                        |

| 1     | End of block interrupt has occurred since the last read of the Status register. |

This bit is cleared by writing a '1' to it.

## **GMAC - Ethernet MAC**

| Bit    | 31        | 30         | 29      | 28        | 27    | 26        | 25  | 24     |

|--------|-----------|------------|---------|-----------|-------|-----------|-----|--------|

|        | WZO       | CLTTO      | OP[1:0] |           |       | PHYA[4:1] |     |        |

| Access | R/W       | R/W        | R/W     | R/W       | R/W   | R/W       | R/W | R/W    |

| Reset  | 0         | 0          | 0       | 0         | 0     | 0         | 0   | 0      |

|        |           |            |         |           |       |           |     |        |

| Bit    | 23        | 22         | 21      | 20        | 19    | 18        | 17  | 16     |

|        | PHYA[0:0] |            |         | REGA[4:0] |       |           | WTN | I[1:0] |

| Access | R/W       | R/W        | R/W     | R/W       | R/W   | R/W       | R/W | R/W    |

| Reset  | 0         | 0          | 0       | 0         | 0     | 0         | 0   | 0      |

|        |           |            |         |           |       |           |     |        |

| Bit    | 15        | 14         | 13      | 12        | 11    | 10        | 9   | 8      |

|        |           | DATA[15:8] |         |           |       |           |     |        |

| Access | R/W       | R/W        | R/W     | R/W       | R/W   | R/W       | R/W | R/W    |

| Reset  | 0         | 0          | 0       | 0         | 0     | 0         | 0   | 0      |

|        |           |            |         |           |       |           |     |        |

| Bit    | 7         | 6          | 5       | 4         | 3     | 2         | 1   | 0      |

|        |           |            |         | DATA      | [7:0] |           |     |        |

| Access | R/W       | R/W        | R/W     | R/W       | R/W   | R/W       | R/W | R/W    |

| Reset  | 0         | 0          | 0       | 0         | 0     | 0         | 0   | 0      |

|        |           |            |         |           |       |           |     |        |

#### Bit 31 – WZO Write ZERO

Must be written to '0'.

| Value | Description |

|-------|-------------|

| 0     | Mandatory   |

| 1     | Reserved    |

## Bit 30 – CLTTO Clause 22 Operation

| Value | Description         |

|-------|---------------------|

| 0     | Clause 45 operation |

| 1     | Clause 22 operation |

## Bits 29:28 - OP[1:0] Operation

| Value | Description |

|-------|-------------|

| 01    | Write       |

| 10    | Read        |

| Other | Reseved     |

## Bits 27:23 - PHYA[4:0] PHY Address

**Bits 22:18 – REGA[4:0]** Register Address Specifies the register in the PHY to access.

Bits 17:16 – WTN[1:0] Write Ten Must be written to '10'.

| Value | Description |

|-------|-------------|

| 10    | Mandatory   |

| Other | Reserved    |

© 2018 Microchip Technology Inc.

|        | Name:<br>Offset:<br>Reset:<br>Property: | GMAC_TI<br>0x1DC<br>0x00000000<br>- |     |     |        |     |     |     |

|--------|-----------------------------------------|-------------------------------------|-----|-----|--------|-----|-----|-----|

| Bit    | 31                                      | 30                                  | 29  | 28  | 27     | 26  | 25  | 24  |

|        |                                         |                                     |     |     |        |     |     |     |

| Access |                                         |                                     |     |     |        |     |     |     |

| Reset  |                                         |                                     |     |     |        |     |     |     |

| 5.4    |                                         | 22                                  | 0.4 | 00  | 10     | 10  | 47  | 10  |

| Bit    | 23                                      | 22                                  | 21  | 20  | 19     | 18  | 17  | 16  |

|        |                                         |                                     |     |     | [7:0]  |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

| Bit    | 15                                      | 14                                  | 13  | 12  | 11     | 10  | 9   | 8   |

|        |                                         |                                     |     | ACN | S[7:0] |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

| Bit    | 7                                       | 6                                   | 5   | 4   | 3      | 2   | 1   | 0   |

|        |                                         |                                     |     | CNS | 6[7:0] |     |     |     |

| Access | R/W                                     | R/W                                 | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                   | 0   | 0   | 0      | 0   | 0   | 0   |

|        |                                         |                                     |     |     |        |     |     |     |

## 38.8.88 GMAC IEEE 1588 Timer Increment Register

## Bits 23:16 - NIT[7:0] Number of Increments

The number of increments after which the alternative increment is used.

### Bits 15:8 – ACNS[7:0] Alternative Count Nanoseconds

Alternative count of nanoseconds by which the 1588 Timer Nanoseconds Register will be incremented each clock cycle.

## Bits 7:0 - CNS[7:0] Count Nanoseconds

A count of nanoseconds by which the IEEE 1588 Timer Nanoseconds Register will be incremented each clock cycle.

## 39.5.3.4 USB Reset

The USBHS sends a USB bus reset when the user writes a one to the Send USB Reset bit in the Host General Control register (USBHS\_HSTCTRL.RESET). The USB Reset Sent Interrupt bit in the Host Global Interrupt Status register (USBHS\_HSTISR.RSTI) is set when the USB reset has been sent. In this case, all pipes are disabled and de-allocated.

If the bus was previously in a "Suspend" state (the Start of Frame Generation Enable (USBHS\_HSTCTRL.SOFE) bit is zero), the USBHS automatically switches to the "Resume" state, the Host Wakeup Interrupt (USBHS\_HSTISR.HWUPI) bit is set and the USBHS\_HSTCTRL.SOFE bit is set in order to generate SOFs or micro SOFs immediately after the USB reset.

At the end of the reset, the user should check the USBHS\_SR.SPEED field to know the speed running according to the peripheral capability (LS.FS/HS).

## 39.5.3.5 Pipe Reset

A pipe can be reset at any time by writing a one to the Pipe x Reset (USBHS\_HSTPIP.PRSTx) bit. This is recommended before using a pipe upon hardware reset or when a USB bus reset has been sent. This resets:

- the internal state machine of the pipe,

- the receive and transmit bank FIFO counters,

- all the registers of the pipe (USBHS\_HSTPIPCFGx, USBHS\_HSTPIPISRx, USBHS\_HSTPIPIMRx), except its configuration (USBHS\_HSTPIPCFGx.ALLOC, USBHS\_HSTPIPCFGx.PBK, USBHS\_HSTPIPCFGx.PSIZE, USBHS\_HSTPIPCFGx.PTOKEN, USBHS\_HSTPIPCFGx.PTYPE, USBHS\_HSTPIPCFGx.PEPNUM, USBHS\_HSTPIPCFGx.INTFRQ) and its Data Toggle Sequence field (USBHS\_HSTPIPISRx.DTSEQ).

The pipe configuration remains active and the pipe is still enabled.

The pipe reset may be associated with a clear of the data toggle sequence. This can be achieved by setting the Reset Data Toggle bit in the Pipe x Control register (USBHS\_HSTPIPIMRx.RSTDT) (by writing a one to the Reset Data Toggle Set bit in the Pipe x Control Set register (USBHS\_HSTPIPIERx.RSTDTS)).

In the end, the user has to write a zero to the USBHS\_HSTPIP.PRSTx bit to complete the reset operation and to start using the FIFO.

#### 39.5.3.6 Pipe Activation

The pipe is maintained inactive and reset (see "Pipe Reset" for more details) as long as it is disabled (USBHS\_HSTPIP.PENx = 0). The Data Toggle Sequence field (USBHS\_HSTPIPISRx.DTSEQ) is also reset.

The algorithm represented in the following figure must be followed to activate a pipe.

## USB High-Speed Interface (USBHS)

## 39.6.23 Device Endpoint Interrupt Disable Register (Control, Bulk, Interrupt Endpoints)

Name:

USBHS\_DEVEPTIDRx

Offset:

0x0220 + x\*0x04 [x=0..9]

Reset:

0

Property:

Read/Write

This register view is relevant only if EPTYPE = 0x0, 0x2, or 0x3 in "Device Endpoint x Configuration Register".