Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 34                                                                        |

| Number of Gates                | 30000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package        | 48-QFN (6x6)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-z1qng48 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Core Architecture**

#### VersaTile

The proprietary IGLOO and ProASIC3 device architectures provide granularity comparable to gate arrays. The device core consists of a sea-of-VersaTiles architecture.

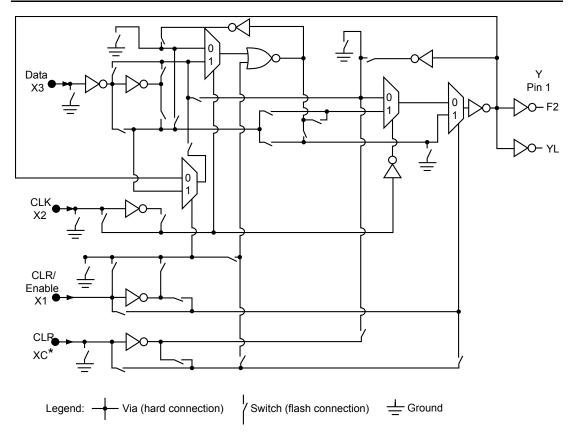

As illustrated in Figure 1-8, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- · Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4<sup>th</sup> input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions can be connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, SET/CLR is supported by a fourth input. The SET/CLR signal can only be routed to this fourth input over the VersaNet (global) network. However, if, in the user's design, the SET/CLR signal is not routed over the VersaNet network, a compile warning message will be given, and the intended logic function will be implemented by two VersaTiles instead of one.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources.

\* This input can only be connected to the global clock distribution network.

Figure 1-8 • Low Power Flash Device Core VersaTile

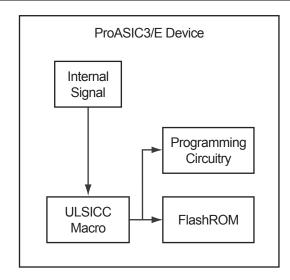

Table 2-2 • Using ULSICC Macro\*

| VHDL                        |         | Verilog      |                                  |

|-----------------------------|---------|--------------|----------------------------------|

| COMPONENT ULSICC            |         |              | module ULSICC(LSICC);            |

| port (                      |         |              | input LSICC;                     |

|                             | : in    | STD_ULOGIC); | endmodule                        |

| END COMPONENT;              |         |              |                                  |

|                             |         |              | Example:                         |

| Example:                    |         |              | ULSICC U1(.LSICC(myInputSignal)) |

| COMPONENT ULSICC            |         |              | /* synthesis syn_noprune=1 */;   |

| port (                      |         |              |                                  |

| LSICC                       | : in    | STD_ULOGIC); |                                  |

| END COMPONENT;              |         |              |                                  |

|                             |         |              |                                  |

| attribute syn_noprune : boo | lean;   |              |                                  |

| attribute syn_noprune of u  | : labe  |              |                                  |

| ul: ULSICC port map(myInput | Signal) | ;            |                                  |

Note: \*Supported in Libero® software v7.2 and newer versions.

Figure 2-2 • User Low Static (Idle) Mode Application—Internal Control Signal

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Dividers *n* and *m* (the input divider and feedback divider, respectively) provide integer frequency division factors from 1 to 128. The output dividers *u*, *v*, and *w* provide integer division factors from 1 to 32. Frequency scaling of the reference clock CLKA is performed according to the following formulas:

$$f_{GLA} = f_{CLKA} \times m / (n \times u) - GLA$$

Primary PLL Output Clock

EQ 4-1

$f_{GLB} = f_{YB} = f_{CLKA} \times m / (n \times v) - GLB$  Secondary 1 PLL Output Clock(s)

EQ 4-2

$f_{GLC} = f_{YC} = f_{CLKA} \times m / (n \times w) - GLC$  Secondary 2 PLL Output Clock(s)

EQ 4-3

SmartGen provides a user-friendly method of generating the configured PLL netlist, which includes automatically setting the division factors to achieve the closest possible match to the requested frequencies. Since the five output clocks share the *n* and *m* dividers, the achievable output frequencies are interdependent and related according to the following formula:

$$f_{GLA} = f_{GLB} \times (v / u) = f_{GLC} \times (w / u)$$

EQ 4-4

## **Clock Delay Adjustment**

There are a total of seven configurable delay elements implemented in the PLL architecture.

Two of the delays are located in the feedback path, entitled System Delay and Feedback Delay. System Delay provides a fixed delay of 2 ns (typical), and Feedback Delay provides selectable delay values from 0.6 ns to 5.56 ns in 160 ps increments (typical). For PLLs, delays in the feedback path will effectively advance the output signal from the PLL core with respect to the reference clock. Thus, the System and Feedback delays generate negative delay on the output clock. Additionally, each of these delays can be independently bypassed if necessary.

The remaining five delays perform traditional time delay and are located at each of the outputs of the PLL. Besides the fixed global driver delay of 0.755 ns for each of the global networks, the global multiplexer outputs (GLA, GLB, and GLC) each feature an additional selectable delay value, as given in Table 4-7.

Table 4-7 • Delay Values in Libero SoC Software per Device Family

| Device                | Typical | Starting Values | Increments | Ending Value |

|-----------------------|---------|-----------------|------------|--------------|

| ProASIC3              | 200 ps  | 0 to 735 ps     | 200 ps     | 6.735 ns     |

| IGLOO/ProASIC3L 1.5 V | 360 ps  | 0 to 1.610 ns   | 360 ps     | 12.410 ns    |

| IGLOO/ProASIC3L 1.2 V | 580 ps  | 0 to 2.880 ns   | 580 ps     | 20.280 ns    |

The additional YB and YC signals have access to a selectable delay from 0.6 ns to 5.56 ns in 160 ps increments (typical). This is the same delay value as the CLKDLY macro. It is similar to CLKDLY, which bypasses the PLL core just to take advantage of the phase adjustment option with the delay value.

The following parameters must be taken into consideration to achieve minimum delay at the outputs (GLA, GLB, GLC, YB, and YC) relative to the reference clock: routing delays from the PLL core to CCC outputs, core outputs and global network output delays, and the feedback path delay. The feedback path delay acts as a time advance of the input clock and will offset any delays introduced beyond the PLL core output. The routing delays are determined from back-annotated simulation and are configuration-dependent.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

global assignments are not allocated properly. See the "Physical Constraints for Quadrant Clocks" section for information on assigning global signals to the quadrant clock networks.

Promoted global signals will be instantiated with CLKINT macros to drive these signals onto the global network. This is automatically done by Designer when the Auto-Promotion option is selected. If the user wishes to assign the signals to the quadrant globals instead of the default chip globals, this can done by using ChipPlanner, by declaring a physical design constraint (PDC), or by importing a PDC file.

### Physical Constraints for Quadrant Clocks

If it is necessary to promote global clocks (CLKBUF, CLKINT, PLL, CLKDLY) to quadrant clocks, the user can define PDCs to execute the promotion. PDCs can be created using PDC commands (pre-compile) or the MultiView Navigator (MVN) interface (post-compile). The advantage of using the PDC flow over the MVN flow is that the Compile stage is able to automatically promote any regular net to a global net before assigning it to a quadrant. There are three options to place a quadrant clock using PDC commands:

- Place a clock core (not hardwired to an I/O) into a quadrant clock location.

- Place a clock core (hardwired to an I/O) into an I/O location (set\_io) or an I/O module location (set\_location) that drives a quadrant clock location.

- Assign a net driven by a regular net or a clock net to a quadrant clock using the following command:

```

assign_local_clock -net <net name> -type quadrant <quadrant clock region> where

```

<net name> is the name of the net assigned to the local user clock region.

<quadrant clock region> defines which quadrant the net should be assigned to. Quadrant

clock regions are defined as UL (upper left), UR (upper right), LL (lower left), and LR (lower right).

Note: If the net is a regular net, the software inserts a CLKINT buffer on the net.

#### For example:

```

assign_local_clock -net localReset -type quadrant UR

```

Keep in mind the following when placing quadrant clocks using MultiView Navigator:

#### Hardwired I/O-Driven CCCs

Find the associated clock input port under the Ports tab, and place the input port at one of the Gmn\* locations using PinEditor or I/O Attribute Editor, as shown in Figure 4-32.

Figure 4-32 • Port Assignment for a CCC with Hardwired I/O Clock Input

ProASIC3 nano FPGA Fabric User's Guide

• Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

Figure 4-33 • Quadrant Clock Assignment for a Global Net

#### External I/O-Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

#### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

## **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 110.

## **Conclusion**

The advanced CCCs of the IGLOO and ProASIC3 devices are ideal for applications requiring precise clock management. They integrate easily with the internal low-skew clock networks and provide flexible frequency synthesis, clock deskewing, and/or time-shifting operations.

## **Related Documents**

## **Application Notes**

Board-Level Considerations

http://www.microsemi.com/soc/documents/ALL AC276 AN.pdf

### **Datasheets**

Fusion Family of Mixed Signal FPGAs http://www.microsemi.com/soc/documents/Fusion DS.pdf

### **User's Guides**

IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3 libguide ug.pdf

## **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date          | Changes                                                                                                                                                                                                                                 | Page          |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| August 2012   | The "Implementing EXTFB in ProASIC3/E Devices" section is new (SAR 36647).                                                                                                                                                              | 70            |

|               | Table 4-7 • Delay Values in Libero SoC Software per Device Family was added to the "Clock Delay Adjustment" section (SAR 22709).                                                                                                        | 86            |

|               | The "Phase Adjustment" section was rewritten to explain better why the visual CCC shows both the actual phase and the actual delay that is equivalent to this phase shift (SAR 29647).                                                  | 87            |

|               | The hyperlink for the <i>Board-Level Considerations</i> application note was corrected (SAR 36663)                                                                                                                                      | 112, 113      |

| December 2011 | Figure 4-20 • PLL Block Diagram, Figure 4-22 • CCC Block Control Bits – Graphical Representation of Assignments, and Table 4-12 • MUXA, MUXB, MUXC were revised to change the phase shift assignments for PLLs 4 through 7 (SAR 33791). | 85, 89,<br>93 |

| June 2011     | The description for RESETEN in Table 4-8 • Configuration Bit Descriptions for the CCC Blocks was revised. The phrase "and should not be modified via dynamic configuration" was deleted because RESETEN is read only (SAR 25949).       | 90            |

| July 2010     | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                               | N/A           |

|               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                               | N/A           |

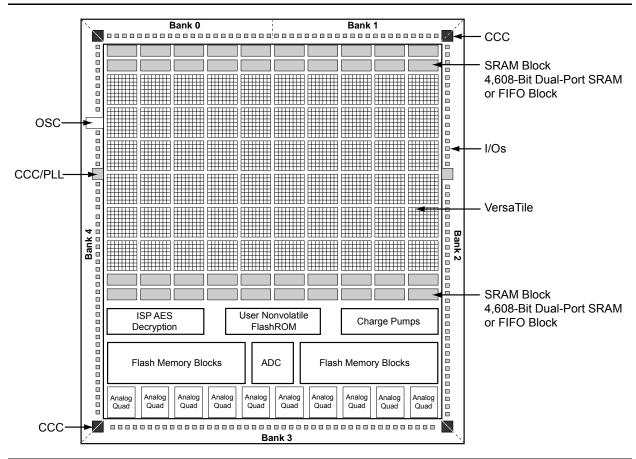

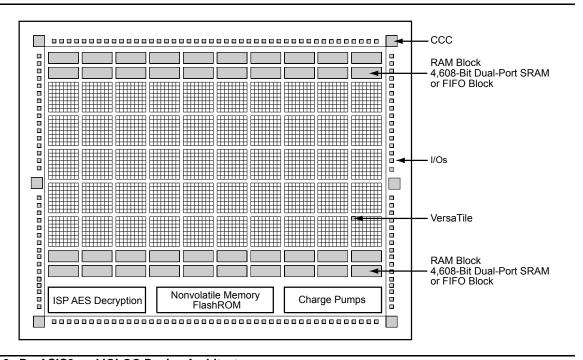

Figure 5-2 • Fusion Device Architecture Overview (AFS600)

Figure 5-3 • ProASIC3 and IGLOO Device Architecture

ProASIC3 nano FPGA Fabric User's Guide

## FlashROM Generation and Instantiation in the Design

The SmartGen core generator, available in Libero SoC and Designer, is the only tool that can be used to generate the FlashROM content. SmartGen has several user-friendly features to help generate the FlashROM contents. Instead of selecting each byte and assigning values, you can create a region within a page, modify the region, and assign properties to that region. The FlashROM user interface, shown in Figure 5-10, includes the configuration grid, existing regions list, and properties field. The properties field specifies the region-specific information and defines the data used for that region. You can assign values to the following properties:

- Static Fixed Data—Enables you to fix the data so it cannot be changed during programming time.

This option is useful when you have fixed data stored in this region, which is required for the

operation of the design in the FPGA. Key storage is one example.

- 2. Static Modifiable Data—Select this option when the data in a particular region is expected to be static data (such as a version number, which remains the same for a long duration but could conceivably change in the future). This option enables you to avoid changing the value every time you enter new data.

- 3. Read from File—This provides the full flexibility of FlashROM usage to the customer. If you have a customized algorithm for generating the FlashROM data, you can specify this setting. You can then generate a text file with data for as many devices as you wish to program, and load that into the FlashPoint programming file generation software to get programming files that include all the data. SmartGen will optionally pass the location of the file where the data is stored if the file is specified in SmartGen. Each text file has only one type of data format (binary, decimal, hex, or ASCII text). The length of each data file must be shorter than or equal to the selected region length. If the data is shorter than the selected region length, the most significant bits will be padded with 0s. For multiple text files for multiple regions, the first lines are for the first device. In SmartGen, Load Sim. Value From File allows you to load the first device data in the MEM file for simulation.

- 4. Auto Increment/Decrement—This scenario is useful when you specify the contents of FlashROM for a large number of devices in a series. You can specify the step value for the serial number and a maximum value for inventory control. During programming file generation, the actual number of devices to be programmed is specified and a start value is fed to the software.

Figure 5-10 • SmartGen GUI of the FlashROM

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

without reprogramming the device. Dynamic flag settings are determined by register values and can be altered without reprogramming the device by reloading the register values either from the design or through the UJTAG interface described in the "Initializing the RAM/FIFO" section on page 148.

SmartGen can also configure the FIFO to continue counting after the FIFO is full. In this configuration, the FIFO write counter will wrap after the counter is full and continue to write data. With the FIFO configured to continue to read after the FIFO is empty, the read counter will also wrap and re-read data that was previously read. This mode can be used to continually read back repeating data patterns stored in the FIFO (Figure 6-15).

### Figure 6-15 • SmartGen FIFO Configuration Interface

FIFOs configured using SmartGen can also make use of the port mapping feature to configure the names of the ports.

#### Limitations

Users should be aware of the following limitations when configuring SRAM blocks for low power flash devices:

- SmartGen does not track the target device in a family, so it cannot determine if a configured memory block will fit in the target device.

- Dual-port RAMs with different read and write aspect ratios are not supported.

- Cascaded memory blocks can only use a maximum of 64 blocks of RAM.

- The Full flag of the FIFO is sensitive to the maximum depth of the actual physical FIFO block, not the depth requested in the SmartGen interface.

I/O Software Control in Low Power Flash Devices

those banks, the user does not need to assign the same VCCI voltage to another bank. The user needs to assign the other three VCCI voltages to three more banks.

## Assigning Technologies and VREF to I/O Banks

Low power flash devices offer a wide variety of I/O standards, including voltage-referenced standards. Before proceeding to Layout, each bank must have the required VCCI voltage assigned for the corresponding I/O technologies used for that bank. The voltage-referenced standards require the use of a reference voltage (VREF). This assignment can be done manually or automatically. The following sections describe this in detail.

## Manually Assigning Technologies to I/O Banks

The user can import the PDC at this point and resolve this requirement. The PDC command is set\_iobank [bank name] -vcci [vcci value]

Another method is to use the I/O Bank Settings dialog box (MVN > Edit > I/O Bank Settings) to set up the  $V_{CCI}$  voltage for the bank (Figure 8-12).

Figure 8-12 • Setting VCCI for a Bank

#### DDR for Microsemi's Low Power Flash Devices

```

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

TRIBUFF_F_8U_0_inst : TRIBUFF_F_8U

port map(D => Q, E => TrienAux, PAD => PAD);

end DEF_ARCH;

```

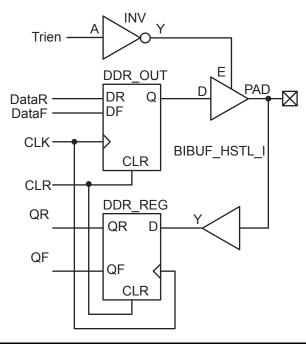

### **DDR Bidirectional Buffer**

Figure 9-8 • DDR Bidirectional Buffer, LOW Output Enable (HSTL Class II)

## Verilog

```

module DDR_BiDir_HSTL_I_LowEnb(DataR,DataF,CLR,CLK,Trien,QR,QF,PAD);

input DataR, DataF, CLR, CLK, Trien;

output QR, QF;

inout PAD;

wire TrienAux, D, Q;

INV Inv_Tri(.A(Trien), .Y(TrienAux));

DDR_OUT DDR_OUT_O_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

DDR_REG DDR_REG_O_inst(.D(D),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

BIBUF_HSTL_I BIBUF_HSTL_I_O_inst(.PAD(PAD),.D(Q),.E(TrienAux),.Y(D));

endmodule

```

### **Device Programmers**

#### Single Device Programmer

Single device programmers are used to program a device before it is mounted on the system board.

The advantage of using device programmers is that no programming hardware is required on the system board. Therefore, no additional components or board space are required.

Adapter modules are purchased with single device programmers to support the FPGA packages used. The FPGA is placed in the adapter module and the programming software is run from a PC. Microsemi supplies the programming software for all of the Microsemi programmers. The software allows for the selection of the correct die/package and programming files. It will then program and verify the device.

Single-site programmers

A single-site programmer programs one device at a time. Microsemi offers Silicon Sculptor 3, built by BP Microsystems, as a single-site programmer. Silicon Sculptor 3 and associated software are available only from Microsemi.

- Advantages: Lower cost than multi-site programmers. No additional overhead for programming on the system board. Allows local control of programming and data files for maximum security. Allows on-demand programming on-site.

- Limitations: Only programs one device at a time.

- Multi-site programmers

Often referred to as batch or gang programmers, multi-site programmers can program multiple devices at the same time using the same programming file. This is often used for large volume programming and by programming houses. The sites often have independent processors and memory enabling the sites to operate concurrently, meaning each site may start programming the same file independently. This enables the operator to change one device while the other sites continue programming, which increases throughput. Multiple adapter modules for the same package are required when using a multi-site programmer. Silicon Sculptor I, II, and 3 programmers can be cascaded to program multiple devices in a chain. Multi-site programmers, such as the BP2610 and BP2710, can also be purchased from BP Microsystems. When using BP Microsystems multi-site programmers, users must use programming adapter modules available only from Microsemi. Visit the Microsemi SoC Products Group website to view the part numbers of the desired adapter module:

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx.

Also when using BP Microsystems programmers, customers must use Microsemi programming software to ensure the best programming result will occur.

- Advantages: Provides the capability of programming multiple devices at the same time. No additional overhead for programming on the system board. Allows local control of programming and data files for maximum security.

- Limitations: More expensive than a single-site programmer

- · Automated production (robotic) programmers

Automated production programmers are based on multi-site programmers. They consist of a large input tray holding multiple parts and a robotic arm to select and place parts into appropriate programming sockets automatically. When the programming of the parts is complete, the parts are removed and placed in a finished tray. The automated programmers are often used in volume programming houses to program parts for which the programming time is small. BP Microsystems part number BP4710, BP4610, BP3710 MK2, and BP3610 are available for this purpose. Auto programmers cannot be used to program RTAX-S devices.

Where an auto-programmer is used, the appropriate open-top adapter module from BP Microsystems must be used.

### Figure 11-15 • Programming Fusion Security Settings Only

- 2. Choose the desired security level setting and enter the key(s).

- The **High** security level employs FlashLock Pass Key with AES Key protection.

- The **Medium** security level employs FlashLock Pass Key protection only.

Figure 11-16 • High Security Level to Implement FlashLock Pass Key and AES Key Protection

## FlashROM and Programming Files

Each low power flash device has 1 kbit of on-chip, nonvolatile flash memory that can be accessed from the FPGA core. This nonvolatile FlashROM is arranged in eight pages of 128 bits (Figure 12-3). Each page can be programmed independently, with or without the 128-bit AES encryption. The FlashROM can only be programmed via the IEEE 1532 JTAG port and cannot be programmed from the FPGA core. In addition, during programming of the FlashROM, the FPGA core is powered down automatically by the on-chip programming control logic.

|        |   |    |    |    |    | Ву | ∕te Nu | umbe | r in F | age |   |   |   |   |   |   |   |

|--------|---|----|----|----|----|----|--------|------|--------|-----|---|---|---|---|---|---|---|

|        |   | 15 | 14 | 13 | 12 | 11 | 10     | 9    | 8      | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|        | 7 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| _      | 6 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Number | 5 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Шn     | 4 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

|        | 3 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Page   | 2 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Δ.     | 1 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

|        | 0 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

Figure 12-3 • FlashROM Architecture

When using FlashROM combined with AES, many subscription-based applications or device serialization applications are possible. The FROM configurator found in the Libero SoC Catalog supports easy management of the FlashROM contents, even over large numbers of devices. The FROM configurator can support FlashROM contents that contain the following:

- Static values

- Random numbers

- · Values read from a file

- · Independent updates of each page

In addition, auto-incrementing of fields is possible. In applications where the FlashROM content is different for each device, you have the option to generate a single STAPL file for all the devices or individual serialization files for each device. For more information on how to generate the FlashROM content for device serialization, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 117.

Libero SoC includes a unique tool to support the generation and management of FlashROM and FPGA programming files. This tool is called FlashPoint.

Depending on the applications, designers can use the FlashPoint software to generate a STAPL file with different contents. In each case, optional AES encryption and/or different security settings can be set.

In Designer, when you click the Programming File icon, FlashPoint launches, and you can generate STAPL file(s) with four different cases (Figure 12-4 on page 268). When the serialization feature is used during the configuration of FlashROM, you can generate a single STAPL file that will program all the devices or an individual STAPL file for each device.

The following cases present the FPGA core and FlashROM programming file combinations that can be used for different applications. In each case, you can set the optional security settings (FlashLock Pass Key and/or AES Key) depending on the application.

- A single STAPL file or multiple STAPL files with multiple FlashROM contents and the FPGA core content. A single STAPL file will be generated if the device serialization feature is not used. You can program the whole FlashROM or selectively program individual pages.

- 2. A single STAPL file for the FPGA core content

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

## Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 13-1 support the voltage switching circuit feature and the functions described in this document.

Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family*              | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGL00    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Power-Up/-Down Behavior of Low Power Flash Devices

## Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 17-1 support power-up behavior and the functions described in this document.

Table 17-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

ProASIC3 nano FPGA Fabric User's Guide

## I/O Behavior at Power-Up/-Down

This section discusses the behavior of device I/Os, used and unused, during power-up/-down of  $V_{CCI}$  and  $V_{CCI}$ . As mentioned earlier, VMVx and  $V_{CCI}$ Bx are tied together, and therefore, inputs and outputs are powered up/down at the same time.

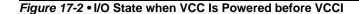

## I/O State during Power-Up/-Down

This section discusses the characteristics of I/O behavior during device power-up and power-down. Before the start of power-up, all I/Os are in tristate mode. The I/Os will remain tristated during power-up until the last voltage supply (VCC or VCCI) is powered to its functional level (power supply functional levels are discussed in the "Power-Up to Functional Time" section on page 312). After the last supply reaches the functional level, the outputs will exit the tristate mode and drive the logic at the input of the output buffer. Similarly, the input buffers will pass the external logic into the FPGA fabric once the last supply reaches the functional level. The behavior of user I/Os is independent of the VCC and VCCI sequence or the state of other voltage supplies of the FPGA (VPUMP and VJTAG). Figure 17-2 shows the output buffer driving HIGH and its behavior during power-up with 10 k $\Omega$  external pull-down. In Figure 17-2, VCC is powered first, and VCCI is powered 5 ms after VCC. Figure 17-3 on page 312 shows the state of the I/O when VCCI is powered about 5 ms before VCC. In the circuitry shown in Figure 17-3 on page 312, the output is externally pulled down.

During power-down, device I/Os become tristated once the first power supply (VCC or VCCI) drops below its brownout voltage level. The I/O behavior during power-down is also independent of voltage supply sequencing.

The following devices and families do not support cold-sparing:

- IGLOO: AGL060, AGL125, AGL250, AGL600, AGL1000

- ProASIC3: A3P060, A3P125, A3P250, A3P400, A3P600, A3P1000

- ProASIC3L: A3P250L, A3P600L, A3P1000L

- Military ProASIC3: A3P1000

## **Hot-Swapping**

Hot-swapping is the operation of hot insertion or hot removal of a card in a powered-up system. The I/Os need to be configured in hot-insertion mode if hot-swapping compliance is required. For more details on the levels of hot-swap compatibility in low power flash devices, refer to the "Hot-Swap Support" section in the I/O Structures chapter of the user's guide for the device you are using.

The following devices and families support hot-swapping:

- IGLOO: AGL015 and AGL030

- All IGLOO nano

- All IGLOO PLUS

- All IGLOOe

- ProASIC3L: A3PE3000L

- ProASIC3: A3P015 and A3P030

- All ProASIC3 nano

- All ProASIC3E

- Military ProASIC3EL: A3PE600L and A3PE3000L

- RT ProASIC3: RT3PE600L and RT3PE3000L

The following devices and families do not support hot-swapping:

- IGLOO: AGL060, AGL125, AGL250, AGL400, AGL600, AGL1000

- ProASIC3: A3P060, A3P125, A3P250, A3P400, A3P600, A3P1000

- ProASIC3L: A3P250L, A3P600L, A3P1000L

- · Military ProASIC3: A3P1000

## Conclusion

Microsemi's low power flash FPGAs provide an excellent programmable logic solution for a broad range of applications. In addition to high performance, low cost, security, nonvolatility, and single chip, they are live at power-up (meet Level 0 of the LAPU classification) and offer clear and easy-to-use power-up/down characteristics. Unlike SRAM FPGAs, low power flash devices do not require any specific power-up/down sequencing and have extremely low power-up inrush current in any power-up sequence. Microsemi low power flash FPGAs also support both cold-sparing and hot-swapping for applications requiring these capabilities.

# A - Summary of Changes

## **History of Revision to Chapters**

The following table lists chapters that were affected in each revision of this document. Each chapter includes its own change history because it may appear in other device family user's guides. Refer to the individual chapter for a list of specific changes.

| Revision<br>(month/year)       | Chapter Affected                                                                                                                                    | List of Changes (page number) |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Revision 5<br>(September 2012) | "Microprocessor Programming of Microsemi's Low Power Flash Devices" was revised.                                                                    | 290                           |

| Revision 4<br>(August 2012)    | "FPGA Array Architecture in Low Power Flash Devices" was revised.                                                                                   | 20                            |

|                                | The "Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs" chapter was added (SAR 32020).                                                          | 21                            |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "SRAM and FIFO Memories in Microsemi's Low Power Flash Devices" was revised.                                                                        | 157                           |

|                                | "I/O Structures in nano Devices" was revised.                                                                                                       | 183                           |

|                                | The "Pin Descriptions" and "Packaging" chapters were removed. This information is now published in the datasheet for each product line (SAR 34772). | N/A                           |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                              | 273                           |

|                                | "Boundary Scan in Low Power Flash Devices" was revised.                                                                                             | 296                           |

| Revision 3<br>(December 2011)  | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "UJTAG Applications in Microsemi's Low Power Flash Devices" was revised.                                                                            | 306                           |

| Revision 2<br>(June 2011)      | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "I/O Structures in nano Devices" was revised.                                                                                                       | 183                           |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                      | 204                           |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                              | 273                           |

| Revision 1<br>(July 2010)      | "Global Resources in Low Power Flash Devices" was revised.                                                                                          | 59                            |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                      | 204                           |

|                                | "DDR for Microsemi's Low Power Flash Devices" was revised.                                                                                          | 219                           |

|                                | "Programming Flash Devices" was revised.                                                                                                            | 232                           |