Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | -                                                                          |

| Number of I/O                  | 34                                                                         |

| Number of Gates                | 30000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package        | 48-QFN (6x6)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-z1qng48i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ProASIC3 nano FPGA Fabric User's Guide

|    | IEEE 1532 (JTAG) Interface                                                   | 264 |

|----|------------------------------------------------------------------------------|-----|

|    | Security                                                                     | 264 |

|    | Security in ARM-Enabled Low Power Flash Devices                              | 265 |

|    | FlashROM and Programming Files                                               | 267 |

|    | Programming Solution                                                         | 268 |

|    | ISP Programming Header Information                                           | 269 |

|    | Board-Level Considerations                                                   | 271 |

|    | Conclusion                                                                   | 272 |

|    | Related Documents                                                            | 272 |

|    | List of Changes                                                              | 273 |

| 13 | Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming | 275 |

|    | Introduction                                                                 | 275 |

|    | Microsemi's Flash Families Support Voltage Switching Circuit                 | 276 |

|    | Circuit Description                                                          |     |

|    | Circuit Verification                                                         |     |

|    | DirectC                                                                      |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

| 14 | Microprocessor Programming of Microsemi's Low Power Flash Devices            | 283 |

|    | Introduction                                                                 |     |

|    | Microprocessor Programming Support in Flash Devices                          |     |

|    | Programming Algorithm                                                        |     |

|    | Implementation Overview                                                      |     |

|    | Hardware Requirement                                                         |     |

|    | Security                                                                     |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

| 15 | Boundary Scan in Low Power Flash Devices                                     | 291 |

|    | Boundary Scan                                                                |     |

|    | TAP Controller State Machine                                                 |     |

|    | Microsemi's Flash Devices Support the JTAG Feature                           |     |

|    | Boundary Scan Support in Low Power Devices                                   |     |

|    | Boundary Scan Opcodes                                                        |     |

|    | Boundary Scan Chain                                                          |     |

|    | Board-Level Recommendations                                                  |     |

|    | Advanced Boundary Scan Register Settings                                     |     |

|    | List of Changes                                                              |     |

| 16 | UJTAG Applications in Microsemi's Low Power Flash Devices                    | 297 |

|    | Introduction                                                                 |     |

|    | UJTAG Support in Flash-Based Devices                                         |     |

|    | UJTAG Macro                                                                  |     |

|    |                                                                              |     |

|    | UJTAG Operation                                                              |     |

|    | Typical UJTAG Applications                                                   |     |

|    | Conclusion                                                                   |     |

|    | Related Documents                                                            |     |

|    | List of Changes                                                              | ასხ |

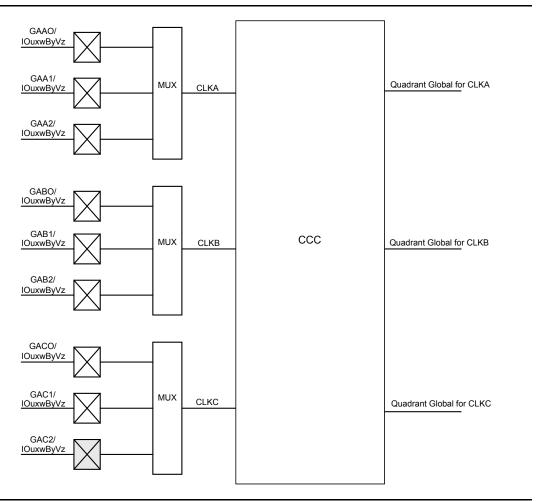

Figure 3-6 shows all nine global inputs for the location A connected to the top left quadrant global network via CCC.

Figure 3-6 • Global Inputs

Since each bank can have a different I/O standard, the user should be careful to choose the correct global I/O for the design. There are 54 global pins available to access 18 global networks. For the single-ended and voltage-referenced I/O standards, you can use any of these three available I/Os to access the global network. For differential I/O standards such as LVDS and LVPECL, the I/O macro needs to be placed on (A0, A1), (B0, B1), (C0, C1), or a similar location. The unassigned global I/Os can be used as regular I/Os. Note that pin names starting with GF and GC are associated with the chip global networks, and GA, GB, GD, and GE are used for quadrant global networks. Table 3-2 on page 38 and Table 3-3 on page 39 show the general chip and quadrant global pin names.

standard for CLKBUF is LVTTL in the current Microsemi Libero $^{\circledR}$  System-on-Chip (SoC) and Designer software.

Table 3-9 • I/O Standards within CLKBUF

| Name             | Description                                                    |

|------------------|----------------------------------------------------------------|

| CLKBUF_LVCMOS5   | LVCMOS clock buffer with 5.0 V CMOS voltage level              |

| CLKBUF_LVCMOS33  | LVCMOS clock buffer with 3.3 V CMOS voltage level              |

| CLKBUF_LVCMOS25  | LVCMOS clock buffer with 2.5 V CMOS voltage level <sup>1</sup> |

| CLKBUF_LVCMOS18  | LVCMOS clock buffer with 1.8 V CMOS voltage level              |

| CLKBUF_LVCMOS15  | LVCMOS clock buffer with 1.5 V CMOS voltage level              |

| CLKBUF_LVCMOS12  | LVCMOS clock buffer with 1.2 V CMOS voltage level              |

| CLKBUF_PCI       | PCI clock buffer                                               |

| CLKBUF_PCIX      | PCIX clock buffer                                              |

| CLKBUF_GTL25     | GTL clock buffer with 2.5 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTL33     | GTL clock buffer with 3.3 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTLP25    | GTL+ clock buffer with 2.5 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_GTLP33    | GTL+ clock buffer with 3.3 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_ HSTL _I  | HSTL Class I clock buffer <sup>1</sup>                         |

| CLKBUF_ HSTL _II | HSTL Class II clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_I   | SSTL2 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_II  | SSTL2 Class II clock buffer <sup>1</sup>                       |

| CLKBUF_SSTL3_I   | SSTL3 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL3_II  | SSTL3 Class II clock buffer <sup>1</sup>                       |

#### Notes:

- 1. Supported in only the IGLOOe, ProASIC3E, AFS600, and AFS1500 devices

- 2. By default, the CLKBUF macro uses the 3.3 V LVTTL I/O technology.

The current synthesis tool libraries only infer the CLKBUF or CLKINT macros in the netlist. All other global macros must be instantiated manually into your HDL code. The following is an example of CLKBUF LVCMOS25 global macro instantiations that you can copy and paste into your code:

#### **VHDL**

```

component clkbuf_lvcmos25

port (pad : in std_logic; y : out std_logic);

end component

begin

-- concurrent statements

u2 : clkbuf_lvcmos25 port map (pad => ext_clk, y => int_clk);

end

Verilog

module design (_____);

input ____;

output ____;

clkbuf_lvcmos25 u2 (.y(int_clk), .pad(ext_clk);

endmodule

```

Global Resources in Low Power Flash Devices

#### Step 1

Run Synthesis with default options. The Synplicity log shows the following device utilization:

#### Cell usage:

|          | cell count | area | count*area |

|----------|------------|------|------------|

| DFN1E1C1 | 1536       | 2.0  | 3072.0     |

| BUFF     | 278        | 1.0  | 278.0      |

| INBUF    | 10         | 0.0  | 0.0        |

| VCC      | 9          | 0.0  | 0.0        |

| GND      | 9          | 0.0  | 0.0        |

| OUTBUF   | 6          | 0.0  | 0.0        |

| CLKBUF   | 3          | 0.0  | 0.0        |

| PLL      | 2          | 0.0  | 0.0        |

| TOTAL    | 1853       |      | 3350.0     |

### Step 2

Run Compile with the **Promote regular nets whose fanout is greater than** option selected in Designer; you will see the following in the Compile report:

| Device utilization report:              |       |      |        |       |           |  |  |

|-----------------------------------------|-------|------|--------|-------|-----------|--|--|

| ======================================= |       |      |        |       |           |  |  |

| CORE                                    | Used: | 1536 | Total: | 13824 | (11.11%)  |  |  |

| IO (W/ clocks)                          | Used: | 19   | Total: | 147   | (12.93%)  |  |  |

| Differential IO                         | Used: | 0    | Total: | 65    | (0.00%)   |  |  |

| GLOBAL                                  | Used: | 8    | Total: | 18    | (44.44%)  |  |  |

| PLL                                     | Used: | 2    | Total: | 2     | (100.00%) |  |  |

| RAM/FIFO                                | Used: | 0    | Total: | 24    | (0.00%)   |  |  |

| FlashROM                                | Used: | 0    | Total: | 1     | (0.00%)   |  |  |

|                                         |       |      |        |       |           |  |  |

The following nets have been assigned to a global resource:

| Fanout |                        | Name    | abbigned to a groba |

|--------|------------------------|---------|---------------------|

| 1536   | INT_NET                | Net :   | EN_ALL_c            |

|        |                        | Driver: | EN_ALL_pad_CLKINT   |

|        |                        | Source: | AUTO PROMOTED       |

| 1536   | ${\tt SET/RESET\_NET}$ | Net :   | ACLR_c              |

|        |                        | Driver: | ACLR_pad_CLKINT     |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK1_c             |

|        |                        | Driver: | QCLK1_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK2_c             |

|        |                        | Driver: | QCLK2_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK3_c             |

|        |                        | Driver: | QCLK3_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | \$1N14              |

|        |                        | Driver: | \$1I5/Core          |

|        |                        | Source: | ESSENTIAL           |

| 256    | CLK_NET                | Net :   | \$1N12              |

|        |                        | Driver: | \$1I6/Core          |

|        |                        | Source: | ESSENTIAL           |

| 256    | CLK_NET                | Net :   | \$1N10              |

|        |                        | Driver: | \$1I6/Core          |

|        |                        | Source: | ESSENTIAL           |

Designer will promote five more signals to global due to high fanout. There are eight signals assigned to global networks.

# 4 - Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### Introduction

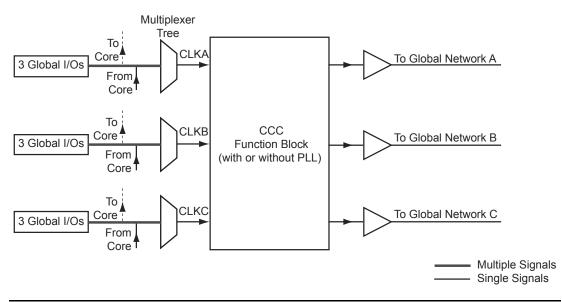

This document outlines the following device information: Clock Conditioning Circuit (CCC) features, PLL core specifications, functional descriptions, software configuration information, detailed usage information, recommended board-level considerations, and other considerations concerning clock conditioning circuits and global networks in low power flash devices or mixed signal FPGAs.

## **Overview of Clock Conditioning Circuitry**

In Fusion, IGLOO, and ProASIC3 devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations. The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides. For device-specific variations, refer to the "Device-Specific Layout" section on page 78.

The CCC is composed of the following:

- · PLL core

- · 3 phase selectors

- · 6 programmable delays and 1 fixed delay that advances/delays phase

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 4-6 on page 71 because they are automatically configured based on the user's required frequencies)

- · 1 dynamic shift register that provides CCC dynamic reconfiguration capability

Figure 4-1 provides a simplified block diagram of the physical implementation of the building blocks in each of the CCCs.

Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3

#### **External Feedback Configuration**

For certain applications, such as those requiring generation of PCB clocks that must be matched with existing board delays, it is useful to implement an external feedback, EXTFB. The Phase Detector of the PLL core will receive CLKA and EXTFB as inputs. EXTFB may be processed by the fixed System Delay element as well as the *M* divider element. The EXTFB option is currently not supported.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

: test_pll

Family

: ProASIC3E

Output Format

: VHDL

: Static PLL

Type

Input Freq(MHz)

: 10.000

CLKA Source

: Hardwired I/O

Feedback Delay Value Index : 1

Feedback Mux Select : 2

XDLY Mux Select

: No

Primary Freq(MHz) : 3

Primary PhaseShift : 0

Primary Delay Value Index : 1

: 33.000

Primary Mux Select : 4

Secondaryl Freq(MHz) : 66.000

Use GLB

: YES

Use YB

: YES

: 1

GLB Delay Value Index

YB Delay Value Index

Secondaryl PhaseShift

Secondary1 Mux Select

Secondary2 Freq(MHz)

: 101.000

: YES

Use GLC

Use YC

: NO

GLC Delay Value Index

: 1

YC Delay Value Index

: 1

Secondary2 PhaseShift

: 0

Secondary2 Mux Select

Primary Clock frequency 33.333

Primary Clock Phase Shift 0.000

Primary Clock Output Delay from CLKA 0.180

Secondary1 Clock frequency 66.667

Secondaryl Clock Phase Shift 0.000

Secondaryl Clock Global Output Delay from CLKA 0.180

Secondaryl Clock Core Output Delay from CLKA 0.625

Secondary2 Clock frequency 100.000

Secondary2 Clock Phase Shift 0.000

Secondary2 Clock Global Output Delay from CLKA 0.180

```

Below is an example Verilog HDL description of a legal PLL core configuration generated by SmartGen:

```

module test_pll(POWERDOWN,CLKA,LOCK,GLA);

input POWERDOWN, CLKA;

output LOCK, GLA;

```

#### ProASIC3 nano FPGA Fabric User's Guide

The following is an example of a PLL configuration utilizing the clock frequency synthesis and clock delay adjustment features. The steps include generating the PLL core with SmartGen, performing simulation for verification with Model *Sim*, and performing static timing analysis with SmartTime in Designer.

Parameters of the example PLL configuration:

Input Frequency - 20 MHz

Primary Output Requirement – 20 MHz with clock advancement of 3.02 ns

Secondary 1 Output Requirement - 40 MHz with clock delay of 2.515 ns

Figure 4-29 shows the SmartGen settings. Notice that the overall delays are calculated automatically, allowing the user to adjust the delay elements appropriately to obtain the desired delays.

#### Figure 4-29 • SmartGen Settings

After confirming the correct settings, generate a structural netlist of the PLL and verify PLL core settings by checking the log file:

```

Name

: test_pll_delays

Family

: ProASIC3E

Output Format

: VHDL

: Static PLL

Type

Input Freq(MHz)

: 20.000

CLKA Source

: Hardwired I/O

Feedback Delay Value Index

: 21

Feedback Mux Select

XDLY Mux Select

Primary Freq(MHz)

Primary PhaseShift

: No

: 20.000

: 0

Primary Delay Value Index

: 1

Primary Mux Select

: 4

Secondaryl Freq(MHz)

: 40.000

Use GLB

: YES

Use YB

: NO

Primary Clock frequency 20.000

Primary Clock Phase Shift 0.000

```

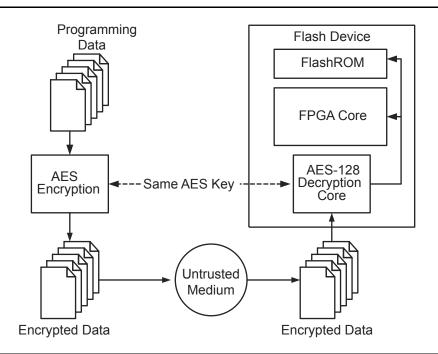

## FlashROM Security

Low power flash devices have an on-chip Advanced Encryption Standard (AES) decryption core, combined with an enhanced version of the Microsemi flash-based lock technology (FlashLock®). Together, they provide unmatched levels of security in a programmable logic device. This security applies to both the FPGA core and FlashROM content. These devices use the 128-bit AES (Rijndael) algorithm to encrypt programming files for secure transmission to the on-chip AES decryption core. The same algorithm is then used to decrypt the programming file. This key size provides approximately  $3.4 \times 10^{38}$  possible 128-bit keys. A computing system that could find a DES key in a second would take approximately 149 trillion years to crack a 128-bit AES key. The 128-bit FlashLock feature in low power flash devices works via a FlashLock security Pass Key mechanism, where the user locks or unlocks the device with a user-defined key. Refer to the "Security in Low Power Flash Devices" section on page 235.

If the device is locked with certain security settings, functions such as device read, write, and erase are disabled. This unique feature helps to protect against invasive and noninvasive attacks. Without the correct Pass Key, access to the FPGA is denied. To gain access to the FPGA, the device first must be unlocked using the correct Pass Key. During programming of the FlashROM or the FPGA core, you can generate the security header programming file, which is used to program the AES key and/or FlashLock Pass Key. The security header programming file can also be generated independently of the FlashROM and FPGA core content. The FlashLock Pass Key is not stored in the FlashROM.

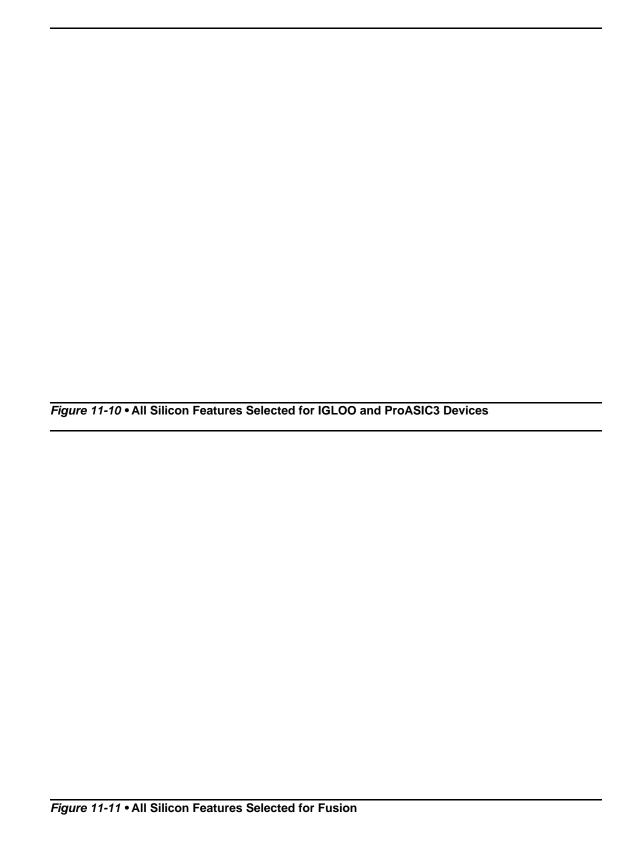

Low power flash devices with AES-based security allow for secure remote field updates over public networks such as the Internet, and ensure that valuable intellectual property (IP) remains out of the hands of IP thieves. Figure 5-5 shows this flow diagram.

Figure 5-5 • Programming FlashROM Using AES

ProASIC3 nano FPGA Fabric User's Guide

#### FlashROM Generation and Instantiation in the Design

The SmartGen core generator, available in Libero SoC and Designer, is the only tool that can be used to generate the FlashROM content. SmartGen has several user-friendly features to help generate the FlashROM contents. Instead of selecting each byte and assigning values, you can create a region within a page, modify the region, and assign properties to that region. The FlashROM user interface, shown in Figure 5-10, includes the configuration grid, existing regions list, and properties field. The properties field specifies the region-specific information and defines the data used for that region. You can assign values to the following properties:

- Static Fixed Data—Enables you to fix the data so it cannot be changed during programming time.

This option is useful when you have fixed data stored in this region, which is required for the

operation of the design in the FPGA. Key storage is one example.

- 2. Static Modifiable Data—Select this option when the data in a particular region is expected to be static data (such as a version number, which remains the same for a long duration but could conceivably change in the future). This option enables you to avoid changing the value every time you enter new data.

- 3. Read from File—This provides the full flexibility of FlashROM usage to the customer. If you have a customized algorithm for generating the FlashROM data, you can specify this setting. You can then generate a text file with data for as many devices as you wish to program, and load that into the FlashPoint programming file generation software to get programming files that include all the data. SmartGen will optionally pass the location of the file where the data is stored if the file is specified in SmartGen. Each text file has only one type of data format (binary, decimal, hex, or ASCII text). The length of each data file must be shorter than or equal to the selected region length. If the data is shorter than the selected region length, the most significant bits will be padded with 0s. For multiple text files for multiple regions, the first lines are for the first device. In SmartGen, Load Sim. Value From File allows you to load the first device data in the MEM file for simulation.

- 4. Auto Increment/Decrement—This scenario is useful when you specify the contents of FlashROM for a large number of devices in a series. You can specify the step value for the serial number and a maximum value for inventory control. During programming file generation, the actual number of devices to be programmed is specified and a start value is fed to the software.

Figure 5-10 • SmartGen GUI of the FlashROM

#### Notes:

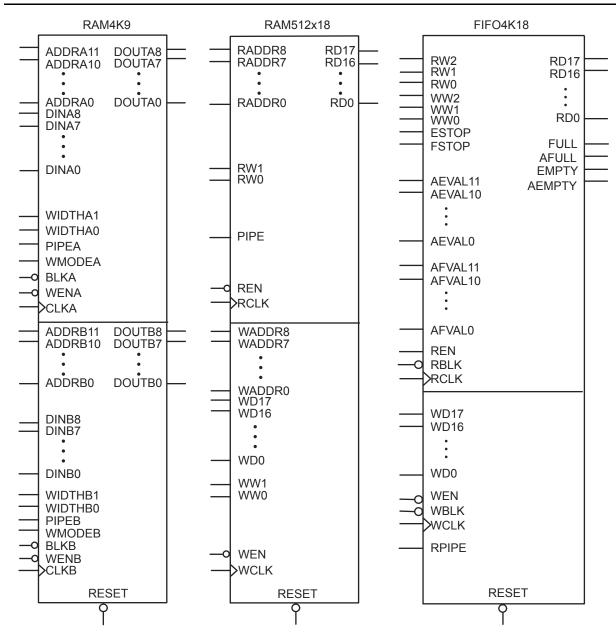

- 1. Automotive ProASIC3 devices restrict RAM4K9 to a single port or to dual ports with the same clock 180° out of phase (inverted) between clock pins. In single-port mode, inputs to port B should be tied to ground to prevent errors during compile. This warning applies only to automotive ProASIC3 parts of certain revisions and earlier. Contact Technical Support at soc\_tech @microsemi.com for information on the revision number for a particular lot and date code.

- 2. For FIFO4K18, the same clock 180° out of phase (inverted) between clock pins should be used.

Figure 6-3 • Supported Basic RAM Macros

Table 6-10 • RAM and FIFO Memory Block Consumption

|       |    | Depth         |                                 |                                |                                |                                                |                                                 |                                                 |                                                    |                                                    |                                                   |                                                    |

|-------|----|---------------|---------------------------------|--------------------------------|--------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

|       | Ī  |               | 25                              | 56                             | 512                            | 1,024                                          | 2,048                                           | 4,096                                           | 8,192                                              | 16,384                                             | 32,768                                            | 65,536                                             |

|       | Ī  |               | Two-Port                        | Dual-Port                      | Dual-Port                      | Dual-Port                                      | Dual-Port                                       | Dual-Port                                       | Dual-Port                                          | Dual-Port                                          | Dual-Port                                         | Dual-Port                                          |

|       | 1  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 1                                               | 2                                                  | 4                                                  | 8                                                 | 16 × 1                                             |

|       | Ī  | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2,048 × 2                                       | 4,096 × 1                                       | 2 × (4,096 × 1)<br>Cascade Deep                    | 4 × (4,096 × 1)<br>Cascade Deep                    | 8 × (4,096 × 1)<br>Cascade Deep                   | 16 × (4,096 × 1)<br>Cascade Deep                   |

|       | 2  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 2                                               | 4                                                  | 8                                                  | 16                                                | 32                                                 |

|       | -  | Configuration | Any                             | Any                            | Any                            | 1,024×4                                        | 2,048 × 2                                       | 2 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 2 Wide   | 8 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 2 Wide   | 16 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 2 Wide | 32 × (4,096 × 1)<br>Cascaded 16<br>Deep and 2 Wide |

|       | 4  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 2                                               | 4                                               | 8                                                  | 16                                                 | 32                                                | 64                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2 × (2,048 × 2)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 4 Wide   | 16 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 4 Wide  | 32 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 4 Wide | 64 × (4,096 × 1)<br>Cascaded 16<br>Deep and 4 Wide |

|       | 8  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 | 64                                                |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (1,024 × 4)<br>Cascaded Wide               | 4 × (2,048 × 2)<br>Cascaded Wide                | 8 × (4,096 × 1)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 8 Wide  | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 8 Wide  | 64 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 8 Wide |                                                    |

|       | 9  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 |                                                   |                                                    |

|       | Ī  | Configuration | Any                             | Any                            | Any                            | 2 × (512 × 9)<br>Cascaded Deep                 | 4 × (512 × 9)<br>Cascaded Deep                  | 8 × (512 × 9)<br>Cascaded Deep                  | 16 × (512 × 9)<br>Cascaded Deep                    | 32 × (512 × 9)<br>Cascaded Deep                    |                                                   |                                                    |

|       | 16 | Number Block  | 1                               | 1                              | 1                              | 4                                              | 8                                               | 16                                              | 32                                                 | 64                                                 |                                                   |                                                    |

| Width | -  | Configuration | 256 × 18                        | 256 × 18                       | 256 × 18                       | 4 × (1,024 × 4)<br>Cascaded Wide               | 8 × (2,048 × 2)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 16 Wide | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 16 Wide |                                                   |                                                    |

|       | 18 | Number Block  | 1                               | 2                              | 2                              | 4                                              | 8                                               | 18                                              | 32                                                 |                                                    |                                                   |                                                    |

|       | -  | Configuration | 256 × 8                         | 2 × (512 × 9)<br>Cascaded Wide | 2 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 2 Wide | 8 × (512 × 9)<br>Cascaded 4 Deep<br>and 2 Wide  | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 2 Wide | 16 × (512 × 9)<br>Cascaded 16<br>Deep and 2 Wide   |                                                    |                                                   |                                                    |

|       | 32 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              | 64                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 8 × (1,024 × 4)<br>Cascaded Wide               | 16 × (2,048 × 2)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 32 Wide |                                                    |                                                   |                                                    |

|       | 36 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 4 Wide |                                                    |                                                    |                                                   |                                                    |

|       | 64 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              | 64                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (1,024 × 4)<br>Cascaded Wide              | 32 × (2,048 × 2)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded Wide               |                                                    |                                                    |                                                   |                                                    |

|       | 72 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (512 × 9)<br>Cascaded Wide                | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 8 Wide |                                                 |                                                    |                                                    |                                                   |                                                    |

Memory configurations represented by grayed cells are not supported.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## **Software Support**

The SmartGen core generator is the easiest way to select and configure the memory blocks (Figure 6-12). SmartGen automatically selects the proper memory block type and aspect ratio, and cascades the memory blocks based on the user's selection. SmartGen also configures any additional signals that may require tie-off.

SmartGen will attempt to use the minimum number of blocks required to implement the desired memory. When cascading, SmartGen will configure the memory for width before configuring for depth. For example, if the user requests a 256×8 FIFO, SmartGen will use a 512×9 FIFO configuration, not 256×18.

Figure 6-12 • SmartGen Core Generator Interface

I/O Software Control in Low Power Flash Devices

## Flash FPGAs I/O Support

The flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

Table 8-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGL00    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLO0e               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

The procedure is as follows:

- 1. Select the bank to which you want VCCI to be assigned from the Choose Bank list.

- Select the I/O standards for that bank. If you select any standard, the tool will automatically show all compatible standards that have a common VCCI voltage requirement.

- 3. Click Apply.

- 4. Repeat steps 1–3 to assign VCCI voltages to other banks. Refer to Figure 8-11 on page 197 to find out how many I/O banks are needed for VCCI bank assignment.

### **Manually Assigning VREF Pins**

Voltage-referenced inputs require an input reference voltage (VREF). The user must assign VREF pins before running Layout. Before assigning a VREF pin, the user must set a VREF technology for the bank to which the pin belongs.

## VREF Rules for the Implementation of Voltage-Referenced I/O Standards

The VREF rules are as follows:

- 1. Any I/O (except JTAG I/Os) can be used as a V<sub>REF</sub> pin.

- 2. One V<sub>REF</sub> pin can support up to 15 I/Os. It is recommended, but not required, that eight of them be on one side and seven on the other side (in other words, all 15 can still be on one side of VREF).

- 3. SSTL3 (I) and (II): Up to 40 I/Os per north or south bank in any position

- 4. LVPECL / GTL+ 3.3 V / GTL 3.3 V: Up to 48 I/Os per north or south bank in any position (not applicable for IGLOO nano and ProASIC3 nano devices)

- 5. SSTL2 (I) and (II) / GTL + 2.5 V / GTL 2.5 V: Up to 72 I/Os per north or south bank in any position

- 6. VREF minibanks partition rule: Each I/O bank is physically partitioned into VREF minibanks. The VREF pins within a VREF minibank are interconnected internally, and consequently, only one VREF voltage can be used within each VREF minibank. If a bank does not require a VREF signal, the VREF pins of that bank are available as user I/Os.

- 7. The first VREF minibank includes all I/Os starting from one end of the bank to the first power triple and eight more I/Os after the power triple. Therefore, the first VREF minibank may contain (0 + 8), (2 + 8), (4 + 8), (6 + 8), or (8 + 8) I/Os.

The second VREF minibank is adjacent to the first VREF minibank and contains eight I/Os, a power triple, and eight more I/Os after the triple. An analogous rule applies to all other VREF minibanks but the last.

The last VREF minibank is adjacent to the previous one but contains eight I/Os, a power triple, and all I/Os left at the end of the bank. This bank may also contain (8 + 0), (8 + 2), (8 + 4), (8 + 6), or (8 + 8) available I/Os.

#### Example:

```

4 I/Os \rightarrow Triple \rightarrow 8 I/Os, 8 I/Os \rightarrow Triple \rightarrow 8 I/Os, 8 I/Os \rightarrow Triple \rightarrow 2 I/Os

```

That is, minibank A = (4 + 8) I/Os, minibank B = (8 + 8) I/Os, minibank C = (8 + 2) I/Os.

8. Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os.

## Assigning the VREF Voltage to a Bank

When importing the PDC file, the VREF voltage can be assigned to the I/O bank. The PDC command is as follows:

```

set iobank -vref [value]

```

Another method for assigning VREF is by using MVN > Edit > I/O Bank Settings (Figure 8-13 on page 200).

#### ProASIC3 nano FPGA Fabric User's Guide

#### **VHDL**

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_BiDir_HSTL_I_LowEnb is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; QR, QF : out std_logic;

PAD : inout std_logic) ;

end DDR_BiDir_HSTL_I_LowEnb;

architecture DEF_ARCH of DDR_BiDir_HSTL_I_LowEnb is

component INV

port(A : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

component BIBUF_HSTL_I

port(PAD : inout std_logic := 'U'; D, E : in std_logic := 'U'; Y : out std_logic);

end component;

signal TrienAux, D, Q : std_logic ;

begin

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

DDR_REG_0_inst : DDR_REG

port map(D => D, CLK => CLK, CLR => CLR, QR => QR, QF => QF);

BIBUF_HSTL_I_0_inst : BIBUF_HSTL_I

port map(PAD => PAD, D => Q, E => TrienAux, Y => D);

end DEF_ARCH;

```

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

| Date                     | Changes                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010<br>(continued) | The "Chain Integrity Test Error Analyze Chain Failure" section was renamed to the "Scan Chain Failure" section, and the Analyze Chain command was changed to Scan Chain. It was noted that occasionally a faulty programmer can cause scan chain failures.                                                                                                                                   | 272  |

| v1.5<br>(August 2009)    | The "CoreMP7 Device Security" section was removed from "Security in ARM-Enabled Low Power Flash Devices", since M7-enabled devices are no longer supported.                                                                                                                                                                                                                                  | 265  |

| v1.4<br>(December 2008)  | The "ISP Architecture" section was revised to include information about core voltage for IGLOO V2 and ProASIC3L devices, as well as 50 mV increments allowable in Designer software.                                                                                                                                                                                                         | 261  |

|                          | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                            | 262  |

|                          | A second capacitor was added to Figure 12-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                                                                                                  | 271  |

| v1.3<br>(October 2008)   | The "ISP Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                  | 262  |

| v1.2<br>(June 2008)      | The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs Supporting ISP:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                    | 262  |

| v1.1<br>(March 2008)     | The "ISP Architecture" section was updated to included the IGLOO PLUS family in the discussion of family-specific support. The text, "When 1.2 V is used, the device can be reprogrammed in-system at 1.5 V only," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when all supplies (VCC, VCCI, and VJTAG) are at 1.5 V." | 261  |

|                          | The "ISP Support in Flash-Based Devices" section and Table 12-1 • Flash-Based FPGAs Supporting ISP were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 262  |

|                          | The "Security" section was updated to mention that 15 k gate devices do not have a built-in 128-bit decryption core.                                                                                                                                                                                                                                                                         | 264  |

|                          | Table 12-2 • Power Supplies was revised to remove the Normal Operation column and add a table note stating, "All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation."                                                                                                                                                                           | 263  |

|                          | The "ISP Programming Header Information" section was revised to change FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT. Table 12-3 • Programming Header Ordering Codes was updated with the same change, as well as adding the part number FFSD-05-D-06.00-01-N, a 10-pin cable with 50-mil-pitch sockets.                                                                                        | 269  |

|                          | The "Board-Level Considerations" section was updated to describe connecting two capacitors in parallel across VPUMP and GND for proper programming.                                                                                                                                                                                                                                          | 271  |

| v1.0<br>(January 2008)   | Information was added to the "Programming Voltage (VPUMP) and VJTAG" section about the JTAG interface pin.                                                                                                                                                                                                                                                                                   | 263  |

| 51900055-2/7.06          | ACTgen was changed to SmartGen.                                                                                                                                                                                                                                                                                                                                                              | N/A  |

|                          | In Figure 12-6 • Board Layout and Programming Header Top View, the order of the text was changed to:  VJTAG from the target board  VCCI from the target board  VCC from the target board                                                                                                                                                                                                     | 271  |

Microprocessor Programming of Microsemi's Low Power Flash Devices

#### Remote Upgrade via TCP/IP

Transmission Control Protocol (TCP) provides a reliable bitstream transfer service between two endpoints on a network. TCP depends on Internet Protocol (IP) to move packets around the network on its behalf. TCP protects against data loss, data corruption, packet reordering, and data duplication by adding checksums and sequence numbers to transmitted data and, on the receiving side, sending back packets and acknowledging the receipt of data.

The system containing the low power flash device can be assigned an IP address when deployed in the field. When the device requires an update (core or FlashROM), the programming instructions along with the new programming data (AES-encrypted cipher text) can be sent over the Internet to the target system via the TCP/IP protocol. Once the MCU receives the instruction and data, it can proceed with the FPGA update. Low power flash devices support Message Authentication Code (MAC), which can be used to validate data for the target device. More details are given in the "Message Authentication Code (MAC) Validation/Authentication" section.

## **Hardware Requirement**

To facilitate the programming of the low power flash families, the system must have a microprocessor (with access to the device JTAG pins) to process the programming algorithm, memory to store the programming algorithm, programming data, and the necessary programming voltage. Refer to the relevant datasheet for programming voltages.

## **Security**

#### **Encrypted Programming**

As an additional security measure, the devices are equipped with AES decryption. AES works in two steps. The first step is to program a key into the devices in a secure or trusted programming center (such as Microsemi SoC Products Group In-House Programming (IHP) center). The second step is to encrypt any programming files with the same encryption key. The encrypted programming file will only work with the devices that have the same key. The AES used in the low power flash families is the 128-bit AES decryption engine (Rijndael algorithm).

## Message Authentication Code (MAC) Validation/Authentication

As part of the AES decryption flow, the devices are equipped with a MAC validation/authentication system. MAC is an authentication tag, also called a checksum, derived by applying an on-chip authentication scheme to a STAPL file as it is loaded into the FPGA. MACs are computed and verified with the same key so they can only be verified by the intended recipient. When the MCU system receives the AES-encrypted programming data (cipher text), it can validate the data by loading it into the FPGA and performing a MAC verification prior to loading the data, via a second programming pass, into the FPGA core cells. This prevents erroneous or corrupt data from getting into the FPGA.

Low power flash devices with AES and MAC are superior to devices with only DES or 3DES encryption. Because the MAC verifies the correctness of the data, the FPGA is protected from erroneous loading of invalid programming data that could damage a device (Figure 14-5 on page 289).

The AES with MAC enables field updates over public networks without fear of having the design stolen. An encrypted programming file can only work on devices with the correct key, rendering any stolen files

useless to the thief. To learn more about the low power flash devices' security features, refer to the "Security in Low Power Flash Devices" section on page 235.

Figure 14-5 • ProASIC3 Device Encryption Flow

## Conclusion

The Fusion, IGLOO, and ProASIC3 FPGAs are ideal for applications that require field upgrades. The single-chip devices save board space by eliminating the need for EEPROM. The built-in AES with MAC enables transmission of programming data over any network without fear of design theft. Fusion, IGLOO, and ProASIC3 FPGAs are IEEE 1532–compliant and support STAPL, making the target programming software easy to implement.

## *Microsemi*

Index

| architecture of user nonvolatile 117 configuration 120 custom serialization 129 design flow 124 generation 125 programming and accessing 122 programming file 127 programming files 267 SmartGen 126 FlashROM read-back 305 | ISP 223, 224 architecture 261 board-level considerations 271 circuit 277 microprocessor 283  J JTAG 1532 261 JTAG interface 285 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| G                                                                                                                                                                                                                           | L                                                                                                                               |

| global architecture 31                                                                                                                                                                                                      | layout                                                                                                                          |

| global buffers                                                                                                                                                                                                              | device-specific 78                                                                                                              |

| no programmable delays 64                                                                                                                                                                                                   | LTC3025 linear voltage regulator 277                                                                                            |

| with PLL function 67                                                                                                                                                                                                        |                                                                                                                                 |

| with programmable delays 64                                                                                                                                                                                                 | M                                                                                                                               |

| global macros                                                                                                                                                                                                               | MAC validation/authentication 288                                                                                               |

| Synplicity 50                                                                                                                                                                                                               | macros                                                                                                                          |

| globals                                                                                                                                                                                                                     | CLKBUF 77                                                                                                                       |

| designer flow 53                                                                                                                                                                                                            | CLKBUF_LVDS/LVPECL 77                                                                                                           |

| networks 58                                                                                                                                                                                                                 | CLKDLY 65, 73                                                                                                                   |

| spines and rows 41                                                                                                                                                                                                          | FIFO4KX18 141                                                                                                                   |

| ·                                                                                                                                                                                                                           | PLL 73                                                                                                                          |

| Н                                                                                                                                                                                                                           | PLL macro signal descriptions 68                                                                                                |

| HLD code                                                                                                                                                                                                                    | RAM4K9 137                                                                                                                      |

| instantiating 192                                                                                                                                                                                                           | RAM512X18 139                                                                                                                   |

| hot-swap 167                                                                                                                                                                                                                | supported basic RAM macros 136<br>UJTAG 299                                                                                     |

| hot-swapping 317                                                                                                                                                                                                            |                                                                                                                                 |

|                                                                                                                                                                                                                             | MCU FPGA programming model 286 memory availability 146                                                                          |

| I                                                                                                                                                                                                                           | memory blocks 135                                                                                                               |

| I/O banks                                                                                                                                                                                                                   | microprocessor programming 283                                                                                                  |

| standards 40                                                                                                                                                                                                                | Microsemi SoC Products Group                                                                                                    |

| standards compatibility 162                                                                                                                                                                                                 | email 321                                                                                                                       |

| I/O standards 77                                                                                                                                                                                                            | web-based technical support 321                                                                                                 |

| global macros 46                                                                                                                                                                                                            | website 321                                                                                                                     |

| single-ended 166                                                                                                                                                                                                            | WODONG 021                                                                                                                      |

| I/Os                                                                                                                                                                                                                        | 0                                                                                                                               |

| assigning technologies 198                                                                                                                                                                                                  | OTP 223                                                                                                                         |

| assignments defined in PDC file 193                                                                                                                                                                                         | output slew rate 175                                                                                                            |

| automatically assigning 202                                                                                                                                                                                                 | output siew rate 175                                                                                                            |

| behavior at power-up/-down 311                                                                                                                                                                                              | D                                                                                                                               |

| board-level considerations 181                                                                                                                                                                                              | P                                                                                                                               |

| buffer schematic cell 191                                                                                                                                                                                                   | PDC                                                                                                                             |

| cell architecture 207                                                                                                                                                                                                       | global promotion and demotion 51                                                                                                |

| configuration with SmartGen 188                                                                                                                                                                                             | place-and-route 193                                                                                                             |

| features 163, 164, 167                                                                                                                                                                                                      | PLL                                                                                                                             |

| global, naming 35                                                                                                                                                                                                           | behavior at brownout condition 315 configuration bits 90                                                                        |

| manually assigning technologies 198 nano standard 162                                                                                                                                                                       | corniguration bits 90 core specifications 84                                                                                    |

| register combining 174                                                                                                                                                                                                      | dynamic PLL configuration 87                                                                                                    |

| simplified buffer circuitry 165                                                                                                                                                                                             | functional description 85                                                                                                       |

| software support 177                                                                                                                                                                                                        | power supply decoupling scheme 112                                                                                              |

| software-controlled attributes 187                                                                                                                                                                                          | PLL block signals 68                                                                                                            |

| user I/O assignment flow chart 185                                                                                                                                                                                          | PLL macro block diagram 69                                                                                                      |

| user naming convention 178                                                                                                                                                                                                  | product support                                                                                                                 |

| wide range support 166                                                                                                                                                                                                      | customer service 321                                                                                                            |

|                                                                                                                                                                                                                             |                                                                                                                                 |