Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | -                                                                          |

| Number of I/O                  | 77                                                                         |

| Number of Gates                | 30000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-z1vq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ProASIC3 nano FPGA Fabric User's Guide

|    | IEEE 1532 (JTAG) Interface                                                   | 264 |

|----|------------------------------------------------------------------------------|-----|

|    | Security                                                                     | 264 |

|    | Security in ARM-Enabled Low Power Flash Devices                              | 265 |

|    | FlashROM and Programming Files                                               | 267 |

|    | Programming Solution                                                         | 268 |

|    | ISP Programming Header Information                                           | 269 |

|    | Board-Level Considerations                                                   | 271 |

|    | Conclusion                                                                   | 272 |

|    | Related Documents                                                            | 272 |

|    | List of Changes                                                              | 273 |

| 13 | Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming | 275 |

|    | Introduction                                                                 | 275 |

|    | Microsemi's Flash Families Support Voltage Switching Circuit                 | 276 |

|    | Circuit Description                                                          |     |

|    | Circuit Verification                                                         |     |

|    | DirectC                                                                      |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

| 14 | Microprocessor Programming of Microsemi's Low Power Flash Devices            | 283 |

|    | Introduction                                                                 |     |

|    | Microprocessor Programming Support in Flash Devices                          |     |

|    | Programming Algorithm                                                        |     |

|    | Implementation Overview                                                      |     |

|    | Hardware Requirement                                                         |     |

|    | Security                                                                     |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

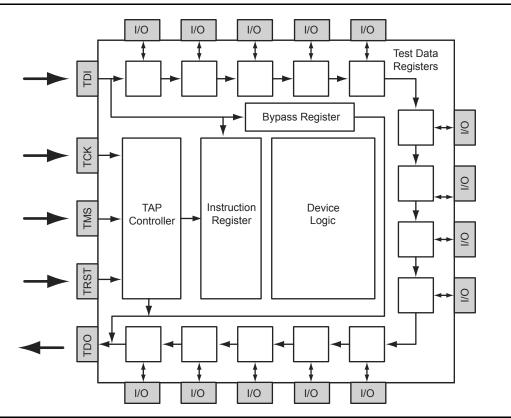

| 15 | Boundary Scan in Low Power Flash Devices                                     | 291 |

|    | Boundary Scan                                                                |     |

|    | TAP Controller State Machine                                                 |     |

|    | Microsemi's Flash Devices Support the JTAG Feature                           |     |

|    | Boundary Scan Support in Low Power Devices                                   |     |

|    | Boundary Scan Opcodes                                                        |     |

|    | Boundary Scan Chain                                                          |     |

|    | Board-Level Recommendations                                                  |     |

|    | Advanced Boundary Scan Register Settings                                     |     |

|    | List of Changes                                                              |     |

| 16 | UJTAG Applications in Microsemi's Low Power Flash Devices                    | 297 |

|    | Introduction                                                                 |     |

|    | UJTAG Support in Flash-Based Devices                                         |     |

|    | UJTAG Macro                                                                  |     |

|    |                                                                              |     |

|    | UJTAG Operation                                                              |     |

|    | Typical UJTAG Applications                                                   |     |

|    | Conclusion                                                                   |     |

|    | Related Documents                                                            |     |

|    | List of Changes                                                              | ასხ |

#### **Routing Architecture**

The routing structure of low power flash devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed, very-long-line resources; and the high-performance VersaNet networks.

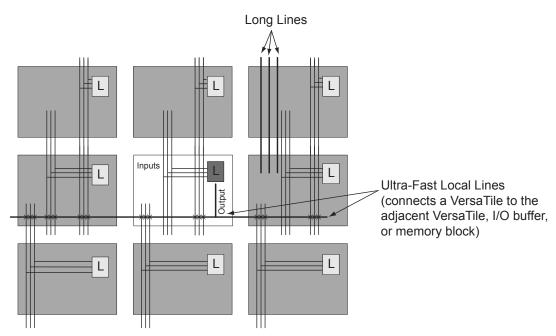

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 1-10). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaTile global network.

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire device (Figure 1-11 on page 19). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Routing software automatically inserts active buffers to limit loading effects.

The high-speed, very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length ±12 VersaTiles in the vertical direction and length ±16 in the horizontal direction from a given core VersaTile (Figure 1-12 on page 19). Very long lines in low power flash devices have been enhanced over those in previous ProASIC families. This provides a significant performance boost for long-reach signals.

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or internal logic. These nets are typically used to distribute clocks, resets, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input of every VersaTile. For more details on VersaNets, refer to the "Global Resources in Low Power Flash Devices" section on page 31.

Note: Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 1-10 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

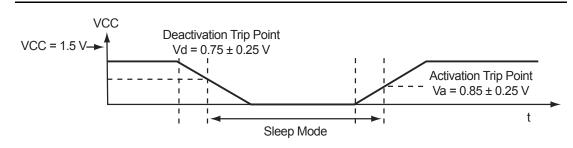

Figure 2-5 • Entering and Exiting Sleep Mode—Typical Timing Diagram

#### **Shutdown Mode**

For all ProASIC3/E and ProASIC3 nano devices, shutdown mode can be entered by turning off all power supplies when device functionality is not needed. Cold-sparing and hot-insertion features in ProASIC3 nano devices enable the device to be powered down without turning off the entire system. When power returns, the live at power-up feature enables immediate operation of the device.

#### Using Sleep Mode or Shutdown Mode in the System

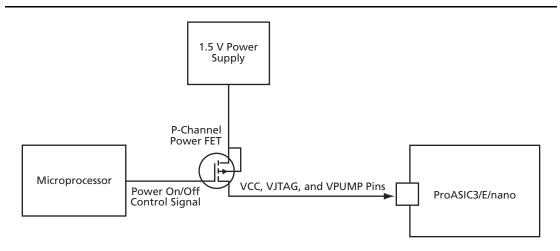

Depending on the power supply and components used in an application, there are many ways to turn the power supplies connected to the device on or off. For example, Figure 2-6 shows how a microprocessor is used to control a power FET. It is recommended that power FETs with low on resistance be used to perform the switching action.

Figure 2-6 • Controlling Power On/Off State Using Microprocessor and Power FET

Table 3-2 • Chip Global Pin Name

| I/O Type               | Beginning of I/O Name | Notes                                                        |

|------------------------|-----------------------|--------------------------------------------------------------|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |

|                        | GFA2/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |

|                        | GFB2/IOuxwByVz        |                                                              |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |

|                        | GFC2/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |

|                        | GCA2/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |

|                        | GCB2/IOuxwByVz        |                                                              |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a ch       |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |

|                        | GCC2/IOuxwByVz        |                                                              |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFA1/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFB1/IOuxwByVz        |                                                              |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFC1/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCA1/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCB1/IOuxwByVz        |                                                              |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCC1/IOuxwByVz        |                                                              |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

ProASIC3 nano FPGA Fabric User's Guide

You can control the maximum number of shared instances allowed for the legalization to take place using the Compile Option dialog box shown in Figure 3-17. Refer to Libero SoC / Designer online help for details on the Compile Option dialog box. A large number of shared instances most likely indicates a floorplanning problem that you should address.

Figure 3-17 • Shared Instances in the Compile Option Dialog Box

#### **Designer Flow for Global Assignment**

To achieve the desired result, pay special attention to global management during synthesis and place-and-route. The current Synplify tool does not insert more than six global buffers in the netlist by default. Thus, the default flow will not assign any signal to the quadrant global network. However, you can use attributes in Synplify and increase the default global macro assignment in the netlist. Designer v6.2 supports automatic quadrant global assignment, which was not available in Designer v6.1. Layout will make the choice to assign the correct signals to global. However, you can also utilize PDC and perform manual global assignment to overwrite any automatic assignment. The following step-by-step suggestions guide you in the layout of your design and help you improve timing in Designer:

- 1. Run Compile and check the Compile report. The Compile report has global information in the "Device Utilization" section that describes the number of chip and quadrant signals in the design. A "Net Report" section describes chip global nets, quadrant global nets, local clock nets, a list of nets listed by fanout, and net candidates for local clock assignment. Review this information. Note that YB or YC are counted as global only when they are used in isolation; if you use YB only and not GLB, this net is not shown in the global/quadrant nets report. Instead, it appears in the Global Utilization report.

- 2. If some signals have a very high fanout and are candidates for global promotion, promote those signals to global using the compile options or PDC commands. Figure 3-18 on page 54 shows the Globals Management section of the compile options. Select **Promote regular nets whose fanout is greater than** and enter a reasonable value for fanouts.

#### Global Resources in Low Power Flash Devices

| Date                              | Changes                                                                                                                                                                                                                                                                                                              | Page   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| v1.1<br>(March 2008)              | The "Global Architecture" section was updated to include the IGLOO PLUS family. The bullet was revised to include that the west CCC does not contain a PLL core in 15 k and 30 k devices. Instances of "A3P030 and AGL030 devices" were replaced with "15 k and 30 k gate devices."                                  | 31     |

| v1.1<br>(continued)               | Table 3-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                    | 32     |

|                                   | The "VersaNet Global Network Distribution" section, "Spine Architecture" section, the note in Figure 3-1 • Overview of VersaNet Global Network and Device Architecture, and the note in Figure 3-3 • Simplified VersaNet Global Network (60 k gates and above) were updated to include mention of 15 k gate devices. | 33, 34 |

|                                   | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to add the A3P015 device, and to revise the values for clock trees, globals/spines per tree, and globals/spines per device for the A3P030 and AGL030 devices.                                                                             | 41     |

|                                   | Table 3-5 • Globals/Spines/Rows for IGLOO PLUS Devices is new.                                                                                                                                                                                                                                                       | 42     |

|                                   | CLKBUF_LVCMOS12 was added to Table 3-9 • I/O Standards within CLKBUF.                                                                                                                                                                                                                                                | 47     |

|                                   | The "User's Guides" section was updated to include the three different I/O Structures chapters for ProASIC3 and IGLOO device families.                                                                                                                                                                               | 58     |

| v1.0<br>(January 2008)            | Figure 3-3 • Simplified VersaNet Global Network (60 k gates and above) was updated.                                                                                                                                                                                                                                  | 34     |

|                                   | The "Naming of Global I/Os" section was updated.                                                                                                                                                                                                                                                                     | 35     |

|                                   | The "Using Global Macros in Synplicity" section was updated.                                                                                                                                                                                                                                                         | 50     |

|                                   | The "Global Promotion and Demotion Using PDC" section was updated.                                                                                                                                                                                                                                                   | 51     |

|                                   | The "Designer Flow for Global Assignment" section was updated.                                                                                                                                                                                                                                                       | 53     |

|                                   | The "Simple Design Example" section was updated.                                                                                                                                                                                                                                                                     | 55     |

| 51900087-0/1.05<br>(January 2005) | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated.                                                                                                                                                                                                                                          | 41     |

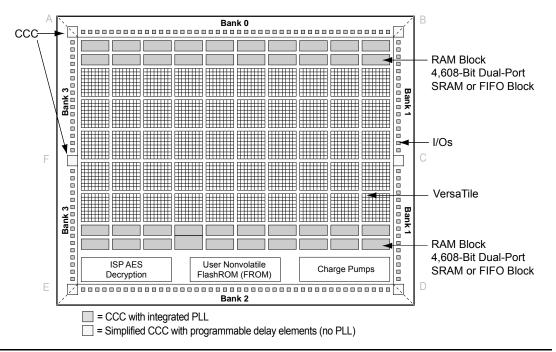

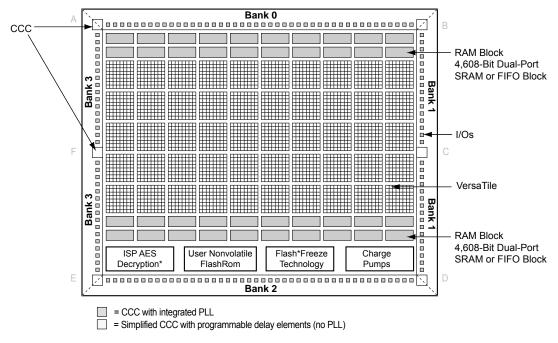

#### **Fusion CCC Locations**

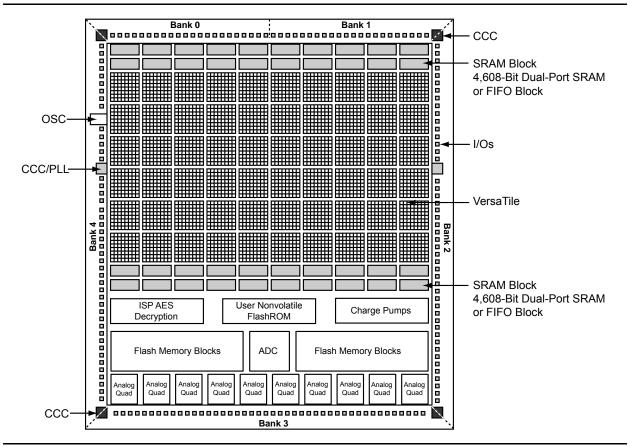

Fusion devices have six CCCs: one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-17 and Figure 4-18). The device can have one integrated PLL in the middle of the west side of the device or two integrated PLLs in the middle of the east and west sides of the device (middle right and middle left).

Figure 4-17 • CCC Locations in Fusion Family Devices (AFS090, AFS250, M1AFS250)

Figure 4-18 • CCC Locations in Fusion Family Devices (except AFS090, AFS250, M1AFS250)

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.4<br>(December 2008) | The "CCC Support in Microsemi's Flash Devices" section was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                                                                                                       | 63   |

|                         | Figure 4-2 • CCC Options: Global Buffers with No Programmable Delay was revised to add the CLKBIBUF macro.                                                                                                                                                                                                                                                                                                                | 64   |

|                         | The description of the reference clock was revised in Table 4-2 • Input and Output Description of the CLKDLY Macro.                                                                                                                                                                                                                                                                                                       | 65   |

|                         | Figure 4-7 • Clock Input Sources (30 k gates devices and below) is new. Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF_LVDS/LVPECL, and CLKINT (60 k gates devices and above) applies to 60 k gate devices and above.                                                                                                                                                                                          | 72   |

|                         | The "IGLOO and ProASIC3" section was updated to include information for IGLOO nano devices.                                                                                                                                                                                                                                                                                                                               | 73   |

|                         | A note regarding Fusion CCCs was added to Figure 4-9 • Illustration of Hardwired I/O (global input pins) Usage for IGLOO and ProASIC3 devices 60 k Gates and Larger and the name of the figure was changed from Figure 4-8 • Illustration of Hardwired I/O (global input pins) Usage. Figure 4-10 • Illustration of Hardwired I/O (global input pins) Usage for IGLOO and ProASIC3 devices 30 k Gates and Smaller is new. | 74   |

|                         | Table 4-5 • Number of CCCs by Device Size and Package was updated to include IGLOO nano and ProASIC3 nano devices. Entries were added to note differences for the CS81, CS121, and CS201 packages.                                                                                                                                                                                                                        | 78   |

|                         | The "Clock Conditioning Circuits without Integrated PLLs" section was rewritten.                                                                                                                                                                                                                                                                                                                                          | 79   |

|                         | The "IGLOO and ProASIC3 CCC Locations" section was updated for nano devices.                                                                                                                                                                                                                                                                                                                                              | 81   |

|                         | Figure 4-13 • CCC Locations in the 15 k and 30 k Gate Devices was deleted.                                                                                                                                                                                                                                                                                                                                                | 4-20 |

| v1.3<br>(October 2008)  | This document was updated to include Fusion and RT ProASIC3 device information. Please review the document very carefully.                                                                                                                                                                                                                                                                                                | N/A  |

|                         | The "CCC Support in Microsemi's Flash Devices" section was updated.                                                                                                                                                                                                                                                                                                                                                       | 63   |

|                         | In the "Global Buffer with Programmable Delay" section, the following sentence was changed from:  "In this case, the I/O must be placed in one of the dedicated global I/O locations."                                                                                                                                                                                                                                    | 64   |

|                         | To "In this case, the software will automatically place the dedicated global I/O in the appropriate locations."                                                                                                                                                                                                                                                                                                           |      |

|                         | Figure 4-4 • CCC Options: Global Buffers with PLL was updated to include OADIVRST and OADIVHALF.                                                                                                                                                                                                                                                                                                                          | 67   |

|                         | In Figure 4-6 • CCC with PLL Block "fixed delay" was changed to "programmable delay".                                                                                                                                                                                                                                                                                                                                     | 67   |

|                         | Table 4-3 • Input and Output Signals of the PLL Block was updated to include OADIVRST and OADIVHALF descriptions.                                                                                                                                                                                                                                                                                                         | 68   |

|                         | Table 4-8 • Configuration Bit Descriptions for the CCC Blocks was updated to include configuration bits 88 to 81. Note 2 is new. In addition, the description for bit <76:74> was updated.                                                                                                                                                                                                                                | 90   |

|                         | Table 4-16 • Fusion Dynamic CCC Clock Source Selection and Table 4-17 • Fusion Dynamic CCC NGMUX Configuration are new.                                                                                                                                                                                                                                                                                                   | 94   |

|                         | Table 4-18 • Fusion Dynamic CCC Division by Half Configuration and Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families are new.                                                                                                                                                                                                                                                               | 95   |

# 5 – FlashROM in Microsemi's Low Power Flash Devices

#### Introduction

The Fusion, IGLOO, and ProASIC3 families of low power flash-based devices have a dedicated nonvolatile FlashROM memory of 1,024 bits, which provides a unique feature in the FPGA market. The FlashROM can be read, modified, and written using the JTAG (or UJTAG) interface. It can be read but not modified from the FPGA core. Only low power flash devices contain on-chip user nonvolatile memory (NVM).

### **Architecture of User Nonvolatile FlashROM**

Low power flash devices have 1 kbit of user-accessible nonvolatile flash memory on-chip that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits (16 bytes) during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core. Figure 5-1 shows the FlashROM logical structure.

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports synchronous read. The address is latched on the rising edge of the clock, and the new output data is stable after the falling edge of the same clock cycle. For more information, refer to the timing diagrams in the DC and Switching Characteristics chapter of the appropriate datasheet. The FlashROM can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

| Byte Number in Bank        |   |    |    |    |    |    | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |   |   |

|----------------------------|---|----|----|----|----|----|----------------------|---|---|---|---|---|---|---|---|---|---|

|                            |   | 15 | 14 | 13 | 12 | 11 | 10                   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| of                         | 7 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| SB (                       | 6 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| 3 MSB<br>EAD)              | 5 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| —                          | 4 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| m<br>SR (                  | 3 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Number 3 MS<br>ADDR (READ) | 2 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Bank Number<br>ADDR (R     | 1 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Ä                          | 0 |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

Figure 5-1 • FlashROM Architecture

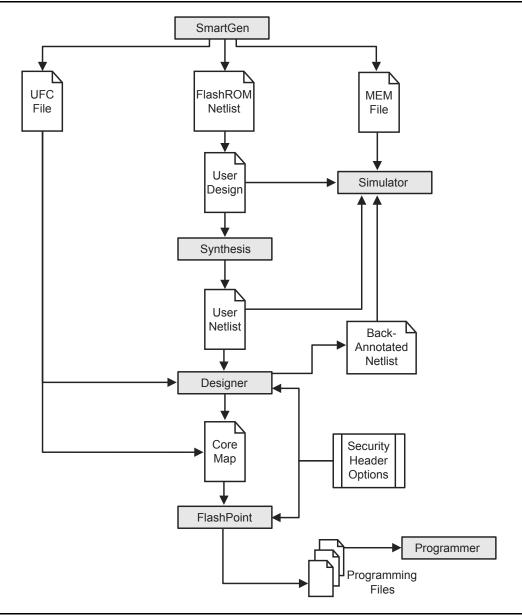

# FlashROM Design Flow

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

FlashROM in Microsemi's Low Power Flash Devices

#### Conclusion

The Fusion, IGLOO, and ProASIC3 families are the only FPGAs that offer on-chip FlashROM support. This document presents information on the FlashROM architecture, possible applications, programming, access through the JTAG and UJTAG interface, and integration into your design. In addition, the Libero tool set enables easy creation and modification of the FlashROM content.

The nonvolatile FlashROM block in the FPGA can be customized, enabling multiple applications.

Additionally, the security offered by the low power flash devices keeps both the contents of FlashROM and the FPGA design safe from system over-builders, system cloners, and IP thieves.

#### **Related Documents**

#### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/documents/FlashPro UG.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                   | Page     |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                 |          |  |  |  |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 5-1 • Flash-Based FPGAs.                                                                                                                         |          |  |  |  |  |  |

| v1.3<br>(October 2008)  | The "FlashROM Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                          | 118      |  |  |  |  |  |

|                         | Figure 5-2 • Fusion Device Architecture Overview (AFS600) was replaced. Figure 5-5 • Programming FlashROM Using AES was revised to change "Fusion" to "Flash Device."                                     | 119, 121 |  |  |  |  |  |

|                         | The FlashPoint User's Guide was removed from the "User's Guides" section, as its content is now part of the FlashPro User's Guide.                                                                        | 130      |  |  |  |  |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 5-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 118      |  |  |  |  |  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                         | N/A      |  |  |  |  |  |

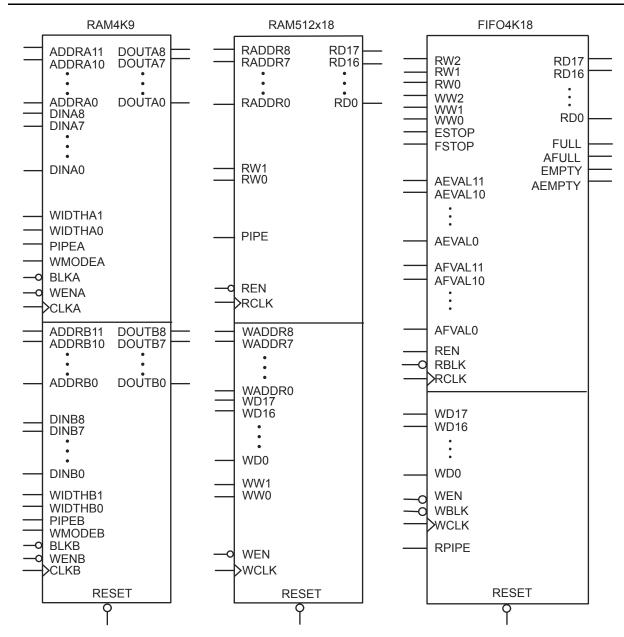

#### Notes:

- 1. Automotive ProASIC3 devices restrict RAM4K9 to a single port or to dual ports with the same clock 180° out of phase (inverted) between clock pins. In single-port mode, inputs to port B should be tied to ground to prevent errors during compile. This warning applies only to automotive ProASIC3 parts of certain revisions and earlier. Contact Technical Support at soc\_tech @microsemi.com for information on the revision number for a particular lot and date code.

- 2. For FIFO4K18, the same clock 180° out of phase (inverted) between clock pins should be used.

Figure 6-3 • Supported Basic RAM Macros

#### Table 7-8 • Hot-Swap Level 1

| Description                            | Cold-swap                                                                                                                                                                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                | No                                                                                                                                                                                         |

| Bus State                              | -                                                                                                                                                                                          |

| Card Ground Connection                 | -                                                                                                                                                                                          |

| Device Circuitry Connected to Bus Pins | -                                                                                                                                                                                          |

| Example Application                    | System and card with Microsemi FPGA chip are powered down, and the card is plugged into the system. Then the power supplies are turned on for the system but not for the FPGA on the card. |

| Compliance of nano Devices             | Compliant                                                                                                                                                                                  |

#### Table 7-9 • Hot-Swap Level 2

| Description                            | Hot-swap while reset                                                                                                                                          |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                | Yes                                                                                                                                                           |

| Bus State                              | Held in reset state                                                                                                                                           |

| Card Ground Connection                 | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                |

| Device Circuitry Connected to Bus Pins | -                                                                                                                                                             |

| Example Application                    | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable. |

| Compliance of nano Devices             | Compliant                                                                                                                                                     |

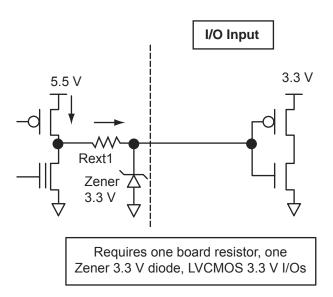

#### Solution 2

This solution requires one board resistor and one Zener 3.3 V diode, as demonstrated in Figure 7-6.

#### Solution 2

Figure 7-6 • Solution 2

#### Solution 3

This solution requires a bus switch on the board, as demonstrated in Figure 7-7.

# Solution 3 I/O Input 3.3 V Switch IDTQS32X23 5.5 V Requires a bus switch on the board, LVTTL/LVCMOS 3.3 V I/Os.

Figure 7-7 • Solution 3

Figure 11-3 • Block Representation of the AES Decryption Core in a Fusion AFS600 FPGA

# **Security Features**

IGLOO and ProASIC3 devices have two entities inside: FlashROM and the FPGA core fabric. Fusion devices contain three entities: FlashROM, FBs, and the FPGA core fabric. The parts can be programmed or updated independently with a STAPL programming file. The programming files can be AES-encrypted or plaintext. This allows maximum flexibility in providing security to the entire device. Refer to the "Programming Flash Devices" section on page 221 for information on the FlashROM structure.

Unlike SRAM-based FPGA devices, which require a separate boot PROM to store programming data, low power flash devices are nonvolatile, and the secured configuration data is stored in on-chip flash cells that are part of the FPGA fabric. Once programmed, this data is an inherent part of the FPGA array and does not need to be loaded at system power-up. SRAM-based FPGAs load the configuration bitstream upon power-up; therefore, the configuration is exposed and can be read easily.

The built-in FPGA core, FBs, and FlashROM support programming files encrypted with the 128-bit AES (FIPS-192) block ciphers. The AES key is stored in dedicated, on-chip flash memory and can be programmed before the device is shipped to other parties (allowing secure remote field updates).

## Security in ARM-Enabled Low Power Flash Devices

There are slight differences between the regular flash devices and the ARM<sup>®</sup>-enabled flash devices, which have the M1 and M7 prefix.

The AES key is used by Microsemi and preprogrammed into the device to protect the ARM IP. As a result, the design is encrypted along with the ARM IP, according to the details below.

#### **Programming File Header Definition**

In each STAPL programming file generated, there will be information about how the AES key and FlashLock Pass Key are configured. Table 11-8 shows the header definitions in STAPL programming files for different security levels.

Table 11-8 • STAPL Programming File Header Definitions by Security Level

| Security Level                                                  | STAPL File Header Definition          |  |  |  |  |  |

|-----------------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| No security (no FlashLock Pass Key or AES key)                  | NOTE "SECURITY" "Disable";            |  |  |  |  |  |

| FlashLock Pass Key with no AES key                              | NOTE "SECURITY" "KEYED ";             |  |  |  |  |  |

| FlashLock Pass Key with AES key                                 | NOTE "SECURITY" "KEYED ENCRYPT ";     |  |  |  |  |  |

| Permanent Security Settings option enabled                      | NOTE "SECURITY" "PERMLOCK ENCRYPT ";  |  |  |  |  |  |

| AES-encrypted FPGA array (for programming updates)              | NOTE "SECURITY" "ENCRYPT CORE ";      |  |  |  |  |  |

| AES-encrypted FlashROM (for programming updates)                | NOTE "SECURITY" "ENCRYPT FROM ";      |  |  |  |  |  |

| AES-encrypted FPGA array and FlashROM (for programming updates) | NOTE "SECURITY" "ENCRYPT FROM CORE "; |  |  |  |  |  |

#### Example File Headers

#### STAPL Files Generated with FlashLock Key and AES Key Containing Key Information

- FlashLock Key / AES key indicated in STAPL file header definition

- · Intended ONLY for secured/trusted environment programming applications

```

_____

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EDB9";

NOTE "SAVE_DATA" "FRomStream";

NOTE "SECURITY" "KEYED ENCRYPT ";

NOTE "ALG_VERSION" "1";

NOTE "MAX FREO" "20000000";

NOTE "SILSIG" "$00000000";

NOTE "PASS_KEY" "$00123456789012345678901234567890";

NOTE "AES_KEY" "$ABCDEFABCDEFABCDEFABCDEFABCDEFAB";

______

```

# **Related Documents**

#### **User's Guides**

FlashPro User's Guide http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                    | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                  | N/A  |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-Enabled Low Power Flash Devices", since M7-enabled devices are no longer supported.                                                | 238  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 11-1 • Flash-Based FPGAs.                                                                                                                         | 236  |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                           | 236  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 11-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 236  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                      | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                | 236  |

Boundary Scan in Low Power Flash Devices

# Microsemi's Flash Devices Support the JTAG Feature

The flash-based FPGAs listed in Table 15-1 support the JTAG feature and the functions described in this document.

#### Table 15-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                                  |  |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                                            |  |

|          | IGLO0e               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                                        |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                                          |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                                   |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                                      |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                                     |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                                          |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                                        |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                                  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                                        |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                                         |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC <sup>®</sup> 3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 15-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 15-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Figure 15-2 • Boundary Scan Chain

# **Board-Level Recommendations**

Table 15-3 gives pull-down recommendations for the TRST and TCK pins.

Table 15-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance*          |

|----------------|------------------------------|

| VJTAG at 3.3 V | 200 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 2.5 V | 200 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.5 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.2 V | TBD                          |

Note: Equivalent parallel resistance if more than one device is on JTAG chain (Figure 15-3)