Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 77                                                                        |

| Number of Gates                | 30000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-z2vq100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 17 | Power-Up/-Down Behavior of Low Power Flash Devices | . 307 |

|----|----------------------------------------------------|-------|

|    | Introduction                                       | 307   |

|    | Flash Devices Support Power-Up Behavior            | 308   |

|    | Power-Up/-Down Sequence and Transient Current      |       |

|    | I/O Behavior at Power-Up/-Down                     | 311   |

|    | Cold-Sparing                                       | 316   |

|    | Hot-Swapping                                       |       |

|    | Conclusion                                         | 317   |

|    | Related Documents                                  | 318   |

|    | List of Changes                                    | 318   |

| Α  | Summary of Changes                                 | . 319 |

|    | History of Revision to Chapters                    |       |

| В  | Product Support                                    | . 321 |

|    | Customer Service                                   | 321   |

|    | Customer Technical Support Center                  | 32    |

|    | Technical Support                                  |       |

|    | Website                                            | 32′   |

|    | Contacting the Customer Technical Support Center   | 32′   |

|    | ITAR Technical Support                             |       |

|    | Indov                                              | 300   |

#### Global Resources in Low Power Flash Devices

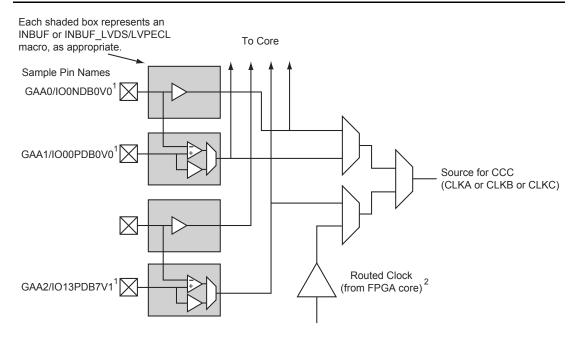

Figure 3-5 shows more detailed global input connections. It shows the global input pins connection to the northwest quadrant global networks. Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- · The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Note: Differential inputs are not supported for IGLOO nano or ProASIC3 nano devices.

Figure 3-5 • Global I/O Overview

## **Clock Aggregation Architecture**

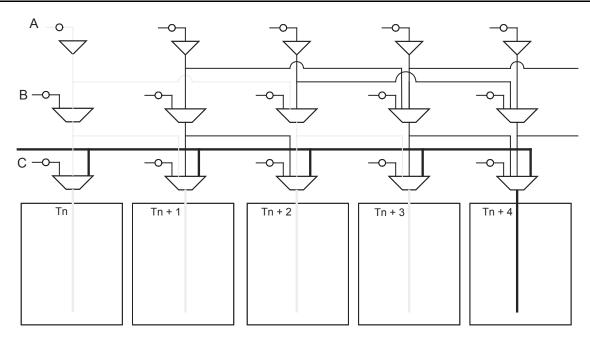

This clock aggregation feature allows a balanced clock tree, which improves clock skew. The physical regions for clock aggregation are defined from left to right and shift by one spine. For chip global networks, there are three types of clock aggregation available, as shown in Figure 3-10:

- Long lines that can drive up to four adjacent spines (A)

- · Long lines that can drive up to two adjacent spines (B)

- · Long lines that can drive one spine (C)

There are three types of clock aggregation available for the quadrant spines, as shown in Figure 3-10:

- I/Os or local resources that can drive up to four adjacent spines

- I/Os or local resources that can drive up to two adjacent spines

- I/Os or local resources that can drive one spine

As an example, A3PE600 and AFS600 devices have twelve spine locations: T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, and B6. Table 3-7 shows the clock aggregation you can have in A3PE600 and AFS600.

Figure 3-10 • Four Spines Aggregation

Table 3-7 • Spine Aggregation in A3PE600 or AFS600

| Clock Aggregation | Spine                                                                |  |

|-------------------|----------------------------------------------------------------------|--|

| 1 spine           | T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, B6                       |  |

| 2 spines          | T1:T2, T2:T3, T3:T4, T4:T5, T5:T6, B1:B2, B2:B3, B3:B4, B4:B5, B5:B6 |  |

| 4 spines          | B1:B4, B2:B5, B3:B6, T1:T4, T2:T5, T3:T6                             |  |

The clock aggregation for the quadrant spines can cross over from the left to right quadrant, but not from top to bottom. The quadrant spine assignment T1:T4 is legal, but the quadrant spine assignment T1:B1 is not legal. Note that this clock aggregation is hardwired. You can always assign signals to spine T1 and B2 by instantiating a buffer, but this may add skew in the signal.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **Software Configuration**

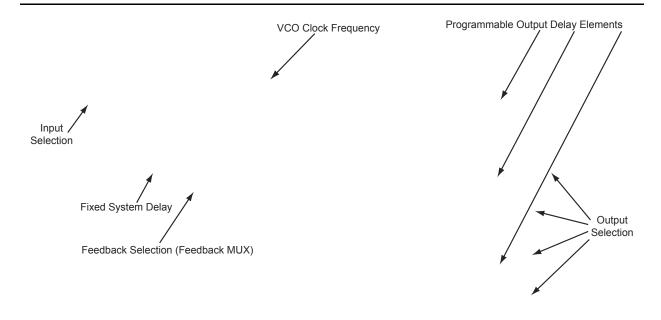

SmartGen automatically generates the desired CCC functional block by configuring the control bits, and allows the user to select two CCC modes: Static PLL and Delayed Clock (CLKDLY).

#### Static PLL Configuration

The newly implemented Visual PLL Configuration Wizard feature provides the user a quick and easy way to configure the PLL with the desired settings (Figure 4-23). The user can invoke SmartGen to set the parameters and generate the netlist file with the appropriate flash configuration bits set for the CCCs. As mentioned in "PLL Macro Block Diagram" on page 69, the input reference clock CLKA can be configured to be driven by Hardwired I/O, External I/O, or Core Logic. The user enters the desired settings for all the parameters (output frequency, output selection, output phase adjustment, clock delay, feedback delay, and system delay). Notice that the actual values (divider values, output frequency, delay values, and phase) are shown to aid the user in reaching the desired design frequency in real time. These values are typical-case data. Best- and worst-case data can be observed through static timing analysis in SmartTime within Designer.

For dynamic configuration, the CCC parameters are defined using either the external JTAG port or an internally defined serial interface via the built-in dynamic shift register. This feature provides the ability to compensate for changes in the external environment.

Figure 4-23 • Visual PLL Configuration Wizard

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **Dynamic PLL Configuration**

To generate a dynamically reconfigurable CCC, the user should select **Dynamic CCC** in the configuration section of the SmartGen GUI (Figure 4-26). This will generate both the CCC core and the configuration shift register / control bit MUX.

#### Figure 4-26 • SmartGen GUI

Even if dynamic configuration is selected in SmartGen, the user must still specify the static configuration data for the CCC (Figure 4-27). The specified static configuration is used whenever the MODE signal is set to LOW and the CCC is required to function in the static mode. The static configuration data can be used as the default behavior of the CCC where required.

Figure 4-27 • Dynamic CCC Configuration in SmartGen

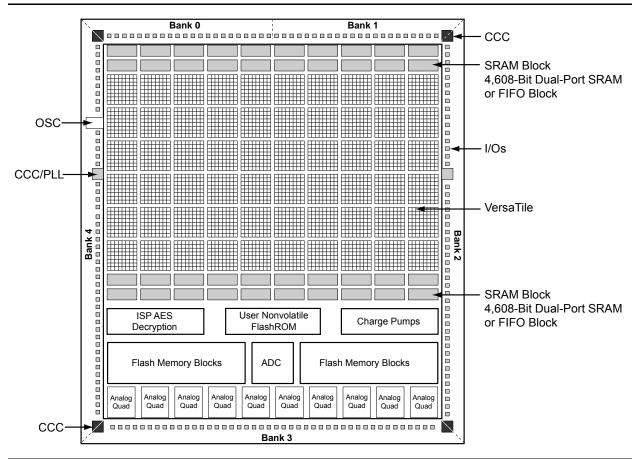

Figure 5-2 • Fusion Device Architecture Overview (AFS600)

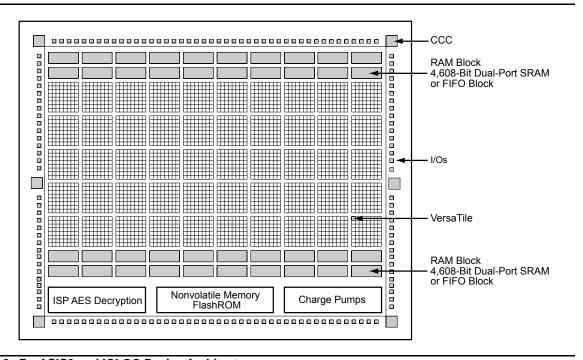

Figure 5-3 • ProASIC3 and IGLOO Device Architecture

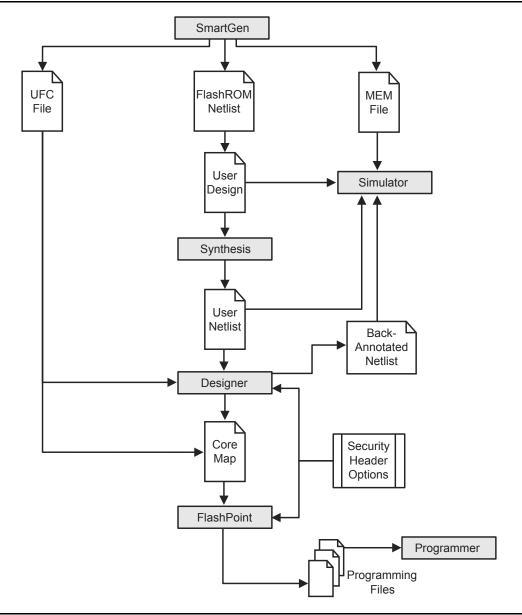

## FlashROM Design Flow

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

#### Notes:

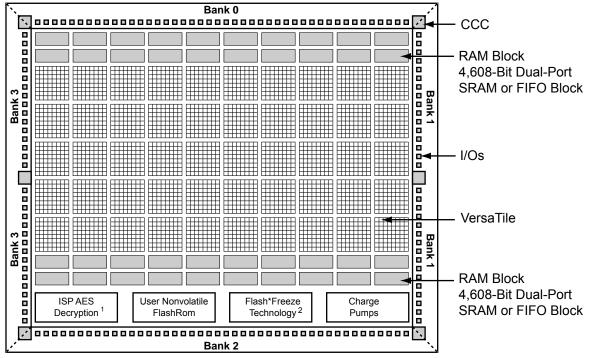

- 1. AES decryption not supported in 30 k gate devices and smaller.

- 2. Flash\*Freeze is supported in all IGLOO devices and the ProASIC3L devices.

Figure 6-1 • IGLOO and ProASIC3 Device Architecture Overview

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## Initializing the RAM/FIFO

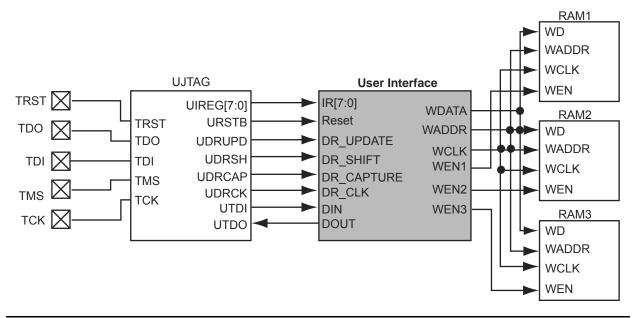

The SRAM blocks can be initialized with data to use as a lookup table (LUT). Data initialization can be accomplished either by loading the data through the design logic or through the UJTAG interface. The UJTAG macro is used to allow access from the JTAG port to the internal logic in the device. By sending the appropriate initialization string to the JTAG Test Access Port (TAP) Controller, the designer can put the JTAG circuitry into a mode that allows the user to shift data into the array logic through the JTAG port using the UJTAG macro. For a more detailed explanation of the UJTAG macro, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 117.

A user interface is required to receive the user command, initialization data, and clock from the UJTAG macro. The interface must synchronize and load the data into the correct RAM block of the design. The main outputs of the user interface block are the following:

- Memory block chip select: Selects a memory block for initialization. The chip selects signals for each memory block that can be generated from different user-defined pockets or simple logic, such as a ring counter (see below).

- · Memory block write address: Identifies the address of the memory cell that needs to be initialized.

- Memory block write data: The interface block receives the data serially from the UTDI port of the UJTAG macro and loads it in parallel into the write data ports of the memory blocks.

- Memory block write clock: Drives the WCLK of the memory block and synchronizes the write data, write address, and chip select signals.

Figure 6-8 shows the user interface between UJTAG and the memory blocks.

Figure 6-8 • Interfacing TAP Ports and SRAM Blocks

An important component of the interface between the UJTAG macro and the RAM blocks is a serial-in/parallel-out shift register. The width of the shift register should equal the data width of the RAM blocks. The RAM data arrives serially from the UTDI output of the UJTAG macro. The data must be shifted into a shift register clocked by the JTAG clock (provided at the UDRCK output of the UJTAG macro).

Then, after the shift register is fully loaded, the data must be transferred to the write data port of the RAM block. To synchronize the loading of the write data with the write address and write clock, the output of the shift register can be pipelined before driving the RAM block.

The write address can be generated in different ways. It can be imported through the TAP using a different instruction opcode and another shift register, or generated internally using a simple counter. Using a counter to generate the address bits and sweep through the address range of the RAM blocks is

## Low Power Flash Device I/O Support

The low power flash families listed in Table 7-1 support I/Os and the functions described in this document.

#### Table 7-1 • Flash-Based FPGAs

| Series   | Family*       | Description                                                    |

|----------|---------------|----------------------------------------------------------------|

| IGLOO    | IGLOO nano    | Lowest power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |

| ProASIC3 | ProASIC3 nano | Lowest cost 1.5 V FPGAs with balanced performance              |

Note: \*The device name links to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

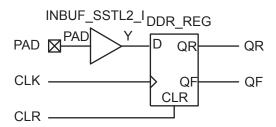

## **DDR Input Register**

Figure 9-5 • DDR Input Register (SSTL2 Class I)

The corresponding structural representations, as generated by SmartGen, are shown below:

#### Verilog

end DEF\_ARCH;

```

module DDR_InBuf_SSTL2_I(PAD,CLR,CLK,QR,QF);

input PAD, CLR, CLK;

output QR, QF;

wire Y;

INBUF_SSTL2_I INBUF_SSTL2_I_0_inst(.PAD(PAD),.Y(Y));

DDR_REG_DDR_REG_O_inst(.D(Y),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

endmodule

VHDL

library ieee;

use ieee.std_logic_1164.all;

--The correct library will be inserted automatically by SmartGen

library proasic3; use proasic3.all;

--library fusion; use fusion.all;

--library igloo; use igloo.all;

entity DDR_InBuf_SSTL2_I is

port(PAD, CLR, CLK : in std_logic; QR, QF : out std_logic) ;

end DDR_InBuf_SSTL2_I;

architecture DEF_ARCH of DDR_InBuf_SSTL2_I is

component INBUF_SSTL2_I

port(PAD : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

signal Y : std_logic ;

begin

INBUF_SSTL2_I_0_inst : INBUF_SSTL2_I

port map(PAD => PAD, Y => Y);

DDR_REG_0_inst : DDR_REG

\label{eq:clk_port_map} \texttt{port_map}(\texttt{D} => \texttt{Y}, \texttt{CLK} => \texttt{CLK}, \texttt{CLR} => \texttt{CLR}, \texttt{QR} => \texttt{QR}, \texttt{QF} => \texttt{QF});

```

## **Related Documents**

Below is a list of related documents, their location on the Microsemi SoC Products Group website, and a brief summary of each document.

#### **Application Notes**

Programming Antifuse Devices

http://www.microsemi.com/soc/documents/AntifuseProgram\_AN.pdf *Implementation of Security in Actel's ProASIC and ProASICPLUS Flash-Based FPGAs*http://www.microsemi.com/soc/documents/Flash Security AN.pdf

#### **User's Guides**

#### FlashPro Programmers

FlashPro4, <sup>1</sup> FlashPro3, FlashPro Lite, and FlashPro<sup>2</sup>

http://www.microsemi.com/soc/products/hardware/program\_debug/flashpro/default.aspx

FlashPro User's Guide

http://www.microsemi.com/soc/documents/FlashPro UG.pdf

The FlashPro User's Guide includes hardware and software setup, self-test instructions, use instructions, and a troubleshooting / error message guide.

#### Silicon Sculptor 3 and Silicon Sculptor II

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/default.aspx

#### **Other Documents**

http://www.microsemi.com/soc/products/solutions/security/default.aspx#flashlock

The security resource center describes security in Microsemi Flash FPGAs.

Quality and Reliability Guide

http://www.microsemi.com/soc/documents/RelGuide.pdf

Programming and Functional Failure Guidelines

http://www.microsemi.com/soc/documents/FA Policies Guidelines 5-06-00002.pdf

<sup>.</sup> FlashPro4 replaced FlashPro3 in Q1 2010.

<sup>2.</sup> FlashPro is no longer available.

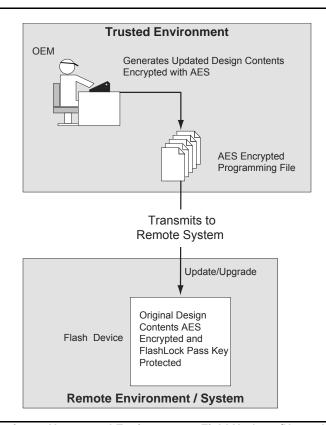

#### Application 3: Nontrusted Environment—Field Updates/Upgrades

Programming or reprogramming of devices may occur at remote locations. Reconfiguration of devices in consumer products/equipment through public networks is one example. Typically, the remote system is already programmed with particular design contents. When design update (FPGA array contents update) and/or data upgrade (FlashROM and/or FB contents upgrade) is necessary, an updated programming file with AES encryption can be generated, sent across public networks, and transmitted to the remote system. Reprogramming can then be done using this AES-encrypted programming file, providing easy and secure field upgrades. Low power flash devices support this secure ISP using AES. The detailed flow for this application is shown in Figure 11-8. Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide for more information.

To prepare devices for this scenario, the user can initially generate a programming file with the available security setting options. This programming file is programmed into the devices before shipment. During the programming file generation step, the user has the option of making the security settings permanent or not. In situations where no changes to the security settings are necessary, the user can select this feature in the software to generate the programming file with permanent security settings. Microsemi recommends that the programming file use encryption with an AES key, especially when ISP is done via public domain.

For example, if the designer wants to use an AES key for the FPGA array and the FlashROM, **Permanent** needs to be chosen for this setting. At first, the user chooses the options to use an AES key for the FPGA array and the FlashROM, and then chooses **Permanently lock the security settings**. A unique AES key is chosen. Once this programming file is generated and programmed to the devices, the AES key is permanently stored in the on-chip memory, where it is secured safely. The devices are sent to distant locations for the intended application. When an update is needed, a new programming file must be generated. The programming file must use the same AES key for encryption; otherwise, the authentication will fail and the file will not be programmed in the device.

Figure 11-8 • Application 3: Nontrusted Environment—Field Updates/Upgrades

ProASIC3 nano FPGA Fabric User's Guide

Table 11-5 • FlashLock Security Options for Fusion

| Security Option       | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / no FlashLock | -             | _              | _            | -   |

| FlashLock             | ✓             | ✓              | ✓            | ✓   |

| AES and FlashLock     | ✓             | ✓              | ✓            | ✓   |

For this scenario, generate the programming file as follows:

1. Select only the **Security settings** option, as indicated in Figure 11-14 and Figure 11-15 on page 252. Click **Next**.

Figure 11-14 • Programming IGLOO and ProASIC3 Security Settings Only

## **Microprocessor Programming Support in Flash Devices**

The flash-based FPGAs listed in Table 14-1 support programming with a microprocessor and the functions described in this document.

Table 14-1 • Flash-Based FPGAs

| Series      | Family*              | Description                                                                                                                                                                                    |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO IGLOO |                      | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|             |                      | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|             | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|             | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3    | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|             | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|             | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|             | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|             | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|             | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|             | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion      | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

#### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Microprocessor Programming of Microsemi's Low Power Flash Devices

#### Remote Upgrade via TCP/IP

Transmission Control Protocol (TCP) provides a reliable bitstream transfer service between two endpoints on a network. TCP depends on Internet Protocol (IP) to move packets around the network on its behalf. TCP protects against data loss, data corruption, packet reordering, and data duplication by adding checksums and sequence numbers to transmitted data and, on the receiving side, sending back packets and acknowledging the receipt of data.

The system containing the low power flash device can be assigned an IP address when deployed in the field. When the device requires an update (core or FlashROM), the programming instructions along with the new programming data (AES-encrypted cipher text) can be sent over the Internet to the target system via the TCP/IP protocol. Once the MCU receives the instruction and data, it can proceed with the FPGA update. Low power flash devices support Message Authentication Code (MAC), which can be used to validate data for the target device. More details are given in the "Message Authentication Code (MAC) Validation/Authentication" section.

## **Hardware Requirement**

To facilitate the programming of the low power flash families, the system must have a microprocessor (with access to the device JTAG pins) to process the programming algorithm, memory to store the programming algorithm, programming data, and the necessary programming voltage. Refer to the relevant datasheet for programming voltages.

## **Security**

#### **Encrypted Programming**

As an additional security measure, the devices are equipped with AES decryption. AES works in two steps. The first step is to program a key into the devices in a secure or trusted programming center (such as Microsemi SoC Products Group In-House Programming (IHP) center). The second step is to encrypt any programming files with the same encryption key. The encrypted programming file will only work with the devices that have the same key. The AES used in the low power flash families is the 128-bit AES decryption engine (Rijndael algorithm).

## Message Authentication Code (MAC) Validation/Authentication

As part of the AES decryption flow, the devices are equipped with a MAC validation/authentication system. MAC is an authentication tag, also called a checksum, derived by applying an on-chip authentication scheme to a STAPL file as it is loaded into the FPGA. MACs are computed and verified with the same key so they can only be verified by the intended recipient. When the MCU system receives the AES-encrypted programming data (cipher text), it can validate the data by loading it into the FPGA and performing a MAC verification prior to loading the data, via a second programming pass, into the FPGA core cells. This prevents erroneous or corrupt data from getting into the FPGA.

Low power flash devices with AES and MAC are superior to devices with only DES or 3DES encryption. Because the MAC verifies the correctness of the data, the FPGA is protected from erroneous loading of invalid programming data that could damage a device (Figure 14-5 on page 289).

The AES with MAC enables field updates over public networks without fear of having the design stolen. An encrypted programming file can only work on devices with the correct key, rendering any stolen files

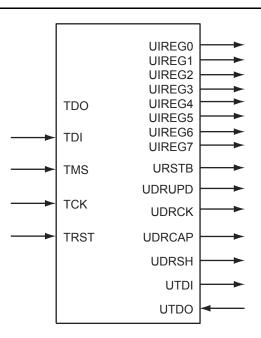

## **UJTAG Macro**

The UJTAG tiles can be instantiated in a design using the UJTAG macro from the Fusion, IGLOO, or ProASIC3 macro library. Note that "UJTAG" is a reserved name and cannot be used for any other user-defined blocks. A block symbol of the UJTAG tile macro is presented in Figure 16-2. In this figure, the ports on the left side of the block are connected to the JTAG TAP Controller, and the right-side ports are accessible by the FPGA core VersaTiles. The TDI, TMS, TDO, TCK, and TRST ports of UJTAG are only provided for design simulation purposes and should be treated as external signals in the design netlist. However, these ports must NOT be connected to any I/O buffer in the netlist. Figure 16-3 on page 300 illustrates the correct connection of the UJTAG macro to the user design netlist. Microsemi Designer software will automatically connect these ports to the TAP during place-and-route. Table 16-2 gives the port descriptions for the rest of the UJTAG ports:

Table 16-2 • UJTAG Port Descriptions

| Port        | Description                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UIREG [7:0] | This 8-bit bus carries the contents of the JTAG Instruction Register of each device. Instruction Register values 16 to 127 are not reserved and can be employed as user-defined instructions.                                                                                         |

| URSTB       | URSTB is an active-low signal and will be asserted when the TAP Controller is in Test-Logic-Reset mode. URSTB is asserted at power-up, and a power-on reset signal resets the TAP Controller. URSTB will stay asserted until an external TAP access changes the TAP Controller state. |

| UTDI        | This port is directly connected to the TAP's TDI signal.                                                                                                                                                                                                                              |

| UTDO        | This port is the user TDO output. Inputs to the UTDO port are sent to the TAP TDO output MUX when the IR address is in user range.                                                                                                                                                    |

| UDRSH       | Active-high signal enabled in the ShiftDR TAP state                                                                                                                                                                                                                                   |

| UDRCAP      | Active-high signal enabled in the CaptureDR TAP state                                                                                                                                                                                                                                 |

| UDRCK       | This port is directly connected to the TAP's TCK signal.                                                                                                                                                                                                                              |

| UDRUPD      | Active-high signal enabled in the UpdateDR TAP state                                                                                                                                                                                                                                  |

Figure 16-2 • UJTAG Tile Block Symbol

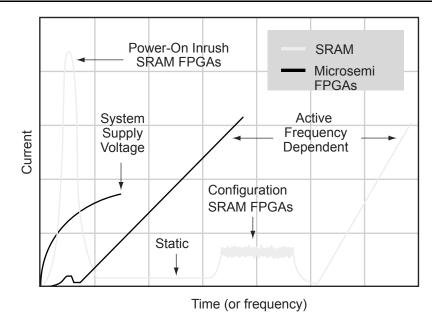

Figure 17-1 • Types of Power Consumption in SRAM FPGAs and Microsemi Nonvolatile FPGAs

#### **Transient Current on VCC**

The characterization of the transient current on VCC is performed on nearly all devices within the IGLOO, ProASIC3L, and ProASIC3 families. A sample size of five units is used from each device family member. All the device I/Os are internally pulled down while the transient current measurements are performed. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCC, when the power supply is powered at ramp-rates ranging from 15 V/ms to 0.15 V/ms, does not exceed the maximum standby current specified in the device datasheets. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAS* datasheet for more information.

Similarly, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCC. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCC is typically in the range of 1–5 mA.

#### **Transient Current on VCCI**

The characterization of the transient current on VCCI is performed on devices within the IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, ProASIC3 nano, and ProASIC3L groups of devices, similarly to VCC transient current measurements. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCCI, when the power supply is powered at ramp-rates ranging from 33 V/ms to 0.33 V/ms, does not exceed the maximum standby current specified in the device datasheet. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAS* datasheet for more information.

Similarly, IGLOO, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCCI. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCCI is typically in the range of 1–2 mA.

# Microsemi.

# Index

| Numerics                                | PLL and CLKDLY macros 73                     |

|-----------------------------------------|----------------------------------------------|

| 5 V input and output tolerance 171      | clocks                                       |

| p c c c c q c c c c c c c c c c c c c c | delay adjustment 86                          |

| Α                                       | detailed usage information 104               |

| AES encryption 239                      | multipliers and dividers 85                  |

| architecture 131                        | phase adjustment 87                          |

| four I/O banks 13                       | physical constraints for quadrant clocks 108 |

| global 31                               | SmartGen settings 105                        |

| IGLOO 12                                | static timing analysis 107                   |

| IGLOO 12<br>IGLOO nano 11               | cold-sparing 170, 316                        |

| IGLOO PLUS 13                           | compiling 195                                |

| IGLOOP 14                               | report 195                                   |

| ProASIC3 nano 11                        | contacting Microsemi SoC Products Group      |

| ProASIC3E 14                            | customer service 321                         |

| routing 18                              | email 321                                    |

| spine 41                                | web-based technical support 321              |

| SRAM and FIFO 135                       | customer service 321                         |

| architecture overview 11                |                                              |

| array coordinates 16                    | D                                            |

| •                                       | DDR                                          |

| В                                       | architecture 205                             |

| boundary scan 291                       | design example 216                           |

| board-level recommendations 294         | I/O options 207                              |

| chain 293                               | input/output support 209                     |

| opcodes 293                             | instantiating registers 210                  |

| brownout voltage 315                    | design example 55                            |

| 3                                       | design recommendations 46                    |

| C                                       | device architecture 131                      |

| CCC 82                                  | DirectC 280                                  |

| board-level considerations 112          | DirectC code 285                             |

| cascading 109                           | dual-tile designs 160                        |

| Fusion locations 83                     | F                                            |

| global resources 62                     | E                                            |

| hardwired I/O clock input 108           | efficient long-line resources 19             |

| IGLOO locations 81                      | encryption 289                               |

| IGLOOe locations 82                     | ESD protection 171                           |

| locations 80                            |                                              |

| naming conventions 179                  | F                                            |

| overview 61                             | FIFO                                         |

| ProASIC3 locations 81                   | features 141                                 |

| ProASIC3E locations 82                  | initializing 148                             |

| programming 62                          | memory block consumption 147                 |

| software configuration 96               | software support 154                         |

| with integrated PLLs 79                 | usage 144                                    |

| without integrated PLLs 79              | flash switch for programming 9               |

| chip global aggregation 43              | FlashLock                                    |

| CLKDLY macro 65                         | IGLOO and ProASIC devices 241                |

| clock aggregation 44                    | permanent 241                                |

| clock macros 46                         | FlashROM                                     |

| clock sources                           | access using JTAG port 123                   |

| core logic 76                           | architecture 267                             |

## *Microsemi*

Index

| architecture of user nonvolatile 117 configuration 120 custom serialization 129 design flow 124 generation 125 programming and accessing 122 programming file 127 programming files 267 SmartGen 126 FlashROM read-back 305 | ISP 223, 224 architecture 261 board-level considerations 271 circuit 277 microprocessor 283  J JTAG 1532 261 JTAG interface 285 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| G                                                                                                                                                                                                                           | L                                                                                                                               |

| global architecture 31                                                                                                                                                                                                      | layout                                                                                                                          |

| global buffers                                                                                                                                                                                                              | device-specific 78                                                                                                              |

| no programmable delays 64                                                                                                                                                                                                   | LTC3025 linear voltage regulator 277                                                                                            |

| with PLL function 67                                                                                                                                                                                                        |                                                                                                                                 |

| with programmable delays 64                                                                                                                                                                                                 | M                                                                                                                               |

| global macros                                                                                                                                                                                                               | MAC validation/authentication 288                                                                                               |

| Synplicity 50                                                                                                                                                                                                               | macros                                                                                                                          |

| globals                                                                                                                                                                                                                     | CLKBUF 77                                                                                                                       |

| designer flow 53                                                                                                                                                                                                            | CLKBUF_LVDS/LVPECL 77                                                                                                           |

| networks 58                                                                                                                                                                                                                 | CLKDLY 65, 73                                                                                                                   |

| spines and rows 41                                                                                                                                                                                                          | FIFO4KX18 141                                                                                                                   |

| ·                                                                                                                                                                                                                           | PLL 73                                                                                                                          |

| Н                                                                                                                                                                                                                           | PLL macro signal descriptions 68                                                                                                |

| HLD code                                                                                                                                                                                                                    | RAM4K9 137                                                                                                                      |

| instantiating 192                                                                                                                                                                                                           | RAM512X18 139                                                                                                                   |

| hot-swap 167                                                                                                                                                                                                                | supported basic RAM macros 136<br>UJTAG 299                                                                                     |

| hot-swapping 317                                                                                                                                                                                                            |                                                                                                                                 |

|                                                                                                                                                                                                                             | MCU FPGA programming model 286 memory availability 146                                                                          |

| I                                                                                                                                                                                                                           | memory blocks 135                                                                                                               |

| I/O banks                                                                                                                                                                                                                   | microprocessor programming 283                                                                                                  |

| standards 40                                                                                                                                                                                                                | Microsemi SoC Products Group                                                                                                    |

| standards compatibility 162                                                                                                                                                                                                 | email 321                                                                                                                       |

| I/O standards 77                                                                                                                                                                                                            | web-based technical support 321                                                                                                 |

| global macros 46                                                                                                                                                                                                            | website 321                                                                                                                     |

| single-ended 166                                                                                                                                                                                                            | WODONG 021                                                                                                                      |

| I/Os                                                                                                                                                                                                                        | 0                                                                                                                               |

| assigning technologies 198                                                                                                                                                                                                  | OTP 223                                                                                                                         |

| assignments defined in PDC file 193                                                                                                                                                                                         | output slew rate 175                                                                                                            |

| automatically assigning 202                                                                                                                                                                                                 | output siew rate 175                                                                                                            |

| behavior at power-up/-down 311                                                                                                                                                                                              | D                                                                                                                               |

| board-level considerations 181                                                                                                                                                                                              | P                                                                                                                               |

| buffer schematic cell 191                                                                                                                                                                                                   | PDC                                                                                                                             |

| cell architecture 207                                                                                                                                                                                                       | global promotion and demotion 51                                                                                                |

| configuration with SmartGen 188                                                                                                                                                                                             | place-and-route 193                                                                                                             |

| features 163, 164, 167                                                                                                                                                                                                      | PLL                                                                                                                             |

| global, naming 35                                                                                                                                                                                                           | behavior at brownout condition 315 configuration bits 90                                                                        |

| manually assigning technologies 198 nano standard 162                                                                                                                                                                       | corniguration bits 90 core specifications 84                                                                                    |

| register combining 174                                                                                                                                                                                                      | dynamic PLL configuration 87                                                                                                    |

| simplified buffer circuitry 165                                                                                                                                                                                             | functional description 85                                                                                                       |

| software support 177                                                                                                                                                                                                        | power supply decoupling scheme 112                                                                                              |

| software-controlled attributes 187                                                                                                                                                                                          | PLL block signals 68                                                                                                            |

| user I/O assignment flow chart 185                                                                                                                                                                                          | PLL macro block diagram 69                                                                                                      |

| user naming convention 178                                                                                                                                                                                                  | product support                                                                                                                 |

| wide range support 166                                                                                                                                                                                                      | customer service 321                                                                                                            |

|                                                                                                                                                                                                                             |                                                                                                                                 |