### Microchip Technology - <u>A3PN060-Z1VQ100I Datasheet</u>

Welcome to **E-XFL.COM**

Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 71                                                                         |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-z1vq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

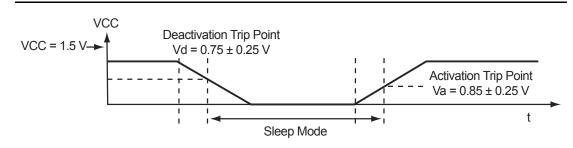

Figure 2-5 • Entering and Exiting Sleep Mode—Typical Timing Diagram

## **Shutdown Mode**

For all ProASIC3/E and ProASIC3 nano devices, shutdown mode can be entered by turning off all power supplies when device functionality is not needed. Cold-sparing and hot-insertion features in ProASIC3 nano devices enable the device to be powered down without turning off the entire system. When power returns, the live at power-up feature enables immediate operation of the device.

## Using Sleep Mode or Shutdown Mode in the System

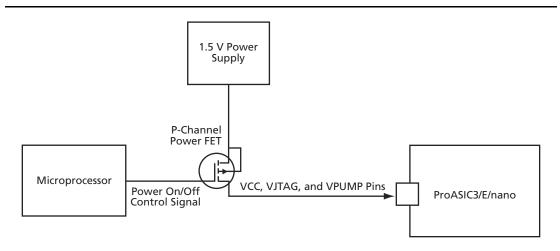

Depending on the power supply and components used in an application, there are many ways to turn the power supplies connected to the device on or off. For example, Figure 2-6 shows how a microprocessor is used to control a power FET. It is recommended that power FETs with low on resistance be used to perform the switching action.

Figure 2-6 • Controlling Power On/Off State Using Microprocessor and Power FET

Table 3-2 • Chip Global Pin Name

| I/O Type               | Beginning of I/O Name | Notes                                                        |

|------------------------|-----------------------|--------------------------------------------------------------|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |

|                        | GFA2/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |

|                        | GFB2/IOuxwByVz        |                                                              |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |

|                        | GFC2/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |

|                        | GCA2/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |

|                        | GCB2/IOuxwByVz        |                                                              |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |

|                        | GCC2/IOuxwByVz        |                                                              |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFA1/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFB1/IOuxwByVz        |                                                              |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFC1/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCA1/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCB1/IOuxwByVz        |                                                              |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCC1/IOuxwByVz        |                                                              |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

#### Simple Design Example

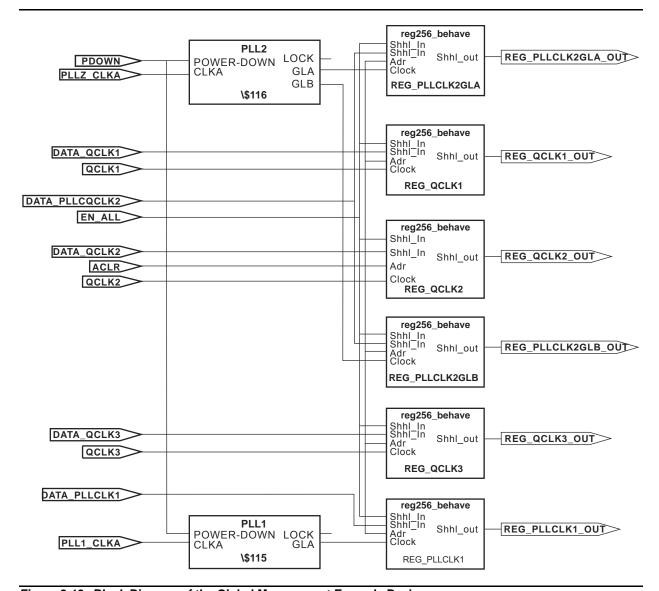

Consider a design consisting of six building blocks (shift registers) and targeted for an A3PE600-PQ208 (Figure 3-16 on page 52). The example design consists of two PLLs (PLL1 has GLA only; PLL2 has both GLA and GLB), a global reset (ACLR), an enable (EN\_ALL), and three external clock domains (QCLK1, QCLK2, and QCLK3) driving the different blocks of the design. Note that the PQ208 package only has two PLLs (which access the chip global network). Because of fanout, the global reset and enable signals need to be assigned to the chip global resources. There is only one free chip global for the remaining global (QCLK1, QCLK2, QCLK3). Place two of these signals on the quadrant global resource. The design example demonstrates manually assignment of QCLK1 and QCLK2 to the quadrant global using the PDC command.

Figure 3-19 • Block Diagram of the Global Management Example Design

#### Notes:

- 1. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 2. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

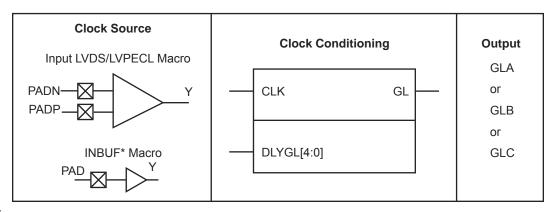

Figure 4-3 • CCC Options: Global Buffers with Programmable Delay

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay. The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the software will automatically place the dedicated global I/O in the appropriate locations. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the low power flash family. The available INBUF macros are described in the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

The CLKDLY macro can be driven directly from the FPGA core. The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate the clock input driven by the hardwired I/O connection.

The visual CLKDLY configuration in the SmartGen area of the Microsemi Libero System-on-Chip (SoC) and Designer tools allows the user to select the desired amount of delay and configures the delay elements appropriately. SmartGen also allows the user to select the input clock source. SmartGen will automatically instantiate the special macro, PLLINT, when needed.

## **CLKDLY Macro Signal Descriptions**

The CLKDLY macro supports one input and one output. Each signal is described in Table 4-2.

Table 4-2 • Input and Output Description of the CLKDLY Macro

| Signal | Name            | I/O    | Description                                                       |

|--------|-----------------|--------|-------------------------------------------------------------------|

| CLK    | Reference Clock | Input  | Reference clock input                                             |

| GL     | Global Output   | Output | Primary output clock to respective global/quadrant clock networks |

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

#### **CCC Locations**

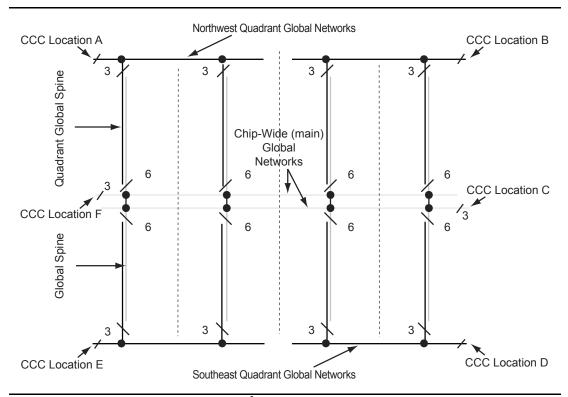

CCCs located in the middle of the east and west sides of the device access the three VersaNet global networks on each side (six total networks), while the four CCCs located in the four corners access three quadrant global networks (twelve total networks). See Figure 4-13.

Figure 4-13 • Global Network Architecture for 60 k Gate Devices and Above

The following explains the locations of the CCCs in IGLOO and ProASIC3 devices:

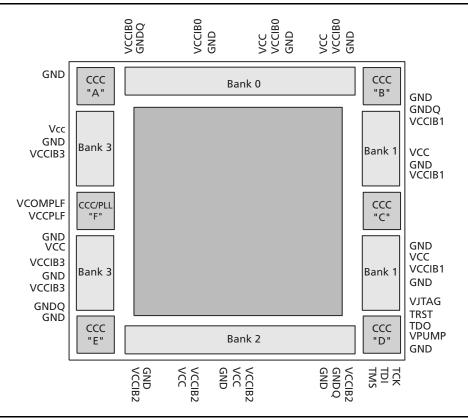

In Figure 4-15 on page 82 through Figure 4-16 on page 82, CCCs with integrated PLLs are indicated in red, and simplified CCCs are indicated in yellow. There is a letter associated with each location of the CCC, in clockwise order. The upper left corner CCC is named "A," the upper right is named "B," and so on. These names finish up at the middle left with letter "F."

Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

| Config.<br>Bits | Signal              | Name                             | Description                                                                                                                                     |  |

|-----------------|---------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 83              | RXCSEL <sup>1</sup> | CLKC input selection             | Select the CLKC input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 82              | RXBSEL <sup>1</sup> | CLKB input selection             | Select the CLKB input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 81              | RXASEL <sup>1</sup> | CLKA input selection             | Select the CLKA input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 80              | RESETEN             | Reset Enable                     | Enables (active high) the synchronization of PLL output dividers after dynamic reconfiguration (SUPDATE). The Reset Enable signal is READ-ONLY. |  |

| 79              | DYNCSEL             | Clock Input C Dynamic<br>Select  | Configures clock input C to be sent to GLC for dynamic control. <sup>2</sup>                                                                    |  |

| 78              | DYNBSEL             | Clock Input B Dynamic<br>Select  | Configures clock input B to be sent to GLB for dynamic control. <sup>2</sup>                                                                    |  |

| 77              | DYNASEL             | Clock Input A Dynamic<br>Select  | Configures clock input A for dynamic PLL configuration. <sup>2</sup>                                                                            |  |

| <76:74>         | VCOSEL[2:0]         | VCO Gear Control                 | Three-bit VCO Gear Control for four frequency ranges (refer to Table 4-19 on page 95 and Table 4-20 on page 95).                                |  |

| 73              | STATCSEL            | MUX Select on Input C            | MUX selection for clock input C <sup>2</sup>                                                                                                    |  |

| 72              | STATBSEL            | MUX Select on Input B            | MUX selection for clock input B <sup>2</sup>                                                                                                    |  |

| 71              | STATASEL            | MUX Select on Input A            | MUX selection for clock input A <sup>2</sup>                                                                                                    |  |

| <70:66>         | DLYC[4:0]           | YC Output Delay                  | Sets the output delay value for YC.                                                                                                             |  |

| <65:61>         | DLYB[4:0]           | YB Output Delay                  | Sets the output delay value for YB.                                                                                                             |  |

| <60:56>         | DLYGLC[4:0]         | GLC Output Delay                 | Sets the output delay value for GLC.                                                                                                            |  |

| <55:51>         | DLYGLB[4:0]         | GLB Output Delay                 | Sets the output delay value for GLB.                                                                                                            |  |

| <50:46>         | DLYGLA[4:0]         | Primary Output Delay             | Primary GLA output delay                                                                                                                        |  |

| 45              | XDLYSEL             | System Delay Select              | When selected, inserts System Delay in the feedback path in Figure 4-20 on page 85.                                                             |  |

| <44:40>         | FBDLY[4:0]          | Feedback Delay                   | Sets the feedback delay value for the feedback element in Figure 4-20 on page 85.                                                               |  |

| <39:38>         | FBSEL[1:0]          | Primary Feedback Delay<br>Select | Controls the feedback MUX: no delay, include programmable delay element, or use external feedback.                                              |  |

| <37:35>         | OCMUX[2:0]          | Secondary 2 Output<br>Select     | Selects from the VCO's four phase outputs for GLC/YC.                                                                                           |  |

| <34:32>         | OBMUX[2:0]          | Secondary 1 Output<br>Select     | Selects from the VCO's four phase outputs for GLB/YB.                                                                                           |  |

#### Notes:

- 1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

- 2. This value depends on the input clock source, so Layout must complete before these bits can be set.

After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools >

Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

FlashROM in Microsemi's Low Power Flash Devices

## Conclusion

The Fusion, IGLOO, and ProASIC3 families are the only FPGAs that offer on-chip FlashROM support. This document presents information on the FlashROM architecture, possible applications, programming, access through the JTAG and UJTAG interface, and integration into your design. In addition, the Libero tool set enables easy creation and modification of the FlashROM content.

The nonvolatile FlashROM block in the FPGA can be customized, enabling multiple applications.

Additionally, the security offered by the low power flash devices keeps both the contents of FlashROM and the FPGA design safe from system over-builders, system cloners, and IP thieves.

## **Related Documents**

#### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/documents/FlashPro UG.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                   |          |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                 |          |  |  |  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 5-1 • Flash-Based FPGAs.                                                                                                                         |          |  |  |  |

| v1.3<br>(October 2008)  | The "FlashROM Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                          | 118      |  |  |  |

|                         | Figure 5-2 • Fusion Device Architecture Overview (AFS600) was replaced. Figure 5-5 • Programming FlashROM Using AES was revised to change "Fusion" to "Flash Device."                                     | 119, 121 |  |  |  |

|                         | The FlashPoint User's Guide was removed from the "User's Guides" section, as its content is now part of the FlashPro User's Guide.                                                                        | 130      |  |  |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 5-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. |          |  |  |  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                         | N/A      |  |  |  |

## **SRAM and FIFO Architecture**

To meet the needs of high-performance designs, the memory blocks operate strictly in synchronous mode for both read and write operations. The read and write clocks are completely independent, and each can operate at any desired frequency up to 250 MHz.

- 4k×1, 2k×2, 1k×4, 512×9 (dual-port RAM—2 read / 2 write or 1 read / 1 write)

- 512×9, 256×18 (2-port RAM—1 read / 1 write)

- Sync write, sync pipelined / nonpipelined read

Automotive ProASIC3 devices support single-port SRAM capabilities or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). The Libero SoC software macro libraries support a dual-port macro only. For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

The memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY).

Simultaneous dual-port read/write and write/write operations at the same address are allowed when certain timing requirements are met.

During RAM operation, addresses are sourced by the user logic, and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes.

The low power flash device architecture enables the read and write sizes of RAMs to be organized independently, allowing for bus conversion. For example, the write size can be set to 256×18 and the read size to 512×9.

Both the write width and read width for the RAM blocks can be specified independently with the WW (write width) and RW (read width) pins. The different D×W configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1. When widths of one, two, or four are selected, the ninth bit is unused. For example, when writing nine-bit values and reading four-bit values, only the first four bits and the second four bits of each nine-bit value are addressable for read operations. The ninth bit is not accessible.

Conversely, when writing four-bit values and reading nine-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

## **Memory Blocks and Macros**

Memory blocks can be configured with many different aspect ratios, but are generically supported in the macro libraries as one of two memory elements: RAM4K9 or RAM512X18. The RAM4K9 is configured as a true dual-port memory block, and the RAM512X18 is configured as a two-port memory block. Dual-port memory allows the RAM to both read from and write to either port independently. Two-port memory allows the RAM to read from one port and write to the other using a common clock or independent read and write clocks. If needed, the RAM4K9 blocks can be configured as two-port memory blocks. The memory block can be configured as a FIFO by combining the basic memory block with dedicated FIFO controller logic. The FIFO macro is named FIFO4KX18 (Figure 6-3 on page 136).

Clocks for the RAM blocks can be driven by the VersaNet (global resources) or by regular nets. When using local clock segments, the clock segment region that encompasses the RAM blocks can drive the RAMs. In the dual-port configuration (RAM4K9), each memory block port can be driven by either rising-edge or falling-edge clocks. Each port can be driven by clocks with different edges. Though only a rising-edge clock can drive the physical block itself, the Microsemi Designer software will automatically bubble-push the inversion to properly implement the falling-edge trigger for the RAM block.

# Low Power Flash Device I/O Support

The low power flash families listed in Table 7-1 support I/Os and the functions described in this document.

#### Table 7-1 • Flash-Based FPGAs

| Series   | Family*       | Description                                                    |  |

|----------|---------------|----------------------------------------------------------------|--|

| IGLOO    | IGLOO nano    | Lowest power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |  |

| ProASIC3 | ProASIC3 nano | Lowest cost 1.5 V FPGAs with balanced performance              |  |

Note: \*The device name links to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## I/O Standards

#### Single-Ended Standards

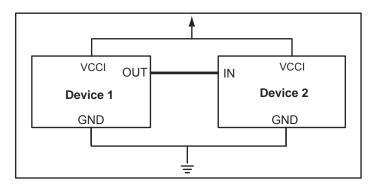

These I/O standards use a push-pull CMOS output stage with a voltage referenced to system ground to designate logical states. The input buffer configuration, output drive, and I/O supply voltage ( $V_{CCI}$ ) vary among the I/O standards (Figure 7-4).

Figure 7-4 • Single-Ended I/O Standard Topology

The advantage of these standards is that a common ground can be used for multiple I/Os. This simplifies board layout and reduces system cost. Their low-edge-rate (*dv/dt*) data transmission causes less electromagnetic interference (EMI) on the board. However, they are not suitable for high-frequency (>200 MHz) switching due to noise impact and higher power consumption.

#### LVTTL (Low-Voltage TTL)

This is a general-purpose standard (EIA/JESD8-B) for 3.3 V applications. It uses an LVTTL input buffer and a push-pull output buffer. The LVTTL output buffer can have up to six different programmable drive strengths. Refer to "I/O Programmable Features" on page 167 for details. Refer to Table 7-14 on page 176 for details.

#### LVCMOS (Low-Voltage CMOS)

The low power flash devices provide five voltage levels for LVCMOS: LVCMOS  $3.3 \, \text{V}$ , LVCMOS  $2.5 \, \text{V}$ , LVCMOS  $1.8 \, \text{V}$ , LVCMOS  $1.5 \, \text{V}$ , and LVCMOS  $1.2 \, \text{V}$ .

LVCMOS 3.3 V is an extension of the LVCMOS standard (JESD8-B-compliant) used for general-purpose 3.3 V applications. LVCMOS 2.5 V is an extension of the LVCMOS standard (JESD8-5-compliant) used for general-purpose 2.5 V applications. LVCMOS 1.8 V is an extension of the LVCMOS standard (JESD8-7-compliant) used for general-purpose 1.8 V applications. LVCMOS 1.5 V is an extension of the LVCMOS standard (JESD8-11-compliant) used for general-purpose 1.5 V applications. LVCMOS 1.2V is an extension of the LVCMOS standard (JESD8-12A-compliant) used for general-purpose 1.2 V applications.

The VCCI values for these standards are 3.3 V, 2.5 V, 1.8 V, 1.5 V, and 1.2 V, respectively. Like LVTTL, the output buffer has up to four different programmable drive strengths (2, 4, 6, and 8 mA). Refer to "nano Output Drive and Slew" on page 176 for details.

# Wide Range I/O Support

Microsemi nano devices support JEDEC defined wide range I/O operation. ProASIC3 nano devices support the JESD8-B specification covering both 3 V and 3.3 V supplies, for an effective operating range of 2.7 V - 3.6 V. IGLOO nano devices support both the JESD8-B specification per the above and JESD8-12A with 1.2 V nominal, supporting an effective operating range of 1.14 V - 1.575 V.

#### **Electrostatic Discharge Protection**

Low power flash devices are tested per JEDEC Standard JESD22-A114-B.

These devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

All nano devices are qualified to the Human Body Model (HBM) and the Charged Device Model (CDM).

Table 7-12 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in nano Devices

| I/O Assignment     | Clamp Diode | Hot Insertion | 5 V Input<br>Tolerance | Input Buffer     | Output<br>Buffer |

|--------------------|-------------|---------------|------------------------|------------------|------------------|

| 3.3 V LVTTL/LVCMOS | No          | Yes           | Yes*                   | Enabled/Disabled |                  |

| LVCMOS 2.5 V       | No          | Yes           | No                     | Enabled/Disabled |                  |

| LVCMOS 1.8 V       | No          | Yes           | No                     | Enabled/Disabled |                  |

| LVCMOS 1.5 V       | No          | Yes           | No                     | Enabled/Disabled |                  |

| LVCMOS 1.2 V       | No          | Yes           | No                     | Enabled/Disabled |                  |

<sup>\*</sup> Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

#### **5 V Input and Output Tolerance**

nano devices can be made 5 V-input-tolerant for certain I/O standards by using external level shifting techniques. 5 V output compliance can be achieved using certain I/O standards.

Table 7-5 on page 163 shows the I/O standards that support 5 V input tolerance. Only 3.3 V LVTTL/LVCMOS standards support 5 V output tolerance.

#### 5 V Input Tolerance

I/Os can support 5 V input tolerance when LVTTL 3.3 V or LVCMOS 3.3 V configurations are used (see Table 7-12). There are three recommended solutions for achieving 5 V receiver tolerance (see Figure 7-5 on page 172 to Figure 7-7 on page 173 for details of board and macro setups). All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

#### Solution 1

The board-level design must ensure that the reflected waveform at the pad does not exceed the limits provided in the recommended operating conditions in the datasheet. This is a requirement to ensure long-term reliability.

This solution requires two board resistors, as demonstrated in Figure 7-5 on page 172. Here are some examples of possible resistor values (based on a simplified simulation model with no line effects and  $10~\Omega$  transmitter output resistance, where Rtx\_out\_high = (VCCI – VOH) / I<sub>OH</sub> and Rtx out low = VOL / I<sub>OL</sub>).

Example 1 (high speed, high current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$ R1 = 36  $\Omega$  (±5%), P(r1)min = 0.069  $\Omega$ R2 = 82  $\Omega$  (±5%), P(r2)min = 0.158  $\Omega$

$Imax_tx = 5.5 \text{ V} / (82 \times 0.95 + 36 \times 0.95 + 10) = 45.04 \text{ mA}$

$t_{RISE}$  =  $t_{FALL}$  = 0.85 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

$t_{RISE}$  =  $t_{FALL}$  = 4 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

# **User I/O Naming Convention**

Due to the comprehensive and flexible nature of nano Standard I/Os, a naming scheme is used to show the details of each I/O (Figure 7-8). The name identifies to which I/O bank it belongs.

I/O Nomenclature = FF/Gmn/IOuxwBy

Gmn is only used for I/Os that also have CCC access—i.e., global pins.

- FF = Indicates the I/O dedicated for the Flash\*Freeze mode activation pin

- G = Global

- m = Global pin location associated with each CCC on the device: A (northwest corner), B (northeast corner), C (east middle), D (southeast corner), E (southwest corner), and F (west middle)

- global input MUX and pin number of the associated Global location m—either A0, A1, A2, B0, B1, B2, C0, C1, or C2. Refer to the "Global Resources in Low Power Flash Devices" section on page 31 for information about the three input pins per clock source MUX at CCC location m.

- u = I/O pair number in the bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction

- x = R (Regular—single-ended) for the I/Os that support single-ended standards.

- w = S (Single-Ended)

- B = Bank

- y = Bank number (0–3). The Bank number starts at 0 from the northwest I/O bank and proceeds in a clockwise direction.

Figure 7-8 • I/O Naming Conventions for nano Devices - Top View

# Implementing I/Os in Microsemi Software

Microsemi Libero SoC software is integrated with design entry tools such as the SmartGen macro builder, the ViewDraw schematic entry tool, and an HDL editor. It is also integrated with the synthesis and Designer tools. In this section, all necessary steps to implement the I/Os are discussed.

#### **Design Entry**

There are three ways to implement I/Os in a design:

- Use the SmartGen macro builder to configure I/Os by generating specific I/O library macros and then instantiating them in top-level code. This is especially useful when creating I/O bus structures.

- 2. Use an I/O buffer cell in a schematic design.

- 3. Manually instantiate specific I/O macros in the top-level code.

If technology-specific macros, such as INBUF\_LVCMOS33 and OUTBUF\_PCI, are used in the HDL code or schematic, the user will not be able to change the I/O standard later on in Designer. If generic I/O macros are used, such as INBUF, OUTBUF, TRIBUF, CLKBUF, and BIBUF, the user can change the I/O standard using the Designer I/O Attribute Editor tool.

#### Using SmartGen for I/O Configuration

The SmartGen tool in Libero SoC provides a GUI-based method of configuring the I/O attributes. The user can select certain I/O attributes while configuring the I/O macro in SmartGen. The steps to configure an I/O macro with specific I/O attributes are as follows:

- 1. Open Libero SoC.

- 2. On the left-hand side of the Catalog View, select I/O, as shown in Figure 8-2.

Figure 8-2 • SmartGen Catalog

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                                                   |     |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| August 2012             | The notes in Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666).                           |     |  |  |  |

| June 2011               | Figure 8-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.                                 | 188 |  |  |  |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                                                      | 199 |  |  |  |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                                              |     |  |  |  |

| July 2010               | lotes were added where appropriate to point out that IGLOO nano and ProASIC3 ano devices do not support differential inputs (SAR 21449).                                                                  |     |  |  |  |

| v1.4<br>(December 2008) |                                                                                                                                                                                                           |     |  |  |  |

|                         | The notes for Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.                             | 187 |  |  |  |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                                          |     |  |  |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 8-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 186 |  |  |  |

| v1.1<br>(March 2008)    | This document was previously part of the I/O Structures in IGLOO and ProASIC3 Devices document. The content was separated and made into a new document.                                                   | N/A |  |  |  |

|                         | Table 8-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                                                      | 187 |  |  |  |

## **Programming Solutions**

Details for the available programmers can be found in the programmer user's guides listed in the "Related Documents" section on page 231.

All the programmers except FlashPro4, FlashPro3, FlashPro Lite, and FlashPro require adapter modules, which are designed to support device packages. All modules are listed on the Microsemi SoC Products Group website at

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx. They are not listed in this document, since this list is updated frequently with new package options and any upgrades required to improve programming yield or support new families.

Table 10-3 • Programming Solutions

| Programmer                 | Vendor             | ISP              | Single<br>Device | Multi-Device                | Availability                                     |

|----------------------------|--------------------|------------------|------------------|-----------------------------|--------------------------------------------------|

| FlashPro4                  | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro3                  | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro Lite <sup>2</sup> | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro                   | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Discontinued                                     |

| Silicon Sculptor 3         | Microsemi          | Yes <sup>3</sup> | Yes              | Cascade option (up to two)  | Available                                        |

| Silicon Sculptor II        | Microsemi          | Yes <sup>3</sup> | Yes              | Cascade option (up to two)  | Available                                        |

| Silicon Sculptor           | Microsemi          | Yes              | Yes              | Cascade option (up to four) | Discontinued                                     |

| Sculptor 6X                | Microsemi          | No               | Yes              | Yes                         | Discontinued                                     |

| BP MicroProgrammers        | BP<br>Microsystems | No               | Yes              | Yes                         | Contact BP<br>Microsystems at<br>www.bpmicro.com |

#### Notes:

- 1. Multiple devices can be connected in the same JTAG chain for programming.

- 2. If FlashPro Lite is used for programming, the programmer derives all of its power from the target pc board's VDD supply. The FlashPro Lite's VPP and VPN power supplies use the target pc board's VDD as a power source. The target pc board must supply power to both the VDDP and VDD power pins of the ProASICPLUS device in addition to supplying VDD to the FlashPro Lite. The target pc board needs to provide at least 500 mA of current to the FlashPro Lite VDD connection for programming.

- 3. Silicon Sculptor II and Silicon Sculptor 3 can only provide ISP for ProASIC and ProASIC families, not for Fusion, IGLOO, or ProASIC3 devices.

## **Related Documents**

## **User's Guides**

FlashPro User's Guide http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                    |     |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                  | N/A |  |  |  |

| v1.5<br>(August 2009)   | The "CoreMP7 Device Security" section was removed from "Security in ARM-Enabled Low Power Flash Devices", since M7-enabled devices are no longer supported.                                                |     |  |  |  |

| v1.4<br>(December 2008) | GLOO nano and ProASIC3 nano devices were added to Table 11-1 • Flash-Based FPGAs.                                                                                                                          |     |  |  |  |

| v1.3<br>(October 2008)  | The "Security Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                           |     |  |  |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 11-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. |     |  |  |  |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                                                                      | N/A |  |  |  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                | 236 |  |  |  |

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 13-1 support the voltage switching circuit feature and the functions described in this document.

Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family*              | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGL00    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# **Circuit Description**

All IGLOO devices as well as the ProASIC3L product family are available in two versions: V5 devices, which are powered by a 1.5 V supply and V2 devices, which are powered by a supply anywhere in the range of 1.2 V to 1.5 V in 50 mV increments. Applications that use IGLOO or ProASIC3L devices powered by a 1.2 V core supply must have a mechanism that switches the core voltage from 1.2 V (or other voltage below 1.5 V) to 1.5 V during in-system programming (ISP). There are several possible techniques to meet this requirement. Microsemi recommends utilizing a linear voltage regulator, a resistor voltage divider, and an N-Channel Digital FET to set the appropriate VCC voltage, as shown in Figure 13-1.

Where 1.2 V is mentioned in the following text, the meaning applies to any voltage below the 1.5 V range. Resistor values in the figures have been calculated for 1.2 V, so refer to power regulator datasheets if a different core voltage is required.

The main component of Microsemi's recommended circuit is the LTC3025 linear voltage regulator from LinearTech. The output voltage of the LTC3025 on the OUT pin is set by the ratio of two external resistors, R37 and R38, in a voltage divider. The linear voltage regulator adjusts the voltage on the OUT pin to maintain the ADJ pin voltage at 0.4 V (referenced to ground). By using an R38 value of 40.2 k $\Omega$  and an R37 value of 80.6 k $\Omega$ , the output voltage on the OUT pin is 1.2 V. To achieve 1.5 V on the OUT pin, R44 can be used in parallel with R38. The OUT pin can now be used as a switchable source for the VCC supply. Refer to the *LTC3025 Linear Voltage Regulator datasheet* for more information.

In Figure 13-1, the N-Channel Digital FET is used to enable and disable R44. This FET is controlled by the JTAG TRST signal driven by the FlashPro3 programmer. During programming of the device, the TRST signal is driven HIGH by the FlashPro3, and turns the N-Channel Digital FET ON. When the FET is ON, R44 becomes enabled as a parallel resistance to R38, which forces the regulator to set OUT to 1.5 V.

When the FlashPro3 is connected and not in programming mode or when it is not connected, the pull-down resistor, R10, will pull the TRST signal LOW. When this signal is LOW, the N-Channel Digital FET is "open" and R44 is not part of the resistance seen by the LTC3025. The new resistance momentarily changes the voltage value on the ADJ pin, which in turn causes the output of the LTC3025 to compensate by setting OUT to 1.2 V. Now the device will run in regular active mode at the regular 1.2 V core voltage.

Figure 13-1 • Circuit Diagram

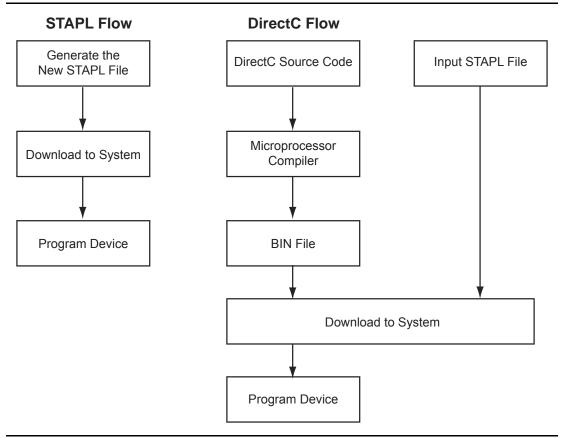

#### STAPL vs. DirectC

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 14-4).

Figure 14-4 • STAPL vs. DirectC

# **Typical UJTAG Applications**

Bidirectional access to the JTAG port from VersaTiles—without putting the device into test mode—creates flexibility to implement many different applications. This section describes a few of these. All are based on importing/exporting data through the UJTAG tiles.

#### Clock Conditioning Circuitry—Dynamic Reconfiguration

In low power flash devices, CCCs, which include PLLs, can be configured dynamically through either an 81-bit embedded shift register or static flash programming switches. These 81 bits control all the characteristics of the CCC: routing MUX architectures, delay values, divider values, etc. Table 16-3 lists the 81 configuration bits in the CCC.

Table 16-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks

| Bit Number(s) | Control Function |

|---------------|------------------|

| 80            | RESET ENABLE     |

| 79            | DYNCSEL          |

| 78            | DYNBSEL          |

| 77            | DYNASEL          |

| <76:74>       | VCOSEL [2:0]     |

| 73            | STATCSEL         |

| 72            | STATBSEL         |

| 71            | STATASEL         |

| <70:66>       | DLYC [4:0]       |

| <65:61>       | DLYB {4:0]       |

| <60:56>       | DLYGLC [4:0]     |

| <55:51>       | DLYGLB [4:0]     |

| <50:46>       | DLYGLA [4:0]     |

| 45            | XDLYSEL          |

| <44:40>       | FBDLY [4:0]      |

| <39:38>       | FBSEL            |

| <37:35>       | OCMUX [2:0]      |

| <34:32>       | OBMUX [2:0]      |

| <31:29>       | OAMUX [2:0]      |

| <28:24>       | OCDIV [4:0]      |

| <23:19>       | OBDIV [4:0]      |

| <18:14>       | OADIV [4:0]      |

| <13:7>        | FBDIV [6:0]      |

| <6:0>         | FINDIV [6:0]     |

The embedded 81-bit shift register (for the dynamic configuration of the CCC) is accessible to the VersaTiles, which, in turn, have access to the UJTAG tiles. Therefore, the CCC configuration shift register can receive and load the new configuration data stream from JTAG.

Dynamic reconfiguration eliminates the need to reprogram the device when reconfiguration of the CCC functional blocks is needed. The CCC configuration can be modified while the device continues to operate. Employing the UJTAG core requires the user to design a module to provide the configuration data and control the CCC configuration shift register. In essence, this is a user-designed TAP Controller requiring chip resources.

Similar reconfiguration capability exists in the ProASIC PLUS® family. The only difference is the number of shift register bits controlling the CCC (27 in ProASIC and 81 in IGLOO, ProASIC3, and Fusion).