Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 18432                                                                       |

| Number of I/O                  | 71                                                                          |

| Number of Gates                | 60000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                    |

| Supplier Device Package        | 100-VQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-z1vqg100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ProASIC3 nano FPGA Fabric User's Guide

|    | IEEE 1532 (JTAG) Interface                                                   | 264 |

|----|------------------------------------------------------------------------------|-----|

|    | Security                                                                     | 264 |

|    | Security in ARM-Enabled Low Power Flash Devices                              | 265 |

|    | FlashROM and Programming Files                                               | 267 |

|    | Programming Solution                                                         | 268 |

|    | ISP Programming Header Information                                           | 269 |

|    | Board-Level Considerations                                                   | 271 |

|    | Conclusion                                                                   | 272 |

|    | Related Documents                                                            | 272 |

|    | List of Changes                                                              | 273 |

| 13 | Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming | 275 |

|    | Introduction                                                                 | 275 |

|    | Microsemi's Flash Families Support Voltage Switching Circuit                 | 276 |

|    | Circuit Description                                                          |     |

|    | Circuit Verification                                                         |     |

|    | DirectC                                                                      |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

| 14 | Microprocessor Programming of Microsemi's Low Power Flash Devices            | 283 |

|    | Introduction                                                                 |     |

|    | Microprocessor Programming Support in Flash Devices                          |     |

|    | Programming Algorithm                                                        |     |

|    | Implementation Overview                                                      |     |

|    | Hardware Requirement                                                         |     |

|    | Security                                                                     |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              |     |

| 15 | Boundary Scan in Low Power Flash Devices                                     | 291 |

|    | Boundary Scan                                                                |     |

|    | TAP Controller State Machine                                                 |     |

|    | Microsemi's Flash Devices Support the JTAG Feature                           |     |

|    | Boundary Scan Support in Low Power Devices                                   |     |

|    | Boundary Scan Opcodes                                                        |     |

|    | Boundary Scan Chain                                                          |     |

|    | Board-Level Recommendations                                                  |     |

|    | Advanced Boundary Scan Register Settings                                     |     |

|    | List of Changes                                                              |     |

| 16 | UJTAG Applications in Microsemi's Low Power Flash Devices                    | 297 |

|    | Introduction                                                                 |     |

|    | UJTAG Support in Flash-Based Devices                                         |     |

|    | UJTAG Macro                                                                  |     |

|    |                                                                              |     |

|    | UJTAG Operation                                                              |     |

|    | Typical UJTAG Applications                                                   |     |

|    | Conclusion                                                                   |     |

|    | Related Documents                                                            |     |

|    | List of Changes                                                              | ასხ |

# 3 – Global Resources in Low Power Flash Devices

# Introduction

IGLOO, Fusion, and ProASIC3 FPGA devices offer a powerful, low-delay VersaNet global network scheme and have extensive support for multiple clock domains. In addition to the Clock Conditioning Circuits (CCCs) and phase-locked loops (PLLs), there is a comprehensive global clock distribution network called a VersaNet global network. Each logical element (VersaTile) input and output port has access to these global networks. The VersaNet global networks can be used to distribute low-skew clock signals or high-fanout nets. In addition, these highly segmented VersaNet global networks contain spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside their region. This allows users the flexibility to create low-skew local clock networks using spines. This document describes VersaNet global networks and discusses how to assign signals to these global networks and spines in a design flow. Details concerning low power flash device PLLs are described in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 61. This chapter describes the low power flash devices' global architecture and uses of these global networks in designs.

# **Global Architecture**

Low power flash devices offer powerful and flexible control of circuit timing through the use of global circuitry. Each chip has up to six CCCs, some with PLLs.

- In IGLOOe, ProASIC3EL, and ProASIC3E devices, all CCCs have PLLs—hence, 6 PLLs per device (except the PQ208 package, which has only 2 PLLs).

- In IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, and ProASIC3L devices, the west CCC contains a PLL core (except in 10 k through 30 k devices).

- In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.

Refer to Table 4-6 on page 84 for details. Each PLL includes delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three chip global lines on each side of the chip (six chip global lines total). The CCCs at the four corners each have access to three quadrant global lines in each quadrant of the chip (except in 10 k through 30 k gate devices).

The nano 10 k, 15 k, and 20 k devices support four VersaNet global resources, and 30 k devices support six global resources. The 10 k through 30 k devices have simplified CCCs called CCC-GLs.

The flexible use of the VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Note: Microsemi recommends that you choose the appropriate global pin and use the appropriate global resource so you can realize these benefits.

The following sections give an overview of the VersaNet global network, the structure of the global network, access point for the global networks, and the clock aggregation feature that enables a design to have very low clock skew using spines.

# **Spine Access**

The physical location of each spine is identified by the letter T (top) or B (bottom) and an accompanying number (Tn or Bn). The number n indicates the horizontal location of the spine; 1 refers to the first spine on the left side of the die. Since there are six chip spines in each spine tree, there are up to six spines available for each combination of T (or B) and n (for example, six T1 spines). Similarly, there are three quadrant spines available for each combination of T (or B) and n (for example, four T1 spines), as shown in Figure 3-7.

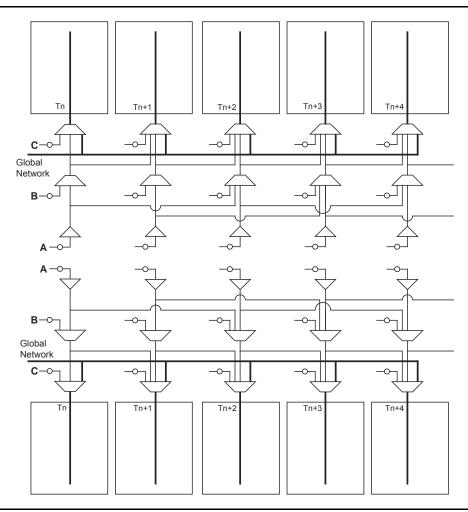

Figure 3-7 • Chip Global Aggregation

A spine is also called a local clock network, and is accessed by the dedicated global MUX architecture. These MUXes define how a particular spine is driven. Refer to Figure 3-8 on page 44 for the global MUX architecture. The MUXes for each chip global spine are located in the middle of the die. Access to the top and bottom chip global spine is available from the middle of the die. There is no control dependency between the top and bottom spines. If a top spine, T1, of a chip global network is assigned to a net, B1 is not wasted and can be used by the global clock network. The signal assigned only to the top or bottom spine cannot access the middle two rows of the architecture. However, if a spine is using the top and bottom at the same time (T1 and B1, for instance), the previous restriction is lifted.

The MUXes for each quadrant global spine are located in the north and south sides of the die. Access to the top and bottom quadrant global spines is available from the north and south sides of the die. Since the MUXes for quadrant spines are located in the north and south sides of the die, you should not try to drive T1 and B1 quadrant spines from the same signal.

# **Clock Aggregation Architecture**

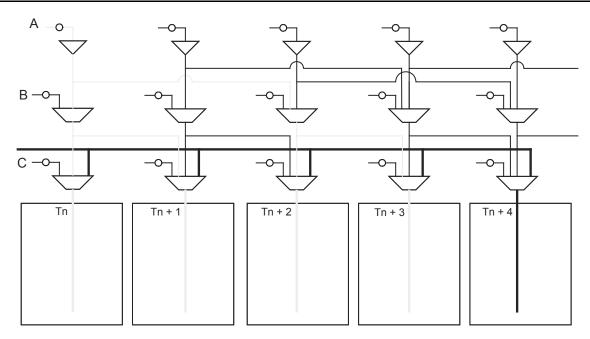

This clock aggregation feature allows a balanced clock tree, which improves clock skew. The physical regions for clock aggregation are defined from left to right and shift by one spine. For chip global networks, there are three types of clock aggregation available, as shown in Figure 3-10:

- Long lines that can drive up to four adjacent spines (A)

- · Long lines that can drive up to two adjacent spines (B)

- · Long lines that can drive one spine (C)

There are three types of clock aggregation available for the quadrant spines, as shown in Figure 3-10:

- I/Os or local resources that can drive up to four adjacent spines

- I/Os or local resources that can drive up to two adjacent spines

- I/Os or local resources that can drive one spine

As an example, A3PE600 and AFS600 devices have twelve spine locations: T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, and B6. Table 3-7 shows the clock aggregation you can have in A3PE600 and AFS600.

Figure 3-10 • Four Spines Aggregation

Table 3-7 • Spine Aggregation in A3PE600 or AFS600

| Clock Aggregation | Spine                                                                |

|-------------------|----------------------------------------------------------------------|

| 1 spine           | T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, B6                       |

| 2 spines          | T1:T2, T2:T3, T3:T4, T4:T5, T5:T6, B1:B2, B2:B3, B3:B4, B4:B5, B5:B6 |

| 4 spines          | B1:B4, B2:B5, B3:B6, T1:T4, T2:T5, T3:T6                             |

The clock aggregation for the quadrant spines can cross over from the left to right quadrant, but not from top to bottom. The quadrant spine assignment T1:T4 is legal, but the quadrant spine assignment T1:B1 is not legal. Note that this clock aggregation is hardwired. You can always assign signals to spine T1 and B2 by instantiating a buffer, but this may add skew in the signal.

Global Resources in Low Power Flash Devices

#### **Global Macro and Placement Selections**

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a global / quadrant global network. For 60K gate devices and above, if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen, the first and second inputs are considered as paired, and the third input is paired with a regular I/O. The user then has the choice of selecting one of the two sets to be used as the global input source. There is also the option to allow an internal clock signal to feed the global network. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

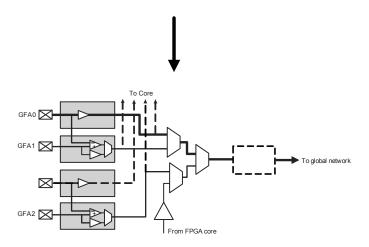

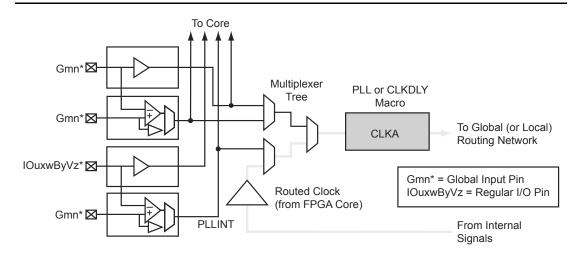

#### Hardwired I/O Clock Source

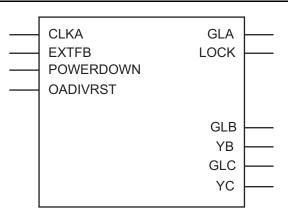

Hardwired I/O refers to global input pins that are hardwired to the multiplexer tree, which directly accesses the global network. These global input pins have designated pin locations and are indicated with the I/O naming convention Gmn (m refers to any one of the positions where the global buffers is available, and n refers to any one of the three global input MUXes and the pin number of the associated global location, m). Choosing this option provides the benefit of directly connecting to the global buffers, which provides less delay. See Figure 3-11 for an example illustration of the connections, shown in red. If a CLKBUF macro is initiated, the clock input can be placed at one of nine dedicated global input pin locations: GmA0, GmA1, GmA2, GmB0, GmB1, GmB2, GmC0, GmC1, or GmC2. Note that the placement of the global will determine whether you are using chip global or quadrant global. For example, if the CLKBIF is placed in one of the GF pin locations, it will use the chip global network; if the CLKBIF is placed in one of the GA pin locations, it will use quadrant global network. This is shown in Figure 3-12 on page 49 and Figure 3-13 on page 49.

Figure 3-11 • CLKBUF Macro

Note: OAVDIVRST exists only in the Fusion PLL.

Figure 3-15 • PLLs in Low Power Flash Devices

You can use the syn global buffers attribute in Synplify to specify a maximum number of global macros to be inserted in the netlist. This can also be used to restrict the number of global buffers inserted. In the Synplicity 8.1 version or newer, a new attribute, syn global minfanout, has been added for low power flash devices. This enables you to promote only the high-fanout signal to global. However, be aware that you can only have six signals assigned to chip global networks, and the rest of the global signals should be assigned to quadrant global networks. So, if the netlist has 18 global macros, the remaining 12 global macros should have fanout that allows the instances driven by these globals to be placed inside a quadrant.

## Global Promotion and Demotion Using PDC

The HDL source file or schematic is the preferred place for defining which signals should be assigned to a clock network using clock macro instantiation. This method is preferred because it is guaranteed to be honored by the synthesis tools and Designer software and stop any replication on this net by the synthesis tool. Note that a signal with fanout may have logic replication if it is not promoted to global during synthesis. In that case, the user cannot promote that signal to global using PDC. See Synplicity Help for details on using this attribute. To help you with global management, Designer allows you to promote a signal to a global network or demote a global macro to a regular macro from the user netlist using the compile options and/or PDC commands.

The following are the PDC constraints you can use to promote a signal to a global network:

1. PDC syntax to promote a regular net to a chip global clock:

```

assign_global_clock -net netname

```

The following will happen during promotion of a regular signal to a global network:

- If the net is external, the net will be driven by a CLKINT inserted automatically by Compile.

- The I/O macro will not be changed to CLKBUF macros.

- If the net is an internal net, the net will be driven by a CLKINT inserted automatically by Compile.

- 2. PDC syntax to promote a net to a quadrant clock:

```

assign_local_clock -net netname -type quadrant UR|UL|LR|LL

```

This follows the same rule as the chip global clock network.

The following PDC command demotes the clock nets to regular nets.

unassign\_global\_clock -net netname

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### Core Logic Clock Source

Core logic refers to internal routed nets. Internal routed signals access the CCC via the FPGA Core Fabric. Similar to the External I/O option, whenever the clock source comes internally from the core itself, the routed signal is instantiated with a PLLINT macro before connecting to the CCC clock input (see Figure 4-12 for an example illustration of the connections, shown in red).

Figure 4-12 • Illustration of Core Logic Usage

For Fusion devices, the input reference clock can also be from the embedded RC oscillator and crystal oscillator. In this case, the CCC configuration is the same as the hardwired I/O clock source, and users are required to instantiate the RC oscillator or crystal oscillator macro and connect its output to the input reference clock of the CCC block.

# **Device-Specific Layout**

Two kinds of CCCs are offered in low power flash devices: CCCs with integrated PLLs, and CCCs without integrated PLLs (simplified CCCs). Table 4-5 lists the number of CCCs in various devices.

Table 4-5 • Number of CCCs by Device Size and Package

| Device         |                |                    | CCCs with          | CCCs without                     |

|----------------|----------------|--------------------|--------------------|----------------------------------|

| ProASIC3       | IGLOO          | Package            | Integrated<br>PLLs | Integrated PLLs (simplified CCC) |

| A3PN010        | AGLN010        | All                | 0                  | 2                                |

| A3PN015        | AGLN015        | All                | 0                  | 2                                |

| A3PN020        | AGLN020        | All                | 0                  | 2                                |

|                | AGLN060        | CS81               | 0                  | 6                                |

| A3PN060        | AGLN060        | All other packages | 1                  | 5                                |

|                | AGLN125        | CS81               | 0                  | 6                                |

| A3PN125        | AGLN125        | All other packages | 1                  | 5                                |

|                | AGLN250        | CS81               | 0                  | 6                                |

| A3PN250        | AGLN250        | All other packages | 1                  | 5                                |

| A3P015         | AGL015         | All                | 0                  | 2                                |

| A3P030         | AGL030/AGLP030 | All                | 0                  | 2                                |

|                | AGL060/AGLP060 | CS121/CS201        | 0                  | 6                                |

| A3P060         | AGL060/AGLP060 | All other packages | 1                  | 5                                |

| A3P125         | AGL125/AGLP125 | All                | 1                  | 5                                |

| A3P250/L       | AGL250         | All                | 1                  | 5                                |

| A3P400         | AGL400         | All                | 1                  | 5                                |

| A3P600/L       | AGL600         | All                | 1                  | 5                                |

| A3P1000/L      | AGL1000        | All                | 1                  | 5                                |

| A3PE600        | AGLE600        | PQ208              | 2                  | 4                                |

| A3PE600/L      |                | All other packages | 6                  | 0                                |

| A3PE1500       |                | PQ208              | 2                  | 4                                |

| A3PE1500       |                | All other packages | 6                  | 0                                |

| A3PE3000/L     |                | PQ208              | 2                  | 4                                |

| A3PE3000/L     | AGLE3000       | All other packages | 6                  | 0                                |

| Fusion Devices |                |                    |                    |                                  |

| AFS090         |                | All                | 1                  | 5                                |

| AFS250, M1AFS  | 250            | All                | 1                  | 5                                |

| AFS600, M7AFS  | 600, M1AFS600  | All                | 2                  | 4                                |

| AFS1500, M1AF  | S1500          | All                | 2                  | 4                                |

Note: nano 10 k, 15 k, and 20 k offer 6 global MUXes instead of CCCs.

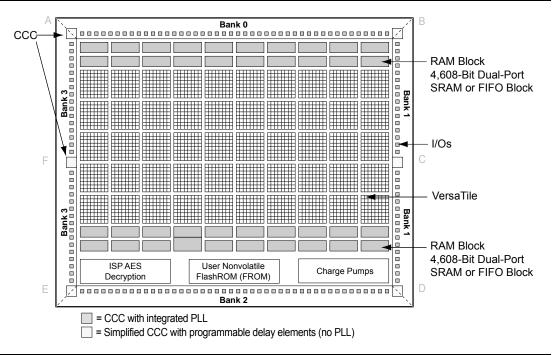

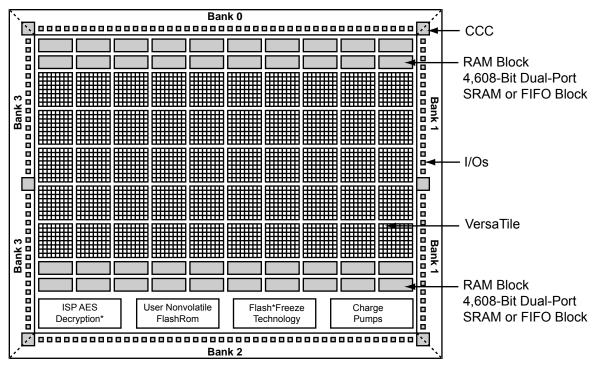

#### IGLOO and ProASIC3 CCC Locations

In all IGLOO and ProASIC3 devices (except 10 k through 30 k gate devices, which do not contain PLLs), six CCCs are located in the same positions as the IGLOOe and ProASIC3E CCCs. Only one of the CCCs has an integrated PLL and is located in the middle of the west (middle left) side of the device. The other five CCCs are simplified CCCs and are located in the four corners and the middle of the east side of the device (Figure 4-14).

Figure 4-14 • CCC Locations in IGLOO and ProASIC3 Family Devices (except 10 k through 30 k gate devices)

Note: The number and architecture of the banks are different for some devices.

10 k through 30 k gate devices do not support PLL features. In these devices, there are two CCC-GLs at the lower corners (one at the lower right, and one at the lower left). These CCC-GLs do not have programmable delays.

## ProASIC3 nano FPGA Fabric User's Guide

The following is an example of a PLL configuration utilizing the clock frequency synthesis and clock delay adjustment features. The steps include generating the PLL core with SmartGen, performing simulation for verification with Model *Sim*, and performing static timing analysis with SmartTime in Designer.

Parameters of the example PLL configuration:

Input Frequency - 20 MHz

Primary Output Requirement – 20 MHz with clock advancement of 3.02 ns

Secondary 1 Output Requirement - 40 MHz with clock delay of 2.515 ns

Figure 4-29 shows the SmartGen settings. Notice that the overall delays are calculated automatically, allowing the user to adjust the delay elements appropriately to obtain the desired delays.

#### Figure 4-29 • SmartGen Settings

After confirming the correct settings, generate a structural netlist of the PLL and verify PLL core settings by checking the log file:

```

Name

: test_pll_delays

Family

: ProASIC3E

Output Format

: VHDL

: Static PLL

Type

Input Freq(MHz)

: 20.000

CLKA Source

: Hardwired I/O

Feedback Delay Value Index

: 21

Feedback Mux Select

XDLY Mux Select

Primary Freq(MHz)

Primary PhaseShift

: No

: 20.000

: 0

Primary Delay Value Index

: 1

Primary Mux Select

: 4

Secondaryl Freq(MHz)

: 40.000

Use GLB

: YES

Use YB

: NO

Primary Clock frequency 20.000

Primary Clock Phase Shift 0.000

```

# FlashROM Support in Flash-Based Devices

The flash FPGAs listed in Table 5-1 support the FlashROM feature and the functions described in this document.

Table 5-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                   |  |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                             |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                         |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                           |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                    |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                       |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                      |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                           |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                         |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                   |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                         |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                          |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmat analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and fla memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

# **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Table 7-13 • Comparison Table for 5 V-Compliant Receiver Solutions

| Solution | Board Components         | Speed                    | Current Limitations                     |

|----------|--------------------------|--------------------------|-----------------------------------------|

| 1        | Two resistors            | Low to High <sup>1</sup> | Limited by transmitter's drive strength |

| 2        | Resistor and Zener 3.3 V | Medium                   | Limited by transmitter's drive strength |

| 3        | Bus switch               | High                     | N/A                                     |

#### Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

- 3. At 70°C, customers could still use 420  $\Omega$  on every I/O.

- 4. At 85°C, a 5 V solution on every other I/O is permitted, since the resistance is lower (150  $\Omega$  ) and the current is higher. Also, the designer can still use 420  $\Omega$  and use the solution on every I/O.

- 5. At 100°C, the 5 V solution on every I/O is permitted, since 420  $\Omega$  are used to limit the current to 5.9 mA.

## 5 V Output Tolerance

nano Standard I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, the I/Os can directly drive signals into 5 V TTL receivers. In fact,  $V_{OL}$  = 0.4 V and  $V_{OH}$  = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceeds the  $V_{IL}$  = 0.8 V and  $V_{IH}$  = 2 V level requirements of 5 V TTL receivers. Therefore, level 1 and level 0 will be recognized correctly by 5 V TTL receivers.

## **Schmitt Trigger**

A Schmitt trigger is a buffer used to convert a slow or noisy input signal into a clean one before passing it to the FPGA. Using Schmitt trigger buffers guarantees a fast, noise-free input signal to the FPGA.

nano devices have Schmitt triggers built into their I/O circuitry. Schmitt Trigger is available on all I/O configurations.

This feature can be implemented by using a Physical Design Constraints (PDC) command (Table 7-5 on page 163) or by selecting a check box in the I/O Attribute Editor in Designer. The check box is cleared by default.

# I/O Register Combining

Every I/O has several embedded registers in the I/O tile that are close to the I/O pads. Rather than using the internal register from the core, the user has the option of using these registers for faster clock-to-out timing, and external hold and setup. When combining these registers at the I/O buffer, some architectural rules must be met. Provided these rules are met, the user can enable register combining globally during Compile (as shown in the "Compiling the Design" section in the "I/O Software Control in Low Power Flash Devices" section on page 185.

This feature is supported by all I/O standards.

#### Rules for Registered I/O Function:

- 1. The fanout between an I/O pin (D, Y, or E) and a register must be equal to one for combining to be considered on that pin.

- All registers (Input, Output, and Output Enable) connected to an I/O must share the same clear or preset function:

- If one of the registers has a CLR pin, all the other registers that are candidates for combining in the I/O must have a CLR pin.

3. Double-click I/O to open the Create Core window, which is shown in Figure 8-3).

#### Figure 8-3 • I/O Create Core Window

As seen in Figure 8-3, there are five tabs to configure the I/O macro: Input Buffers, Output Buffers, Bidirectional Buffers, Tristate Buffers, and DDR.

#### **Input Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The **Special** variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options (see Figure 8-3). All the I/O standards and supply voltages ( $V_{CCI}$ ) supported for the device family are available for selection.

I/O Software Control in Low Power Flash Devices

Table 8-3 • PDC I/O Constraints (continued)

| Command               | Action                                                      | Example                                                                                                                                                                                                                                                                                                                                           | Comment                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I/O Attribute Cons    | I/O Attribute Constraint                                    |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| set_io                | Sets the attributes of an I/O                               | set_io portname [-pinname value] [-fixed value] [-iostd value] [-out_drive value] [-slew value] [-schmitt_trigger value] [-in_delay value] [-skew value] [-out_load value] [-register value]  set_io IN2 -pinname 28 -fixed yes -iostd LVCMOS15 -out_drive 12 -slew high -RES_PULL None -SCHMITT_TRIGGER Off -IN_DELAY Off -skew off -REGISTER No | If the I/O macro is generic (e.g., INBUF) or technology-specific (INBUF_LVCMOS25), then all I/O attributes can be assigned using this constraint. If the netlist has an I/O macro that specifies one of its attributes, that attribute cannot be changed using this constraint, though other attributes can be changed. Example: OUTBUF_S_24 (low slew, output drive 24 mA) Slew and output drive cannot be changed. |  |  |  |

| I/O Region Placer     | nent Constraints                                            |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| define_region         | Defines either a rectangular region or a rectilinear region | <pre>define_region   -name [region_name]   -type [region_type] x1 y1 x2 y2  define_region -name test   -type inclusive 0 15 2 29</pre>                                                                                                                                                                                                            | If any number of I/Os must be assigned to a particular I/O region, such a region can be created with this constraint.                                                                                                                                                                                                                                                                                                |  |  |  |

| to a specified region |                                                             | assign_region [region name] [macro_name] assign_region test U12                                                                                                                                                                                                                                                                                   | This constraint assigns I/O macros to the I/O regions. When assigning an I/O macro, PDC naming conventions must be followed if the macro name contains special characters; e.g., if the macro name is \\\$1119\ the correct use of escape characters is \\\\\\$1119\\\.                                                                                                                                              |  |  |  |

Note: Refer to the Libero SoC User's Guide for detailed rules on PDC naming and syntax conventions.

# **Security Architecture**

Fusion, IGLOO, and ProASIC3 devices have been designed with the most comprehensive programming logic design security in the industry. In the architecture of these devices, security has been designed into the very fabric. The flash cells are located beneath seven metal layers, and the use of many device design and layout techniques makes invasive attacks difficult. Since device layers cannot be removed without disturbing the charge on the programmed (or erased) flash gates, devices cannot be easily deconstructed to decode the design. Low power flash devices are unique in being reprogrammable and having inherent resistance to both invasive and noninvasive attacks on valuable IP. Secure, remote ISP is now possible with AES encryption capability for the programming file during electronic transfer. Figure 11-2 shows a view of the AES decryption core inside an IGLOO device; Figure 11-3 on page 238 shows the AES decryption core inside a Fusion device. The AES core is used to decrypt the encrypted programming file when programming.

Note: \*ISP AES Decryption is not supported by 30 k gate devices and smaller. For details of other architecture features by device, refer to the appropriate family datasheet.

Figure 11-2 • Block Representation of the AES Decryption Core in IGLOO and ProASIC3 Devices

#### Figure 11-19 • FlashLock Pass Key, Previously Programmed Devices

It is important to note that when the security settings need to be updated, the user also needs to select the **Security settings** check box in Step 1, as shown in Figure 11-10 on page 248 and Figure 11-11 on page 248, to modify the security settings. The user must consider the following:

- If only a new AES key is necessary, the user must re-enter the same Pass Key previously programmed into the device in Designer and then generate a programming file with the same Pass Key and a different AES key. This ensures the programming file can be used to access and program the device and the new AES key.

- If a new Pass Key is necessary, the user can generate a new programming file with a new Pass Key (with the same or a new AES key if desired). However, for programming, the user must first load the original programming file with the Pass Key that was previously used to unlock the device. Then the new programming file can be used to program the new security settings.

# **Advanced Options**

As mentioned, there may be applications where more complicated security settings are required. The "Custom Security Levels" section in the *FlashPro User's Guide* describes different advanced options available to aid the user in obtaining the best available security settings.

# **Programming File Header Definition**

In each STAPL programming file generated, there will be information about how the AES key and FlashLock Pass Key are configured. Table 11-8 shows the header definitions in STAPL programming files for different security levels.

Table 11-8 • STAPL Programming File Header Definitions by Security Level

| Security Level                                                  | STAPL File Header Definition          |  |

|-----------------------------------------------------------------|---------------------------------------|--|

| No security (no FlashLock Pass Key or AES key)                  | NOTE "SECURITY" "Disable";            |  |

| FlashLock Pass Key with no AES key                              | NOTE "SECURITY" "KEYED ";             |  |

| FlashLock Pass Key with AES key                                 | NOTE "SECURITY" "KEYED ENCRYPT ";     |  |

| Permanent Security Settings option enabled                      | NOTE "SECURITY" "PERMLOCK ENCRYPT ";  |  |

| AES-encrypted FPGA array (for programming updates)              | NOTE "SECURITY" "ENCRYPT CORE ";      |  |

| AES-encrypted FlashROM (for programming updates)                | NOTE "SECURITY" "ENCRYPT FROM ";      |  |

| AES-encrypted FPGA array and FlashROM (for programming updates) | NOTE "SECURITY" "ENCRYPT FROM CORE "; |  |

## Example File Headers

#### STAPL Files Generated with FlashLock Key and AES Key Containing Key Information

- FlashLock Key / AES key indicated in STAPL file header definition

- · Intended ONLY for secured/trusted environment programming applications

```

_____

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EDB9";

NOTE "SAVE_DATA" "FRomStream";

NOTE "SECURITY" "KEYED ENCRYPT ";

NOTE "ALG_VERSION" "1";

NOTE "MAX FREO" "20000000";

NOTE "SILSIG" "$00000000";

NOTE "PASS_KEY" "$00123456789012345678901234567890";

NOTE "AES_KEY" "$ABCDEFABCDEFABCDEFABCDEFABCDEFAB";

______

```

## ProASIC3 nano FPGA Fabric User's Guide

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                                                                                                                 | Changes                                                                                                                                               |     |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| July 2010                                                                                                            | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             |     |  |

| v1.1 The "Introduction" was revised to include information about the core supply vorange of operation in V2 devices. |                                                                                                                                                       | 275 |  |

| IGLOO nano device support was added to Table 13-1 • Flash-Based Supporting Voltage Switching Circuit.                |                                                                                                                                                       | 276 |  |

|                                                                                                                      | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 277 |  |

| v1.0<br>(August 2008)                                                                                                | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. |     |  |

Power-Up/-Down Behavior of Low Power Flash Devices

# Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 17-1 support power-up behavior and the functions described in this document.

Table 17-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# **B** – Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

## **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 650.318.8044

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

## **Website**

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

# **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc tech@microsemi.com.