Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 71                                                                         |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-z2vqg100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **VersaNet Global Network Distribution**

One of the architectural benefits of low power flash architecture is the set of powerful, low-delay VersaNet global networks that can access the VersaTiles, SRAM, and I/O tiles of the device. Each device offers a chip global network with six global lines (except for nano 10 k, 15 k, and 20 k gate devices) that are distributed from the center of the FPGA array. In addition, each device (except the 10 k through 30 k gate device) has four quadrant global networks, each consisting of three quadrant global net resources. These quadrant global networks can only drive a signal inside their own quadrant. Each VersaTile has access to nine global line resources—three quadrant and six chip-wide (main) global networks—and a total of 18 globals are available on the device (3 × 4 regional from each quadrant and 6 global).

Figure 3-1 shows an overview of the VersaNet global network and device architecture for devices 60 k and above. Figure 3-2 and Figure 3-3 on page 34 show simplified VersaNet global networks.

The VersaNet global networks are segmented and consist of spines, global ribs, and global multiplexers (MUXes), as shown in Figure 3-1. The global networks are driven from the global rib at the center of the die or quadrant global networks at the north or south side of the die. The global network uses the MUX trees to access the spine, and the spine uses the clock ribs to access the VersaTile. Access is available to the chip or quadrant global networks and the spines through the global MUXes. Access to the spine using the global MUXes is explained in the "Spine Architecture" section on page 41.

These VersaNet global networks offer fast, low-skew routing resources for high-fanout nets, including clock signals. In addition, these highly segmented global networks offer users the flexibility to create low-skew local clock networks using spines for up to 252 internal/external clocks or other high-fanout nets in low power flash devices. Optimal usage of these low-skew networks can result in significant improvement in design performance.

Note: Not applicable to 10 k through 30 k gate devices

Figure 3-1 • Overview of VersaNet Global Network and Device Architecture

# **Spine Architecture**

The low power flash device architecture allows the VersaNet global networks to be segmented. Each of these networks contains spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside its region. The nine spines available in a vertical column reside in global networks with two separate regions of scope: the quadrant global network, which has three spines, and the chip (main) global network, which has six spines. Note that the number of quadrant globals and globals/spines per tree varies depending on the specific device. Refer to Table 3-4 for the clocking resources available for each device. The spines are the vertical branches of the global network tree, shown in Figure 3-3 on page 34. Each spine in a vertical column of a chip (main) global network is further divided into two spine segments of equal lengths: one in the top and one in the bottom half of the die (except in 10 k through 30 k gate devices).

Top and bottom spine segments radiating from the center of a device have the same height. However, just as in the ProASIC family, signals assigned only to the top and bottom spine cannot access the middle two rows of the die. The spines for quadrant clock networks do not cross the middle of the die and cannot access the middle two rows of the architecture.

Each spine and its associated ribs cover a certain area of the device (the "scope" of the spine; see Figure 3-3 on page 34). Each spine is accessed by the dedicated global network MUX tree architecture, which defines how a particular spine is driven—either by the signal on the global network from a CCC, for example, or by another net defined by the user. Details of the chip (main) global network spine-selection MUX are presented in Figure 3-8 on page 44. The spine drivers for each spine are located in the middle of the die.

Quadrant spines can be driven from user I/Os or an internal signal from the north and south sides of the die. The ability to drive spines in the quadrant global networks can have a significant effect on system performance for high-fanout inputs to a design. Access to the top quadrant spine regions is from the top of the die, and access to the bottom quadrant spine regions is from the bottom of the die. The A3PE3000 device has 28 clock trees and each tree has nine spines; this flexible global network architecture enables users to map up to 252 different internal/external clocks in an A3PE3000 device.

Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices

| ProASIC3/<br>ProASIC3L<br>Devices | IGLOO<br>Devices | Chip<br>Globals | Quadrant<br>Globals<br>(4×3) | Clock<br>Trees | Globals/<br>Spines<br>per<br>Tree | Total<br>Spines<br>per<br>Device | VersaTiles<br>in Each<br>Tree | Total<br>VersaTiles | Rows<br>in<br>Each<br>Spine |

|-----------------------------------|------------------|-----------------|------------------------------|----------------|-----------------------------------|----------------------------------|-------------------------------|---------------------|-----------------------------|

| A3PN010                           | AGLN010          | 4               | 0                            | 1              | 0                                 | 0                                | 260                           | 260                 | 4                           |

| A3PN015                           | AGLN015          | 4               | 0                            | 1              | 0                                 | 0                                | 384                           | 384                 | 6                           |

| A3PN020                           | AGLN020          | 4               | 0                            | 1              | 0                                 | 0                                | 520                           | 520                 | 6                           |

| A3PN060                           | AGLN060          | 6               | 12                           | 4              | 9                                 | 36                               | 384                           | 1,536               | 12                          |

| A3PN125                           | AGLN125          | 6               | 12                           | 8              | 9                                 | 72                               | 384                           | 3,072               | 12                          |

| A3PN250                           | AGLN250          | 6               | 12                           | 8              | 9                                 | 72                               | 768                           | 6,144               | 24                          |

| A3P015                            | AGL015           | 6               | 0                            | 1              | 9                                 | 9                                | 384                           | 384                 | 12                          |

| A3P030                            | AGL030           | 6               | 0                            | 2              | 9                                 | 18                               | 384                           | 768                 | 12                          |

| A3P060                            | AGL060           | 6               | 12                           | 4              | 9                                 | 36                               | 384                           | 1,536               | 12                          |

| A3P125                            | AGL125           | 6               | 12                           | 8              | 9                                 | 72                               | 384                           | 3,072               | 12                          |

| A3P250/L                          | AGL250           | 6               | 12                           | 8              | 9                                 | 72                               | 768                           | 6,144               | 24                          |

| A3P400                            | AGL400           | 6               | 12                           | 12             | 9                                 | 108                              | 768                           | 9,216               | 24                          |

| A3P600/L                          | AGL600           | 6               | 12                           | 12             | 9                                 | 108                              | 1,152                         | 13,824              | 36                          |

| A3P1000/L                         | AGL1000          | 6               | 12                           | 16             | 9                                 | 144                              | 1,536                         | 24,576              | 48                          |

| A3PE600/L                         | AGLE600          | 6               | 12                           | 12             | 9                                 | 108                              | 1,120                         | 13,440              | 35                          |

| A3PE1500                          |                  | 6               | 12                           | 20             | 9                                 | 180                              | 1,888                         | 37,760              | 59                          |

| A3PE3000/L                        | AGLE3000         | 6               | 12                           | 28             | 9                                 | 252                              | 2,656                         | 74,368              | 83                          |

## **Fusion CCC Locations**

Fusion devices have six CCCs: one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-17 and Figure 4-18). The device can have one integrated PLL in the middle of the west side of the device or two integrated PLLs in the middle of the east and west sides of the device (middle right and middle left).

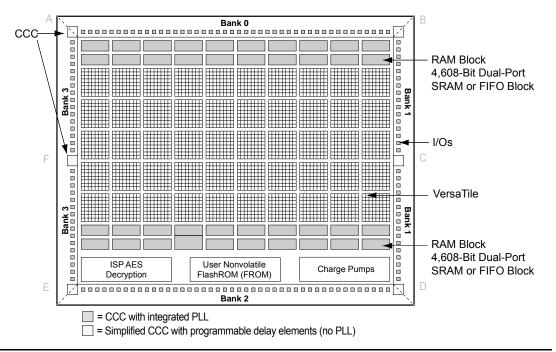

Figure 4-17 • CCC Locations in Fusion Family Devices (AFS090, AFS250, M1AFS250)

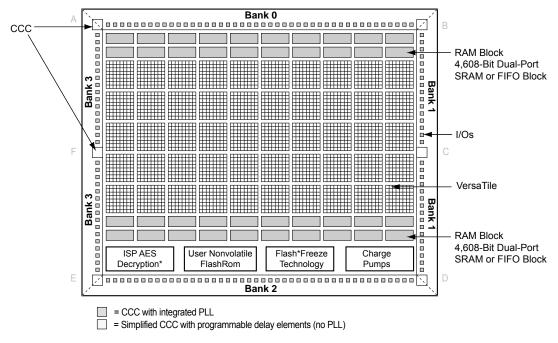

Figure 4-18 • CCC Locations in Fusion Family Devices (except AFS090, AFS250, M1AFS250)

Table 4-18 • Fusion Dynamic CCC Division by Half Configuration

| OADIVHALF /<br>OBDIVHALF /<br>OCDIVHALF | OADIV<4:0> /<br>OBDIV<4:0> /<br>OCDIV<4:0><br>(in decimal) | Divider Factor | Input Clock<br>Frequency | Output Clock<br>Frequency (MHz)   |

|-----------------------------------------|------------------------------------------------------------|----------------|--------------------------|-----------------------------------|

| 1                                       | 2                                                          | 1.5            | 100 MHz RC               | 66.7                              |

|                                         | 4                                                          | 2.5            | Oscillator               | 40.0                              |

|                                         | 6                                                          | 3.5            |                          | 28.6                              |

|                                         | 8                                                          | 4.5            |                          | 22.2                              |

|                                         | 10                                                         | 5.5            |                          | 18.2                              |

|                                         | 12                                                         | 6.5            |                          | 15.4                              |

|                                         | 14                                                         | 7.5            |                          | 13.3                              |

|                                         | 16                                                         | 8.5            |                          | 11.8                              |

|                                         | 18                                                         | 9.5            |                          | 10.5                              |

|                                         | 20                                                         | 10.5           |                          | 9.5                               |

|                                         | 22                                                         | 11.5           |                          | 8.7                               |

|                                         | 24                                                         | 12.5           |                          | 8.0                               |

|                                         | 26                                                         | 13.5           |                          | 7.4                               |

|                                         | 28                                                         | 14.5           |                          | 6.9                               |

| 0                                       | 0–31                                                       | 1–32           | Other Clock Sources      | Depends on other divider settings |

Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families

|                   |               | VCOSEL[2:1]   |               |               |               |               |               |               |  |

|-------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--|

|                   | 00            |               | O             | 01            |               | 10            |               | 11            |  |

| Voltage           | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) |  |

| IGLOO and IGLOO   | PLUS          |               |               |               |               |               |               |               |  |

| 1.2 V ± 5%        | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 160           |  |

| 1.5 V ± 5%        | 24            | 43.75         | 30            | 87.5          | 60            | 175           | 135           | 250           |  |

| ProASIC3L, RT Pro | ASIC3, and    | Military Pro  | ASIC3/L       | •             |               | •             | •             |               |  |

| 1.2 V ± 5%        | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 250           |  |

| 1.5 V ± 5%        | 24            | 43.75         | 30            | 70            | 60            | 175           | 135           | 350           |  |

| ProASIC3 and Fusi | ion           |               |               |               |               |               |               | •             |  |

| 1.5 V ± 5%        | 24            | 43.75         | 33.75         | 87.5          | 67.5          | 175           | 135           | 350           |  |

Table 4-20 • Configuration Bit <74> / VCOSEL<0> Selection for All Families

| VCOSEL[0] | Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0         | Fast PLL lock acquisition time with high tracking jitter. Refer to the corresponding datasheet for specific value and definition. |

| 1         | Slow PLL lock acquisition time with low tracking jitter. Refer to the corresponding datasheet for specific value and definition.  |

DEVICE\_INFO displays the FlashROM content, serial number, Design Name, and checksum, as shown below:

```

EXPORT IDCODE[32] = 123261CF

EXPORT SILSIG[32] = 00000000

User information:

CHECKSUM: 61A0

Design Name:

Programming Method: STAPL

Algorithm Version: 1

Programmer: UNKNOWN

_____

FlashROM Information :

______

Security Setting :

Encrypted FlashROM Programming Enabled.

Encrypted FPGA Array Programming Enabled.

```

The Libero SoC file manager recognizes the UFC and MEM files and displays them in the appropriate view. Libero SoC also recognizes the multiple programming files if you choose the option to generate multiple files for multiple FlashROM contents in Designer. These features enable a user-friendly flow for the FlashROM generation and programming in Libero SoC.

# **Custom Serialization Using FlashROM**

You can use FlashROM for device serialization or inventory control by using the Auto Inc region or Read From File region. FlashPoint will automatically generate the serial number sequence for the Auto Inc region with the **Start Value**, **Max Value**, and **Step Value** provided. If you have a unique serial number generation scheme that you prefer, the Read From File region allows you to import the file with your serial number scheme programmed into the region. See the *FlashPro User's Guide* for custom serialization file format information.

The following steps describe how to perform device serialization or inventory control using FlashROM:

- Generate FlashROM using SmartGen. From the Properties section in the FlashROM Settings dialog box, select the **Auto Inc** or **Read From File** region. For the Auto Inc region, specify the desired step value. You will not be able to modify this value in the FlashPoint software.

- 2. Go through the regular design flow and finish place-and-route.

- 3. Select **Programming File in Designer** and open **Generate Programming File** (Figure 5-12 on page 128).

- 4. Click **Program FlashROM**, browse to the UFC file, and click **Next**. The FlashROM Settings window appears, as shown in Figure 5-13 on page 128.

- 5. Select the FlashROM page you want to program and the data value for the configured regions. The STAPL file generated will contain only the data that targets the selected FlashROM page.

- 6. Modify properties for the serialization.

- For the Auto Inc region, specify the Start and Max values.

- For the Read From File region, select the file name of the custom serialization file.

- 7. Select the FlashROM programming file type you want to generate from the two options below:

- Single programming file for all devices: generates one programming file with all FlashROM values.

- One programming file per device: generates a separate programming file for each FlashROM value.

- 8. Enter the number of devices you want to program and generate the required programming file.

- 9. Open the programming software and load the programming file. The programming software, FlashPro3 and Silicon Sculptor II, supports the device serialization feature. If, for some reason, the device fails to program a part during serialization, the software allows you to reuse or skip the serial data. Refer to the FlashPro User's Guide for details.

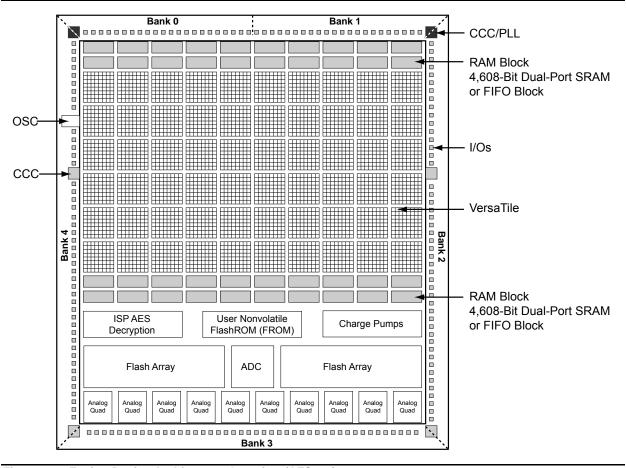

Figure 6-2 • Fusion Device Architecture Overview (AFS600)

## **SRAM and FIFO Architecture**

To meet the needs of high-performance designs, the memory blocks operate strictly in synchronous mode for both read and write operations. The read and write clocks are completely independent, and each can operate at any desired frequency up to 250 MHz.

- 4k×1, 2k×2, 1k×4, 512×9 (dual-port RAM—2 read / 2 write or 1 read / 1 write)

- 512×9, 256×18 (2-port RAM—1 read / 1 write)

- Sync write, sync pipelined / nonpipelined read

Automotive ProASIC3 devices support single-port SRAM capabilities or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). The Libero SoC software macro libraries support a dual-port macro only. For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

The memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY).

Simultaneous dual-port read/write and write/write operations at the same address are allowed when certain timing requirements are met.

During RAM operation, addresses are sourced by the user logic, and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes.

The low power flash device architecture enables the read and write sizes of RAMs to be organized independently, allowing for bus conversion. For example, the write size can be set to 256×18 and the read size to 512×9.

Both the write width and read width for the RAM blocks can be specified independently with the WW (write width) and RW (read width) pins. The different D×W configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1. When widths of one, two, or four are selected, the ninth bit is unused. For example, when writing nine-bit values and reading four-bit values, only the first four bits and the second four bits of each nine-bit value are addressable for read operations. The ninth bit is not accessible.

Conversely, when writing four-bit values and reading nine-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

# **Memory Blocks and Macros**

Memory blocks can be configured with many different aspect ratios, but are generically supported in the macro libraries as one of two memory elements: RAM4K9 or RAM512X18. The RAM4K9 is configured as a true dual-port memory block, and the RAM512X18 is configured as a two-port memory block. Dual-port memory allows the RAM to both read from and write to either port independently. Two-port memory allows the RAM to read from one port and write to the other using a common clock or independent read and write clocks. If needed, the RAM4K9 blocks can be configured as two-port memory blocks. The memory block can be configured as a FIFO by combining the basic memory block with dedicated FIFO controller logic. The FIFO macro is named FIFO4KX18 (Figure 6-3 on page 136).

Clocks for the RAM blocks can be driven by the VersaNet (global resources) or by regular nets. When using local clock segments, the clock segment region that encompasses the RAM blocks can drive the RAMs. In the dual-port configuration (RAM4K9), each memory block port can be driven by either rising-edge or falling-edge clocks. Each port can be driven by clocks with different edges. Though only a rising-edge clock can drive the physical block itself, the Microsemi Designer software will automatically bubble-push the inversion to properly implement the falling-edge trigger for the RAM block.

Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

#### **BLKA and BLKB**

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

#### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

## **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### **WMODEA** and **WMODEB**

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

#### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 139).

Note: For timing diagrams of the RAM signals, refer to the appropriate family datasheet.

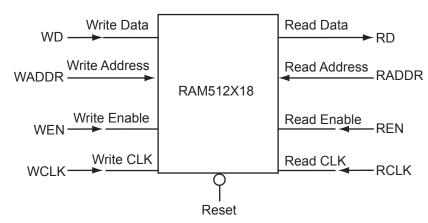

Figure 6-5 • 512X18 Two-Port RAM Block Diagram

#### Signal Descriptions for RAM512X18

RAM512X18 has slightly different behavior from RAM4K9, as it has dedicated read and write ports.

#### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 6-5).

Table 6-5 • Aspect Ratio Settings for WW[1:0]

| WW[1:0] | RW[1:0] | D×W      |

|---------|---------|----------|

| 01      | 01      | 512×9    |

| 10      | 10      | 256×18   |

| 00, 11  | 00, 11  | Reserved |

#### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512×9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, RD[17:9] are undefined.

#### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256×18 aspect ratio is used for write or read, WADDR[8] and RADDR[8] are unused and must be grounded.

#### WCLK and RCLK

These signals are the write and read clocks, respectively. They can be clocked on the rising or falling edge of WCLK and RCLK.

#### WEN and REN

These signals are the write and read enables, respectively. They are both active-low by default. These signals can be configured as active-high.

#### **RESET**

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

## **PIPE**

This signal is used to specify pipelined read on the output. A LOW on PIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

recommended, since it reduces the complexity of the user interface block and the board-level JTAG driver.

Moreover, using an internal counter for address generation speeds up the initialization procedure, since the user only needs to import the data through the JTAG port.

The designer may use different methods to select among the multiple RAM blocks. Using counters along with demultiplexers is one approach to set the write enable signals. Basically, the number of RAM blocks needing initialization determines the most efficient approach. For example, if all the blocks are initialized with the same data, one enable signal is enough to activate the write procedure for all of them at the same time. Another alternative is to use different opcodes to initialize each memory block. For a small number of RAM blocks, using counters is an optimal choice. For example, a ring counter can be used to select from multiple RAM blocks. The clock driver of this counter needs to be controlled by the address generation process.

Once the addressing of one block is finished, a clock pulse is sent to the (ring) counter to select the next memory block.

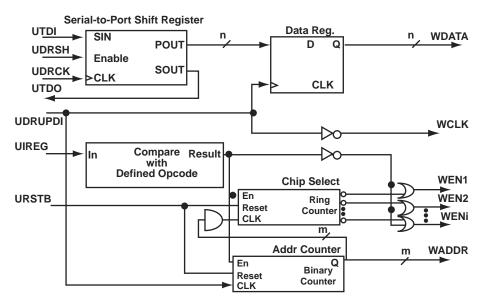

Figure 6-9 illustrates a simple block diagram of an interface block between UJTAG and RAM blocks.

Figure 6-9 • Block Diagram of a Sample User Interface

In the circuit shown in Figure 6-9, the shift register is enabled by the UDRSH output of the UJTAG macro. The counters and chip select outputs are controlled by the value of the TAP Instruction Register. The comparison block compares the UIREG value with the "start initialization" opcode value (defined by the user). If the result is true, the counters start to generate addresses and activate the WEN inputs of appropriate RAM blocks.

The UDRUPD output of the UJTAG macro, also shown in Figure 6-9, is used for generating the write clock (WCLK) and synchronizing the data register and address counter with WCLK. UDRUPD is HIGH when the TAP Controller is in the Data Register Update state, which is an indication of completing the loading of one data word. Once the TAP Controller goes into the Data Register Update state, the UDRUPD output of the UJTAG macro goes HIGH. Therefore, the pipeline register and the address counter place the proper data and address on the outputs of the interface block. Meanwhile, WCLK is defined as the inverted UDRUPD. This will provide enough time (equal to the UDRUPD HIGH time) for the data and address to be placed at the proper ports of the RAM block before the rising edge of WCLK. The inverter is not required if the RAM blocks are clocked at the falling edge of the write clock. An example of this is described in the "Example of RAM Initialization" section on page 150.

I/O Software Control in Low Power Flash Devices

#### **Output Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The **Special** variation has Width, Technology, Output Drive, and Slew Rate options.

#### **Bidirectional Buffers**

There are two variations: Regular and Special.

The **Regular** variation has Enable Polarity (Active High, Active Low) in addition to the Width option.

The **Special** variation has Width, Technology, Output Drive, Slew Rate, and Resistor Pull-Up/-Down options.

#### **Tristate Buffers**

Same as Bidirectional Buffers.

#### DDR

There are eight variations: DDR with Regular Input Buffers, Special Input Buffers, Regular Output Buffers, Special Output Buffers, Regular Tristate Buffers, Special Tristate Buffers, Regular Bidirectional Buffers, and Special Bidirectional Buffers.

These variations resemble the options of the previous I/O macro. For example, the Special Input Buffers variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options. DDR is not available on IGLOO PLUS devices.

- 4. Once the desired configuration is selected, click the **Generate** button. The Generate Core window opens (Figure 8-4).

- 5. Enter a name for the macro. Click **OK**. The core will be generated and saved to the appropriate location within the project files (Figure 8-5 on page 191).

## Figure 8-4 • Generate Core Window

6. Instantiate the I/O macro in the top-level code.

The user must instantiate the DDR\_REG or DDR\_OUT macro in the design. Use SmartGen to generate both these macros and then instantiate them in your top level. To combine the DDR macros with the I/O, the following rules must be met:

I/O Software Control in Low Power Flash Devices

#### I/O Function

Figure 8-8 shows an example of the I/O Function table included in the I/O bank report:

## Figure 8-8 • I/O Function Table

This table lists the number of input I/Os, output I/Os, bidirectional I/Os, and differential input and output I/O pairs that use I/O and DDR registers.

Note: IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Certain rules must be met to implement registered and DDR I/O functions (refer to the I/O Structures section of the handbook for the device you are using and the "DDR" section on page 190).

## I/O Technology

The I/O Technology table (shown in Figure 8-9) gives the values of VCCI and VREF (reference voltage) for all the I/O standards used in the design. The user should assign these voltages appropriately.

Figure 8-9 • I/O Technology Table

DDR for Microsemi's Low Power Flash Devices

# **Instantiating DDR Registers**

Using SmartGen is the simplest way to generate the appropriate RTL files for use in the design. Figure 9-4 shows an example of using SmartGen to generate a DDR SSTL2 Class I input register. SmartGen provides the capability to generate all of the DDR I/O cells as described. The user, through the graphical user interface, can select from among the many supported I/O standards. The output formats supported are Verilog, VHDL, and EDIF.

Figure 9-5 on page 211 through Figure 9-8 on page 214 show the I/O cell configured for DDR using SSTL2 Class I technology. For each I/O standard, the I/O pad is buffered by a special primitive that indicates the I/O standard type.

Figure 9-4 • Example of Using SmartGen to Generate a DDR SSTL2 Class I Input Register

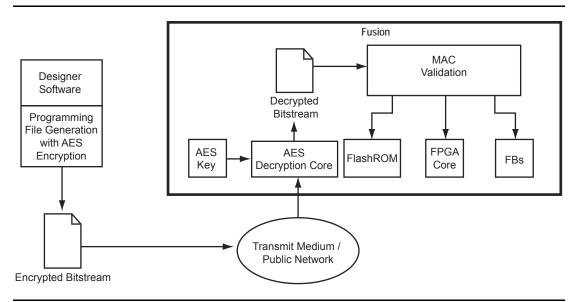

Figure 11-5 • Example Application Scenario Using AES in Fusion Devices

## **FlashLock**

#### **Additional Options for IGLOO and ProASIC3 Devices**

The user also has the option of prohibiting Write operations to the FPGA array but allowing Verify operations on the FPGA array and/or Read operations on the FlashROM without the use of the FlashLock Pass Key. This option provides the user the freedom of verifying the FPGA array and/or reading the FlashROM contents after the device is programmed, without having to provide the FlashLock Pass Key. The user can incorporate AES encryption on the programming files to better enhance the level of security used.

# **Permanent Security Setting Options**

In applications where a permanent lock is not desired, yet the security settings should not be modifiable, IGLOO and ProASIC3 devices can accommodate this requirement.

This application is particularly useful in cases where a device is located at a remote location and must be reprogrammed with a design or data update. Refer to the "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 244 for further discussion and examples of how this can be achieved.

The user must be careful when considering the Permanent FlashLock or Permanent Security Settings option. Once the design is programmed with the permanent settings, it is not possible to reconfigure the security settings already employed on the device. Therefore, exercise careful consideration before programming permanent settings.

#### Permanent FlashLock

The purpose of the permanent lock feature is to provide the benefits of the highest level of security to IGLOO and ProASIC3 devices. If selected, the permanent FlashLock feature will create a permanent barrier, preventing any access to the contents of the device. This is achieved by permanently disabling Write and Verify access to the array, and Write and Read access to the FlashROM. After permanently locking the device, it has been effectively rendered one-time-programmable. This feature is useful if the intended applications do not require design or system updates to the device.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

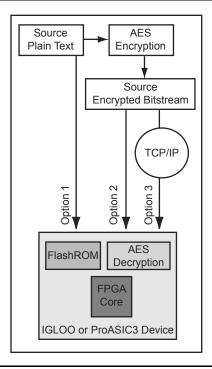

Figure 12-2 shows different applications for ISP programming.

- 1. In a trusted programming environment, you can program the device using the unencrypted (plaintext) programming file.

- 2. You can program the AES Key in a trusted programming environment and finish the final programming in an untrusted environment using the AES-encrypted (cipher text) programming file.

- 3. For the remote ISP updating/reprogramming, the AES Key stored in the device enables the encrypted programming bitstream to be transmitted through the untrusted network connection.

Microsemi low power flash devices also provide the unique Microsemi FlashLock feature, which protects the Pass Key and AES Key. Unless the original FlashLock Pass Key is used to unlock the device, security settings cannot be modified. Microsemi does not support read-back of FPGA core-programmed data; however, the FlashROM contents can selectively be read back (or disabled) via the JTAG port based on the security settings established by the Microsemi Designer software. Refer to the "Security in Low Power Flash Devices" section on page 235 for more information.

Figure 12-2 • Different ISP Use Models

# **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

# **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 15-2).

Table 15-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

# **Boundary Scan Chain**

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 15-2 on page 294), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 15-3 on page 294

# 16 – UJTAG Applications in Microsemi's Low Power Flash Devices

## Introduction

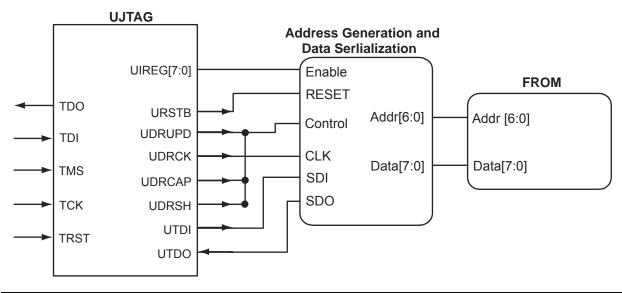

In Fusion, IGLOO, and ProASIC3 devices, there is bidirectional access from the JTAG port to the core VersaTiles during normal operation of the device (Figure 16-1). User JTAG (UJTAG) is the ability for the design to use the JTAG ports for access to the device for updates, etc. While regular JTAG is used, the UJTAG tiles, located at the southeast area of the die, are directly connected to the JTAG Test Access Port (TAP) Controller in normal operating mode. As a result, all the functional blocks of the device, such as Clock Conditioning Circuits (CCCs) with PLLs, SRAM blocks, embedded FlashROM, flash memory blocks, and I/O tiles, can be reached via the JTAG ports. The UJTAG functionality is available by instantiating the UJTAG macro directly in the source code of a design. Access to the FPGA core VersaTiles from the JTAG ports enables users to implement different applications using the TAP Controller (JTAG port). This document introduces the UJTAG tile functionality and discusses a few application examples. However, the possible applications are not limited to what is presented in this document. UJTAG can serve different purposes in many designs as an elementary or auxiliary part of the design. For detailed usage information, refer to the "Boundary Scan in Low Power Flash Devices" section on page 291.

Figure 16-1 • Block Diagram of Using UJTAG to Read FlashROM Contents

Power-Up/-Down Behavior of Low Power Flash Devices

# **Related Documents**

## **Datasheets**

ProASIC3 Flash Family FPGAs

http://www.microsemi.com/soc/documents/PA3\_DS.pdf

ProASIC3E Flash Family FPGAs

http://www.microsemi.com/soc/documents/PA3E\_DS.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                           | Page |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to the document as supported device types.                                                                                                                                                                                        |      |

| v1.1<br>(October 2008)  | The "Introduction" section was updated to add Military ProASIC3EL and RT ProASIC3 devices to the list of devices that can have inputs driven in while the device is not powered.                                                                                                  | 307  |

|                         | The "Flash Devices Support Power-Up Behavior" section was revised to include new families and make the information more concise.                                                                                                                                                  | 308  |

|                         | The "Cold-Sparing" section was revised to add Military ProASIC3/EL and RT ProASIC3 devices to the lists of devices with and without cold-sparing support.                                                                                                                         | 316  |

|                         | The "Hot-Swapping" section was revised to add Military ProASIC3/EL and RT ProASIC3 devices to the lists of devices with and without hot-swap support. AGL400 was added to the list of devices that do not support hot-swapping.                                                   | 317  |

| v1.0<br>(August 2008)   | This document was revised, renamed, and assigned a new part number. It now includes data for the IGLOO and ProASIC3L families.                                                                                                                                                    | N/A  |

| v1.3<br>(March 2008)    | The "List of Changes" section was updated to include the three different I/O Structure handbook chapters.                                                                                                                                                                         | 318  |

| v1.2<br>(February 2008) | The first sentence of the "PLL Behavior at Brownout Condition" section was updated to read, "When PLL power supply voltage and/or $V_{CC}$ levels drop below the VCC brownout levels (0.75 V $\pm$ 0.25 V), the PLL output lock signal goes low and/or the output clock is lost." | 315  |

| v1.1<br>(January 2008)  | The "PLL Behavior at Brownout Condition" section was added.                                                                                                                                                                                                                       | 315  |

# *Microsemi*

Index

| architecture of user nonvolatile 117 configuration 120 custom serialization 129 design flow 124 generation 125 programming and accessing 122 programming file 127 programming files 267 SmartGen 126 FlashROM read-back 305 | ISP 223, 224 architecture 261 board-level considerations 271 circuit 277 microprocessor 283  J JTAG 1532 261 JTAG interface 285 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| G                                                                                                                                                                                                                           | L                                                                                                                               |

| global architecture 31                                                                                                                                                                                                      | layout                                                                                                                          |

| global buffers                                                                                                                                                                                                              | device-specific 78                                                                                                              |

| no programmable delays 64                                                                                                                                                                                                   | LTC3025 linear voltage regulator 277                                                                                            |

| with PLL function 67                                                                                                                                                                                                        |                                                                                                                                 |

| with programmable delays 64                                                                                                                                                                                                 | M                                                                                                                               |

| global macros                                                                                                                                                                                                               | MAC validation/authentication 288                                                                                               |

| Synplicity 50                                                                                                                                                                                                               | macros                                                                                                                          |

| globals                                                                                                                                                                                                                     | CLKBUF 77                                                                                                                       |

| designer flow 53                                                                                                                                                                                                            | CLKBUF_LVDS/LVPECL 77                                                                                                           |

| networks 58                                                                                                                                                                                                                 | CLKDLY 65, 73                                                                                                                   |

| spines and rows 41                                                                                                                                                                                                          | FIFO4KX18 141                                                                                                                   |

| ·                                                                                                                                                                                                                           | PLL 73                                                                                                                          |

| Н                                                                                                                                                                                                                           | PLL macro signal descriptions 68                                                                                                |

| HLD code                                                                                                                                                                                                                    | RAM4K9 137                                                                                                                      |

| instantiating 192                                                                                                                                                                                                           | RAM512X18 139                                                                                                                   |

| hot-swap 167                                                                                                                                                                                                                | supported basic RAM macros 136<br>UJTAG 299                                                                                     |

| hot-swapping 317                                                                                                                                                                                                            |                                                                                                                                 |

|                                                                                                                                                                                                                             | MCU FPGA programming model 286 memory availability 146                                                                          |

| I                                                                                                                                                                                                                           | memory blocks 135                                                                                                               |

| I/O banks                                                                                                                                                                                                                   | microprocessor programming 283                                                                                                  |

| standards 40                                                                                                                                                                                                                | Microsemi SoC Products Group                                                                                                    |

| standards compatibility 162                                                                                                                                                                                                 | email 321                                                                                                                       |

| I/O standards 77                                                                                                                                                                                                            | web-based technical support 321                                                                                                 |

| global macros 46                                                                                                                                                                                                            | website 321                                                                                                                     |

| single-ended 166                                                                                                                                                                                                            | WODONG 021                                                                                                                      |

| I/Os                                                                                                                                                                                                                        | 0                                                                                                                               |

| assigning technologies 198                                                                                                                                                                                                  | OTP 223                                                                                                                         |

| assignments defined in PDC file 193                                                                                                                                                                                         | output slew rate 175                                                                                                            |

| automatically assigning 202                                                                                                                                                                                                 | output siew rate 175                                                                                                            |

| behavior at power-up/-down 311                                                                                                                                                                                              | D                                                                                                                               |

| board-level considerations 181                                                                                                                                                                                              | P                                                                                                                               |

| buffer schematic cell 191                                                                                                                                                                                                   | PDC                                                                                                                             |

| cell architecture 207                                                                                                                                                                                                       | global promotion and demotion 51                                                                                                |

| configuration with SmartGen 188                                                                                                                                                                                             | place-and-route 193                                                                                                             |

| features 163, 164, 167                                                                                                                                                                                                      | PLL                                                                                                                             |

| global, naming 35                                                                                                                                                                                                           | behavior at brownout condition 315 configuration bits 90                                                                        |

| manually assigning technologies 198 nano standard 162                                                                                                                                                                       | corniguration bits 90 core specifications 84                                                                                    |

| register combining 174                                                                                                                                                                                                      | dynamic PLL configuration 87                                                                                                    |

| simplified buffer circuitry 165                                                                                                                                                                                             | functional description 85                                                                                                       |

| software support 177                                                                                                                                                                                                        | power supply decoupling scheme 112                                                                                              |

| software-controlled attributes 187                                                                                                                                                                                          | PLL block signals 68                                                                                                            |

| user I/O assignment flow chart 185                                                                                                                                                                                          | PLL macro block diagram 69                                                                                                      |

| user naming convention 178                                                                                                                                                                                                  | product support                                                                                                                 |

| wide range support 166                                                                                                                                                                                                      | customer service 321                                                                                                            |

|                                                                                                                                                                                                                             |                                                                                                                                 |

| email 321 My Cases 322 outside the U.S. 322 | spine assignment 52 SRAM features 137               |

|---------------------------------------------|-----------------------------------------------------|

| technical support 321 website 321           | initializing 148<br>software support 154            |

| programmers 225                             | usage 141                                           |

| device support 228                          | SSOs 176                                            |

| programming                                 | STAPL player 285                                    |

| AES encryption 253                          | STAPL vs. DirectC 287                               |

| basics 223                                  | switching circuit 278                               |

| features 223                                | verification 278                                    |

| file header definition 257                  |                                                     |

| flash and antifuse 225                      | synthesizing 192                                    |

| flash devices 223                           | <del>T</del>                                        |

| glossary 258                                | T                                                   |

| guidelines for flash programming 229        | TAP controller state machine 291, 300               |

| header pin numbers 270                      | tech support                                        |

| microprocessor 283                          | ITAR 322                                            |

| power supplies 263                          | My Cases 322                                        |

| security 247                                | outside the U.S. 322                                |

| solution 268                                | technical support 321                               |

| solutions 227                               | transient current                                   |

| voltage 263                                 | VCC 310                                             |

| volume services 226                         | VCCI 310                                            |

| programming support 221                     | transient current, power-up/-down 309               |

| R                                           | U                                                   |

| RAM                                         | UJTAG                                               |

| memory block consumption 147                | CCC dynamic reconfiguration 302                     |

| remote upgrade via TCP/IP 288               | fine tuning 303                                     |

| routing structure 18                        | macro 299                                           |

|                                             | operation 300                                       |

| S                                           | port usage 301                                      |

|                                             | use to read FlashROM contents 297                   |

| Schmitt trigger 174                         | ultra-fast local lines 18                           |

| security 264                                |                                                     |

| architecture 237                            | V                                                   |

| encrypted programming 288 examples 242      | variable aspect ratio and cascading 145             |

| features 238                                | VersaNet global networks 33                         |

| FlashLock 241                               | VersaTile 15                                        |

| FlashROM 121                                | very-long-line resources 19                         |

| FlashROM use models 245                     | ViewDraw 191                                        |

| in programmable logic 235                   | VREF pins                                           |

| overview 235                                | manually assigning 199                              |

| signal integrity problem 271                | , , , , , , , , , , , , , , , , , , ,               |

| silicon testing 304                         | W                                                   |

| single tile designs 159                     | weak pull-down 175                                  |

| SmartGen 154                                | weak pull-uowii 175<br>weak pull-up 175             |

| spine architecture 41                       | weak pull-up 175<br>web-based technical support 321 |

|                                             | web-based technical support 321                     |

|                                             |                                                     |