Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 18432                                                                       |

| Number of I/O                  | 71                                                                          |

| Number of Gates                | 60000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                    |

| Supplier Device Package        | 100-VQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-z2vqg100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FPGA Array Architecture in Low Power Flash Devices

# **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

Table 1-1 • Flash-Based FPGAs

| Series    | Family*              | Description                                                                                                                                                                                    |

|-----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO®    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|           | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|           | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|           | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC®3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|           | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|           | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|           | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|           | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|           | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|           | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion    | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# 2 – Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs

## Introduction

The demand for low power systems and semiconductors, combined with the strong growth observed for value-based FPGAs, is driving growing demand for low power FPGAs. For portable and battery-operated applications, power consumption has always been the greatest challenge. The battery life of a system and on-board devices has a direct impact on the success of the product. As a result, FPGAs used in these applications should meet low power consumption requirements.

ProASIC® 3/E and ProASIC3 nano FPGAs offer low power consumption capability inherited from their nonvolatile and live-at-power-up (LAPU) flash technology. This application note describes the power consumption and how to use different power saving modes to further reduce power consumption for power-conscious electronics design.

# **Power Consumption Overview**

In evaluating the power consumption of FPGA technologies, it is important to consider it from a system point of view. Generally, the overall power consumption should be based on static, dynamic, inrush, and configuration power. Few FPGAs implement ways to reduce static power consumption utilizing sleep modes.

SRAM-based FPGAs use volatile memory for their configuration, so the device must be reconfigured after each power-up cycle. Moreover, during this initialization state, the logic could be in an indeterminate state, which might cause inrush current and power spikes. More complex power supplies are required to eliminate potential system power-up failures, resulting in higher costs. For portable electronics requiring frequent power-up and -down cycles, this directly affects battery life, requiring more frequent recharging or replacement.

SRAM-Based FPGA Total Power Consumption = P<sub>static</sub> + P<sub>dynamic</sub> + P<sub>inrush</sub> + P<sub>config</sub>

EQ 1

ProASIC3/E Total Power Consumption = P<sub>static</sub> + P<sub>dvnamic</sub>

EQ2

Unlike SRAM-based FPGAs, Microsemi flash-based FPGAs are nonvolatile and do not require power-up configuration. Additionally, Microsemi nonvolatile flash FPGAs are live at power-up and do not require additional support components. Total power consumption is reduced as the inrush current and configuration power components are eliminated.

Note that the static power component can be reduced in flash FPGAs (such as the ProASIC3/E devices) by entering User Low Static mode or Sleep mode. This leads to an extremely low static power component contribution to the total system power consumption.

The following sections describe the usage of Static (Idle) mode to reduce the power component, User Low Static mode to reduce the static power component, and Sleep mode and Shutdown mode to achieve a range of power consumption when the FPGA or system is idle. Table 2-1 on page 22 summarizes the different low power modes offered by ProASIC3/E devices.

Table 2-1 • ProASIC3/E/nano Low Power Modes Summary

| Mode          | Power Supplies / Clock Status                                                                                                                                                                      | Needed to Start Up                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Active        | On – All, clock                                                                                                                                                                                    | N/A (already active)                                       |

|               | Off – None                                                                                                                                                                                         |                                                            |

| Static (Idle) | On – All                                                                                                                                                                                           | Initiate clock source.                                     |

|               | Off – No active clock in FPGA                                                                                                                                                                      | No need to initialize volatile contents.                   |

|               | Optional: Enter User Low Static (Idle) Mode by enabling ULSICC macro to further reduce power consumption by powering down FlashROM.                                                                |                                                            |

| Sleep         | On – VCCI                                                                                                                                                                                          | Need to turn on core.                                      |

|               | Off – VCC (core voltage), VJTAG (JTAG DC voltage), and VPUMP (programming voltage)                                                                                                                 | Load states from external memory.                          |

|               | LAPU enables immediate operation when power returns.                                                                                                                                               | As needed, restore volatile contents from external memory. |

|               | Optional: Save state of volatile contents in external memory.                                                                                                                                      |                                                            |

| Shutdown      | On – None                                                                                                                                                                                          | Need to turn on VCC, VCCI.                                 |

|               | Off – All power supplies                                                                                                                                                                           |                                                            |

|               | Applicable to all ProASIC3 nano devices, cold-sparing and hot-insertion allow the device to be powered down without bringing down the system. LAPU enables immediate operation when power returns. |                                                            |

# Static (Idle) Mode

In Static (Idle) mode, the clock inputs are not switching and the static power consumption is the minimum power required to keep the device powered up. In this mode, I/Os are only drawing the minimum leakage current specified in the datasheet. Also, in Static (Idle) mode, embedded SRAM, I/Os, and registers retain their values, so the device can enter and exit this mode without any penalty.

If the embedded PLLs are used as the clock source, Static (Idle) mode can be entered easily by pulling LOW the PLL POWERDOWN pin (active-low). By pulling the PLL POWERDOWN pin to LOW, the PLL is turned off. Refer to Figure 2-1 on page 23 for more information.

# 3 – Global Resources in Low Power Flash Devices

## Introduction

IGLOO, Fusion, and ProASIC3 FPGA devices offer a powerful, low-delay VersaNet global network scheme and have extensive support for multiple clock domains. In addition to the Clock Conditioning Circuits (CCCs) and phase-locked loops (PLLs), there is a comprehensive global clock distribution network called a VersaNet global network. Each logical element (VersaTile) input and output port has access to these global networks. The VersaNet global networks can be used to distribute low-skew clock signals or high-fanout nets. In addition, these highly segmented VersaNet global networks contain spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside their region. This allows users the flexibility to create low-skew local clock networks using spines. This document describes VersaNet global networks and discusses how to assign signals to these global networks and spines in a design flow. Details concerning low power flash device PLLs are described in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 61. This chapter describes the low power flash devices' global architecture and uses of these global networks in designs.

## **Global Architecture**

Low power flash devices offer powerful and flexible control of circuit timing through the use of global circuitry. Each chip has up to six CCCs, some with PLLs.

- In IGLOOe, ProASIC3EL, and ProASIC3E devices, all CCCs have PLLs—hence, 6 PLLs per device (except the PQ208 package, which has only 2 PLLs).

- In IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, and ProASIC3L devices, the west CCC contains a PLL core (except in 10 k through 30 k devices).

- In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.

Refer to Table 4-6 on page 84 for details. Each PLL includes delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three chip global lines on each side of the chip (six chip global lines total). The CCCs at the four corners each have access to three quadrant global lines in each quadrant of the chip (except in 10 k through 30 k gate devices).

The nano 10 k, 15 k, and 20 k devices support four VersaNet global resources, and 30 k devices support six global resources. The 10 k through 30 k devices have simplified CCCs called CCC-GLs.

The flexible use of the VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Note: Microsemi recommends that you choose the appropriate global pin and use the appropriate global resource so you can realize these benefits.

The following sections give an overview of the VersaNet global network, the structure of the global network, access point for the global networks, and the clock aggregation feature that enables a design to have very low clock skew using spines.

Table 3-2 • Chip Global Pin Name

| I/O Type               | Beginning of I/O Name | Notes                                                        |

|------------------------|-----------------------|--------------------------------------------------------------|

| Single-Ended           | GFAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFA1/IOuxwByVz        | global at a time.                                            |

|                        | GFA2/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFB1/IOuxwByVz        | global at a time.                                            |

|                        | GFB2/IOuxwByVz        |                                                              |

|                        | GFC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GFC1/IOuxwByVz        | global at a time.                                            |

|                        | GFC2/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCA1/IOuxwByVz        | global at a time.                                            |

|                        | GCA2/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCB1/IOuxwByVz        | global at a time.                                            |

|                        | GCB2/IOuxwByVz        |                                                              |

|                        | GCC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a chip     |

|                        | GCC1/IOuxwByVz        | global at a time.                                            |

|                        | GCC2/IOuxwByVz        |                                                              |

| Differential I/O Pairs | GFAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFA1/IOuxwByVz        |                                                              |

|                        | GFBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFB1/IOuxwByVz        |                                                              |

|                        | GFCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GFC1/IOuxwByVz        |                                                              |

|                        | GCAO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCA1/IOuxwByVz        |                                                              |

|                        | GCBO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCB1/IOuxwByVz        |                                                              |

|                        | GCCO/IOuxwByVz        | The output of the different pair will drive the chip global. |

|                        | GCC1/IOuxwByVz        |                                                              |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

Table 3-3 • Quadrant Global Pin Name

| I/O Type     | Beginning of I/O Name | Notes                                                      |

|--------------|-----------------------|------------------------------------------------------------|

| Single-Ended | GAAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAA1/IOuxwByVz        | quadrant global at a time                                  |

|              | GAA2/IOuxwByVz        |                                                            |

|              | GABO/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAB1/IOuxwByVz        | quadrant global at a time.                                 |

|              | GAB2/IOuxwByVz        |                                                            |

|              | GAC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAC1/IOuxwByVz        | quadrant global at a time.                                 |

|              | GAC2/IOuxwByVz        |                                                            |

|              | GBAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBA1/IOuxwByVz        | at a time.                                                 |

|              | GBA2/IOuxwByVz        |                                                            |

|              | GBBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBB1/IOuxwByVz        | at a time.                                                 |

|              | GBB2/IOuxwByVz        |                                                            |

|              | GBC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBC1/IOuxwByVz        | at a time.                                                 |

|              | GBC2/IOuxwByVz        |                                                            |

|              | GDAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDA1/IOuxwByVz        | at a time.                                                 |

|              | GDA2/IOuxwByVz        |                                                            |

|              | GDBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDB1/IOuxwByVz        | at a time.                                                 |

|              | GDB2/IOuxwByVz        |                                                            |

|              | GDC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDC1/IOuxwByVz        | at a time.                                                 |

|              | GDC2/IOuxwByVz        |                                                            |

|              | GEAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEA1/IOuxwByVz        | at a time.                                                 |

|              | GEA2/IOuxwByVz        |                                                            |

|              | GEBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEB1/IOuxwByVz        | at a time.                                                 |

|              | GEB2/IOuxwByVz        |                                                            |

|              | GEC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEC1/IOuxwByVz        | at a time.                                                 |

|              | GEC2/IOuxwByVz        |                                                            |

| 1            | ĺ                     |                                                            |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

ProASIC3 nano FPGA Fabric User's Guide

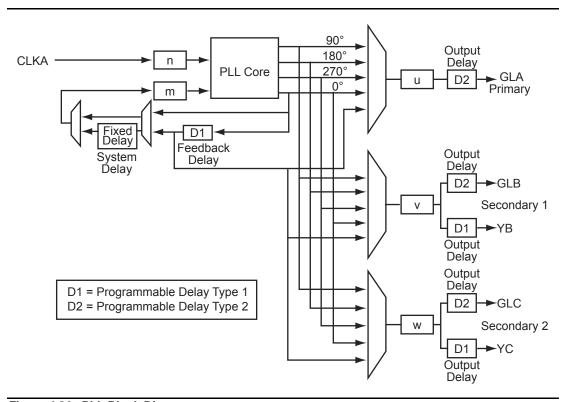

YB and YC are identical to GLB and GLC, respectively, with the exception of a higher selectable final output delay. The SmartGen PLL Wizard will configure these outputs according to user specifications and can enable these signals with or without the enabling of Global Output Clocks.

The above signals can be enabled in the following output groupings in both internal and external feedback configurations of the static PLL:

- · One output GLA only

- Two outputs GLA + (GLB and/or YB)

- Three outputs GLA + (GLB and/or YB) + (GLC and/or YC)

## **PLL Macro Block Diagram**

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global network access, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC).

There are delay elements in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven in the following ways:

- 1. By an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

- 2. Directly from the FPGA core.

- 3. From an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

During power-up, the PLL outputs will toggle around the maximum frequency of the voltage-controlled oscillator (VCO) gear selected. Toggle frequencies can range from 40 MHz to 250 MHz. This will continue as long as the clock input (CLKA) is constant (HIGH or LOW). This can be prevented by LOW assertion of the POWERDOWN signal.

The visual PLL configuration in SmartGen, a component of the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user.

#### External I/O Clock Source

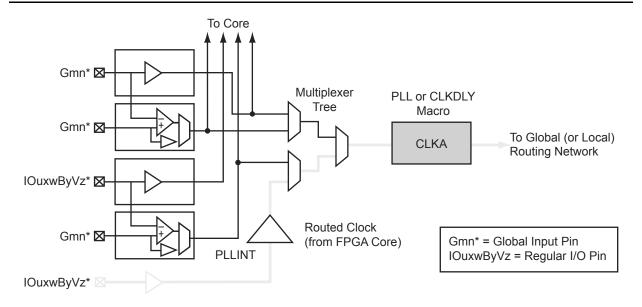

External I/O refers to regular I/O pins. The clock source is instantiated with one of the various INBUF options and accesses the CCCs via internal routing. The user has the option of assigning this input to any of the I/Os labeled with the I/O convention IOuxwByVz. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide, and for Fusion, refer to the Fusion Family of Mixed Signal FPGAs datasheet for more information. Figure 4-11 gives a brief explanation of external I/O usage. Choosing this option provides the freedom of selecting any user I/O location but introduces additional delay because the signal connects to the routed clock input through internal routing before connecting to the CCC reference clock input.

For the External I/O option, the routed signal would be instantiated with a PLLINT macro before connecting to the CCC reference clock input. This instantiation is conveniently done automatically by SmartGen when this option is selected. Microsemi recommends using the SmartGen tool to generate the CCC macro. The instantiation of the PLLINT macro results in the use of the routed clock input of the I/O to connect to the PLL clock input. If not using SmartGen, manually instantiate a PLLINT macro before the PLL reference clock to indicate that the regular I/O driving the PLL reference clock should be used (see Figure 4-11 for an example illustration of the connections, shown in red).

In the above two options, the clock source must be instantiated with one of the various INBUF macros. The reference clock pins of the CCC functional block core macros must be driven by regular input macros (INBUFs), not clock input macros.

Figure 4-11 • Illustration of External I/O Usage

For Fusion devices, the input reference clock can also be from the embedded RC oscillator and crystal oscillator. In this case, the CCC configuration is the same as the hardwired I/O clock source, and users are required to instantiate the RC oscillator or crystal oscillator macro and connect its output to the input reference clock of the CCC block.

difference will cause the VCO to increase its frequency until the output signal is phase-identical to the input after undergoing division. In other words, lock in both frequency and phase is achieved when the output frequency is M times the input. Thus, clock division in the feedback path results in multiplication at the output.

A similar argument can be made when the delay element is inserted into the feedback path. To achieve steady-state lock, the VCO output signal will be delayed by the input period *less* the feedback delay. For periodic signals, this is equivalent to time-advancing the output clock by the feedback delay.

Another key parameter of a PLL system is the acquisition time. Acquisition time is the amount of time it takes for the PLL to achieve lock (i.e., phase-align the feedback signal with the input reference clock). For example, suppose there is no voltage applied to the VCO, allowing it to operate at its free-running frequency. Should an input reference clock suddenly appear, a lock would be established within the maximum acquisition time.

# **Functional Description**

This section provides detailed descriptions of PLL block functionality: clock dividers and multipliers, clock delay adjustment, phase adjustment, and dynamic PLL configuration.

## **Clock Dividers and Multipliers**

The PLL block contains five programmable dividers. Figure 4-20 shows a simplified PLL block.

Figure 4-20 • PLL Block Diagram

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Dividers *n* and *m* (the input divider and feedback divider, respectively) provide integer frequency division factors from 1 to 128. The output dividers *u*, *v*, and *w* provide integer division factors from 1 to 32. Frequency scaling of the reference clock CLKA is performed according to the following formulas:

$$f_{GLA} = f_{CLKA} \times m / (n \times u) - GLA$$

Primary PLL Output Clock

EQ 4-1

$f_{GLB} = f_{YB} = f_{CLKA} \times m / (n \times v) - GLB$  Secondary 1 PLL Output Clock(s)

EQ 4-2

$f_{GLC} = f_{YC} = f_{CLKA} \times m / (n \times w) - GLC$  Secondary 2 PLL Output Clock(s)

EQ 4-3

SmartGen provides a user-friendly method of generating the configured PLL netlist, which includes automatically setting the division factors to achieve the closest possible match to the requested frequencies. Since the five output clocks share the *n* and *m* dividers, the achievable output frequencies are interdependent and related according to the following formula:

$$f_{GLA} = f_{GLB} \times (v / u) = f_{GLC} \times (w / u)$$

EQ 4-4

## **Clock Delay Adjustment**

There are a total of seven configurable delay elements implemented in the PLL architecture.

Two of the delays are located in the feedback path, entitled System Delay and Feedback Delay. System Delay provides a fixed delay of 2 ns (typical), and Feedback Delay provides selectable delay values from 0.6 ns to 5.56 ns in 160 ps increments (typical). For PLLs, delays in the feedback path will effectively advance the output signal from the PLL core with respect to the reference clock. Thus, the System and Feedback delays generate negative delay on the output clock. Additionally, each of these delays can be independently bypassed if necessary.

The remaining five delays perform traditional time delay and are located at each of the outputs of the PLL. Besides the fixed global driver delay of 0.755 ns for each of the global networks, the global multiplexer outputs (GLA, GLB, and GLC) each feature an additional selectable delay value, as given in Table 4-7.

Table 4-7 • Delay Values in Libero SoC Software per Device Family

| Device                | Typical | Starting Values | Increments | Ending Value |

|-----------------------|---------|-----------------|------------|--------------|

| ProASIC3              | 200 ps  | 0 to 735 ps     | 200 ps     | 6.735 ns     |

| IGLOO/ProASIC3L 1.5 V | 360 ps  | 0 to 1.610 ns   | 360 ps     | 12.410 ns    |

| IGLOO/ProASIC3L 1.2 V | 580 ps  | 0 to 2.880 ns   | 580 ps     | 20.280 ns    |

The additional YB and YC signals have access to a selectable delay from 0.6 ns to 5.56 ns in 160 ps increments (typical). This is the same delay value as the CLKDLY macro. It is similar to CLKDLY, which bypasses the PLL core just to take advantage of the phase adjustment option with the delay value.

The following parameters must be taken into consideration to achieve minimum delay at the outputs (GLA, GLB, GLC, YB, and YC) relative to the reference clock: routing delays from the PLL core to CCC outputs, core outputs and global network output delays, and the feedback path delay. The feedback path delay acts as a time advance of the input clock and will offset any delays introduced beyond the PLL core output. The routing delays are determined from back-annotated simulation and are configuration-dependent.

```

DYNCCC Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN), .GLA(GLA), .LOCK(LOCK),

.CLKB(CLKB), .GLB(GLB), .YB(), .CLKC(CLKC), .GLC(GLC), .YC(), .SDIN(SDIN),

.SCLK(SCLK), .SSHIFT(SSHIFT), .SUPDATE(SUPDATE), .MODE(MODE), .SDOUT(SDOUT),

.OADIV0(GND), .OADIV1(GND), .OADIV2(VCC), .OADIV3(GND), .OADIV4(GND), .OAMUX0(GND),

.OAMUX1(GND), .OAMUX2(VCC), .DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND),

.DLYGLA3(GND), .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND), .OBMUX2(GND), .DLYYB0(GND),

.DLYYB1(GND), .DLYYB2(GND), .DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND),

.DLYGLB1(GND), .DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

. \texttt{OCDIV1}(\texttt{GND}) \,, \, \, . \texttt{OCDIV2}(\texttt{GND}) \,, \, \, . \texttt{OCDIV3}(\texttt{GND}) \,, \, \, . \texttt{OCDIV4}(\texttt{GND}) \,, \, \, . \texttt{OCMUX0}(\texttt{GND}) \,, \, \, . \texttt{OCMUX1}(\texttt{GND}) \,, \, \, . \\

. \texttt{OCMUX2}(\texttt{GND}) \,, \; . \texttt{DLYYC0}(\texttt{GND}) \,, \; . \texttt{DLYYC1}(\texttt{GND}) \,, \; . \texttt{DLYYC2}(\texttt{GND}) \,, \; . \texttt{DLYYC3}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND})

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND), .DLYGLC4(GND),

.FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(VCC), .FINDIV3(GND), .FINDIV4(GND),

.FINDIV5(GND), .FINDIV6(GND), .FBDIV0(GND), .FBDIV1(GND), .FBDIV2(GND),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(VCC), .FBDIV6(GND), .FBDLY1(GND), .FBDLY1(GND),

.FBDLY2(GND), .FBDLY3(GND), .FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND),

.XDLYSEL(GND), .VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(VCC));

defparam Core.VCOFREQUENCY = 165.000;

```

endmodule

## **Delayed Clock Configuration**

The CLKDLY macro can be generated with the desired delay and input clock source (Hardwired I/O, External I/O, or Core Logic), as in Figure 4-28.

#### Figure 4-28 • Delayed Clock Configuration Dialog Box

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

: delay_macro

Name

Family

: ProASIC3

: Verilog

Output Format

: Delayed Clock

Type

Delay Index

CLKA Source

: Hardwired I/O

Total Clock Delay = 0.935 ns.

The resultant CLKDLY macro Verilog netlist is as follows:

module delay_macro(GL,CLK);

output GL;

input CLK;

```

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Detailed Usage Information**

## **Clock Frequency Synthesis**

Deriving clocks of various frequencies from a single reference clock is known as frequency synthesis. The PLL has an input frequency range from 1.5 to 350 MHz. This frequency is automatically divided down to a range between 1.5 MHz and 5.5 MHz by input dividers (not shown in Figure 4-19 on page 84) between PLL macro inputs and PLL phase detector inputs. The VCO output is capable of an output range from 24 to 350 MHz. With dividers before the input to the PLL core and following the VCO outputs, the VCO output frequency can be divided to provide the final frequency range from 0.75 to 350 MHz. Using SmartGen, the dividers are automatically set to achieve the closest possible matches to the specified output frequencies.

Users should be cautious when selecting the desired PLL input and output frequencies and the I/O buffer standard used to connect to the PLL input and output clocks. Depending on the I/O standards used for the PLL input and output clocks, the I/O frequencies have different maximum limits. Refer to the family datasheets for specifications of maximum I/O frequencies for supported I/O standards. Desired PLL input or output frequencies will not be achieved if the selected frequencies are higher than the maximum I/O frequencies allowed by the selected I/O standards. Users should be careful when selecting the I/O standards used for PLL input and output clocks. Performing post-layout simulation can help detect this type of error, which will be identified with pulse width violation errors. Users are strongly encouraged to perform post-layout simulation to ensure the I/O standard used can provide the desired PLL input or output frequencies. Users can also choose to cascade PLLs together to achieve the high frequencies needed for their applications. Details of cascading PLLs are discussed in the "Cascading CCCs" section on page 109.

In SmartGen, the actual generated frequency (under typical operating conditions) will be displayed beside the requested output frequency value. This provides the ability to determine the exact frequency that can be generated by SmartGen, in real time. The log file generated by SmartGen is a useful tool in determining how closely the requested clock frequencies match the user specifications. For example, assume a user specifies 101 MHz as one of the secondary output frequencies. If the best output frequency that could be achieved were 100 MHz, the log file generated by SmartGen would indicate the actual generated frequency.

#### Simulation Verification

The integration of the generated PLL and CLKDLY modules is similar to any VHDL component or Verilog module instantiation in a larger design; i.e., there is no special requirement that users need to take into account to successfully synthesize their designs.

For simulation purposes, users need to refer to the VITAL or Verilog library that includes the functional description and associated timing parameters. Refer to the Software Tools section of the Microsemi SoC Products Group website to obtain the family simulation libraries. If Designer is installed, these libraries are stored in the following locations:

```

<Designer_Installation_Directory>\lib\vtl\95\proasic3.vhd

<Designer_Installation_Directory>\lib\vtl\95\proasic3e.vhd

<Designer_Installation_Directory>\lib\vlog\proasic3.v

<Designer_Installation_Directory>\lib\vlog\proasic3e.v

```

For Libero users, there is no need to compile the simulation libraries, as they are conveniently precompiled in the  $ModelSim^{\mathbb{B}}$  Microsemi simulation tool.

# FlashROM Support in Flash-Based Devices

The flash FPGAs listed in Table 5-1 support the FlashROM feature and the functions described in this document.

Table 5-1 • Flash-Based FPGAs

| Series      | Family*              | Description                                                                                                                                                                                    |  |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO IGLOO |                      | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |

|             | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |

|             | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |

|             | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |

| ProASIC3    | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |

|             | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |

|             | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |

|             | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |

|             | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |

|             | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |

|             | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |

| Fusion      | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 5-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, ADDRB should be tied to ground.

Table 6-3 • Address Pins Unused/Used for Various Supported Bus Widths

|       | AD      | ADDRx  |  |  |

|-------|---------|--------|--|--|

| D×W   | Unused  | Used   |  |  |

| 4k×1  | None    | [11:0] |  |  |

| 2k×2  | [11]    | [10:0] |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |

Note: The "x" in ADDRx implies A or B.

#### **DINA and DINB**

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 6-4).

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, DINB should be tied to ground.

#### **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 6-4). The output data on unused pins is undefined.

Table 6-4 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

|       | DINx/D | DINx/DOUTx |  |  |

|-------|--------|------------|--|--|

| D×W   | Unused | Used       |  |  |

| 4k×1  | [8:1]  | [0]        |  |  |

| 2k×2  | [8:2]  | [1:0]      |  |  |

| 1k×4  | [8:4]  | [3:0]      |  |  |

| 512×9 | None   | [8:0]      |  |  |

Note: The "x" in DINx or DOUTx implies A or B.

## RAM512X18 Macro

RAM512X18 is the two-port configuration of the same RAM block (Figure 6-5 on page 140). Like the RAM4K9 nomenclature, the RAM512X18 nomenclature refers to both the deepest possible configuration and the widest possible configuration the two-port RAM block can assume. In two-port mode, the RAM block can be configured to either the 512×9 aspect ratio or the 256×18 aspect ratio. RAM512X18 is also fully synchronous and has the following features:

- · Dedicated read and write ports

- · Active-low read and write enables

- · Selectable pipelined or nonpipelined read

- · Active-low asynchronous reset

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

# 10 - Programming Flash Devices

## Introduction

This document provides an overview of the various programming options available for the Microsemi flash families. The electronic version of this document includes active links to all programming resources, which are available at http://www.microsemi.com/soc/products/hardware/default.aspx. For Microsemi antifuse devices, refer to the *Programming Antifuse Devices* document.

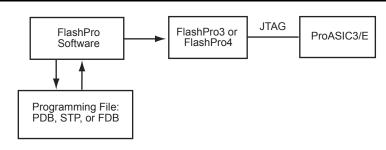

# **Summary of Programming Support**

FlashPro4 and FlashPro3 are high-performance in-system programming (ISP) tools targeted at the latest generation of low power flash devices offered by the SmartFusion, Fusion, IGLOO, and ProASIC affamilies, including ARM-enabled devices. FlashPro4 and FlashPro3 offer extremely high performance through the use of USB 2.0, are high-speed compliant for full use of the 480 Mbps bandwidth, and can program ProASIC3 devices in under 30 seconds. Powered exclusively via USB, FlashPro4 and FlashPro3 provide a VPUMP voltage of 3.3 V for programming these devices.

FlashPro4 replaced FlashPro3 in 2010. FlashPro4 supports SmartFusion, Fusion, ProASIC3, and IGLOO devices as well as future generation flash devices. FlashPro4 also adds 1.2 V programming for IGLOO nano V2 devices. FlashPro4 is compatible with FlashPro3; however it adds a programming mode (PROG\_MODE) signal to the previously unused pin 4 of the JTAG connector. The PROG\_MODE goes high during programming and can be used to turn on a 1.5 V external supply for those devices that require 1.5 V for programming. If both FlashPro3 and FlashPro4 programmers are used for programming the same boards, pin 4 of the JTAG connector must not be connected to anything on the board because FlashPro4 uses pin 4 for PROG\_MODE.

Figure 10-1 • FlashPro Programming Setup

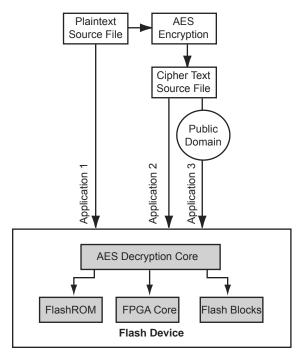

# **Security in Action**

This section illustrates some applications of the security advantages of Microsemi's devices (Figure 11-6).

Note: Flash blocks are only used in Fusion devices

Figure 11-6 • Security Options

#### Figure 11-19 • FlashLock Pass Key, Previously Programmed Devices

It is important to note that when the security settings need to be updated, the user also needs to select the **Security settings** check box in Step 1, as shown in Figure 11-10 on page 248 and Figure 11-11 on page 248, to modify the security settings. The user must consider the following:

- If only a new AES key is necessary, the user must re-enter the same Pass Key previously programmed into the device in Designer and then generate a programming file with the same Pass Key and a different AES key. This ensures the programming file can be used to access and program the device and the new AES key.

- If a new Pass Key is necessary, the user can generate a new programming file with a new Pass Key (with the same or a new AES key if desired). However, for programming, the user must first load the original programming file with the Pass Key that was previously used to unlock the device. Then the new programming file can be used to program the new security settings.

# **Advanced Options**

As mentioned, there may be applications where more complicated security settings are required. The "Custom Security Levels" section in the *FlashPro User's Guide* describes different advanced options available to aid the user in obtaining the best available security settings.

Security in Low Power Flash Devices

#### **STAPL File with AES Encryption**

- Does not contain AES key / FlashLock Key information

- Intended for transmission through web or service to unsecured locations for programming

```

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EF57";

NOTE "SAVE_DATA" "FROMStream";

NOTE "SECURITY" "ENCRYPT FROM CORE ";

NOTE "ALG_VERSION" "1";

NOTE "MAX_FREQ" "200000000";

NOTE "SILSIG" "$000000000";

```

## Conclusion

The new and enhanced security features offered in Fusion, IGLOO, and ProASIC3 devices provide state-of-the-art security to designs programmed into these flash-based devices. Microsemi low power flash devices employ the encryption standard used by NIST and the U.S. government—AES using the 128-bit Rijndael algorithm.

The combination of an on-chip AES decryption engine and FlashLock technology provides the highest level of security against invasive attacks and design theft, implementing the most robust and secure ISP solution. These security features protect IP within the FPGA and protect the system from cloning, wholesale "black box" copying of a design, invasive attacks, and explicit IP or data theft.

# **Glossary**

| Term                             | Explanation                                                                                                                                                                   |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Security Header programming file | Programming file used to program the FlashLock Pass Key and/or AES key into the device to secure the FPGA, FlashROM, and/or FBs.                                              |  |

| AES (encryption) key             | 128-bit key defined by the user when the AES encryption option is set in the Microsemi Designer software when generating the programming file.                                |  |

| FlashLock Pass Key               | 128-bit key defined by the user when the FlashLock option is set in the Microsemi Designe software when generating the programming file.                                      |  |

|                                  | The FlashLock Key protects the security settings programmed to the device. Once a device is programmed with FlashLock, whatever settings were chosen at that time are secure. |  |

| FlashLock                        | The combined security features that protect the device content from attacks. These feature are the following:                                                                 |  |

|                                  | Flash technology that does not require an external bitstream to program the device                                                                                            |  |

|                                  | FlashLock Pass Key that secures device content by locking the security settings and preventing access to the device as defined by the user                                    |  |

|                                  | AES key that allows secure, encrypted device reprogrammability                                                                                                                |  |

# References

National Institute of Standards and Technology. "ADVANCED ENCRYPTION STANDARD (AES) Questions and Answers." 28 January 2002 (10 January 2005).

See http://csrc.nist.gov/archive/aes/index1.html for more information.

# 13 – Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

## Introduction

The IGLOO<sup>®</sup> and ProASIC<sup>®</sup>3L families offer devices that can be powered by either 1.5 V or, in the case of V2 devices, a core supply voltage anywhere in the range of 1.2 V to 1.5 V, in 50 mV increments.

Since IGLOO and ProASIC3L devices are flash-based, they can be programmed and reprogrammed multiple times in-system using Microsemi FlashPro3. FlashPro3 uses the JTAG standard interface (IEEE 1149.1) and STAPL file (defined in JESD 71 to support programming of programmable devices using IEEE 1149.1) for in-system configuration/programming (IEEE 1532) of a device. Programming can also be executed by other methods, such as an embedded microcontroller that follows the same standards above.

All IGLOO and ProASIC3L devices must be programmed with the VCC core voltage at 1.5 V. Therefore, applications using IGLOO or ProASIC3L devices powered by a 1.2 V supply must switch the core supply to 1.5 V for in-system programming.

The purpose of this document is to describe an easy-to-use and cost-effective solution for switching the core supply voltage from 1.2 V to 1.5 V during in-system programming for IGLOO and ProASIC3L devices.

# **B** – Product Support

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

## **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 650.318.8044

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

## **Website**

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

# **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

#### **Email**

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc tech@microsemi.com.