Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 71                                                                         |

| Number of Gates                | 125000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn125-z2vq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 8  | I/O Software Control in Low Power Flash Devices                                          | 185 |

|----|------------------------------------------------------------------------------------------|-----|

|    | Flash FPGAs I/O Support                                                                  | 186 |

|    | Software-Controlled I/O Attributes                                                       | 187 |

|    | Implementing I/Os in Microsemi Software                                                  | 188 |

|    | Assigning Technologies and VREF to I/O Banks                                             | 198 |

|    | Conclusion                                                                               | 203 |

|    | Related Documents                                                                        | 203 |

|    | List of Changes                                                                          | 204 |

| 9  | DDR for Microsemi's Low Power Flash Devices                                              | 205 |

|    | Introduction                                                                             | 205 |

|    | Double Data Rate (DDR) Architecture                                                      |     |

|    | DDR Support in Flash-Based Devices                                                       |     |

|    | I/O Cell Architecture                                                                    |     |

|    | Input Support for DDR                                                                    |     |

|    | Output Support for DDR                                                                   |     |

|    | Instantiating DDR Registers                                                              |     |

|    | Design Example                                                                           |     |

|    | Conclusion                                                                               |     |

|    | List of Changes                                                                          |     |

|    | · · · · · · · · · · · · · · · · · · ·                                                    |     |

| 10 | Programming Flash Devices                                                                | 221 |

|    | Introduction                                                                             | 221 |

|    | Summary of Programming Support                                                           | 221 |

|    | Programming Support in Flash Devices                                                     | 222 |

|    | General Flash Programming Information                                                    | 223 |

|    | Important Programming Guidelines                                                         | 229 |

|    | Related Documents                                                                        | 231 |

|    | List of Changes                                                                          | 232 |

| 11 | Security in Low Power Flash Devices                                                      | 235 |

|    | Security in Programmable Logic                                                           | 235 |

|    | Security Support in Flash-Based Devices                                                  | 236 |

|    | Security Architecture                                                                    | 237 |

|    | Security Features                                                                        | 238 |

|    | Security in Action                                                                       | 242 |

|    | FlashROM Security Use Models                                                             | 245 |

|    | Generating Programming Files                                                             | 247 |

|    | Conclusion                                                                               | 258 |

|    | Glossary                                                                                 | 258 |

|    | References                                                                               | 258 |

|    | Related Documents                                                                        | 259 |

|    | List of Changes                                                                          | 259 |

| 12 | In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X. | 261 |

|    | Introduction                                                                             | 261 |

|    | ISP Architecture                                                                         | 261 |

|    | ISP Support in Flash-Based Devices                                                       | 262 |

|    | Programming Voltage (VPUMP) and VJTAG                                                    | 263 |

|    | Nonvolatile Memory (NVM) Programming Voltage                                             | 263 |

# **Spine Architecture**

The low power flash device architecture allows the VersaNet global networks to be segmented. Each of these networks contains spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside its region. The nine spines available in a vertical column reside in global networks with two separate regions of scope: the quadrant global network, which has three spines, and the chip (main) global network, which has six spines. Note that the number of quadrant globals and globals/spines per tree varies depending on the specific device. Refer to Table 3-4 for the clocking resources available for each device. The spines are the vertical branches of the global network tree, shown in Figure 3-3 on page 34. Each spine in a vertical column of a chip (main) global network is further divided into two spine segments of equal lengths: one in the top and one in the bottom half of the die (except in 10 k through 30 k gate devices).

Top and bottom spine segments radiating from the center of a device have the same height. However, just as in the ProASIC family, signals assigned only to the top and bottom spine cannot access the middle two rows of the die. The spines for quadrant clock networks do not cross the middle of the die and cannot access the middle two rows of the architecture.

Each spine and its associated ribs cover a certain area of the device (the "scope" of the spine; see Figure 3-3 on page 34). Each spine is accessed by the dedicated global network MUX tree architecture, which defines how a particular spine is driven—either by the signal on the global network from a CCC, for example, or by another net defined by the user. Details of the chip (main) global network spine-selection MUX are presented in Figure 3-8 on page 44. The spine drivers for each spine are located in the middle of the die.

Quadrant spines can be driven from user I/Os or an internal signal from the north and south sides of the die. The ability to drive spines in the quadrant global networks can have a significant effect on system performance for high-fanout inputs to a design. Access to the top quadrant spine regions is from the top of the die, and access to the bottom quadrant spine regions is from the bottom of the die. The A3PE3000 device has 28 clock trees and each tree has nine spines; this flexible global network architecture enables users to map up to 252 different internal/external clocks in an A3PE3000 device.

Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices

| ProASIC3/<br>ProASIC3L<br>Devices | IGLOO<br>Devices | Chip<br>Globals | Quadrant<br>Globals<br>(4×3) | Clock<br>Trees | Globals/<br>Spines<br>per<br>Tree | Total<br>Spines<br>per<br>Device | VersaTiles<br>in Each<br>Tree | Total<br>VersaTiles | Rows<br>in<br>Each<br>Spine |

|-----------------------------------|------------------|-----------------|------------------------------|----------------|-----------------------------------|----------------------------------|-------------------------------|---------------------|-----------------------------|

| A3PN010                           | AGLN010          | 4               | 0                            | 1              | 0                                 | 0                                | 260                           | 260                 | 4                           |

| A3PN015                           | AGLN015          | 4               | 0                            | 1              | 0                                 | 0                                | 384                           | 384                 | 6                           |

| A3PN020                           | AGLN020          | 4               | 0                            | 1              | 0                                 | 0                                | 520                           | 520                 | 6                           |

| A3PN060                           | AGLN060          | 6               | 12                           | 4              | 9                                 | 36                               | 384                           | 1,536               | 12                          |

| A3PN125                           | AGLN125          | 6               | 12                           | 8              | 9                                 | 72                               | 384                           | 3,072               | 12                          |

| A3PN250                           | AGLN250          | 6               | 12                           | 8              | 9                                 | 72                               | 768                           | 6,144               | 24                          |

| A3P015                            | AGL015           | 6               | 0                            | 1              | 9                                 | 9                                | 384                           | 384                 | 12                          |

| A3P030                            | AGL030           | 6               | 0                            | 2              | 9                                 | 18                               | 384                           | 768                 | 12                          |

| A3P060                            | AGL060           | 6               | 12                           | 4              | 9                                 | 36                               | 384                           | 1,536               | 12                          |

| A3P125                            | AGL125           | 6               | 12                           | 8              | 9                                 | 72                               | 384                           | 3,072               | 12                          |

| A3P250/L                          | AGL250           | 6               | 12                           | 8              | 9                                 | 72                               | 768                           | 6,144               | 24                          |

| A3P400                            | AGL400           | 6               | 12                           | 12             | 9                                 | 108                              | 768                           | 9,216               | 24                          |

| A3P600/L                          | AGL600           | 6               | 12                           | 12             | 9                                 | 108                              | 1,152                         | 13,824              | 36                          |

| A3P1000/L                         | AGL1000          | 6               | 12                           | 16             | 9                                 | 144                              | 1,536                         | 24,576              | 48                          |

| A3PE600/L                         | AGLE600          | 6               | 12                           | 12             | 9                                 | 108                              | 1,120                         | 13,440              | 35                          |

| A3PE1500                          |                  | 6               | 12                           | 20             | 9                                 | 180                              | 1,888                         | 37,760              | 59                          |

| A3PE3000/L                        | AGLE3000         | 6               | 12                           | 28             | 9                                 | 252                              | 2,656                         | 74,368              | 83                          |

# **Using Clock Aggregation**

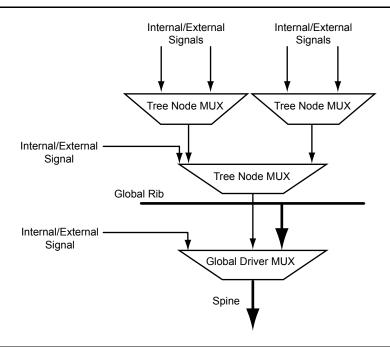

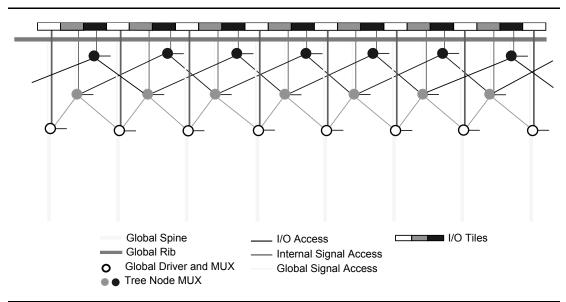

Clock aggregation allows for multi-spine clock domains to be assigned using hardwired connections, without adding any extra skew. A MUX tree, shown in Figure 3-8, provides the necessary flexibility to allow long lines, local resources, or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib in the center of the die, and also through local resources in the north and south ribs, allowing I/Os to feed directly into the clock system. As Figure 3-9 indicates, this access system is contiguous.

There is no break in the middle of the chip for the north and south I/O VersaNet access. This is different from the quadrant clocks located in these ribs, which only reach the middle of the rib.

Figure 3-8 • Spine Selection MUX of Global Tree

Figure 3-9 • Clock Aggregation Tree Architecture

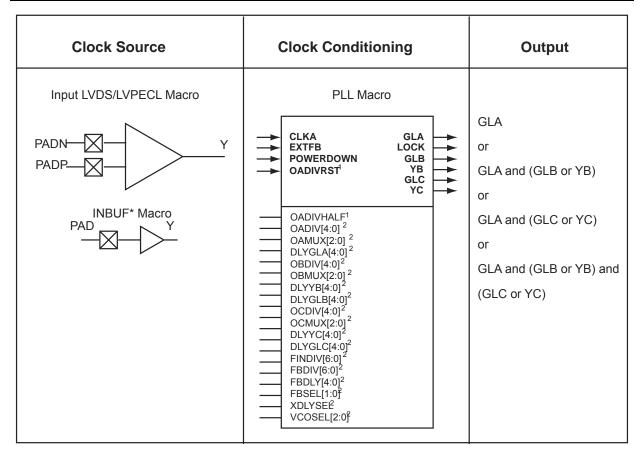

## **Global Buffers with PLL Function**

Clocks requiring frequency synthesis or clock adjustments can utilize the PLL core before connecting to the global / quadrant global networks. A maximum of 18 CCC global buffers can be instantiated in a device—three per CCC and up to six CCCs per device. Each PLL core can generate up to three global/quadrant clocks, while a clock delay element provides one.

The PLL functionality of the clock conditioning block is supported by the PLL macro.

#### Notes:

- 1. For Fusion only.

- 2. Refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide for more information.

- 3. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 4. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Figure 4-4 • CCC Options: Global Buffers with PLL

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL macro also provides power-down input and lock output signals. The additional inputs shown on the macro are configuration settings, which are configured through the use of SmartGen. For manual setting of these bits refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for details.

Figure 4-6 on page 71 illustrates the various clock output options and delay elements.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **PLL Macro Signal Descriptions**

The PLL macro supports two inputs and up to six outputs. Table 4-3 gives a description of each signal.

Table 4-3 • Input and Output Signals of the PLL Block

| Signal    | Name                                  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKA      | Reference Clock                       | Input  | Reference clock input for PLL core; input clock for primary output clock, GLA                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OADIVRST  | Reset Signal for the Output Divider A | Input  | For Fusion only. OADIVRST can be used when you bypass the PLL core (i.e., OAMUX = 001). The purpose of the OADIVRST signals is to reset the output of the final clock divider to synchronize it with the input to that divider when the PLL is bypassed. The signal is active on a low to high transition. The signal must be low for at least one divider input. If PLL core is used, this signal is "don't care" and the internal circuitry will generate the reset signal for the synchronization purpose. |

| OADIVHALF | Output A Division by<br>Half          | Input  | For Fusion only. Active high. Division by half feature. This feature can only be used when users bypass the PLL core (i.e., OAMUX = 001) and the RC Oscillator (RCOSC) drives the CLKA input. This can be used to divide the 100 MHz RC oscillator by a factor of 1.5, 2.5, 3.5, 4.5 14.5). Refer to Table 4-18 on page 95 for more information.                                                                                                                                                              |

| EXTFB     | External Feedback                     | Input  | Allows an external signal to be compared to a reference clock in the PLL core's phase detector.                                                                                                                                                                                                                                                                                                                                                                                                               |

| POWERDOWN | Power Down                            | Input  | Active low input that selects power-down mode and disables the PLL. With the POWERDOWN signal asserted, the PLL core sends 0 V signals on all of the outputs.                                                                                                                                                                                                                                                                                                                                                 |

| GLA       | Primary Output                        | Output | Primary output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GLB       | Secondary 1 Output                    | Output | Secondary 1 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YB        | Core 1 Output                         | Output | Core 1 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GLC       | Secondary 2 Output                    | Output | Secondary 2 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YC        | Core 2 Output                         | Output | Core 2 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LOCK      | PLL Lock Indicator                    | Output | Active high signal indicating that steady-state lock has been achieved between CLKA and the PLL feedback signal                                                                                                                                                                                                                                                                                                                                                                                               |

#### Input Clock

The inputs to the input reference clock (CLKA) of the PLL can come from global input pins, regular I/O pins, or internally from the core. For Fusion families, the input reference clock can also be from the embedded RC oscillator or crystal oscillator.

## **Global Output Clocks**

GLA (Primary), GLB (Secondary 1), and GLC (Secondary 2) are the outputs of Global Multiplexer 1, Global Multiplexer 2, and Global Multiplexer 3, respectively. These signals (GLx) can be used to drive the high-speed global and quadrant networks of the low power flash devices.

A global multiplexer block consists of the input routing for selecting the input signal for the GLx clock and the output multiplexer, as well as delay elements associated with that clock.

### **Core Output Clocks**

YB and YC are known as Core Outputs and can be used to drive internal logic without using global network resources. This is especially helpful when global network resources must be conserved and utilized for other timing-critical paths.

#### Figure 4-31 • Static Timing Analysis Using SmartTime

#### **Place-and-Route Stage Considerations**

Several considerations must be noted to properly place the CCC macros for layout.

For CCCs with clock inputs configured with the Hardwired I/O-Driven option:

- PLL macros must have the clock input pad coming from one of the GmA\* locations.

- CLKDLY macros must have the clock input pad coming from one of the Global I/Os.

If a PLL with a Hardwired I/O input is used at a CCC location and a Hardwired I/O–Driven CLKDLY macro is used at the same CCC location, the clock input of the CLKDLY macro must be chosen from one of the GmB\* or GmC\* pin locations. If the PLL is not used or is an External I/O–Driven or Core Logic–Driven PLL, the clock input of the CLKDLY macro can be sourced from the GmA\*, GmB\*, or GmC\* pin locations.

For CCCs with clock inputs configured with the External I/O–Driven option, the clock input pad can be assigned to any regular I/O location (IO\*\*\*\*\*\*\*\*\*\*\*\*\* pins). Note that since global I/O pins can also be used as regular I/Os, regardless of CCC function (CLKDLY or PLL), clock inputs can also be placed in any of these I/O locations.

By default, the Designer layout engine will place global nets in the design at one of the six chip globals. When the number of globals in the design is greater than six, the Designer layout engine will automatically assign additional globals to the quadrant global networks of the low power flash devices. If the user wishes to decide which global signals should be assigned to chip globals (six available) and which to the quadrant globals (three per quadrant for a total of 12 available), the assignment can be achieved with PinEditor, ChipPlanner, or by importing a placement constraint file. Layout will fail if the

FlashROM in Microsemi's Low Power Flash Devices

# FlashROM Applications

The SmartGen core generator is used to configure FlashROM content. You can configure each page independently. SmartGen enables you to create and modify regions within a page; these regions can be 1 to 16 bytes long (Figure 5-4).

|          |   | Byte Number in Page |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------|---|---------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|          |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| er       | 6 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| pe       | 5 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Numbe    | 4 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| (D)      | 3 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Pag      | 2 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| <u>a</u> | 1 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|          | 0 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Figure 5-4 • FlashROM Configuration

The FlashROM content can be changed independently of the FPGA core content. It can be easily accessed and programmed via JTAG, depending on the security settings of the device. The SmartGen core generator enables each region to be independently updated (described in the "Programming and Accessing FlashROM" section on page 122). This enables you to change the FlashROM content on a per-part basis while keeping some regions "constant" for all parts. These features allow the FlashROM to be used in diverse system applications. Consider the following possible uses of FlashROM:

- Internet protocol (IP) addressing (wireless or fixed)

- · System calibration settings

- Restoring configuration after unpredictable system power-down

- · Device serialization and/or inventory control

- · Subscription-based business models (e.g., set-top boxes)

- · Secure key storage

- · Asset management tracking

- · Date stamping

- · Version management

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

| Date                | Changes                                                                                                                                                                                                                                                                                                                | Page |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.1<br>(continued) | Table 6-1 • Flash-Based FPGAs and associated text were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                           | 134  |

|                     | The text introducing Table 6-8 • Memory Availability per IGLOO and ProASIC3 Device was updated to replace "A3P030 and AGL030" with "15 k and 30 k gate devices." Table 6-8 • Memory Availability per IGLOO and ProASIC3 Device was updated to remove AGL400 and AGLE1500 and include IGLOO PLUS and ProASIC3L devices. | 146  |

## I/O Architecture

#### I/O Tile

IGLOO and ProASIC3 nano devices utilize either a single-tile or dual-tile I/O architecture (Figure 7-1 on page 159 and Figure 7-2 on page 160). The 10 k, 15 k, and 20 k devices utilize the single-tile design and the 60 k, 125 k and 250 k devices utilize the dual-tile design. In both cases, the I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile can be used to support high-performance register inputs and outputs, with register enable if desired. For single-tile designs, all I/O registers share both the CLR and CLK ports, while for the dual-tile designs, the output register and output enable register share one CLK port. For the dual-tile designs, the registers can also be used to support the JESD-79C Double Data Rate (DDR) standard within the I/O structure (see the "DDR for Microsemi's Low Power Flash Devices" section on page 205 for more information).

#### I/O Registers

Each I/O module contains several input and output registers. Refer to Figure 7-3 on page 165 for a simplified representation of the I/O block. The number of input registers is selected by a set of switches (not shown in Figure 7-2 on page 160) between registers to implement single-ended data transmission to and from the FPGA core. The Designer software sets these switches for the user. For single-tile designs, a common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. The I/O register combining requires that no combinatorial logic be present between the register and the I/O.

#### **Power-Up Behavior**

Low power flash devices are power-up/-down friendly; i.e., no particular sequencing is required for power-up and power-down. This eliminates extra board components for power-up sequencing, such as a power-up sequencer.

During power-up, all I/Os are tristated, irrespective of I/O macro type (input buffers, output buffers, I/O buffers with weak pull-ups or weak pull-downs, etc.). Once I/Os become activated, they are set to the user-selected I/O macros. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 307 for details.

### **Drive Strength**

Low power flash devices have up to four programmable output drive strengths. The user can select the drive strength of a particular output in the I/O Attribute Editor or can instantiate a specialized I/O macro, such as OUTBUF\_S\_8 (slew = low, out\_drive = 8 mA).

The maximum available drive strength is 8 mA per I/O. Though no I/O should be forced to source or sink more than 8 mA indefinitely, I/Os may handle a higher amount of current (refer to the device IBIS model for maximum source/sink current) during signal transition (AC current). Every device package has its own power dissipation limit; hence, power calculation must be performed accurately to determine how much current can be tolerated per I/O within that limit.

### I/O Interfacing

Low power flash devices are 5 V-input- and 5 V-output-tolerant without adding any extra circuitry. Along with other low-voltage I/O macros, this 5 V tolerance makes these devices suitable for many types of board component interfacing.

Table 7-17 shows some high-level interfacing examples using low power flash devices.

Table 7-17 • nano High-Level Interface

|           | Clock    |           |       | I/O        |             |          |  |  |  |

|-----------|----------|-----------|-------|------------|-------------|----------|--|--|--|

| Interface | Туре     | Frequency | Туре  | Signals In | Signals Out | Data I/O |  |  |  |

| GM        | Src Sync | 125 MHz   | LVTTL | 8          | 8           | 125 Mbps |  |  |  |

| TBI       | Src Sync | 125 MHz   | LVTTL | 10         | 10          | 125 Mbps |  |  |  |

## Conclusion

IGLOO nano and ProASIC3 nano device support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The nano device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

I/O Software Control in Low Power Flash Devices

# Flash FPGAs I/O Support

The flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

Table 8-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |  |  |  |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IGLOO    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |  |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |  |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |  |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |  |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |  |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |  |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |  |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |  |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |  |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |  |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |  |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

3. Double-click I/O to open the Create Core window, which is shown in Figure 8-3).

#### Figure 8-3 • I/O Create Core Window

As seen in Figure 8-3, there are five tabs to configure the I/O macro: Input Buffers, Output Buffers, Bidirectional Buffers, Tristate Buffers, and DDR.

#### **Input Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The **Special** variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options (see Figure 8-3). All the I/O standards and supply voltages ( $V_{CCI}$ ) supported for the device family are available for selection.

I/O Software Control in Low Power Flash Devices

## **Automatically Assigning Technologies to I/O Banks**

The I/O Bank Assigner (IOBA) tool runs automatically when you run Layout. You can also use this tool from within the MultiView Navigator (Figure 8-17). The IOBA tool automatically assigns technologies and VREF pins (if required) to every I/O bank that does not currently have any technologies assigned to it. This tool is available when at least one I/O bank is unassigned.

To automatically assign technologies to I/O banks, choose I/O Bank Assigner from the **Tools** menu (or click the I/O Bank Assigner's toolbar button, shown in Figure 8-16).

#### Figure 8-16 • I/O Bank Assigner's Toolbar Button

Messages will appear in the Output window informing you when the automatic I/O bank assignment begins and ends. If the assignment is successful, the message "I/O Bank Assigner completed successfully" appears in the Output window, as shown in Figure 8-17.

Figure 8-17 • I/O Bank Assigner Displays Messages in Output Window

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                                                   | Page |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| August 2012             | The notes in Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666).                           | 187  |

| June 2011               | Figure 8-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.                                 | 188  |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                                                      | 199  |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                                              |      |

| July 2010               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                 | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 8-1 • Flash-Based FPGAs.                                                                                                                         | 186  |

|                         | The notes for Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.                             | 187  |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                                          | 186  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 8-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 186  |

| v1.1<br>(March 2008)    | This document was previously part of the I/O Structures in IGLOO and ProASIC3 Devices document. The content was separated and made into a new document.                                                   | N/A  |

|                         | Table 8-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                                                      | 187  |

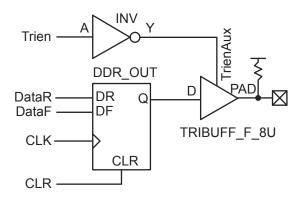

## **DDR Tristate Output Register**

module DDR\_TriStateBuf\_LVTTL\_8mA\_HighSlew\_LowEnb\_PullUp(DataR, DataF, CLR, CLK, Trien,

Figure 9-7 • DDR Tristate Output Register, LOW Enable, 8 mA, Pull-Up (LVTTL)

#### Verilog

```

DataR, DataF, CLR, CLK, Trien;

input

output PAD;

wire TrienAux, Q;

INV Inv_Tri(.A(Trien),.Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

TRIBUFF_F_8U TRIBUFF_F_8U_0_inst(.D(Q),.E(TrienAux),.PAD(PAD));

endmodule

VHDL

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; PAD : out std_logic);

end DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp;

architecture DEF_ARCH of DDR_TriStateBuf_LVTTL_8mA_HighSlew_LowEnb_PullUp is

component INV

port(A : in std_logic := 'U'; Y : out std_logic);

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component TRIBUFF_F_8U

port(D, E : in std_logic := 'U'; PAD : out std_logic);

end component;

signal TrienAux, Q : std_logic ;

begin

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

```

# **Generating Programming Files**

## Generation of the Programming File in a Trusted Environment— Application 1

As discussed in the "Application 1: Trusted Environment" section on page 243, in a trusted environment, the user can choose to program the device with plaintext bitstream content. It is possible to use plaintext for programming even when the FlashLock Pass Key option has been selected. In this application, it is not necessary to employ AES encryption protection. For AES encryption settings, refer to the next sections.

The generated programming file will include the security setting (if selected) and the plaintext programming file content for the FPGA array, FlashROM, and/or FBs. These options are indicated in Table 11-2 and Table 11-3.

Table 11-2 • IGLOO and ProASIC3 Plaintext Security Options, No AES

| Security Protection   | FlashROM Only | FPGA Core Only | Both FlashROM and FPGA |

|-----------------------|---------------|----------------|------------------------|

| No AES / no FlashLock | ✓             | ✓              | ✓                      |

| FlashLock only        | ✓             | ✓              | ✓                      |

| AES and FlashLock     | -             | -              | _                      |

Table 11-3 • Fusion Plaintext Security Options

| Security Protection   | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / no FlashLock | ✓             | ✓              | ✓            | ✓   |

| FlashLock             | ✓             | ✓              | ✓            | ✓   |

| AES and FlashLock     | -             | _              | -            | -   |

Note: For all instructions, the programming of Flash Blocks refers to Fusion only.

For this scenario, generate the programming file as follows:

Select the Silicon features to be programmed (Security Settings, FPGA Array, FlashROM, Flash Memory Blocks), as shown in Figure 11-10 on page 248 and Figure 11-11 on page 248. Click Next

If **Security Settings** is selected (i.e., the FlashLock security Pass Key feature), an additional dialog will be displayed to prompt you to select the security level setting. If no security setting is selected, you will be directed to Step 3.

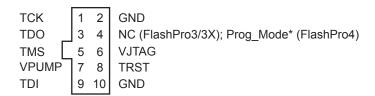

# **ISP Programming Header Information**

The FlashPro4/3/3X programming cable connector can be connected with a 10-pin, 0.1"-pitch programming header. The recommended programming headers are manufactured by AMP (103310-1) and 3M (2510-6002UB). If you have limited board space, you can use a compact programming header manufactured by Samtec (FTSH-105-01-L-D-K). Using this compact programming header, you are required to order an additional header adapter manufactured by Microsemi SoC Products Group (FP3-10PIN-ADAPTER-KIT).

Existing ProASICPLUS family customers who are using the Samtec Small Programming Header (FTSH-113-01-L-D-K) and are planning to migrate to IGLOO or ProASIC3 devices can also use FP3-10PIN-ADAPTER-KIT.

Table 12-3 • Programming Header Ordering Codes

| Manufacturer | Part Number           | Description                                                                                                                                                                                                                                                                                                                                        |

|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP          | 103310-1              | 10-pin, 0.1"-pitch cable header (right-angle PCB mount angle)                                                                                                                                                                                                                                                                                      |

| ЗМ           | 2510-6002UB           | 10-pin, 0.1"-pitch cable header (straight PCB mount angle)                                                                                                                                                                                                                                                                                         |

| Samtec       | FTSH-113-01-L-D-K     | Small programming header supported by FlashPro and Silicon Sculptor                                                                                                                                                                                                                                                                                |

| Samtec       | FTSH-105-01-L-D-K     | Compact programming header                                                                                                                                                                                                                                                                                                                         |

| Samtec       | FFSD-05-D-06.00-01-N  | 10-pin cable with 50 mil pitch sockets; included in FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                         |

| Microsemi    | FP3-10PIN-ADAPTER-KIT | Transition adapter kit to allow FP3 to be connected to a micro 10-pin header (50 mil pitch). Includes a 6 inch Samtec FFSD-05-D-06.00-01-N cable in the kit. The transition adapter board was previously offered as FP3-26PIN-ADAPTER and includes a 26-pin adapter for design transitions from ProASICPLUS based boards to ProASIC3 based boards. |

Note: \*Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 12-5 • Programming Header (top view)

ProASIC3 nano FPGA Fabric User's Guide

2. VCC rises to 1.5 V before programming begins.

#### Figure 13-3 • Programming Algorithm

The oscilloscope plot in Figure 13-3 shows a wider time interval for the programming algorithm and includes the TDI and TMS signals from the FlashPro3. These signals carry the programming information that is programmed into the device and should only start toggling after the  $V_{CC}$  core voltage reaches 1.5 V. Again, TRST from FlashPro3 and the  $V_{CC}$  core voltage of the IGLOO device are labeled. As shown in Figure 13-3, TDI and TMS are floating initially, and the core voltage is 1.2 V. When a programming command on the FlashPro3 is executed, TRST is driven HIGH and TDI is momentarily driven to ground. In response to the HIGH TRST signal, the circuit responds and pulls the core voltage to 1.5 V. After 100 ms, TRST is briefly driven LOW by the FlashPro software. This is expected behavior that ensures the device JTAG state machine is in Reset prior to programming. TRST remains HIGH for the duration of the programming. It can be seen in Figure 13-3 that the VCC core voltage signal remains at 1.5 V for approximately 50 ms before information starts passing through on TDI and TMS. This confirms that the voltage switching circuit drives the VCC core supply voltage to 1.5 V prior to programming.

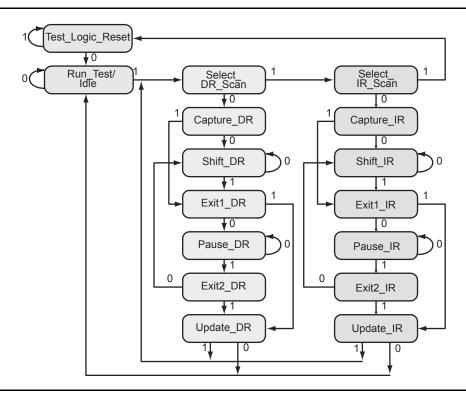

Figure 16-4 • TAP Controller State Diagram

#### **UJTAG Port Usage**

UIREG[7:0] hold the contents of the JTAG instruction register. The UIREG vector value is updated when the TAP Controller state machine enters the Update\_IR state. Instructions 16 to 127 are user-defined and can be employed to encode multiple applications and commands within an application. Loading new instructions into the UIREG vector requires users to send appropriate logic to TMS to put the TAP Controller in a full IR cycle starting from the Select IR Scan state and ending with the Update IR state.

UTDI, UTDO, and UDRCK are directly connected to the JTAG TDI, TDO, and TCK ports, respectively. The TDI input can be used to provide either data (TAP Controller in the Shift\_DR state) or the new contents of the instruction register (TAP Controller in the Shift\_IR state).

UDRSH, UDRUPD, and UDRCAP are HIGH when the TAP Controller state machine is in the Shift\_DR, Update\_DR, and Capture\_DR states, respectively. Therefore, they act as flags to indicate the stages of the data shift process. These flags are useful for applications in which blocks of data are shifted into the design from JTAG pins. For example, an active UDRSH can indicate that UTDI contains the data bitstream, and UDRUPD is a candidate for the end-of-data-stream flag.

As mentioned earlier, users should not connect the TDI, TDO, TCK, TMS, and TRST ports of the UJTAG macro to any port or net of the design netlist. The Designer software will automatically handle the port connection.