# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 68                                                                         |

| Number of Gates                | 250000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn250-z1vq100i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Microsemi

FPGA Array Architecture ibow Power Flash Devices

# **Related Documents**

## User s Guides

Designer User's Guide

http://www.microsemi.com//stocuments/designer\_ug.pdf

# List of Changes

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                         | Page             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| August 2012             | Thel/O State of Newly Shipped Devices" sectionmew (SAR 39542).                                                                                                                                                                                                                                                  | 14               |

| July 2010               | This chapter is no longer published <b>sepa</b> ly with its own part number and ve<br>but is now part of several FPGA fabric user s guides.                                                                                                                                                                     | rsioNn/A         |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added <b>Ta</b> ble 1-1 Flash-Based FPGAs.                                                                                                                                                                                                                            | 10               |

|                         | Figure 1-2 IGLOO and ProASIC3 nano Devé Architecture Overview with Two I<br>Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS device<br>throughFigure 1-5 IGLOO, IGLOO nano, Pr&SIC3 nano, and ProASIC3/L Device<br>Architecture Overview with Four I/O Banks (AGL600 device is shoevne)w. |                  |

|                         | Table 1-4 IGLOO nano and ProASIC3 nano Array Coordinatissnew.                                                                                                                                                                                                                                                   | 17               |

| v1.3<br>(October 2008)  | The title of this document was changeed "Core Architecture of IGLOO a ProASIC3 Devices" to "FPGA Array Ardhecture in Low Power Flash Devices."                                                                                                                                                                  | nd 9             |

|                         | The "FPGA Array Architectre Support" sectionwas revised to include new fami and make the information more concise.                                                                                                                                                                                              | lies 10          |

|                         | Table 1-2 IGLOO and ProASIC3 Array Coordinates as updated to include Milit ProASIC3/EL and RT ProASIC3 devices.                                                                                                                                                                                                 | ary 16           |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptionablen1-1 Flash-<br>Based FPGAs:<br>ProASIC3L was updated to include 1.5 V.<br>The number of PLLs for ProASIC3E was changed from five to six.                                                                                                           | 10               |

| v1.1<br>(March 2008)    | Table 1-1 Flash-Based FPGAs and the accompanying text was updated to in the IGLOO PLUS family. The "IGLOO Terminology" section and "Device Overview" sectionare new.                                                                                                                                            | cludêO           |

|                         | The "Device Overview" sectionwas updated to note that 15 k devices do support SRAM or FIFO.                                                                                                                                                                                                                     | o no <b>î</b> t1 |

|                         | Figure 1-6 IGLOO PLUS Device Architecture Overview with Four I/O Basen new.                                                                                                                                                                                                                                     | ks 13            |

|                         | Table 1-2 IGLOO and ProASIC3 Array Coordinates as updated to add A3PO and AGLO15.                                                                                                                                                                                                                               | 15 16            |

|                         | Table 1-3 IGLOO PLUS Array Coordinate is new.                                                                                                                                                                                                                                                                   | 16               |

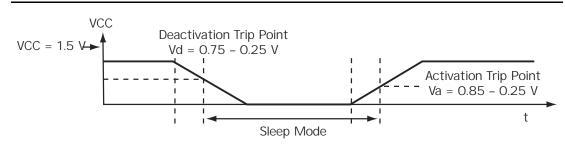

Figure 2-5 Entering and Exiting Sleep Mode Typical Timing Diagram

## Shutdown Mode

For all ProASIC3/E and ProASIC3 nano devices, slowery mode can be entered by turning off all power supplies when device functionality is not needed. Spating and hot-insertioneatures in ProASIC3 nano devices enable the device to be powered relavithout turning off the entire system. When power returns, the live at power-up features immediate operation of the device.

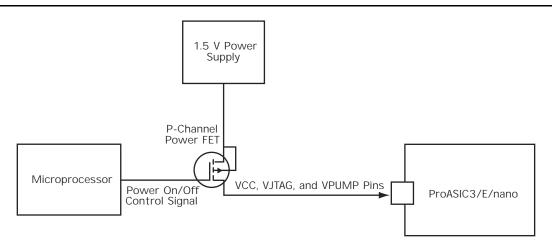

### Using Sleep Mode or Shutdown Mode in the System

Depending on the power supply and components used in an application, there are many ways to turn the power supplies connected to the ide on or off. For example gure 2-6 shows how a microprocessor is used to control a power FET. It is recommended to power FETs with low on resistance be used to perform the switching action.

Figure 2-6 Controlling Power On/Off State Ung Microprocessor and Power FET

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Recommended Board-Level Considerations**

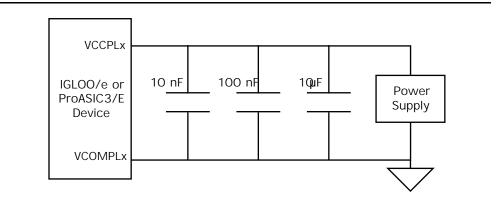

The power to the PLL core is supplied by VCCPLA/B/C/D/E/F (VCCPLx), and the associated ground connections are supplied by VOMPLA/B/C/D/E/F (VCOMPLx). When the PLLs are not used, the Designer place-and-route tool autatically disables the unused PLLto lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Optionally, the PLL can be turned on/off during normal device operation via the POWERDOWN port (Fature 4-3 on page 6)8

## PLL Power Supply Decoupling Scheme

The PLL core is designed to tolerate noise level\$h@nPLL power supply as specified in the datasheets. When operated within the noise limite; PLL will meet the outpuakpeo-peak jitter specifications specified in the datasheets. Us@pplications should always ensure the PLL power supply is powered from a noise-free or low-noise power source.

However, in situations where the PLL power supply theored is higher than the tolerable limits, various decoupling schemes can be designed to suppressend to the PLL power supply. An example is provided inFigure 4-38The VCCPLx and VCOMPLx pins correspond to the PLL analog power supply and ground.

Microsemi strongly recommends that ceramic capacitors (10 nF in parallel with 100 nF) be placed close to the power pins (less than 1 inch awaty) ird generic 10  $\mu$ F electrolytic capacitor is recommended for low-frequency noise and should be placed farther away due to its large physical size. Microsemi recommends that a 6.8  $\mu$ H inductor **beep**l between the supply source and the capacitors to filter out any low-/medium- and high-frequency **moissible** ition, the PCB layers should be controlled so the VCCPLx and VCOMPLx planes have the minimum separation possible, thus generating a good-quality RF capacitor.

For more recommendiatins, refer to the board-Level Consideration application note.

Recommended 100 nF capacitor:

Producer BC Components, type X7R, 100 nF, 16 V

BC Components part number: 0603B104K160BT

Digi-Key part number: BC1254CT-ND

Digi-Key part number: BC1254TR-ND

Recommended 10 nF capacitor:

Surface-mount ceramic capacitor

Producer BC Components, type X7R, 10 nF, 50 V

BC Components part number: 0603B103K500BT

Digi-Key part number: BC1252CT-ND

Digi-Key part number: BC1252TR-ND

Figure 4-38 Decoupling Scheme for One PLL (should be replicated for each PLL used)