Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 68                                                                        |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn250-zvq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

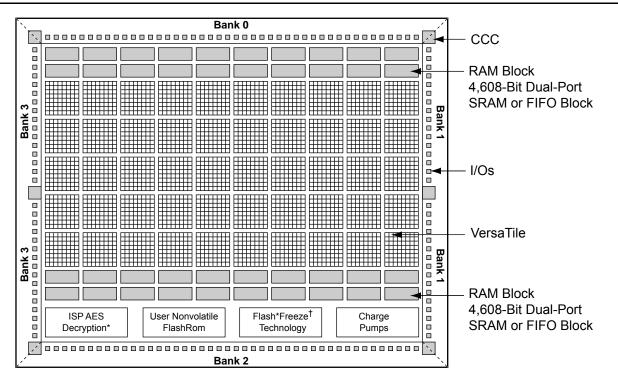

Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device Architecture Overview with Four I/O Banks (AGL600 device is shown)

Note: \* AGLP030 does not contain a PLL or support AES security.

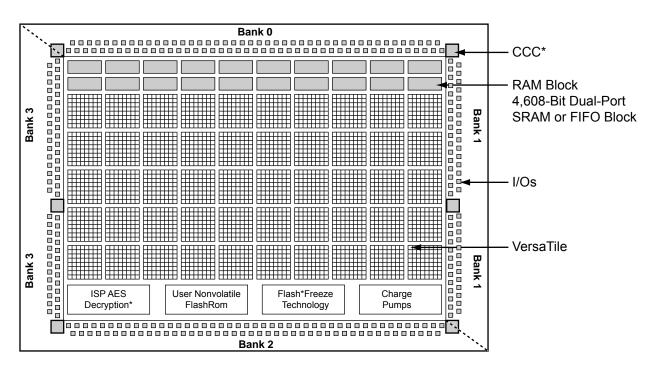

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

## Global Resources in Low Power Flash Devices

| Date                              | Changes                                                                                                                                                                                                                                                                                                              |        |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

| v1.1<br>(March 2008)              | The "Global Architecture" section was updated to include the IGLOO PLUS family. The bullet was revised to include that the west CCC does not contain a PLL core in 15 k and 30 k devices. Instances of "A3P030 and AGL030 devices" were replaced with "15 k and 30 k gate devices."                                  |        |  |

| v1.1<br>(continued)               | Table 3-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                    | 32     |  |

|                                   | The "VersaNet Global Network Distribution" section, "Spine Architecture" section, the note in Figure 3-1 • Overview of VersaNet Global Network and Device Architecture, and the note in Figure 3-3 • Simplified VersaNet Global Network (60 k gates and above) were updated to include mention of 15 k gate devices. | 33, 34 |  |

|                                   | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to add the A3P015 device, and to revise the values for clock trees, globals/spines per tree, and globals/spines per device for the A3P030 and AGL030 devices.                                                                             | 41     |  |

|                                   | Table 3-5 • Globals/Spines/Rows for IGLOO PLUS Devices is new.                                                                                                                                                                                                                                                       | 42     |  |

|                                   | CLKBUF_LVCMOS12 was added to Table 3-9 • I/O Standards within CLKBUF.                                                                                                                                                                                                                                                | 47     |  |

|                                   | The "User's Guides" section was updated to include the three different I/O Structures chapters for ProASIC3 and IGLOO device families.                                                                                                                                                                               | 58     |  |

| v1.0<br>(January 2008)            | Figure 3-3 • Simplified VersaNet Global Network (60 k gates and above) was updated.                                                                                                                                                                                                                                  | 34     |  |

|                                   | The "Naming of Global I/Os" section was updated.                                                                                                                                                                                                                                                                     | 35     |  |

|                                   | The "Using Global Macros in Synplicity" section was updated.                                                                                                                                                                                                                                                         | 50     |  |

|                                   | The "Global Promotion and Demotion Using PDC" section was updated.                                                                                                                                                                                                                                                   | 51     |  |

|                                   | The "Designer Flow for Global Assignment" section was updated.                                                                                                                                                                                                                                                       | 53     |  |

|                                   | The "Simple Design Example" section was updated.                                                                                                                                                                                                                                                                     | 55     |  |

| 51900087-0/1.05<br>(January 2005) | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated.                                                                                                                                                                                                                                          |        |  |

## **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

Table 4-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Table 4-9 to Table 4-15 on page 94 provide descriptions of the configuration data for the configuration bits.

#### Table 4-9 • Input Clock Divider, FINDIV[6:0] (/n)

| FINDIV<6:0> State | Divisor | New Frequency Factor |  |

|-------------------|---------|----------------------|--|

| 0                 | 1       | 1.00000              |  |

| 1                 | 2       | 0.50000              |  |

| :                 | :       | :                    |  |

| 127               | 128     | 0.0078125            |  |

## Table 4-10 • Feedback Clock Divider, FBDIV[6:0] (/m)

| FBDIV<6:0> State | Divisor | New Frequency Factor |  |  |

|------------------|---------|----------------------|--|--|

| 0                | 1       | 1                    |  |  |

| 1                | 2       | 2                    |  |  |

| :                | :       | :                    |  |  |

| 127              | 128     | 128                  |  |  |

#### **Table 4-11 • Output Frequency Dividers**

A Output Divider, OADIV <4:0> (/u);

B Output Divider, OBDIV <4:0> (/v);

C Output Divider, OCDIV <4:0> (/w)

| OADIV<4:0>; OBDIV<4:0>;<br>CDIV<4:0> State | Divisor | New Frequency Factor |

|--------------------------------------------|---------|----------------------|

| 0                                          | 1       | 1.00000              |

| 1                                          | 2       | 0.50000              |

| :                                          | i i     | i i                  |

| 31                                         | 32      | 0.03125              |

## Table 4-12 • MUXA, MUXB, MUXC

| OAMUX<2:0>; OBMUX<2:0>; OCMUX<2:0> State | MUX Input Selected                                                                                             |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 0                                        | None. Six-input MUX and PLL are bypassed. Clock passes only through global MUX and goes directly into HC ribs. |

| 1                                        | Not available                                                                                                  |

| 2                                        | PLL feedback delay line output                                                                                 |

| 3                                        | Not used                                                                                                       |

| 4                                        | PLL VCO 0° phase shift                                                                                         |

| 5                                        | PLL VCO 270° phase shift                                                                                       |

| 6                                        | PLL VCO 180° phase shift                                                                                       |

| 7                                        | PLL VCO 90° phase shift                                                                                        |

#### **External Feedback Configuration**

For certain applications, such as those requiring generation of PCB clocks that must be matched with existing board delays, it is useful to implement an external feedback, EXTFB. The Phase Detector of the PLL core will receive CLKA and EXTFB as inputs. EXTFB may be processed by the fixed System Delay element as well as the *M* divider element. The EXTFB option is currently not supported.

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

: test_pll

Family

: ProASIC3E

Output Format

: VHDL

: Static PLL

Type

Input Freq(MHz)

: 10.000

CLKA Source

: Hardwired I/O

Feedback Delay Value Index : 1

Feedback Mux Select : 2

XDLY Mux Select

: No

Primary Freq(MHz) : 3

Primary PhaseShift : 0

Primary Delay Value Index : 1

: 33.000

Primary Mux Select : 4

Secondaryl Freq(MHz) : 66.000

Use GLB

: YES

Use YB

: YES

: 1

GLB Delay Value Index

YB Delay Value Index

Secondaryl PhaseShift

Secondary1 Mux Select

Secondary2 Freq(MHz)

: 101.000

: YES

Use GLC

Use YC

: NO

GLC Delay Value Index

: 1

YC Delay Value Index

: 1

Secondary2 PhaseShift

: 0

Secondary2 Mux Select

Primary Clock frequency 33.333

Primary Clock Phase Shift 0.000

Primary Clock Output Delay from CLKA 0.180

Secondary1 Clock frequency 66.667

Secondaryl Clock Phase Shift 0.000

Secondaryl Clock Global Output Delay from CLKA 0.180

Secondaryl Clock Core Output Delay from CLKA 0.625

Secondary2 Clock frequency 100.000

Secondary2 Clock Phase Shift 0.000

Secondary2 Clock Global Output Delay from CLKA 0.180

```

Below is an example Verilog HDL description of a legal PLL core configuration generated by SmartGen:

```

module test_pll(POWERDOWN,CLKA,LOCK,GLA);

input POWERDOWN, CLKA;

output LOCK, GLA;

```

ProASIC3 nano FPGA Fabric User's Guide

• Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

Figure 4-33 • Quadrant Clock Assignment for a Global Net

#### External I/O-Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

#### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

## **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 110.

FlashROM in Microsemi's Low Power Flash Devices

Figure 5-12 shows the programming file generator, which enables different STAPL file generation methods. When you select **Program FlashROM** and choose the UFC file, the FlashROM Settings window appears, as shown in Figure 5-13. In this window, you can select the FlashROM page you want to program and the data value for the configured regions. This enables you to use a different page for different programming files.

Figure 5-12 • Programming File Generator

#### Figure 5-13 • Setting FlashROM during Programming File Generation

The programming hardware and software can load the FlashROM with the appropriate STAPL file. Programming software handles the single STAPL file that contains multiple FlashROM contents for multiple devices, and programs the FlashROM in sequential order (e.g., for device serialization). This feature is supported in the programming software. After programming with the STAPL file, you can run DEVICE\_INFO to check the FlashROM content.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## **Example of RAM Initialization**

This section of the document presents a sample design in which a 4×4 RAM block is being initialized through the JTAG port. A test feature has been implemented in the design to read back the contents of the RAM after initialization to verify the procedure.

The interface block of this example performs two major functions: initialization of the RAM block and running a test procedure to read back the contents. The clock output of the interface is either the write clock (for initialization) or the read clock (for reading back the contents). The Verilog code for the interface block is included in the "Sample Verilog Code" section on page 151.

For simulation purposes, users can declare the input ports of the UJTAG macro for easier assignment in the testbench. However, the UJTAG input ports should not be declared on the top level during synthesis. If the input ports of the UJTAG are declared during synthesis, the synthesis tool will instantiate input buffers on these ports. The input buffers on the ports will cause Compile to fail in Designer.

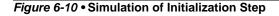

Figure 6-10 shows the simulation results for the initialization step of the example design.

The CLK\_OUT signal, which is the clock output of the interface block, is the inverted DR\_UPDATE output of the UJTAG macro. It is clear that it gives sufficient time (while the TAP Controller is in the Data Register Update state) for the write address and data to become stable before loading them into the RAM block.

Figure 6-11 presents the test procedure of the example. The data read back from the memory block matches the written data, thus verifying the design functionality.

Figure 6-11 • Simulation of the Test Procedure of the Example

## Low Power Flash Device I/O Support

The low power flash families listed in Table 7-1 support I/Os and the functions described in this document.

#### Table 7-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup> Description |                                                                |

|----------|---------------------------------|----------------------------------------------------------------|

| IGLOO    | IGLOO nano                      | Lowest power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |

| ProASIC3 | ProASIC3 nano                   | Lowest cost 1.5 V FPGAs with balanced performance              |

Note: \*The device name links to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# I/O Software Support

In Microsemi's Libero software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards.

Table 7-15 • nano I/O Attributes vs. I/O Standard Applications

|                      | SLEW             |                                                          |          |                         | LOAD<br>it only)   |                    |            |                     |

|----------------------|------------------|----------------------------------------------------------|----------|-------------------------|--------------------|--------------------|------------|---------------------|

| I/O Standard         | (output<br>only) | OUT_DRIVE (output only)                                  | RES_PULL | IGLOO<br>nano           | ProASIC<br>3 nano  | Schmitt<br>Trigger | Hold State | Combine<br>Register |

| LVTTL/<br>LVCMOS3.3  | 1                | <b>√</b> (8)                                             | ✓        | 1                       | 1                  | ✓                  | 1          | 1                   |

| LVCMOS2.5            | 1                | <b>√</b> (8)                                             | ✓        | ✓                       | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.8            | 1                | <b>√</b> (4)                                             | ✓        | 1                       | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.5            | 1                | <b>√</b> (2)                                             | ✓        | 1                       | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.2            | 1                | <b>√</b> (2)                                             | ✓        | 1                       | _                  | 1                  | ✓          | ✓                   |

| Software<br>Defaults | HIGH             | Refer to<br>numbers in<br>parentheses<br>in above cells. | None     | All<br>Devices:<br>5 pF | 10 pF or<br>35 pF* | Off                | Off        | No                  |

Note: \*10 pF for A3PN010, A3PN015, and A3PN020; 35 pF for A3PN060, A3PN125, and A3PN250.

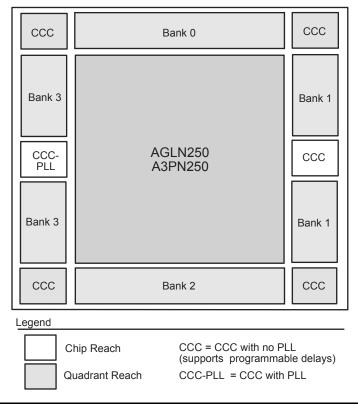

Figure 7-12 • I/O Bank Architecture of AGLN250/A3PN250 Devices

## **Board-Level Considerations**

Low power flash devices have robust I/O features that can help in reducing board-level components. The devices offer single-chip solutions, which makes the board layout simpler and more immune to signal integrity issues. Although, in many cases, these devices resolve board-level issues, special attention should always be given to overall signal integrity. This section covers important board-level considerations to facilitate optimum device performance.

#### **Termination**

Proper termination of all signals is essential for good signal quality. Nonterminated signals, especially clock signals, can cause malfunctioning of the device.

For general termination guidelines, refer to the *Board-Level Considerations* application note for Microsemi FPGAs. Also refer to the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for termination requirements for specific pins.

Low power flash I/Os are equipped with on-chip pull-up/-down resistors. The user can enable these resistors by instantiating them either in the top level of the design (refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide for the available I/O macros with pull-up/-down) or in the I/O Attribute Editor in Designer if generic input or output buffers are instantiated in the top level. Unused I/O pins are configured as inputs with pull-up resistors.

As mentioned earlier, low power flash devices have multiple programmable drive strengths, and the user can eliminate unwanted overshoot and undershoot by adjusting the drive strengths.

## **Related Documents**

## **Application Notes**

Board-Level Considerations

http://www.microsemi.com/soc/documents/ALL\_AC276\_AN.pdf

#### **User's Guides**

Libero SoC User's Guide

http://www.microsemi.com/soc/documents/libero\_ug.pdf

IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide

http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf

SmartGen Core Reference Guide

http://www.microsemi.com/soc/documents/genguide\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date        | Changes                                                                                                                                                                                                                                                                               | Page     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012 | Figure 7-2 • I/O Block Logical Representation for Dual-Tile Designs (60 k,125 k, and 250 k Devices) was revised to indicate that resets on registers 1, 3, 4, and 5 are active high rather than active low (SAR 40698).                                                               | 160      |

|             | The hyperlink for the <i>Board-Level Considerations</i> application note was corrected (SAR 36663).                                                                                                                                                                                   | 181, 183 |

| June 2011   | Figure 7-2 • I/O Block Logical Representation for Dual-Tile Designs (60 k,125 k, and 250 k Devices) was revised so that the I/O_CLR and I/O_OCLK nets are no longer joined in front of Input Register 3 but instead on the branch of the CLR/PRE signal (SAR 26052).                  | 160      |

|             | The following sentence was removed from the "LVCMOS (Low-Voltage CMOS)" section (SAR 22634): "All these versions use a 3.3 V-tolerant CMOS input buffer and a push-pull output buffer."                                                                                               | 166      |

|             | The "5 V Input Tolerance" section was revised to state that 5 V input tolerance can be used with LVTTL 3.3 V and LVCMOS 3.3 V configurations. LVCMOS 2.5 V, LVCMOS 1.8 V, LVCMOS 1.5 V, and LVCMOS 1.2 V were removed from the sentence listing supported configurations (SAR 22427). | 171      |

# 9 – DDR for Microsemi's Low Power Flash Devices

## Introduction

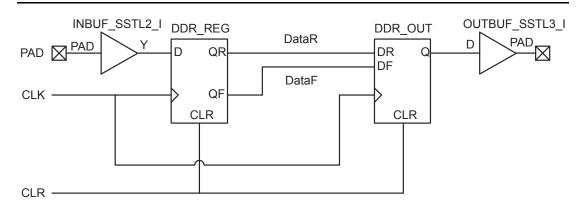

The I/Os in Fusion, IGLOO, and ProASIC3 devices support Double Data Rate (DDR) mode. In this mode, new data is present on every transition (or clock edge) of the clock signal. This mode doubles the data transfer rate compared with Single Data Rate (SDR) mode, where new data is present on one transition (or clock edge) of the clock signal. Low power flash devices have DDR circuitry built into the I/O tiles. I/Os are configured to be DDR receivers or transmitters by instantiating the appropriate special macros (examples shown in Figure 9-4 on page 210 and Figure 9-5 on page 211) and buffers (DDR\_OUT or DDR\_REG) in the RTL design. This document discusses the options the user can choose to configure the I/Os in this mode and how to instantiate them in the design.

## **Double Data Rate (DDR) Architecture**

Low power flash devices support 350 MHz DDR inputs and outputs. In DDR mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidths and signal integrity requirements, making them very efficient for implementing very high-speed systems. High-speed DDR interfaces can be implemented using LVDS (not applicable for IGLOO nano and ProASIC3 nano devices). In IGLOOe, ProASIC3E, AFS600, and AFS1500 devices, DDR interfaces can also be implemented using the HSTL, SSTL, and LVPECL I/O standards. The DDR feature is primarily implemented in the FPGA core periphery and is not tied to a specific I/O technology or limited to any I/O standard.

Figure 9-1 • DDR Support in Low Power Flash Devices

## Types of Programming for Flash Devices

The number of devices to be programmed will influence the optimal programming methodology. Those available are listed below:

- · In-system programming

- Using a programmer

- Using a microprocessor or microcontroller

- · Device programmers

- Single-site programmers

- Multi-site programmers, batch programmers, or gang programmers

- Automated production (robotic) programmers

- Volume programming services

- Microsemi in-house programming

- Programming centers

## In-System Programming

#### **Device Type Supported: Flash**

ISP refers to programming the FPGA after it has been mounted on the system printed circuit board. The FPGA may be preprogrammed and later reprogrammed using ISP.

The advantage of using ISP is the ability to update the FPGA design many times without any changes to the board. This eliminates the requirement of using a socket for the FPGA, saving cost and improving reliability. It also reduces programming hardware expenses, as the ISP methodology is die-/package-independent.

There are two methods of in-system programming: external and internal.

- Programmer ISP—Refer to the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" section on page 261 for more information.

- Using an external programmer and a cable, the device can be programmed through a header on the system board. In Microsemi SoC Products Group documentation, this is referred to as external ISP. Microsemi provides FlashPro4, FlashPro3, FlashPro Lite, or Silicon Sculptor 3 to perform external ISP. Note that Silicon Sculptor II and Silicon Sculptor 3 can only provide ISP for ProASIC and ProASICPLUS® families, not for SmartFusion, Fusion, IGLOO, or ProASIC3. Silicon Sculptor II and Silicon Sculptor 3 can be used for programming ProASIC and ProASICPLUS devices by using an adapter module (part number SMPA-ISP-ACTEL-3).

- Advantages: Allows local control of programming and data files for maximum security. The

programming algorithms and hardware are available from Microsemi. The only hardware

required on the board is a programming header.

- Limitations: A negligible board space requirement for the programming header and JTAG signal routing

- Microprocessor ISP—Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide for more information.

- Using a microprocessor and an external or internal memory, you can store the program in memory and use the microprocessor to perform the programming. In Microsemi documentation, this is referred to as internal ISP. Both the code for the programming algorithm and the FPGA programming file must be stored in memory on the board. Programming voltages must also be generated on the board.

- Advantages: The programming code is stored in the system memory. An external programmer is not required during programming.

- Limitations: This is the approach that requires the most design work, since some way of getting and/or storing the data is needed; a system interface to the device must be designed; and the low-level API to the programming firmware must be written and linked into the code provided by Microsemi. While there are benefits to this methodology, serious thought and planning should go into the decision.

## **ISP Programming Header Information**

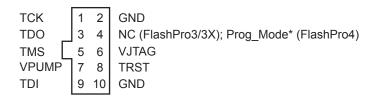

The FlashPro4/3/3X programming cable connector can be connected with a 10-pin, 0.1"-pitch programming header. The recommended programming headers are manufactured by AMP (103310-1) and 3M (2510-6002UB). If you have limited board space, you can use a compact programming header manufactured by Samtec (FTSH-105-01-L-D-K). Using this compact programming header, you are required to order an additional header adapter manufactured by Microsemi SoC Products Group (FP3-10PIN-ADAPTER-KIT).

Existing ProASICPLUS family customers who are using the Samtec Small Programming Header (FTSH-113-01-L-D-K) and are planning to migrate to IGLOO or ProASIC3 devices can also use FP3-10PIN-ADAPTER-KIT.

Table 12-3 • Programming Header Ordering Codes

| Manufacturer | Part Number           | Description                                                                                                                                                                                                                                                                                                                                        |

|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP          | 103310-1              | 10-pin, 0.1"-pitch cable header (right-angle PCB mount angle)                                                                                                                                                                                                                                                                                      |

| ЗМ           | 2510-6002UB           | 10-pin, 0.1"-pitch cable header (straight PCB mount angle)                                                                                                                                                                                                                                                                                         |

| Samtec       | FTSH-113-01-L-D-K     | Small programming header supported by FlashPro and Silicon Sculptor                                                                                                                                                                                                                                                                                |

| Samtec       | FTSH-105-01-L-D-K     | Compact programming header                                                                                                                                                                                                                                                                                                                         |

| Samtec       | FFSD-05-D-06.00-01-N  | 10-pin cable with 50 mil pitch sockets; included in FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                         |

| Microsemi    | FP3-10PIN-ADAPTER-KIT | Transition adapter kit to allow FP3 to be connected to a micro 10-pin header (50 mil pitch). Includes a 6 inch Samtec FFSD-05-D-06.00-01-N cable in the kit. The transition adapter board was previously offered as FP3-26PIN-ADAPTER and includes a 26-pin adapter for design transitions from ProASICPLUS based boards to ProASIC3 based boards. |

Note: \*Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 12-5 • Programming Header (top view)

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| August 2012 | This chapter will now be published standalone as an application note in addition to being part of the IGLOO/ProASIC3/Fusion FPGA fabric user's guides (SAR 38769).                                                                                                                                                                                                                                                                          | N/A      |

|             | The "ISP Programming Header Information" section was revised to update the description of FP3-10PIN-ADAPTER-KIT in Table 12-3 • Programming Header Ordering Codes, clarifying that it is the adapter kit used for ProASICPLUS based boards, and also for ProASIC3 based boards where a compact programming header is being used (SAR 36779).                                                                                                | 269      |

| June 2011   | The VPUMP programming mode voltage was corrected in Table 12-2 • Power Supplies. The correct value is 3.15 V to 3.45 V (SAR 30668).                                                                                                                                                                                                                                                                                                         | 263      |

|             | The notes associated with Figure 12-5 • Programming Header (top view) and Figure 12-6 • Board Layout and Programming Header Top View were revised to make clear the fact that IGLOO nano V2 devices can be programmed at 1.2 V (SAR 30787).                                                                                                                                                                                                 | 269, 271 |

|             | Figure 12-6 • Board Layout and Programming Header Top View was revised to include resistors tying TCK and TRST to GND. Microsemi recommends tying off TCK and TRST to GND if JTAG is not used (SAR 22921). RT ProASIC3 was added to the list of device families.                                                                                                                                                                            | 271      |

|             | In the "ISP Programming Header Information" section, the kit for adapting ProASICPLUS devices was changed from FP3-10PIN-ADAPTER-KIT to FP3-26PIN-ADAPTER-KIT (SAR 20878).                                                                                                                                                                                                                                                                  | 269      |

| July 2010   | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                                                                                                                                   | N/A      |

|             | References to FlashPro4 and FlashPro3X were added to this chapter, giving distinctions between them. References to SmartGen were deleted and replaced with Libero IDE Catalog.                                                                                                                                                                                                                                                              | N/A      |

|             | The "ISP Architecture" section was revised to indicate that V2 devices can be programmed at 1.2 V VCC with FlashPro4.                                                                                                                                                                                                                                                                                                                       | 261      |

|             | SmartFusion was added to Table 12-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                                                                                                     | 262      |

|             | The "Programming Voltage (VPUMP) and VJTAG" section was revised and 1.2 V was added to Table 12-2 • Power Supplies.                                                                                                                                                                                                                                                                                                                         | 263      |

|             | The "Nonvolatile Memory (NVM) Programming Voltage" section is new.                                                                                                                                                                                                                                                                                                                                                                          | 263      |

|             | Cortex-M3 was added to the "Cortex-M1 and Cortex-M3 Device Security" section.                                                                                                                                                                                                                                                                                                                                                               | 265      |

|             | In the "ISP Programming Header Information" section, the additional header adapter ordering number was changed from FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT, which contains 26-pin migration capability.                                                                                                                                                                                                                                 | 269      |

|             | The description of NC was updated in Figure 12-5 • Programming Header (top view), Table 12-4 • Programming Header Pin Numbers and Description and Figure 12-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                               | 269, 270 |

|             | The "Symptoms of a Signal Integrity Problem" section was revised to add that customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots. "FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems" formerly read, "from 24 MHz down to 1 MHz." "The Scan Chain command expects to see 0x2" was changed to 0x1. | 271      |

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

## Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 13-1 support the voltage switching circuit feature and the functions described in this document.

Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series   | Family*              | Description                                                           |

|----------|----------------------|-----------------------------------------------------------------------|

| IGL00    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Microprocessor Programming Support in Flash Devices**

The flash-based FPGAs listed in Table 14-1 support programming with a microprocessor and the functions described in this document.

Table 14-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGL00    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Typical UJTAG Applications**

Bidirectional access to the JTAG port from VersaTiles—without putting the device into test mode—creates flexibility to implement many different applications. This section describes a few of these. All are based on importing/exporting data through the UJTAG tiles.

## Clock Conditioning Circuitry—Dynamic Reconfiguration

In low power flash devices, CCCs, which include PLLs, can be configured dynamically through either an 81-bit embedded shift register or static flash programming switches. These 81 bits control all the characteristics of the CCC: routing MUX architectures, delay values, divider values, etc. Table 16-3 lists the 81 configuration bits in the CCC.

Table 16-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks

| Bit Number(s) | Control Function |  |

|---------------|------------------|--|

| 80            | RESET ENABLE     |  |

| 79            | DYNCSEL          |  |

| 78            | DYNBSEL          |  |

| 77            | DYNASEL          |  |

| <76:74>       | VCOSEL [2:0]     |  |

| 73            | STATCSEL         |  |

| 72            | STATBSEL         |  |

| 71            | STATASEL         |  |

| <70:66>       | DLYC [4:0]       |  |

| <65:61>       | DLYB {4:0]       |  |

| <60:56>       | DLYGLC [4:0]     |  |

| <55:51>       | DLYGLB [4:0]     |  |

| <50:46>       | DLYGLA [4:0]     |  |

| 45            | XDLYSEL          |  |

| <44:40>       | FBDLY [4:0]      |  |

| <39:38>       | FBSEL            |  |

| <37:35>       | OCMUX [2:0]      |  |

| <34:32>       | OBMUX [2:0]      |  |

| <31:29>       | OAMUX [2:0]      |  |

| <28:24>       | OCDIV [4:0]      |  |

| <23:19>       | OBDIV [4:0]      |  |

| <18:14>       | OADIV [4:0]      |  |

| <13:7>        | FBDIV [6:0]      |  |

| <6:0>         | FINDIV [6:0]     |  |

The embedded 81-bit shift register (for the dynamic configuration of the CCC) is accessible to the VersaTiles, which, in turn, have access to the UJTAG tiles. Therefore, the CCC configuration shift register can receive and load the new configuration data stream from JTAG.

Dynamic reconfiguration eliminates the need to reprogram the device when reconfiguration of the CCC functional blocks is needed. The CCC configuration can be modified while the device continues to operate. Employing the UJTAG core requires the user to design a module to provide the configuration data and control the CCC configuration shift register. In essence, this is a user-designed TAP Controller requiring chip resources.

Similar reconfiguration capability exists in the ProASIC PLUS® family. The only difference is the number of shift register bits controlling the CCC (27 in ProASIC and 81 in IGLOO, ProASIC3, and Fusion).